# S6D0114

# **Preliminary**

132 RGB X 176 DOT 1-CHIP DRIVER IC WITH INTERNAL GRAM FOR 262,144 Colors TFT-LCD

July 3, 2002

Ver. 0.0

Prepared by: MinSeok Song

tempest0@samsung.com

Contents in this document are subject to change without notice. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of LCD Driver IC Team.

|         | S6D0114 Specification Revision History |            |               |  |  |  |  |

|---------|----------------------------------------|------------|---------------|--|--|--|--|

| Version | Content Author Date                    |            |               |  |  |  |  |

| 0.0     | Original                               | M. S. Song | July 3 , 2002 |  |  |  |  |

#### INTRODUCTION

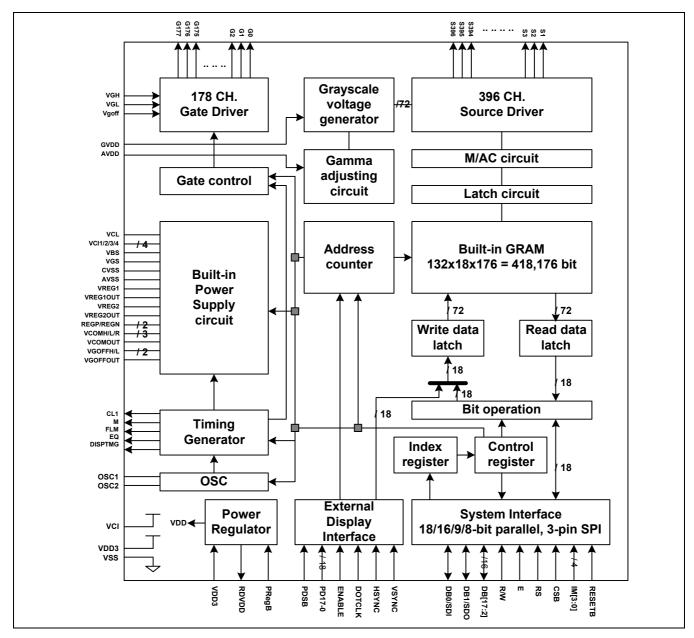

The S6D0114 is 1-chip solution for TFT-LCD panel: source driver with built-in memory, gate driver, power IC are integrated on one chip. This IC can display to a maximum of 132-RGB x 176-dot graphics on 260k-color TFT panel.

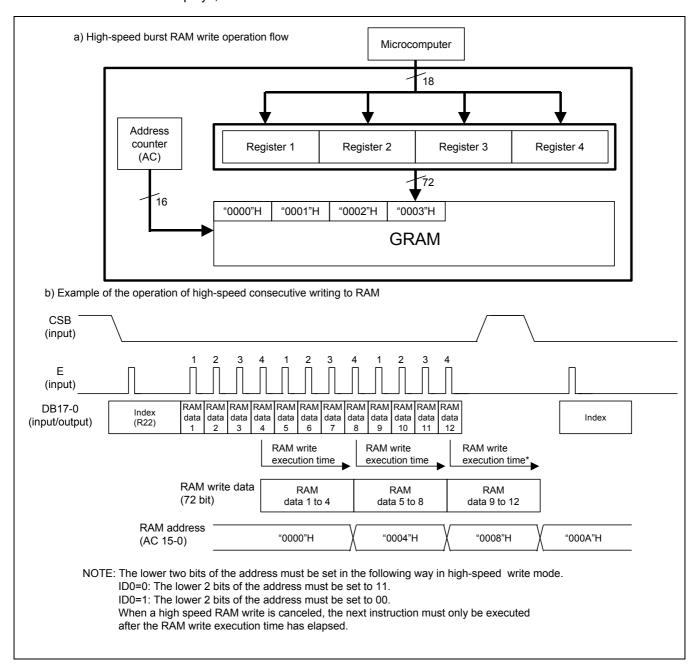

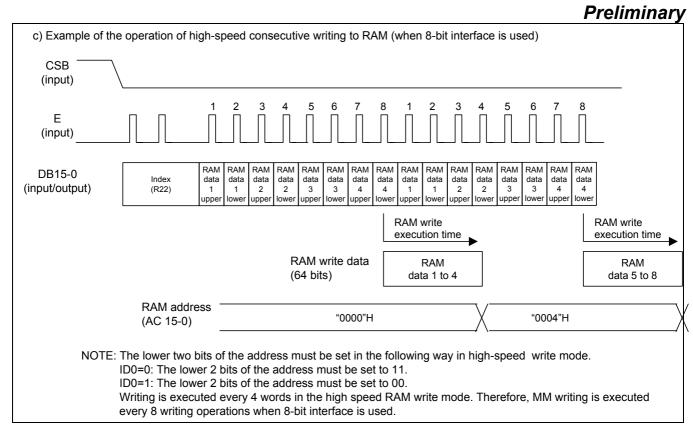

The S6D0114 also supports bit-operation functions, 18-/16-/9-/8-bit high-speed bus interface and high-speed RAM-write functions enable efficient data transfer and high-speed rewriting of data to the internal GRAM.

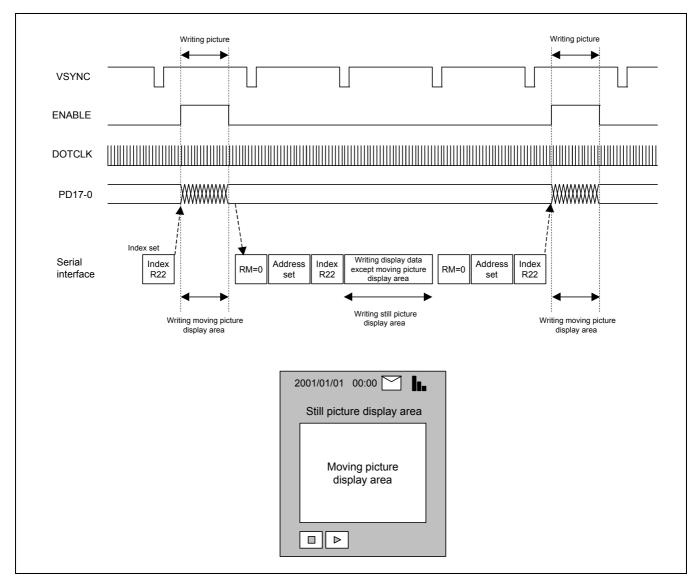

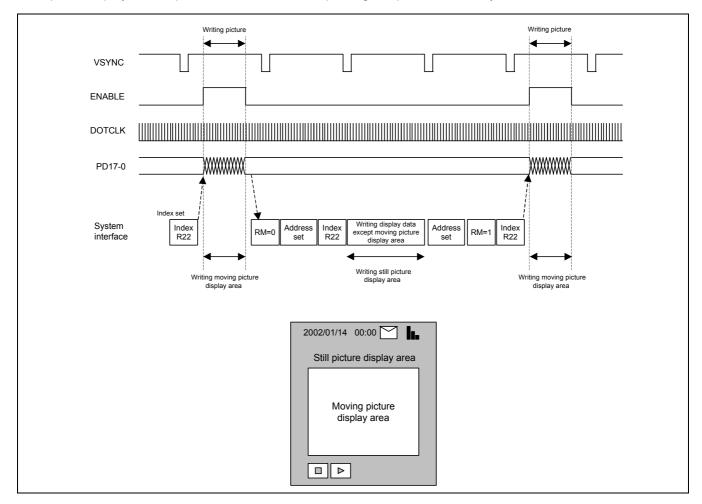

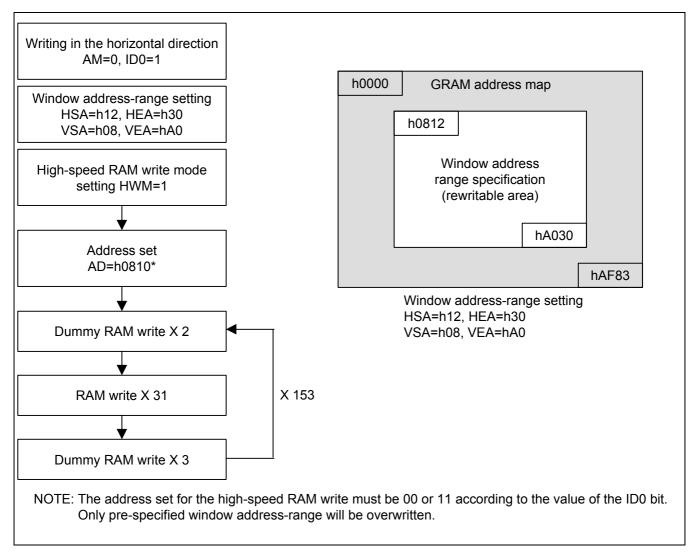

The moving picture area can be specified in internal GRAM by window function. The specified window area can be updated selectively, so that moving picture is able to be displayed simultaneously independent of still picture area.

The S6D0114 has various functions for reducing the power consumption of a LCD system: operating at low voltage (minimum 1.8V), register-controlled power-save mode, partial display mode and so on. The IC has internal GRAM to store 132-RGB x 176-dot 260k-color image and internal booster that generates the LCD driving voltage, breeder resistance and the voltage follower circuit for LCD driver.

This LSI is suitable for any medium-sized or small portable mobile solution requiring long-term driving capabilities, such as digital cellular phones supporting a web browser, bi-directional pagers, and small PDAs.

#### **FEATURES**

132-RGB x 176-dot TFT-LCD display controller/driver IC for 262,144 colors (396ch-source driver/176ch-gate driver)

18-/16-/9-/8-bit high-speed parallel bus interface (80- and 68- system) and serial peripheral interface (SPI)

High-speed RAM write function (transfer 4-word at a time)

Writing to a window-RAM address area by using a window-address function

#### Bit-operation function for graphic processing

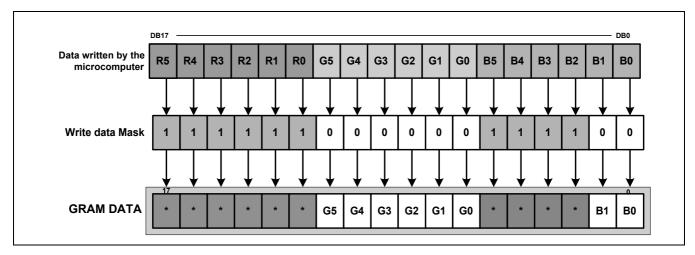

- Write-data mask functions in bit units

- Logical operation in pixel unit and conditional write function

#### Various color-display control functions

- 262,144 colors can be displayed at the same time (including gamma adjust)

- Vertical scroll display function in raster-row units

#### Internal RAM capacity: 132 x 18 x 176 = 418,176 bits

#### Low-power operation supports:

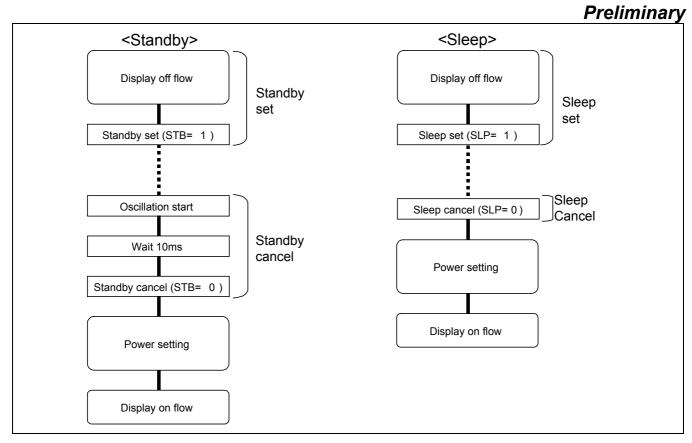

- Power-save mode: standby mode, sleep mode

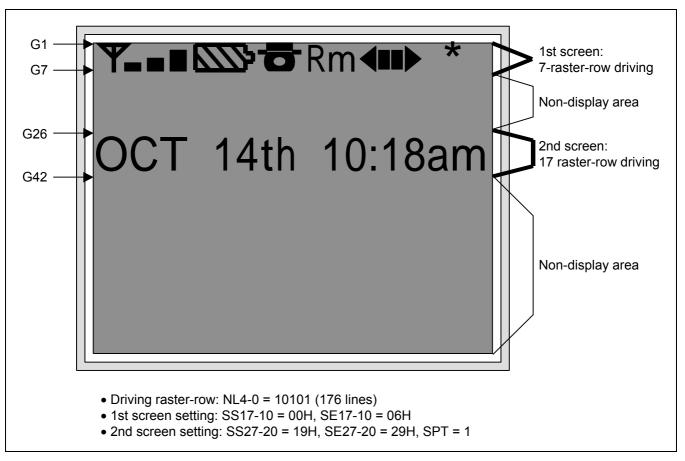

- Partial display of two screens in any position

- Maximum 12-time step-up circuit for generating driving voltage

- Voltage followers to decrease direct current flow in the LCD drive breeder-resistors

- Equalizing function for the switching performance of step-up circuits and operational amplifiers

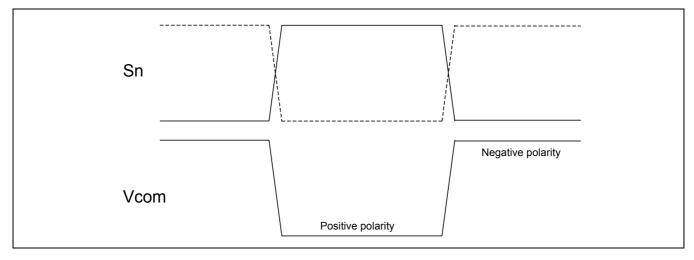

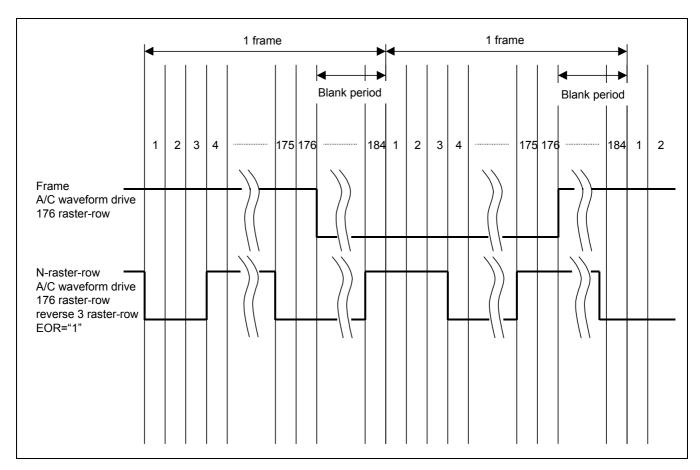

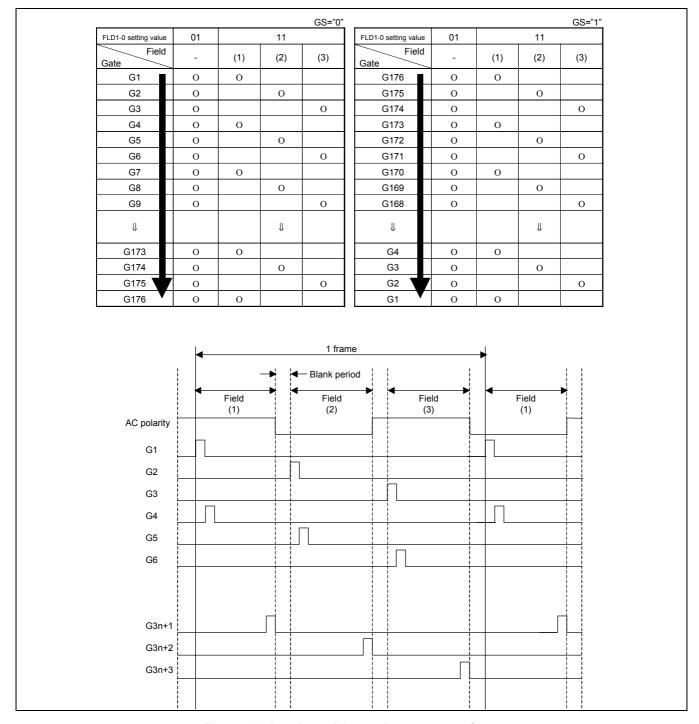

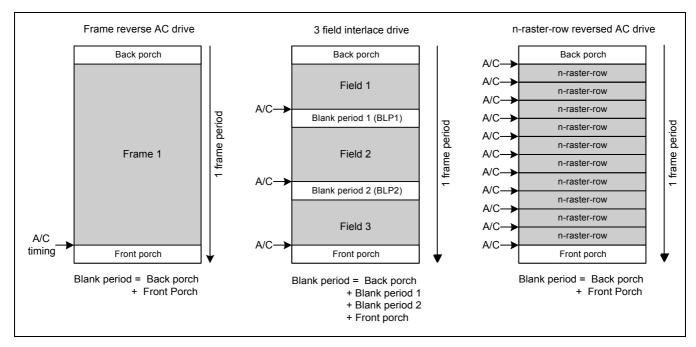

N-raster row inversion drive (Reverse the polarity of driving voltage in every selected raster row)

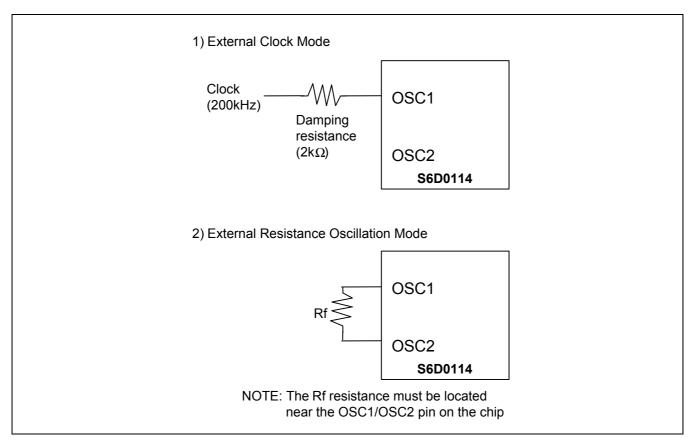

Internal oscillation circuit and external hardware reset

Structure for TFT-display retention volume (Cst/Cadd structure)

#### Alternating functions for TFT-LCD counter-electrode power

N-line alternating drive of Vcom (Vgoff is also available for N-line alternating drive for Cadd)

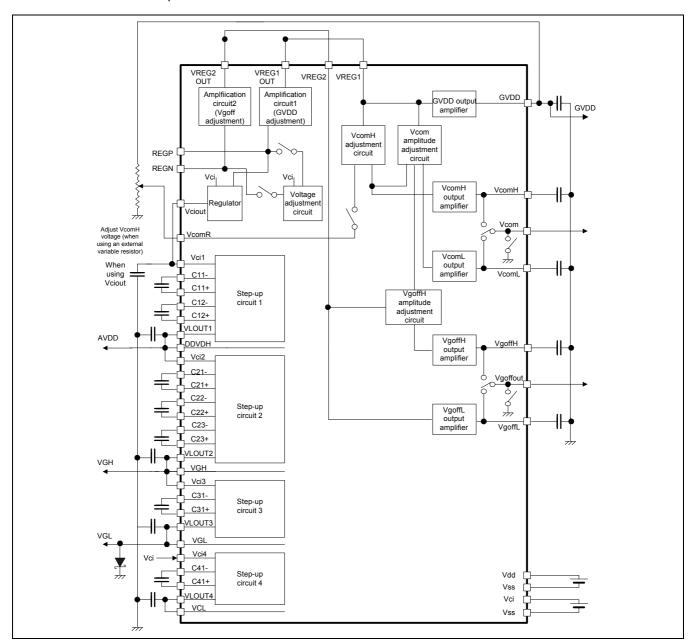

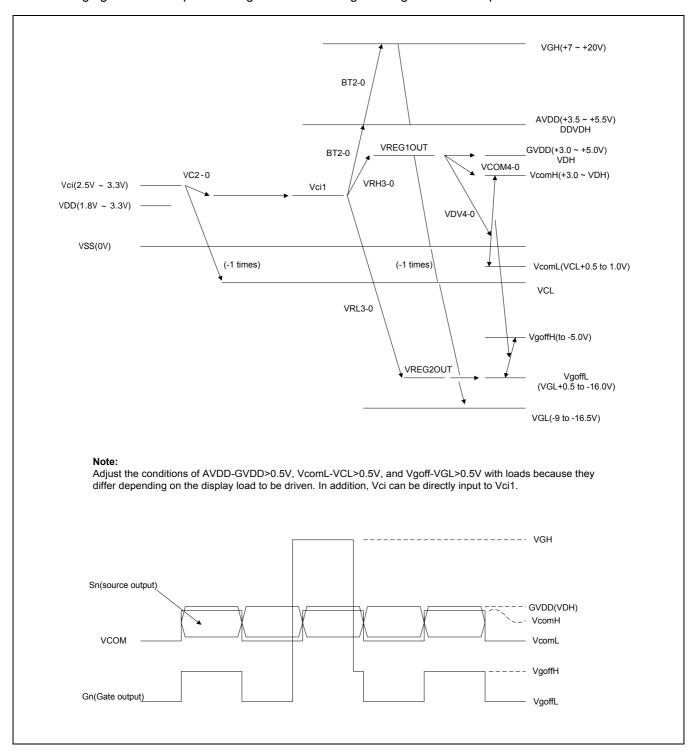

#### Internal power supply circuit

- Step-up circuit: five to nine times, positive-polarity inversion

- Adjustment of Vcom(Vgoff) amplitude: internal 22-level digital potentiometer

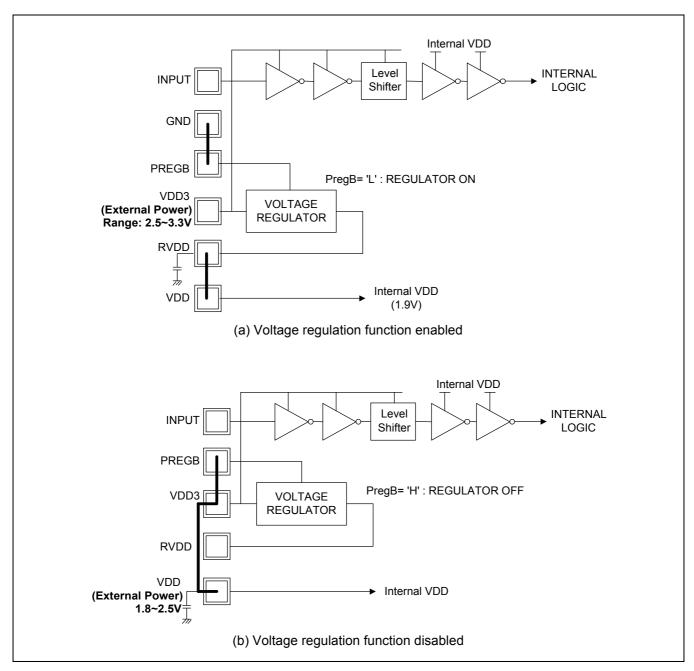

#### **Operating voltage**

- Apply voltage

- VDD to VSS = 1.8 to 2.5 V (non-regulating) (logic voltage range non-regulated)

VDD3 to VSS = 2.3 to 3.3 V (regulating) (logic voltage range regulated)

- Vci to VSS = 2.5 to 3.3 V (internal reference power-supply voltage)

- Vci1 to VSS = 1.7 to 2.75 V (2.5 x  $0.68 \sim 2.75$ ) (power supply for step-up circuits)

- Generate voltage

- For the source driver: AVDD to VSS = 3.5 to 5.5V (power supply for driving circuits)

GVDD to VSS = 3.0 to 5.0V (reference power supply for grayscale voltages)

- For the gate driver: VGH to VGL = 14 to 30 V, VGH to VSS = +7.0 to +20 V, VgoffL = (VGL+0.5)V to -7.5V, VgoffH =  $\sim$  to -1.5V

- For the TFT-LCD counter electrode: Vcom amplitude(max) = 6V, VcomH to VSS(max) = GVDD

VcomL to VSS (max) = 1.0 V to -Vci + 0.5 V

#### **BLOCK DIAGRAM**

Figure 1. S6D0114 Block Diagram

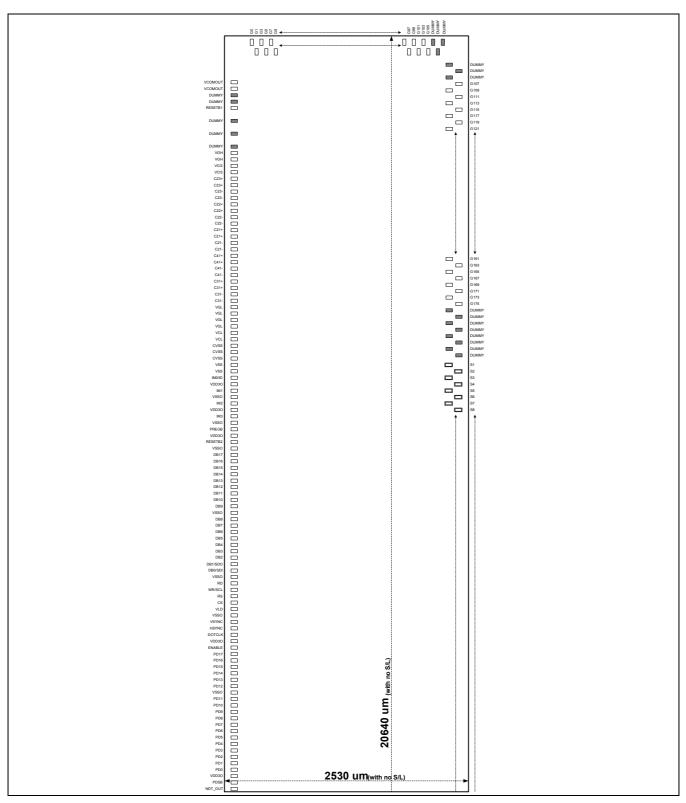

# **PAD CONFIGURATION**

Figure 2. Pad Configuration

Figure 3. Pad Configuration (continued)

Table 1. S6D0114 Pad Dimensions

| Items                   | Pad name.  | Siz   | Unit |      |

|-------------------------|------------|-------|------|------|

| items                   | rau name.  | X     | Y    | Onit |

| Chip size <sup>1)</sup> | -          | 20640 | 2530 |      |

| Dod size                | INPUT PAD  | 54    | 100  | um   |

| Pad size                | OUTPUT PAD | 36    | 70   |      |

#### NOTES:

Scribe line is not included in this chip size (Scribe line: 120um)

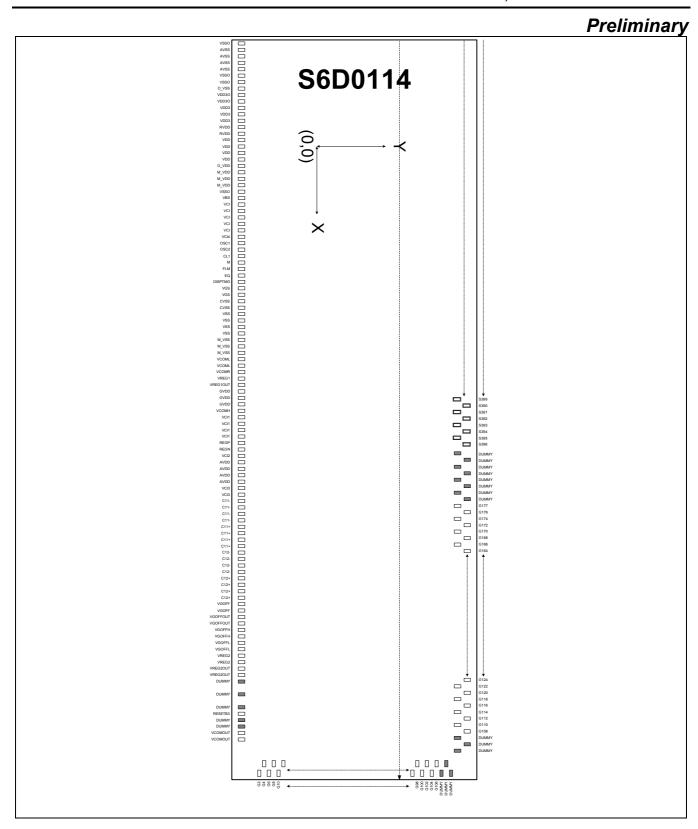

# **ALIGN KEY CONFIGURATION AND COORDINATE**

T.B.D

Figure 4. COG and ILB align key

# T.B.D

Figure 5. Bump align key and align key configuration

# **PAD CENTER COORDINATES**

**Table 2. Pad Center Coordinates**

[Unit: um]

(T.B.D)

#### PIN DESCRIPTION

#### **POWER SUPPLY PIN**

Table 3. Power supply pin description

| Symbol | I/O          | Description                                                                                                                                                                        |

|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | I /<br>Power | System power supply. As S6D0114 has internal regulator, VDD range varies with each mode. Non-regulated mode (PregB = 1): +1.8 ~ +2.5 V Regulated mode (PregB = 0): +1.9V           |

| VDD3   | I /<br>Power | System power supply for regulator as external power. (VDD3: +2.5 ~ +3.3 V)                                                                                                         |

| AVDD   | O /<br>Power | A power output pin for source driver block that is generated from power block. Connect a capacitor for stabilization. (AVDD: +3.5 ~ +5.5 V) Interconnect this pin to VCI2 pin.     |

| GVDD   | I /<br>Power | A Standard level for grayscale voltage generator.  Connect a capacitor for stabilization. When internal GVDD generator is not used, connect an external power supply, AVDD – 0.5 V |

| VCI    | I /<br>Power | An internal reference power supply for VREG1OUT/VREG2OUT. Connect VDD when VDD = 2.5 to 3.3 V. Connect a 2.5 to 3.3 V external-voltage power supply when VDD = 1.8 to 2.5 V.       |

| VSS    | I /<br>Power | System ground (0V)                                                                                                                                                                 |

| CVSS   | I /<br>Power | System ground level for step up circuit block.                                                                                                                                     |

| AVSS   | I /<br>Power | System ground level for analog circuit block.                                                                                                                                      |

| VGS    | I /<br>Power | Reference voltage for gamma voltage generator.                                                                                                                                     |

| VCI1   | Power        | A reference voltage in step-up circuit 1. Connect a capacitor for stabilization.                                                                                                   |

| VCI2   | Power        | A reference voltage in step-up circuit 2.                                                                                                                                          |

| VCI3   | Power        | A reference voltage in step-up circuit 3.                                                                                                                                          |

| VCI4   | Power        | A reference voltage in step-up circuit 4. Connect VCI, VDD, or external power supply lower than 3.3 V.                                                                             |

| VCL    | Power        | A power supply pin for generating VcomL. When VcomL is higher than VSS, outputs VSS level.                                                                                         |

Table 4. Power supply pin description (continued)

| Symbol        | I/O         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBS           | I           | Reference voltage for step-up circuit3.                                                                                                                                                                                                                                                                                                                                                                                                       |

| REGN,<br>REGP | I/O         | Input pins for reference voltages of VREG1OUT, and VREG2OUT when the internal reference-voltage generation circuit is not used. Leave these pins open when the internal reference-voltage generation circuit is used.                                                                                                                                                                                                                         |

| VREG10UT      | 0           | This pin outputs a reference voltage for VREG1 between AVDD and VSS. When the internal reference voltage is not used, the reference voltage can be generated from the voltage of REGP. Connect this pin to VREG1 and a capacitor for stabilization. When this pin is not used, leave it open.                                                                                                                                                 |

| VREG2OUT      | 0           | This pin outputs a reference voltage for VREG2 between VSS and VGL When the internal reference voltage is not used, the reference voltage can be generated from the voltage of REGN. Connect this pin to VREG2 and a capacitor for stabilizatio0n. When this pin is not used, leave it open.                                                                                                                                                  |

| VcomOUT       | 0           | A power supply for the TFT-display counter electrode. The alternating cycle can be set by the M pin. Connect this pin to the TFT-display counter electrode. This pin is also used as equalizing function: When EQ = "High" period, all source driver's outputs (S1 to S396) are short to Vcom level (Hi-z). In case of VcomL < 0V, equalizing function must not be used. (Set EQ bit (R07h) to be "00" for preventing the abnormal function.) |

| VcomR         | I           | A reference voltage of VcomH. When VcomH is externally adjusted, halt the internal adjuster of VcomH by setting the register and insert a variable resistor between GVDD and VSS. When this pin is not externally adjusted, leave it open and adjust VcomH by setting the internal register.                                                                                                                                                  |

| VcomH         | 0           | This pin indicates a high level of Vcom generated in driving the Vcom alternation.  Connect this pin to the capacitor for stabilization.                                                                                                                                                                                                                                                                                                      |

| VcomL         | 0           | When the Vcom alternation is driven, this pin indicates a low level of Vcom. An internal register can be used to adjust the voltage. Connect this pin to a capacitor for stabilization. When the VCOMG bit is low, the VcomL output stops and a capacitor for stabilization is not needed.                                                                                                                                                    |

| VGH           | O/<br>Power | A positive power output pin for gate driver, internal step-up circuits, bias circuits, and operational amplifiers. Connect a capacitor for stabilization.  Interconnect this pin to VCI3 pin.                                                                                                                                                                                                                                                 |

| VGL           | O/<br>Power | A Negative power output pin for gate driver, bias circuits, and operational amplifiers.  Connect a capacitor for stabilization. When internal VGL generator is not used, connect an external-voltage power supply higher than -15.0 V.                                                                                                                                                                                                        |

Table 5. Power supply pin description (continued)

| Symbol                      | I/O | Description                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vgoff                       | I   | Power supply pin for off level for gate of TFT. Connect VgoffOUT and a capacitor for stabilization. When VgoffOUT is not used, connect an external-voltage power supply higher than -TBD V.                                                                                                                                                                        |

| VgoffOUT                    | 0   | An power output pin for gate driver. This pin is a negative voltage for the gate off level. Alternation can be synchronized by M pin. Set the internal register according to the structure of the TFT-display retention volume. For the amplitude at the alternation driving, this pin outputs a voltage between VcomH and VcomL with the VgoffL reference voltage |

| VgoffH                      | 0   | When the Vgoff alternation is driven, this pin indicates a high level of Vgoff. Connect a capacitor for stabilization. When the CAD bit is low, the VgoffH output stops and a capacitor for stabilization is not needed.                                                                                                                                           |

| VgoffL                      | 0   | When the Vgoff alternation is driven, this pin indicates a low level of Vgoff. Connect a capacitor for stabilization. An internal register can be used to adjust the voltage.                                                                                                                                                                                      |

| C11+,C11-<br>~<br>C23+,C23- | -   | Connect the step-up capacitor according to the step-up factor.                                                                                                                                                                                                                                                                                                     |

| C31+ ,<br>C31-              | -   | Connect a step-up capacitor for generating the VGL level.                                                                                                                                                                                                                                                                                                          |

| C41+ ,<br>C41-              | -   | Connect a step-up capacitor for generating the -VCL level.                                                                                                                                                                                                                                                                                                         |

#### **SYSTEM INTERFACE PIN**

Table 6. System interface pin description

| Symbol         | I/O | Description                                                                                                                                                                                                                                                                                            |                                                                                                                                                                           |              |          |                                   |                                               |                    |  |

|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|-----------------------------------|-----------------------------------------------|--------------------|--|

|                |     | Selects the MPU interface mode:                                                                                                                                                                                                                                                                        |                                                                                                                                                                           |              |          |                                   |                                               |                    |  |

|                |     | IM3                                                                                                                                                                                                                                                                                                    | IM2                                                                                                                                                                       | IM1          | IM0/ID   | MPL                               | J interface mode                              | DB PIN assign      |  |

|                |     | VSS                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VSS          | VSS      | 68-system                         | 16-bit bus interface                          | DB17-10, DB8-1     |  |

|                |     | VSS                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VSS          | VDD      |                                   | 8bit bus interface                            | DB17-10            |  |

|                |     | VSS                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VDD          | VSS      | 80-system                         | 16bit bus interface                           | DB17-10, DB8-1     |  |

|                |     | VSS                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VDD          | VDD      |                                   | 8bit bus interface                            | DB17-10            |  |

| IM3-1,         |     | VSS                                                                                                                                                                                                                                                                                                    | VDD                                                                                                                                                                       | VSS          | ID       | Serial perip                      | heral interface (SPI)                         | DB1-0              |  |

| IM0/ID         | ı   | VSS                                                                                                                                                                                                                                                                                                    | VDD                                                                                                                                                                       | VDD          | *        | Non-selecti                       | ing                                           | -                  |  |

|                |     | VDD                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VSS          | VSS      | 68-system                         | 18-bit bus interface                          | DB17-0             |  |

|                |     | VDD                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VSS          | VDD      | 68-system                         | 9bit bus interface                            | DB17-9             |  |

|                |     | VDD                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VDD          | VSS      | 80-system                         | 18bit bus interface                           | DB17-0             |  |

|                |     | VDD                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | VDD          | VDD      | 80-system                         | 9bit bus interface                            | DB17-9             |  |

|                |     | VDD                                                                                                                                                                                                                                                                                                    | VDD                                                                                                                                                                       | *            | *        | Non-selecti                       | ing                                           | -                  |  |

|                |     | When a                                                                                                                                                                                                                                                                                                 | SPI mod                                                                                                                                                                   | le is selec  | ted, the | IM0 pin is us                     | ed as ID setting bit for a                    | device code.       |  |

| CSB            | I   | Low: S6<br>High: S6                                                                                                                                                                                                                                                                                    | Chip select signal input pin. Low: S6D0114 is selected and can be accessed High: S6D0114 is not selected and cannot be accessed Must be fixed at VSS level when not used. |              |          |                                   |                                               |                    |  |

| RS             | 1   |                                                                                                                                                                                                                                                                                                        | Register select pin. Low: Index/status, High: Control                                                                                                                     |              |          |                                   |                                               |                    |  |

|                |     | IM2                                                                                                                                                                                                                                                                                                    | IM1                                                                                                                                                                       | Pin func     | . M      | PU type                           | Pin desc                                      | ription            |  |

|                |     | VSS                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | Е            | 68       | -system                           | Read/Write operation                          | enable pin.        |  |

| E<br>(/WR,SCL) | 1   | VSS                                                                                                                                                                                                                                                                                                    | VDD                                                                                                                                                                       | /WR          | 80       | -system                           | Write strobe signal inp                       |                    |  |

| (/WIX,GOL)     |     | VDD                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | SCL          |          | l peripheral<br>Iterface<br>(SPI) | the synchronous clock signal input pin        |                    |  |

|                |     | IM2                                                                                                                                                                                                                                                                                                    | IM1                                                                                                                                                                       | Pin func     | . M      | PU type                           | Pin desc                                      | ription            |  |

| R/W            |     | VSS                                                                                                                                                                                                                                                                                                    | VSS                                                                                                                                                                       | R/W          | 68       | -system                           | Read/Write operation : Low: Write , High: Rea |                    |  |

| (/RD)          | ı   | VSS                                                                                                                                                                                                                                                                                                    | VDD                                                                                                                                                                       | /RD          | 80       | -system                           | Read strobe signal inp                        |                    |  |

|                |     | When SPI mode is selected, fix this pin at VSS level.                                                                                                                                                                                                                                                  |                                                                                                                                                                           |              |          |                                   |                                               |                    |  |

| DB0/SDI        | I/O | Bi-directional data bus.  18-bit interface: DB 17-0  16-bit interface: DB 17-10, DB 8-1  9-bit interface: DB 17-9  8-bit interface: DB 17-10  Fix DB0 to the VDD3 or VSS level if the pin is not in use.  For a serial peripheral interface (SPI), input data is fetched at the rising edge of the SCI |                                                                                                                                                                           |              |          |                                   | og edge of the SCI                            |                    |  |

|                |     | signal.                                                                                                                                                                                                                                                                                                | siiai peiik                                                                                                                                                               | חוכומו ווונל | ilace (S | i i), iliput da                   | ita is lettiled at the lish                   | ig eage of the SCL |  |

Table 7. System interface pin description (Continued)

| DB1/SDO                         | I/O | Fix DB1 to the                                                                                                                                                                                                                                                                            | Bi-directional data bus.  18-bit interface: DB 17-0  16-bit interface: DB 17-10, DB 8-1  9-bit interface: DB 17-9  8-bit interface: DB 17-10  Fix DB1 to the VDD3 or VSS level if the pin is not in use.  For a serial peripheral interface (SPI), serves as the serial data output pin (SDO).  Successive bits are output at the falling edge of the SCL signal. |                                |                              |  |  |  |  |

|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|--|--|--|--|

| DB17-DB2                        | I/O |                                                                                                                                                                                                                                                                                           | Bi-directional data bus.  18-bit interface: DB 17-0  16-bit interface: DB 17-10, DB 8-1  9-bit interface: DB 17-9  8-bit interface: DB 17-10  Fix unused pin to the VDD3 or VSS level.                                                                                                                                                                            |                                |                              |  |  |  |  |

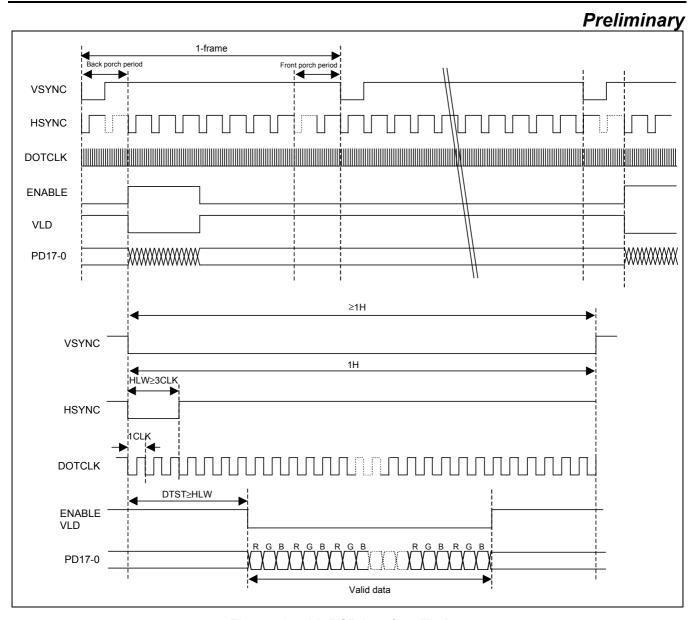

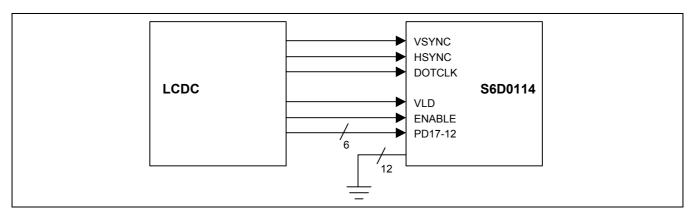

| VLD                             | I   | CSB 0 0 1 Fix VLD pin a                                                                                                                                                                                                                                                                   | GRAM address Update Update Storage                                                                                                                                                                                                                                                                                                                                |                                |                              |  |  |  |  |

| ENABLE                          | I   | Data enable signal pin for RGB interface. High: the IC can be access via RGB interface. Low: the IC cannot be access via RGB interface  ENABLE VLD GRAM write GRAM addre  1 0 Valid Update  1 1 Invalid Update  0 * Invalid Storage  Fix ENABLE pin at VDD3 level if the pin is not used. |                                                                                                                                                                                                                                                                                                                                                                   |                                |                              |  |  |  |  |

| VSYNC                           | I   | Synchronous<br>Low: active                                                                                                                                                                                                                                                                | signal of frame.                                                                                                                                                                                                                                                                                                                                                  | if the pin is not used.        |                              |  |  |  |  |

| HSYNC                           | I   | Low: active                                                                                                                                                                                                                                                                               | Synchronous signal of line.  Low: active Fix HSYNC pin at VDD3 level if the pin is not used.                                                                                                                                                                                                                                                                      |                                |                              |  |  |  |  |

| DOTCLK                          | I   | Input pin for o                                                                                                                                                                                                                                                                           | lot clock.                                                                                                                                                                                                                                                                                                                                                        |                                |                              |  |  |  |  |

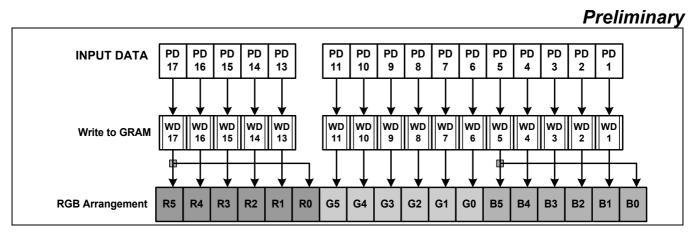

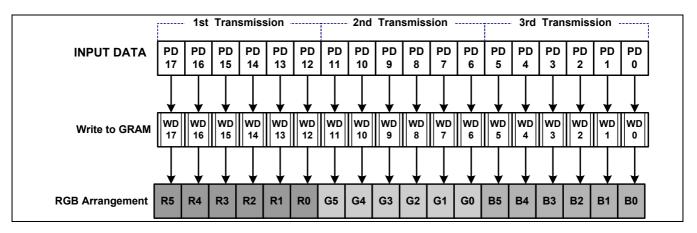

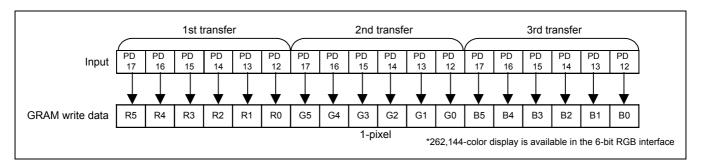

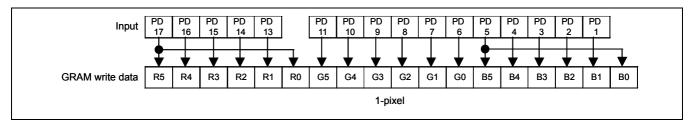

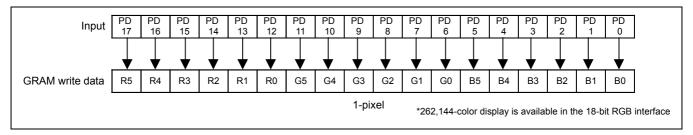

| PD17-PD0                        | I   | RGB data input bus.  18-bit interface: PD 17-0  16-bit interface: PD 17-13, PD 11-1  6-bit interface: PD 17-12  Fix unused pin to the VDD3 or VSS level.                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                   |                                |                              |  |  |  |  |

| PDSB                            | I   | RGB and SYS pin is "low".                                                                                                                                                                                                                                                                 | STEM interface I                                                                                                                                                                                                                                                                                                                                                  | hold DB17-0 pin in common a    | s a data input pin when PDSB |  |  |  |  |

| RESETB1/<br>RESETB2/<br>RESETB3 | I   | Reset pin. Init                                                                                                                                                                                                                                                                           | tializes the LSI w                                                                                                                                                                                                                                                                                                                                                | hen low. Must be reset after p | oower-on.                    |  |  |  |  |

#### **DISPLAY PIN**

Table 8. Display pin description

| Symbol      | I/O | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1 - S396   | 0   | Source driver output pins.  The SS bit can change the shift direction of the source signal.  For example, if SS = 0, gray data of S1 is read from RAM address 0000h.  If SS = 1, contents of is RAM address 0000h is out from S396.  S1, S4, S7, S(3n-1): display Red (R) (SS = 0)  S2, S5, S8, S(3n-2): display Green (G) (SS = 0)  S3, S6, S9, S(3n): display Blue (B) (SS = 0) |

| G1 - G176   | 0   | Gate driver output pins. The output of driving circuit is whether VGH or Vgoff. VGH: gate-ON level Vgoff: gate-OFF level                                                                                                                                                                                                                                                          |

| G0,<br>G177 | 0   | Gate driver output pins for IC maker' stesting. Please, leave it disconnected.                                                                                                                                                                                                                                                                                                    |

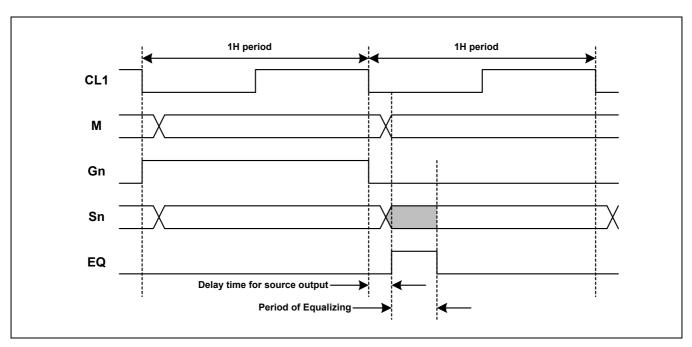

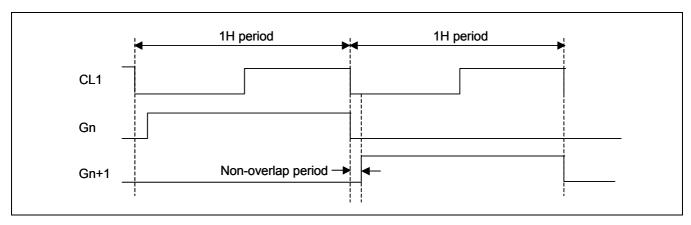

| CL1         | 0   | Output pin for raster-row clock pulse.                                                                                                                                                                                                                                                                                                                                            |

| М           | 0   | Output pin for AC-cycle signal.                                                                                                                                                                                                                                                                                                                                                   |

| FLM         | 0   | Output pin for frame-start pulse.                                                                                                                                                                                                                                                                                                                                                 |

| EQ          | 0   | Output pin for timing for equalizing. Low : Normal display, High : Equalizing                                                                                                                                                                                                                                                                                                     |

| DISPTMG     | 0   | Output pin for Gate off signal.  High : Normal output  Low : Non-display                                                                                                                                                                                                                                                                                                          |

# **MISCELLANEOUS CONTROL PIN**

Table 9. Oscillator and internal power regulator pin description

| Symbol        | I/O | Description                                                                                                                                                                                                              |

|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/<br>OSC2 | I/O | Connect an external resistor for R-C oscillation. When input the clock from outside, input to OSC1, and open OSC2.                                                                                                       |

| PregB         | ı   | Internal power regulator control input pin. When the internal regulated power (RDVDD) is used as VDD, PregB is fixed to "low" level. When the external logic power(VDD3) is used as VDD, PregB is fixed to "high" level. |

| RDVDD         | 0   | Internal power regulated-VDD output (typ. 1.8V). When PregB is "low", RDVDD is connected to VDD pin. When PRegB is "high", leave this pin open.                                                                          |

#### **FUNCTIONAL DESCRIPTION**

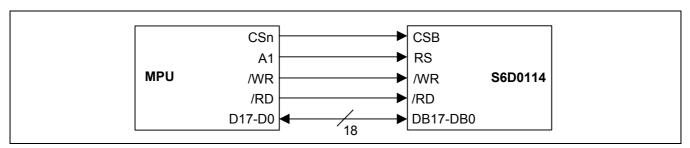

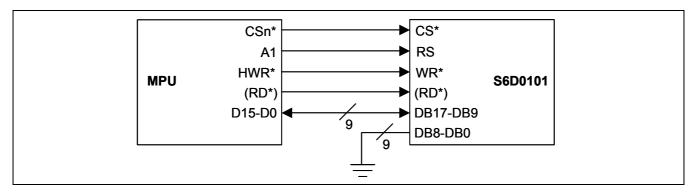

#### SYSTEM INTERFACE

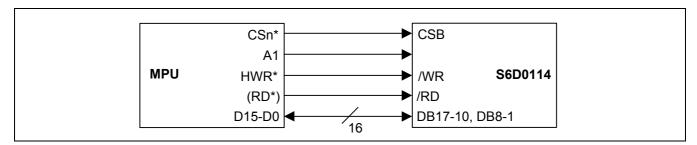

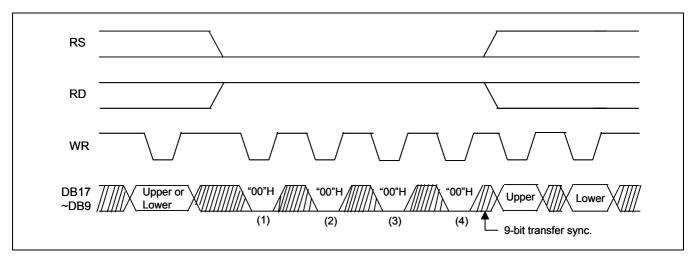

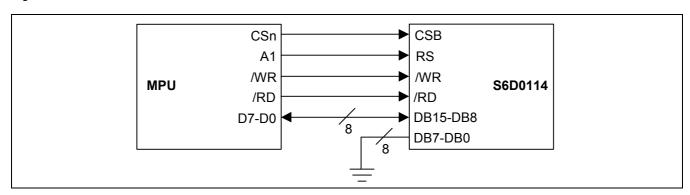

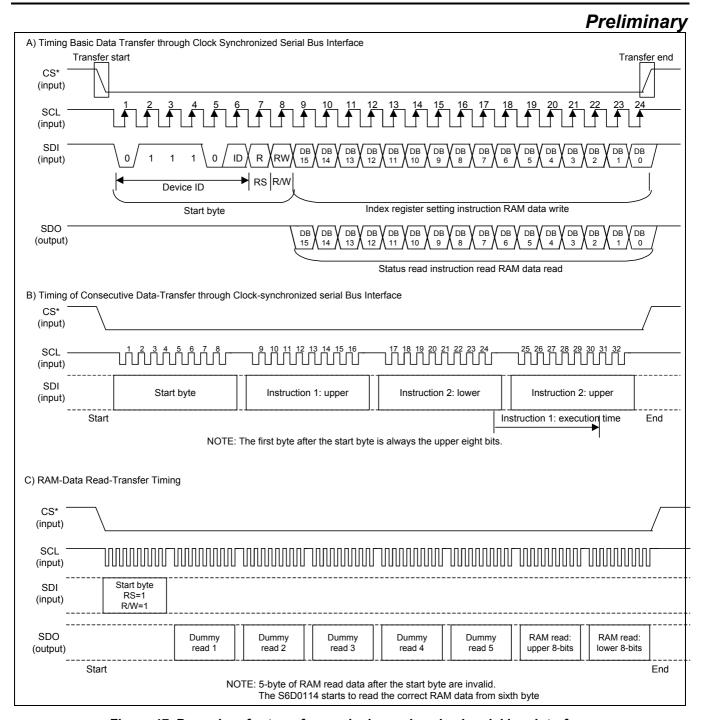

The S6D0114 has five high-speed system interfaces: an 80-system 18-/16-/9-/8-bit bus, a 68-system 18-/16-/9-/8-bit bus, and a serial interface (SPI: Serial Peripheral Interface). The IM3-0 pins select the interface mode.

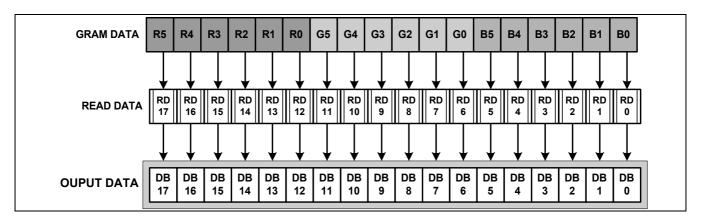

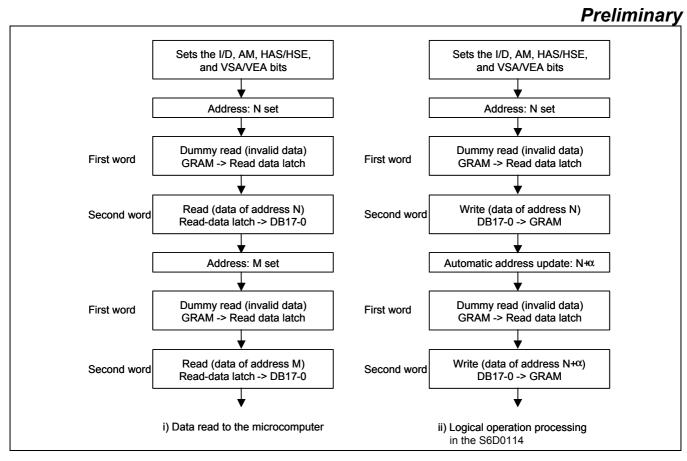

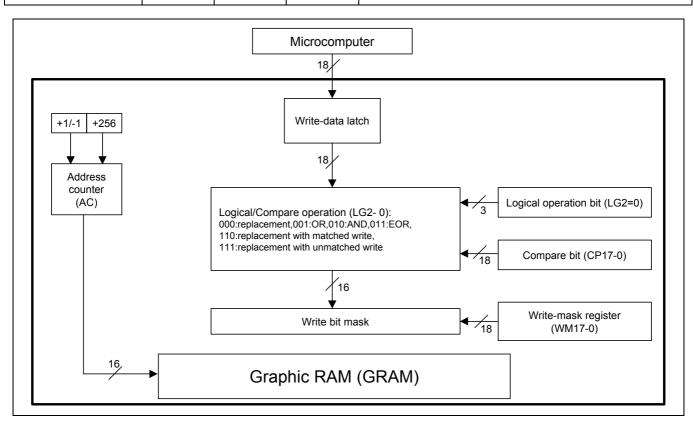

The S6D0114 has three 18-bit registers: an index register (IR), a write data register (WDR), and a read data register (RDR). The IR stores index information for control register and GRAM. The WDR temporarily stores data to be written into control register and GRAM. The RDR temporarily stores data read from GRAM. Data written into the GRAM from MPU is initially written to the WDR and then written to the GRAM automatically. Data is read through the RDR when reading from the GRAM, and the first read data is invalid and the second and the following data are valid. When a logic operation is performed inside of the S6D0114 by using the display data stored in the GRAM and the data written from the MPU, the data read through the RDR is used. Accordingly, the MPU does not need to read data twice or to fetch the read data into the MPU. This enables high-speed processing.

Execution time for instruction, except oscillation start, is 0-clock cycle so that instructions can be written in succession.

| SYSTEM                        | R/W<br>/WR | E<br>/RD             | RS | Operations                                     |

|-------------------------------|------------|----------------------|----|------------------------------------------------|

|                               | 0          | 1                    | 0  | Write index to IR                              |

| 68 1 1 0 Read internal status |            | Read internal status |    |                                                |

| 00                            | 0          | 1                    | 1  | Write to control register and GRAM through WDR |

|                               | 1          | 1                    | 1  | Read from GRAM through RDR                     |

|                               | 0          | 1                    | 0  | Write index to IR                              |

| 90                            | 1          | 0                    | 0  | Read internal status                           |

| 80                            | 0          | 1                    | 1  | Write to control register and GRAM through WDR |

|                               | 1          | 0                    | 1  | Read from GRAM through RDR                     |

Table 10. Register Selection (18-/16-/9-/8- Parallel Interface)

| Table 11. | CSB/VI D | lennia | (GRAM  | undata | control) |

|-----------|----------|--------|--------|--------|----------|

| Table 11. | CODIVLD  | Siunai | IGRAIN | ubuate | CONTROL  |

| CSB | VLD | Operation                                                |

|-----|-----|----------------------------------------------------------|

| 0   | 0   | Data is written to GRAM, GRAM address is updated         |

| 1   | 0   | Data is not written to GRAM, GRAM address is not updated |

| 0   | 1   | Data is not written to GRAM, GRAM address is updated     |

| 1   | 1   | Data is not written to GRAM, GRAM address is not updated |

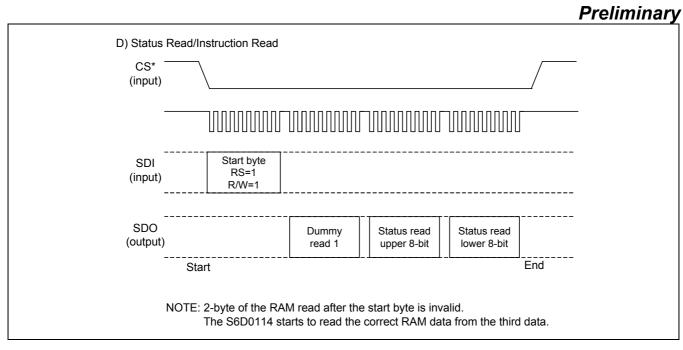

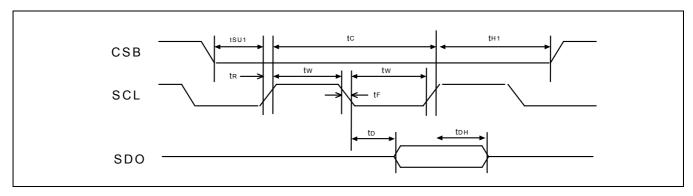

Table 12. Register Selection (Serial Peripheral Interface)

| R/W bit | RS bit | Operation                                           |

|---------|--------|-----------------------------------------------------|

| 0       | 0      | Write index to IR                                   |

| 1       | 0      | Read internal status                                |

| 0       | 1      | Write data to control register and GRAM through WDR |

| 1       | 1      | Read data from GRAM through RDR                     |

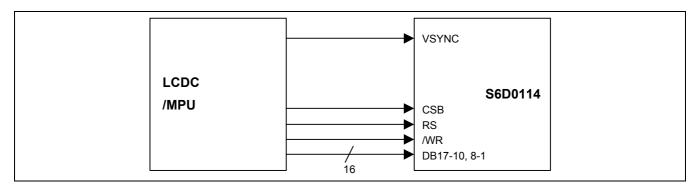

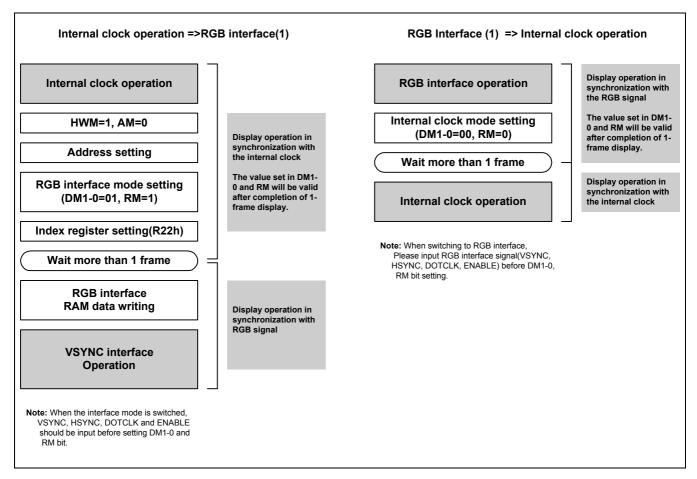

#### **EXTERNAL INTERFACE (RGB-I/F, VSYNC-I/F)**

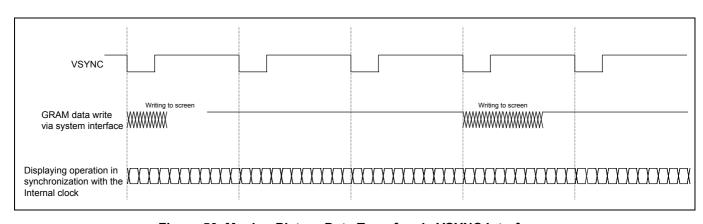

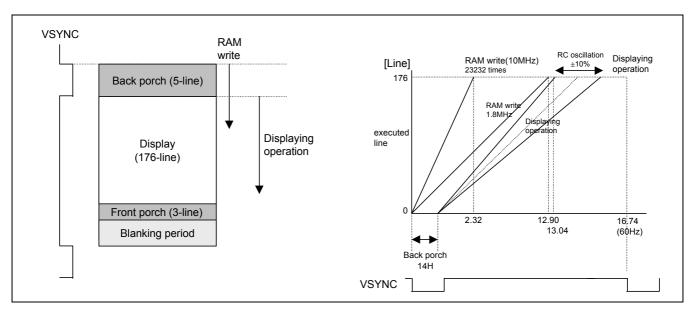

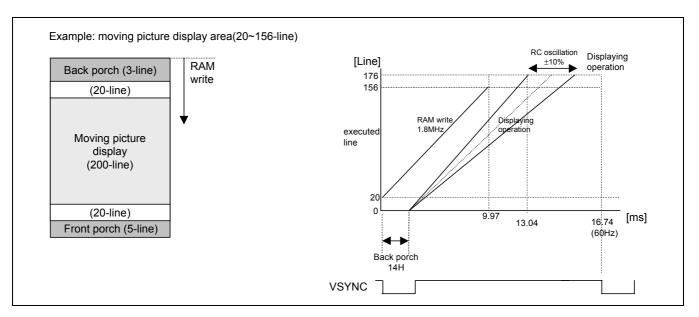

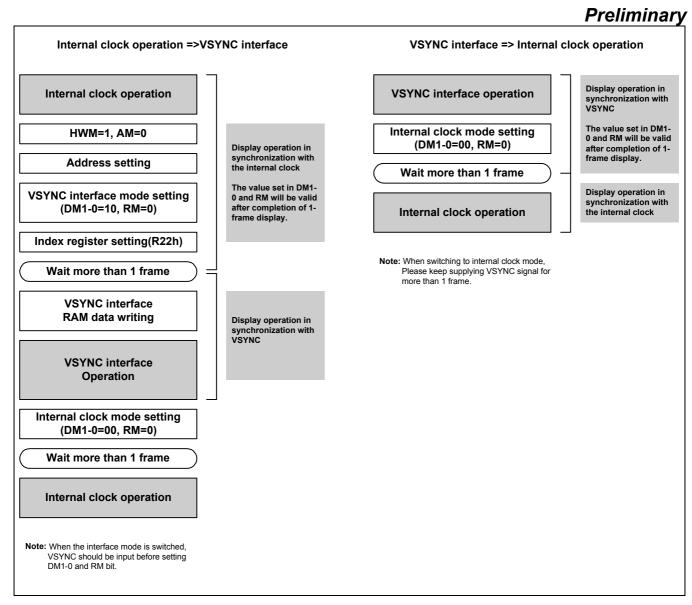

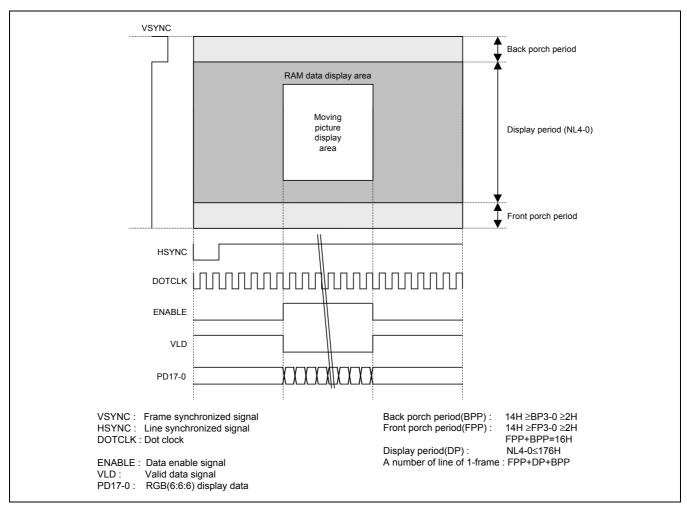

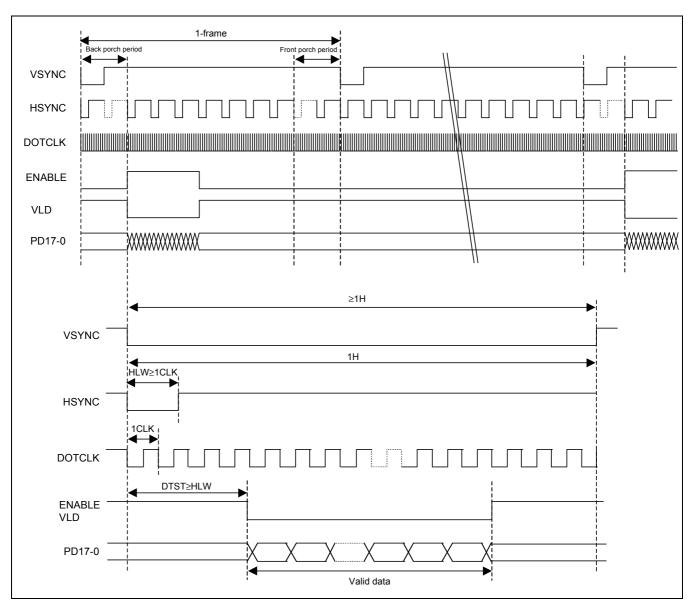

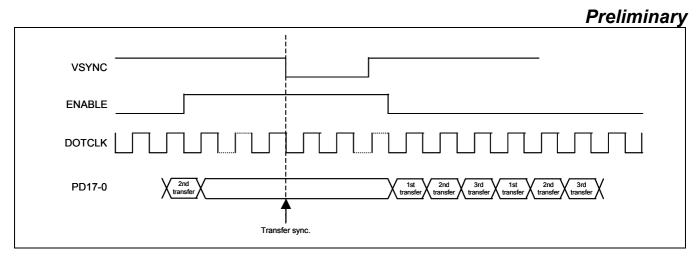

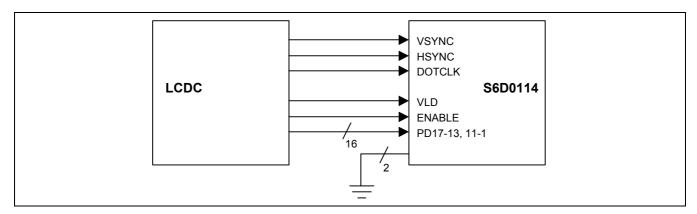

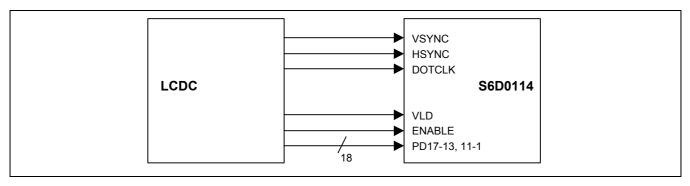

The S6D0114 incorporates RGB and VSYNC interface as external interface for motion picture display. When the RGB interface is selected, the synchronization signals (VSYNC, HSYNC, and DOTCLK) are available for display. The RGB data for display (PD17-0) are written according to enable signal (ENABLE) and data valid signal (VLD) in synchronization with VSYNC, HSYNC, and DOTCLK signal. This allows flicker-free updating of the screen. When the VSYNC interface is selected, internal operation is normally synchronized with internal clock except operation related to frame synchronization: It is synchronized with the VSYNC signal. The data for display are written to GRAM via conventional system interface. There are some limitations on the timing and methods for writing to GRAM in VSYNC interface. See the section on the external display interface.

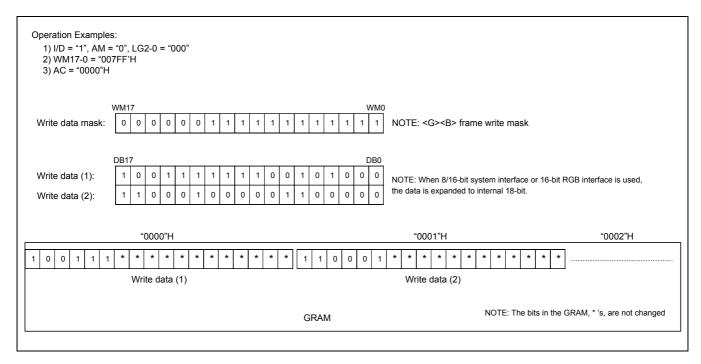

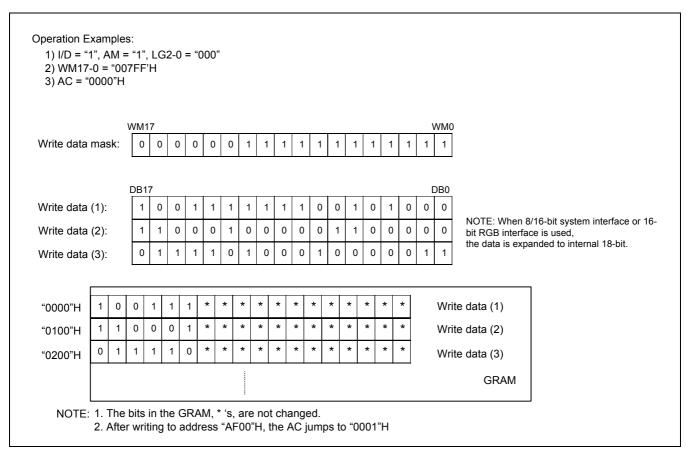

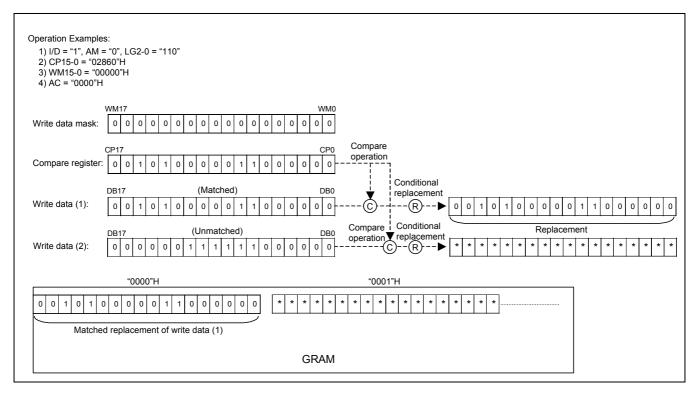

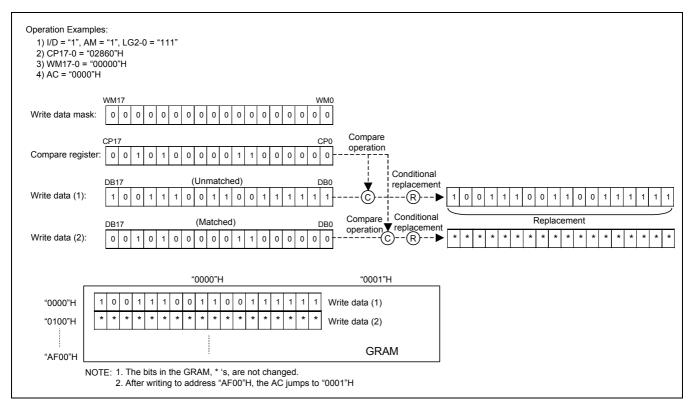

#### **BIT OPERATION**

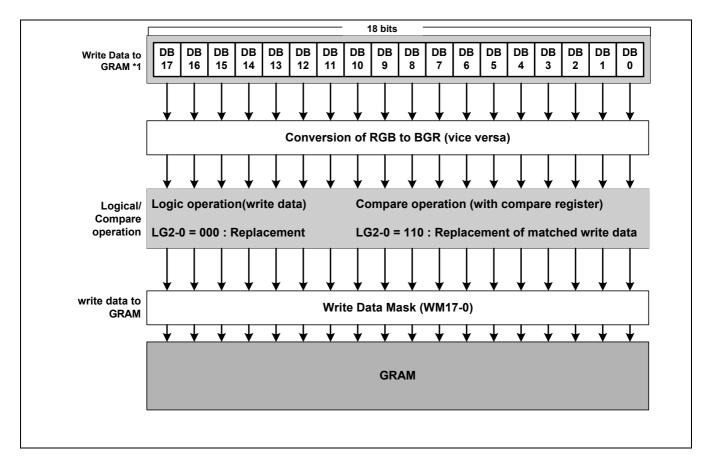

The S6D0114 supports the following functions: a write data mask function that selects and writes data to GRAM in bit unit, a logic operation function that performs logic operations or conditional determination on the display data set in GRAM and writes to GRAM. These functions can greatly reduce the processing loads of the MPU graphics software and can rewrite the display data in the GRAM at high speed. For details, see the Graphics Operation Function section.

#### **ADDRESS COUNTER (AC)**

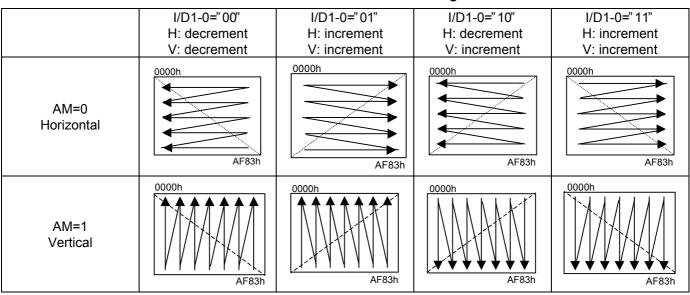

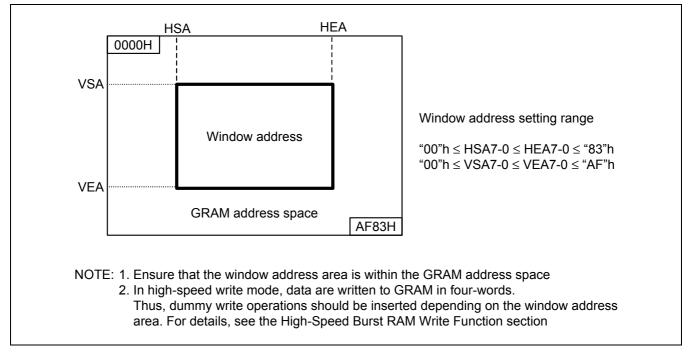

The address counter (AC) assign address to GRAM. When an address-set-instruction is written to the IR, the address information is sent from IR to AC. After writing to the GRAM, the address value of AC is automatically increased/decreased by 1 according to ID1-0 bit of control register. After reading data from GRAM, the AC is not updated. A window address function allows data to be written only to a window area specified by GRAM.

#### **GRAPHICS RAM (GRAM)**

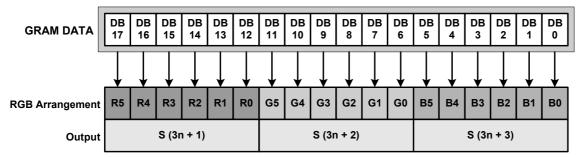

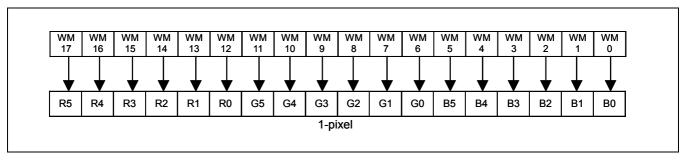

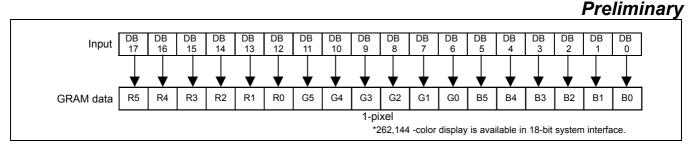

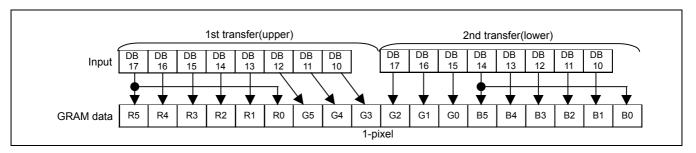

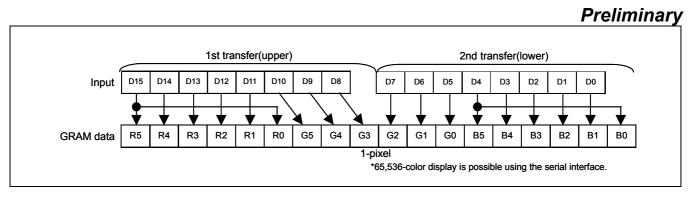

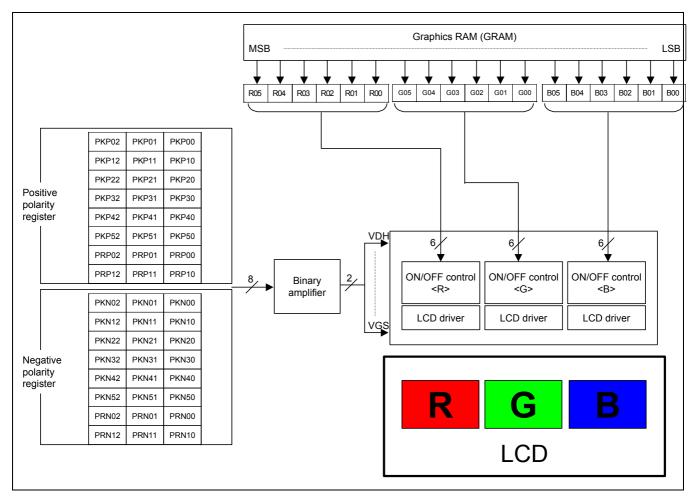

The graphics RAM (GRAM) has 18-bits/pixel and stores the bit-pattern data for 132-RGB x 176-dot display.

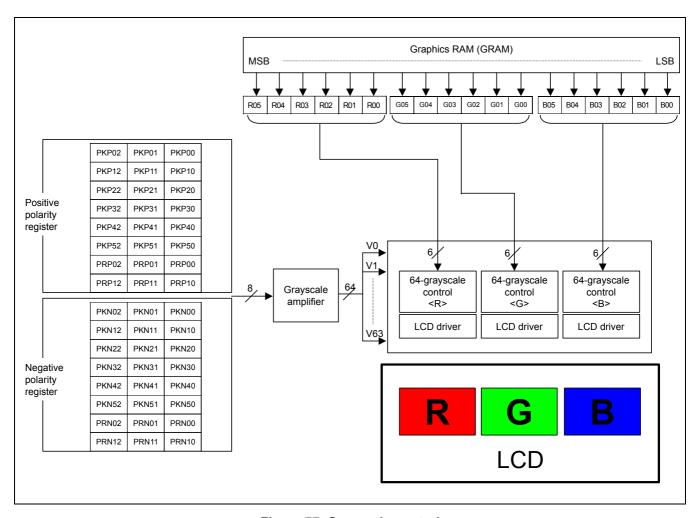

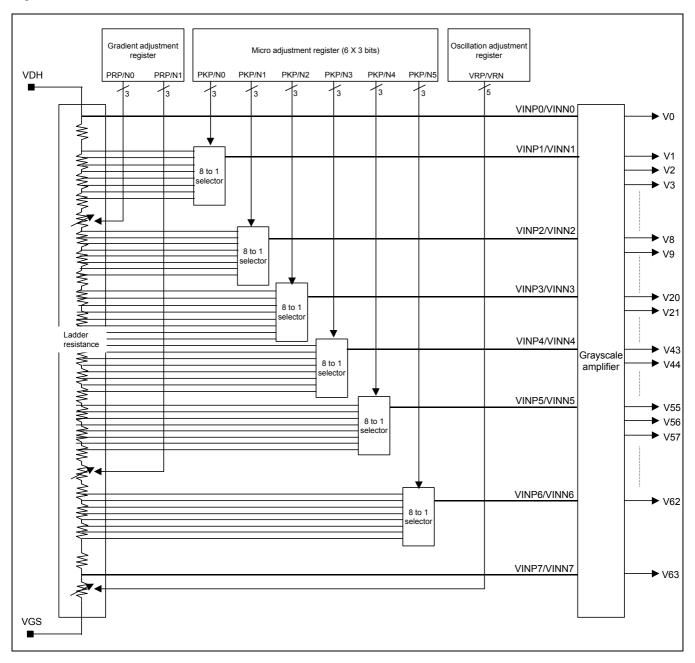

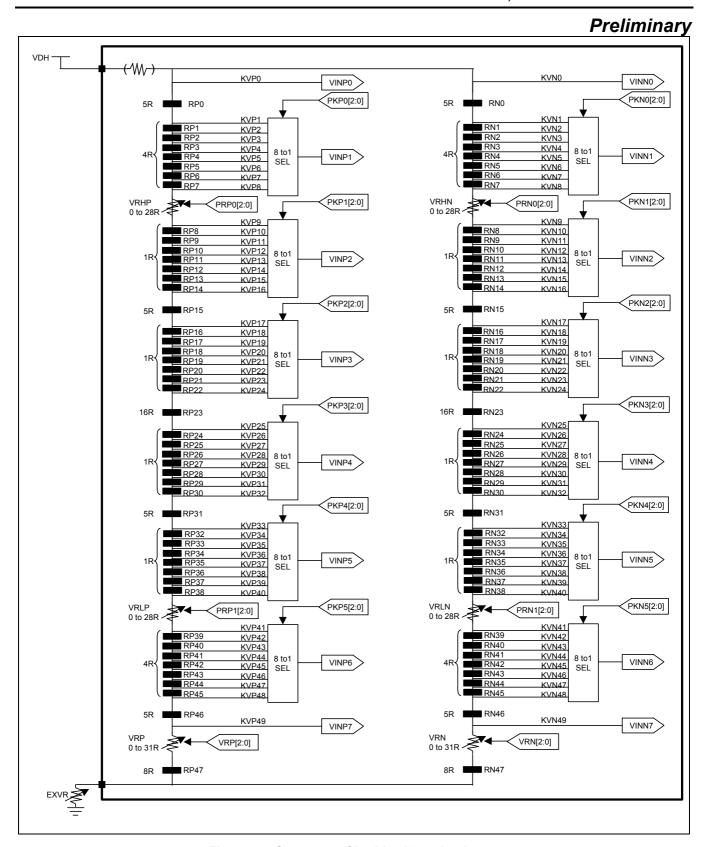

#### **GRAYSCALE VOLTAGE GENERATOR**

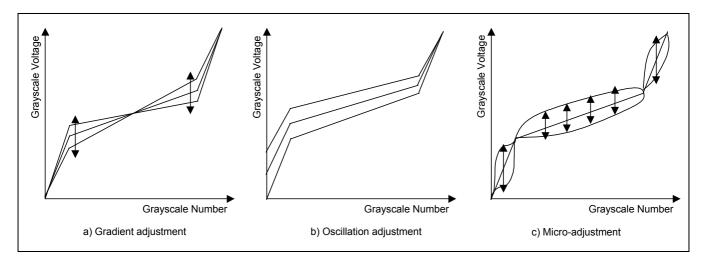

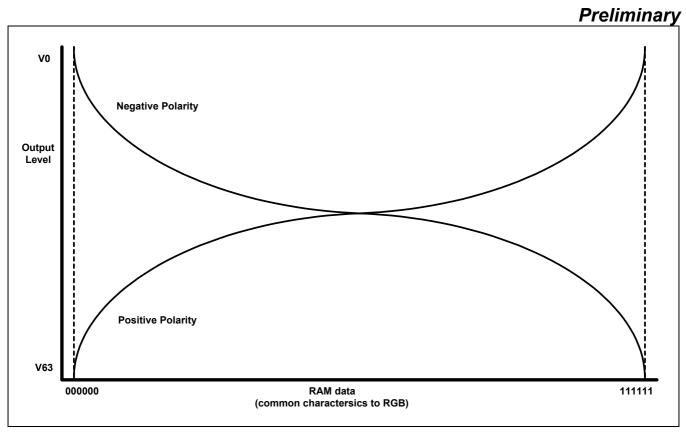

The grayscale voltage circuit generates a certain voltage level that is specified by the grayscale  $\Upsilon$ -adjusting resistor for LCD driver circuit. By use of the generator, 262,144 colors can be displayed at the same time. For details, see the  $\Upsilon$ -adjusting resistor section.

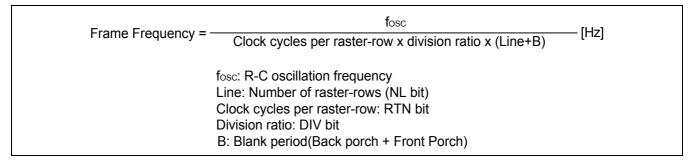

#### **TIMING GENERATOR**

The timing generator generates timing signals for the operation of internal circuits such as GRAM. The GRAM read timing for display and the internal operation timing for MPU access is generated separately to avoid interference with one another. Several important timing signals can be monitored via signal monitoring pin (M, FLM, CL1, EQ, DISPTMG).

#### **OSCILLATION CIRCUIT (OSC)**

The S6D0114 can provide R-C oscillation simply through the addition of an external oscillation-resistor between the OSC1 and OSC2 pin. The appropriate oscillation frequency for operating voltage, display size, and frame frequency

can be obtained by adjusting the external-resistor value. Clock pulse can also be supplied externally. Since R-C oscillation stops during the standby mode, current consumption can be reduced. For details, see the Oscillation Circuit section.

#### **SOURCE DRIVER CIRCUIT**

The liquid crystal display source driver circuit consists of 396 drivers (S1 to S396).

Display pattern data is latched when 396-bit data has arrived. The latched data then enables the source drivers to generate drive waveform outputs. The SS bit can change the shift direction of 396-bit data by selecting an appropriate direction for the device-mounted configuration.

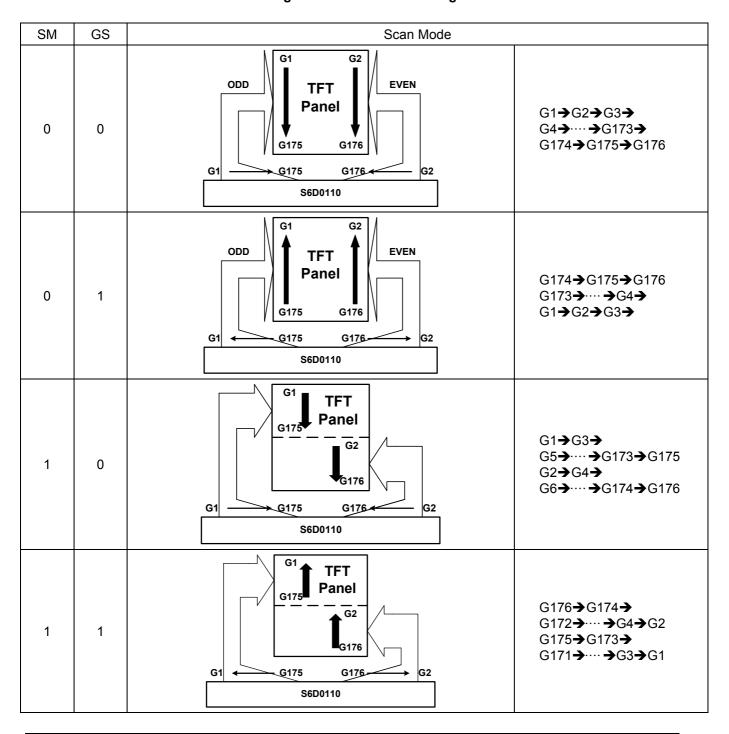

#### **GATE DRIVER CIRCUIT**

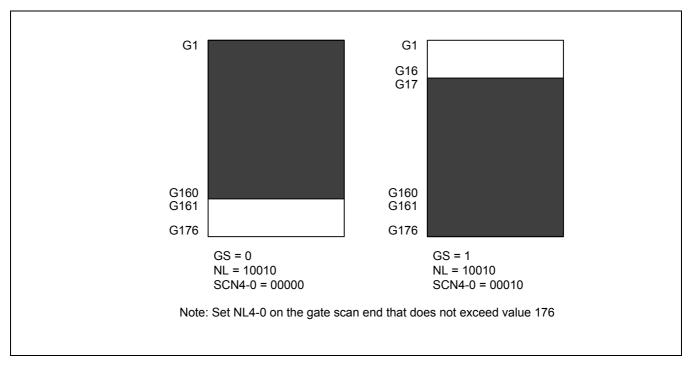

The liquid crystal display gate driver circuit consists of 178 gate drivers (G0 to G177).

The VGH or Vgoff level is output by the signal from the gate control circuit. G0 and G177 are IC maker's test pins.

#### SYSTEM/RGB INTERFACE AND GRAM ADDRESS SETTING

# **GRAM ADDRESS SETTING (SS="0")**

When SS bit is 0 (source output shift direction: right) and BGR bit is 0 (RGB sequence: right) that can be set in R01h register, GRAM address is set as follows:

Table 13. GRAM address (SS="0")

| S/G C | Output | S1         | S2   | S3      | S4       | S5  | Se Se   | S7         | S8   | 68      | S10      | S11  | S12     | <br> | S385       | S386 | S387    | S388     | S389 | S390    | S391       | S392 | S393    | S394       | S395 | S396    |

|-------|--------|------------|------|---------|----------|-----|---------|------------|------|---------|----------|------|---------|------|------------|------|---------|----------|------|---------|------------|------|---------|------------|------|---------|

| GS=0  | GS=1   | DB<br>18   |      | DB<br>0 | DB<br>18 |     | DB<br>0 | DB<br>18   |      | DB<br>0 | DB<br>18 |      | DB<br>0 |      | DB<br>18   |      | DB<br>0 | DB<br>18 |      | DB<br>0 | DB<br>18   |      | DB<br>0 | DB<br>18   |      | DB<br>0 |

| G1    | G176   |            | 000  |         |          | 001 |         |            | 0002 |         |          | 0003 |         | <br> |            | 080  |         |          | 081  |         |            | 082  |         |            | 083  |         |

| G2    | G175   | "0         | 100  | "H      | "0       | 101 | "H      | "(         | 102  | "Н      | "0       | 103  | "H      | <br> | "0         | 180' | "H      | "0       | 181  | "H      | "0         | 182  | "H      | "0         | 183  | "Н      |

| G3    | G174   | "0         | 200  | "H      | "0       | 201 | "H      | "(         | 202  | :"H     | "0       | 203  | "H      | <br> | "0         | 280' | "H      | "0:      | 281  | "H      | "0         | 282  | "H      | "0:        | 283  | "Н      |

| G4    | G173   | "0         | 300  | "H      | "0       | 301 | "H      | "(         | 302  | "H      | "C       | 303  | "H      | <br> | "0         | 380' | "H      | "0       | 381  | "H      | "0         | 382  | "H      | "0:        | 383  | "Н      |

| G5    | G172   | "0         | 400  | "H      | "0       | 401 | "H      | "(         | 402  | "H      | "0       | 403  | "H      | <br> | "0         | 480' | "H      | "0       | 481  | "H      | "0         | 482  | "H      | "0         | 483  | "Н      |

| G6    | G171   | "0         | 500  | "H      | "0       | 501 | "H      | "(         | 502  | "H      | "0       | 503  | "H      | <br> | "0         | 580' | "H      | "0       | 581  | "H      | "0         | 582  | "H      | "0         | 583  | "Н      |

| G7    | G170   | "0         | 600  | "H      | "0       | 601 | "H      | "(         | 602  | !"H     | "0       | 603  | "H      | <br> | "0         | 680' | "H      | "0       | 681  | "H      | "0         | 682  | "H      | "0         | 683  | "Н      |

| G8    | G169   | "0         | 700  | "H      | "0       | 701 | "H      | "(         | 702  | :"H     | "0       | 703  | "H      | <br> | "0         | 780' | "H      | "0       | 781  | "H      | "0         | 782  | "H      | "0         | 783  | "Н      |

| G9    | G168   | <b>"</b> O | 800  | "H      | "0       | 801 | "H      | "          | 802  | :"H     | "0       | 803  | "H      | <br> | "0         | 880' | "H      | "0       | 881  | Н       | <u>"</u>   | 882  | Ï,      | "Ö         | 883  | "H      |

| G10   | G167   | <u>"</u> O | 900  | "H      | "0       | 901 | "H      | "          | 902  | :"H     | "0       | 903  | "H      | <br> | "0         | 980' | "H      | "0       | 981  | Ï,      | <u>"</u>   | 982  | Ï,      | <b>"</b> O | 983  | "H      |

| G11   | G166   | "0         | A00  | "H      | "0.      | A01 | "H      | <u>"</u>   | A02  | ?"H     | "0       | A03  | "H      | <br> | <b>"</b> O | A80  | "H      | "0,      | A81  | "H      | "0         | A82  | "H      | <b>"</b> O | A83  | ;"H     |

| G12   | G165   | "0         | B00  | "H      | "0       | B01 | "H      | <u>"</u>   | B02  | ?"H     | "0       | B03  | "H      | <br> | <u>"</u>   | B80  | "H      | "0       | B81  | "H      | <b>"</b> 0 | B82  | "H      | "OI        | B83  | ;"H     |

| G13   | G164   | "0         | C00  | "Н      | "0       | C01 | "H      | <b>"</b> C | C02  | 2"H     | "0       | C03  | "H      | <br> | <b>"</b> O | C80  | "H      | "0       | C81  | "H      | "0         | C82  | "H      | "00        | C83  | ;"H     |

| G14   | G163   | "0         | D00  | "H      | "0       | D01 | "H      | <b>"</b> C | D02  | 2"H     | "0       | D03  | "H      | <br> | "0         | D80  | "H      | "01      | D81  | "H      | "0         | D82  | "H      | 10"        | D83  | ;"H     |

| G15   | G162   | "0         | E00  | "H      | "0       | E01 | "H      | "          | E02  | 2"H     | "0       | E03  | "H      | <br> | "0         | E80  | "H      | "0       | E81  | "H      | "0         | E82  | "H      | "OI        | E83  | ;"H     |

| G16   | G161   | "0         | F00  | "H      | "0       | F01 | "H      | "          | F02  | 2"H     | "0       | F03  | "H      | <br> | "0         | F80  | "H      | "0       | F81  | "H      | "0         | F82  | "H      | "01        | F83  | /"Н     |

| G17   | G160   | "1         | 000  | "H      | "1       | 001 | "H      | "          | 002  | "H      | "1       | 003  | "H      | <br> | "1         | 080  | "H      | "1       | 081  | "H      | "1         | 082  | "H      | "10        | 083  | ."H     |

| G18   | G159   | "1         | 100  | "H      | "1       | 101 | "H      | =          | 102  | :"H     | "1       | 103  | "H      | <br> | "1         | 180' | "H      | "1       | 181  | "H      | "1         | 182  | "H      | "1         | 183  | "Н      |

| G19   | G158   | "1         | 200  | "H      | "1       | 201 | "H      | =          | 202  | :"H     | "1       | 203  | "Н      | <br> | "1         | 280' | "H      | "1:      | 281  | "H      | "1         | 282  | "H      | "1:        | 283  | "Н      |

| G20   | G157   | "1         | 300  | "H      | "1       | 301 | "H      | =          | 302  | :"H     | "1       | 303  | "H      | <br> | "1         | 380' | "H      | "1       | 381  | Ţ.      | "1         | 382  | Ţ.      | "1:        | 383  | ."H     |

| į     | į      |            | į    |         |          | į   |         |            | į    |         |          | į    |         |      |            | į    |         |          | į    |         |            | į    |         |            | į    |         |

| G169  | G168   | "A         | 800  | "H      | "A       | 801 | "H      | "/         | 802  | 2"H     | "/       | 803  | "H      | <br> | "A         | .880 | "H      | "A       | 881  | "H      | "A         | 880  | "H      | "A         | 883  | ,"H     |

| G170  | G167   | "A         | 900  | "H      | "A       | 901 | "H      | "/         | 902  | 2"H     | "₽       | 903  | "H      | <br> | "A         | 980  | "H      | "А       | 981  | "H      | "A         | 980  | "H      | "A         | 983  | ,"H     |

| G171  | G166   | "A         | A00  | "Н      | "A       | A01 | "H      | "/         | A02  | 2"H     | "Α       | A03  | "Н      | <br> | "A         | A80  | "H      | "A.      | A81  | "H      | "A         | A80  | "H      | "A         | A83  | ;"H     |

| G172  | G165   | "A         | B00  | "Н      | "A       | B01 | "H      | "/         | B02  | 2"H     | "Α       | B03  | "Н      | <br> | "A         | B80  | "H      | "А       | B81  | "H      | "A         | B80  | "H      | "A         | B83  | 3"H     |

| G173  | G164   | "A         | .C00 | "Н      | "A       | C01 | "H      | "/         | C02  | 2"H     | "Α       | C03  | "Н      | <br> | "A         | C80  | "H      | "A       | C81  | "H      | "A         | C80  | "H      | "A         | C83  | 3"H     |

| G174  | G163   | "A         | D00  | "Н      | "A       | D01 | "H      | "/         | D02  | 2"H     | "A       | D03  | "H      | <br> | "A         | D80  | "H      | "A       | D81  | "H      | "A         | D80  | "H      | "Al        | D83  | 3"H     |

| G175  | G162   | "A         | E00  | "H      | "A       | E01 | "H      | "/         | E02  | 2"H     | "Α       | E03  | "H      | <br> | "A         | E80  | "H      | "A       | E81  | "H      | "A         | E80  | "H      | "A         | E83  | ;"H     |

| G176  | G161   | "A         | F00  | "H      | "A       | F01 | "H      | "/         | F02  | 2"H     | "Д       | F03  | "H      | <br> | "A         | F80  | "H      | "Ā       | F81  | "H      | "A         | F80  | "H      | "A         | F83  | ;"H     |

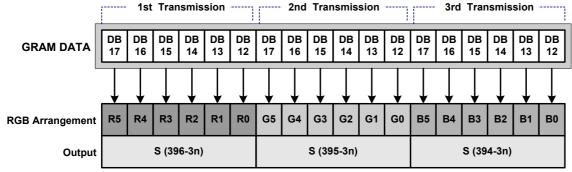

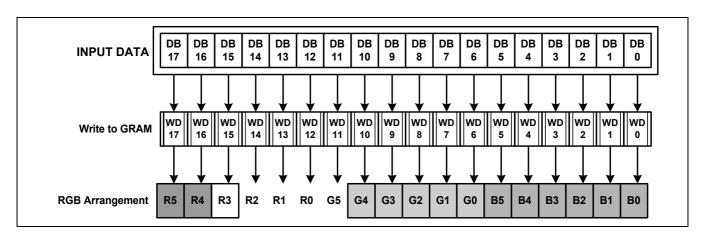

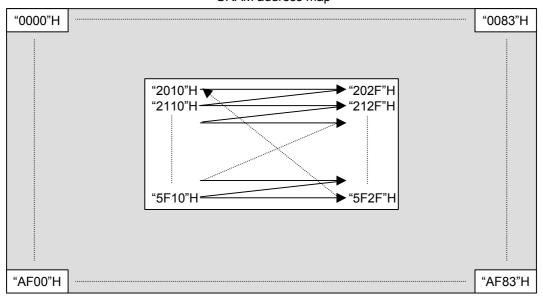

Data fetch from GRAM for display when SS=0 is shown in the following figure.

#### **SYSTEM INTERFACE**

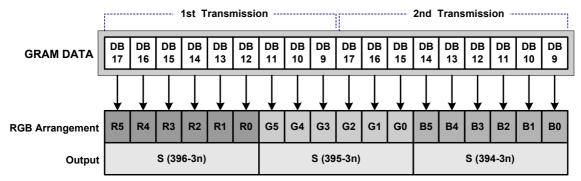

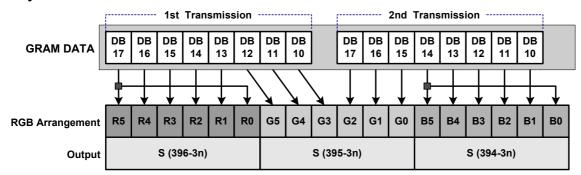

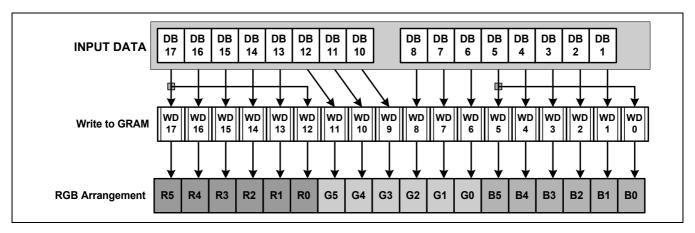

#### 80-system 18-bit interface

Note: n= lower 8 byte of address (0 to 175)

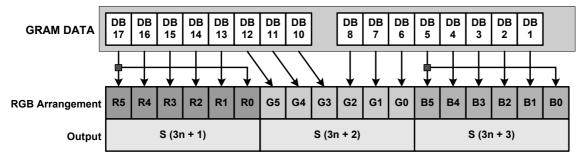

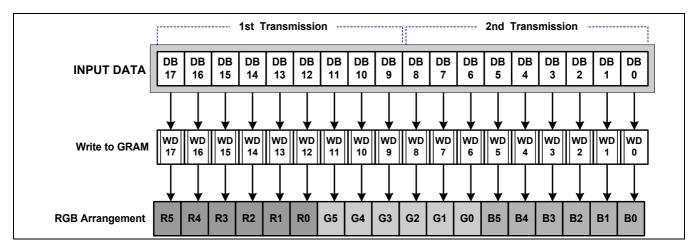

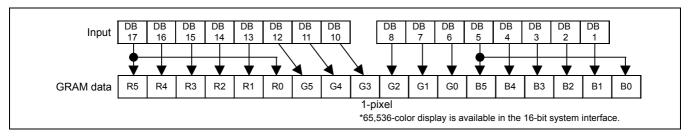

#### 80-system 16-bit interface

Note: n= lower 8 byte of address (0 to 175)

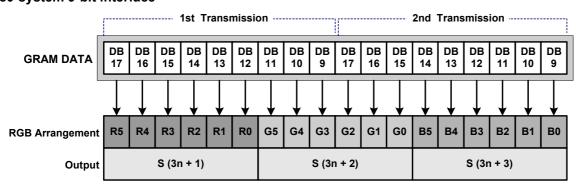

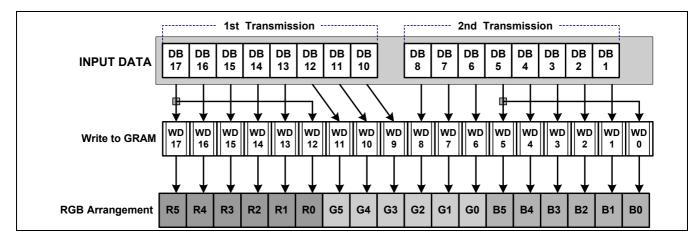

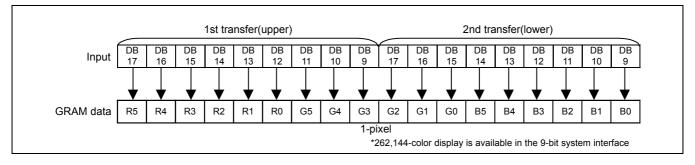

#### 80-system 9-bit interface

Note: n= lower 8 byte of address (0 to 175)

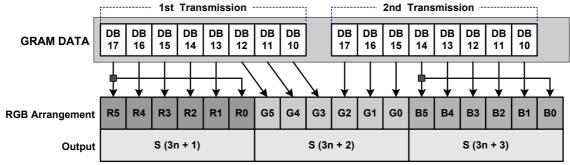

#### 80-system 8-bit interface/SPI

Note: n= lower 8 byte of address (0 to 175)

#### **RGB INTERFACE**

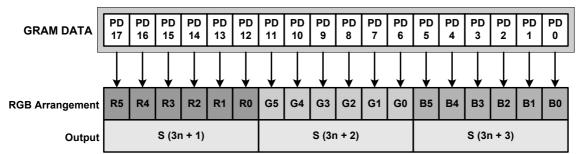

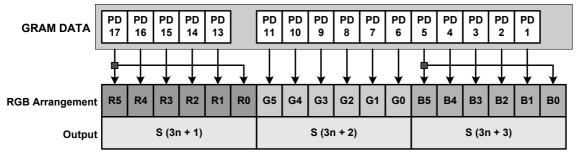

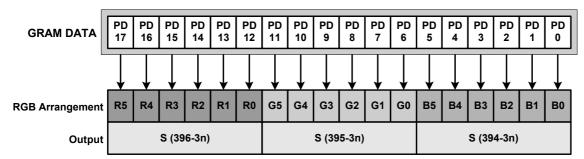

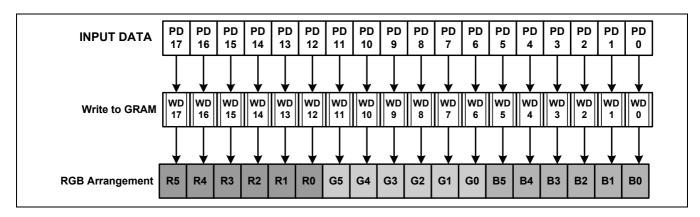

#### 18-bit RGB interface

Note: n= lower 8 byte of address (0 to 175)

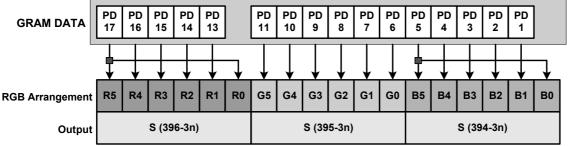

#### 16-bit RGB interface

Note: n= lower 8 byte of address (0 to 175)

#### 6-bit RGB interface

Note: n= lower 8 byte of address (0 to 175)

# **GRAM ADDRESS SETTING (SS="1")**

When SS bit is 1 (source output shift direction: reversed) and BGR bit is 1 (RGB sequence: reversed) that can be set in R01h register, GRAM address is set as follows:

Table 14. GRAM address (SS="1")

| S/G C | Output | S1         | S2  | S3      | S4       | S5  | 98      | S7       | S8   | 68      | S10      | S11  | S12     | <br> | S385     | S386 | S387    | S388       | S389 | 8390    | S391       | S392 | S393    | S394       | S395 | S396    |

|-------|--------|------------|-----|---------|----------|-----|---------|----------|------|---------|----------|------|---------|------|----------|------|---------|------------|------|---------|------------|------|---------|------------|------|---------|

| GS=0  | GS=1   | DB<br>18   |     | DB<br>0 | DB<br>18 |     | DB<br>0 | DB<br>18 |      | DB<br>0 | DB<br>18 |      | DB<br>0 |      | DB<br>18 |      | DB<br>0 | DB<br>18   |      | DB<br>0 | DB<br>18   |      | DB<br>0 | DB<br>18   |      | DB<br>0 |

| G1    | G176   |            | 083 |         |          | 082 |         |          | 081  |         | _        | 080  |         | <br> |          | 003  |         | _          | 002  |         |            | 001  |         |            | 000  |         |

| G2    | G175   | "0         | 183 | "H      | "0       | 182 | "H      | "(       | 181  | "H      | "0       | 180  | "H      | <br> | "0       | 103  | "H      | "0         | 102  | "H      | "0         | 101  | "H      | "0         | 100  | "Н      |

| G3    | G174   | "0         | 283 | "H      | "0       | 282 | "H      | "(       | 281  | "H      | "C       | 280  | "H      | <br> | "0       | 203  | "H      | "0         | 202  | "H      | "0         | 201  | "H      | "0         | 200  | "H      |

| G4    | G173   | "0         | 383 | "H      | "0       | 382 | "H      | "(       | 381  | "H      | "0       | 380  | "H      | <br> | "0       | 303  | "H      | "0         | 302  | "H      | "0         | 301  | "H      | "0         | 300  | "H      |

| G5    | G172   | "0         | 483 | "H      | "0       | 482 | "H      | "(       | )481 | "H      | "0       | )480 | "H      | <br> | "0       | 403' | "H      | "0         | 402' | "H      | "0         | 401  | "H      | "0         | 400  | "H      |

| G6    | G171   | "0         | 583 | "H      | "0       | 582 | "H      | "(       | )581 | "H      | "0       | 580  | "H      | <br> | "0       | 503  | "H      | "0         | 502  | "H      | "0         | 501  | "H      | "0         | 500  | "H      |

| G7    | G170   | "0         | 683 | "H      | "0       | 682 | "H      | "(       | 681  | "H      | "0       | 0880 | "H      | <br> | "0       | 603  | "H      | "0         | 602  | "H      | "0         | 601  | "H      | "0         | 600  | "H      |

| G8    | G169   | "0         | 783 | "H      | "0       | 782 | "H      | "(       | 781  | "Н      | "0       | 780  | "Н      | <br> | "0       | 703  | "H      | "0         | 702' | "H      | "0         | 701  | "H      | "0         | 700  | "H      |

| G9    | G168   | "0         | 883 | "H      | "0       | 882 | "H      | "(       | 088  | ΙΗ      | "0       | 0880 | "Н      | <br> | "0       | 803  | "H      | "0         | 802' | "H      | "0         | 801  | "H      | "0         | 800  | "Н      |

| G10   | G167   | "0         | 983 | "H      | "0       | 982 | "H      | "(       | 981  | "H      | "0       | 980  | "H      | <br> | "0       | 903' | "H      | "0         | 902' | "H      | "0         | 901  | "H      | "0         | 900  | "Н      |

| G11   | G166   | "0         | A83 | "H      | "0       | A82 | "H      | "(       | A81  | "H      | "0       | )A80 | "H      | <br> | "0.      | A03  | T,      | "0,        | A02  | T,      | "0.        | A01  | Ή.      | <b>"</b> O | 400  | "H      |

| G12   | G165   | "0         | B83 | "H      | "0       | B82 | "H      | "(       |      |         | "0       | B80  | "Н      | <br> | "0       | B03  | Ţ,      | "0         | B02  | Ţ,      | "0         | B01  | Τ.      | <b>"</b> O | B00  | "H      |

| G13   | G164   | <b>"</b> 0 | C83 | "H      | "0       | C82 | "H      | "0       | C81  | "H      | "0       | C80  | "H      | <br> | °        | C03  | "H      | "          | C02  | "H      | °          | C01  | "H      | <u>"</u>   | C00  | )"Н     |

| G14   | G163   | <u>"</u>   | D83 | "H      | "0       | D82 | "Н      | "0       | D81  | "H      | "0       | D80  | "H      | <br> | <b>"</b> | D03  | "H      | <b>"</b> O | D02  | "H      | <b>"</b>   | D01  | "Н      | <b>"</b> O | D00  | )"Н     |

| G15   | G162   | "0         | E83 | "H      | "0       | E82 | "Н      | "(       | E81  | "H      | "0       | E80  | "Н      | <br> | "0       | E03  | "H      | "0         | E02  | "H      | <b>"</b> 0 | E01  | "H      | "0         | E00  | "H      |

| G16   | G161   | "0         | F83 | "H      | "0       | F82 | "Н      | "(       | )F81 | "H      | "0       | )F80 | "H      | <br> |          | F03  |         | "0         | F02  | "H      | "0         | F01  | "H      | "0         | F00  | "H      |

| G17   | G160   | "1         | 083 | "H      |          | 082 |         | "/       | 081  | "H      | "1       | 080  | "H      | <br> | "1       | 003  | "H      | "1         | 002  | "H      | "1         | 001  | "H      | "1         | 000  | "H      |

| G18   | G159   | "1         | 183 | "H      | "1       | 182 | "H      | "/       | 181  | "H      | "1       | 180  | "H      | <br> | "1       | 103  | "H      | "1         | 102  | "H      | "1         | 101  | "H      | "1         | 100  | "Н      |

| G19   | G158   | "1         | 283 | "H      | "1       | 282 | "H      | "-       | 281  | "H      | "1       | 280  | "H      | <br> | "1       | 203  | "H      | "1:        | 202  | "H      | "1         | 201  | "H      | "1         | 200  | "H      |

| G20   | G157   | "1         | 383 | "H      | "1       | 382 | "H      | "-       | 381  | "H      | "1       | 380  | "H      | <br> | "1       | 303  | "H      | "1         | 302  | "H      | "1         | 301  | "H      | "1         | 300  | "H      |

| į     | į      |            | į   |         |          | į   |         |          | į    |         |          | į    |         |      |          | į    |         |            | į    |         |            | į    |         |            | į    |         |

| G169  | G168   | "Α         | 883 | "H      | "Α       | 880 | "H      | "/       | \881 | "H      | "/       | A880 | "H      | <br> | "A       | 803  | "H      | "A         | 802  | "H      | "A         | 801  | "H      | "A         | 800  | "Н      |

| G170  | G167   | "Α         | 983 | "H      | "Α       | 980 | "H      | "/       | \981 | "H      | "/       | 1980 | "H      | <br> | "A       | 903  | "H      | "A         | 902  | "H      | "A         | 901  | "H      | "A         | 900  | "H      |

| G171  | G166   | "A         | A83 | "Н      | "A       | A80 | "H      | "/       | A81  | "H      | "∆       | A80  | "H      | <br> | "A       | A03  | "H      | "A         | A02  | "H      | "A         | A01  | "H      | "A         | A00  | )"H     |

| G172  | G165   | "A         | B83 | "Н      | "A       | B80 | "H      | "/       | \B81 | "H      | "∆       | B80  | "Н      | <br> | "A       | B03  | "H      | "A         | B02  | "H      | "A         | B01  | "H      | "A         | B00  | )"H     |

| G173  | G164   | "A         | C83 | "Н      | "A       | C80 | "H      | "/       | C8′  | "Н      | "Α       | C80  | "Н      | <br> | "A       | C03  | "H      | "A         | C02  | "H      | "A         | C01  | "H      | "A         | C00  | )"H     |

| G174  | G163   | "A         | D83 | "Н      | "A       | D80 | "H      | "/       | D8′  | "Н      | "Α       | D80  | "Н      | <br> | "A       | D03  | "H      | "A         | D02  | "H      | "A         | D01  | "H      | "A         | D00  | )"H     |

| G175  | G162   | "A         | E83 | "Н      | "A       | E80 | "H      | "/       | \E81 | "H      | "∆       | E80  | "Н      | <br> | "A       | E03  | "H      | "A         | E02  | "H      | "A         | E01  | "H      | "A         | E00  | )"H     |

| G176  | G161   | "A         | F83 | "H      | "A       | F80 | "H      | "/       | \F81 | "Н      | "∆       | \F80 | "H      | <br> | "A       | F03  | "H      | "A         | F02  | "H      | "A         | F01  | "H      | "A         | F00  | )"H     |

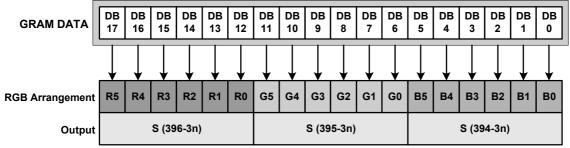

Data fetch from GRAM for display when SS=1 is shown in the following figure.

#### **SYSTEM INTERFACE**

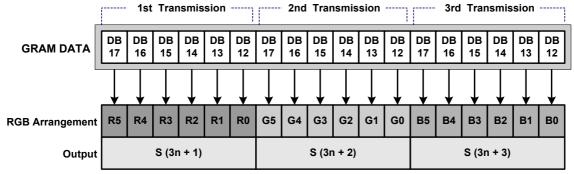

#### 80-system 18-bit interface

Note: n= lower 8 byte of address (0 to 175)

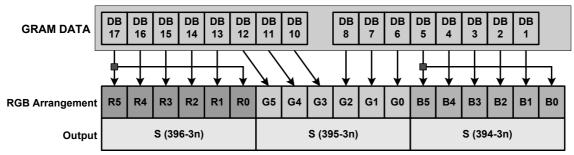

#### 80-system 16-bit interface

Note: n= lower 8 byte of address (0 to 175)

#### 80-system 9-bit interface

Note: n= lower 8 byte of address (0 to 175)

#### 80-system 8-bit interface

Note: n= lower 8 byte of address (0 to 175)

#### **RGB INTERFACE**

#### 18-bit interface

Note: n= lower 8 byte of address (0 to 175)

#### 16-bit interface

Note: n= lower 8 byte of address (0 to 175)

#### 6-bit interface

Note: n= lower 8 byte of address (0 to 175)

#### **INSTRUCTIONS**

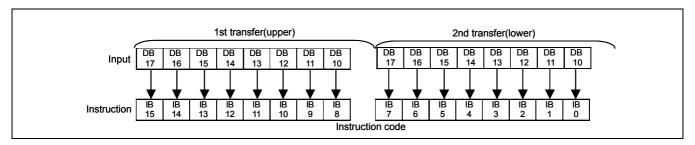

The S6D0114 uses the 18-bit bus architecture. Before the internal operation of the S6D0114 starts, control information is temporarily stored in the registers described below to allow high-speed interfacing with a high-performance microcomputer. The internal operation of the S6D0114 is determined by signals sent from the microcomputer. These signals, which include the register selection signal (RS), the read/write signal (R/W), and the data bus signals (DB17 to DB0), make up the S6D0114 instructions.

There are nine categories of instructions that:

- Specify the index

- Read the status

- Control the display

- Control power management

- Process the graphics data

- Set internal GRAM addresses

- Transfer data to and from the internal GRAM

- Set grayscale level for the internal grayscale palette table

- Interface with the gate driver and power supply IC

Normally, instructions that write data are used the most. However, an auto-update of internal GRAM addresses after each data write can lighten the microcomputer program load. As instructions are executed in 0 cycles, they can be written in succession.

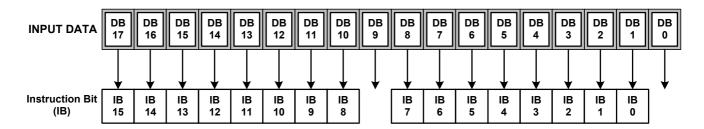

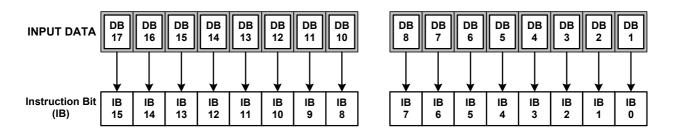

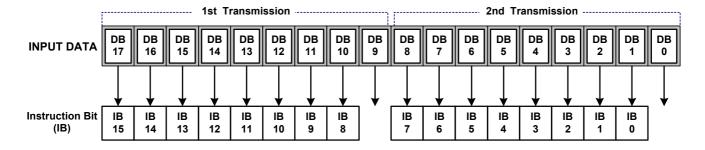

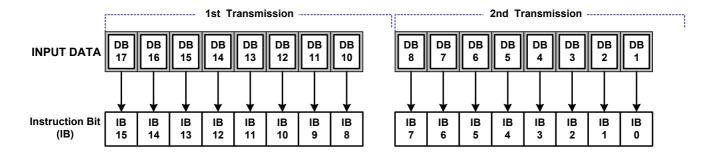

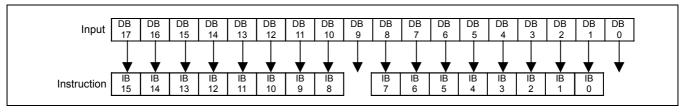

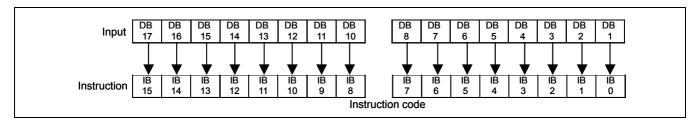

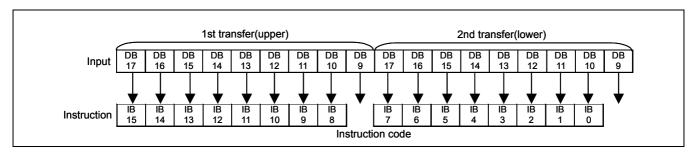

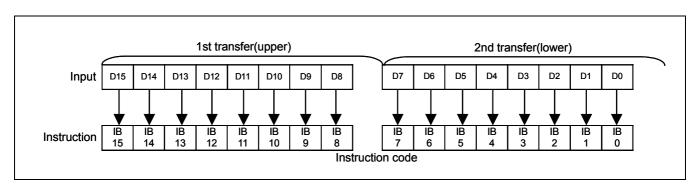

The 16-bit instruction assignment differ from interface-setup (18-/16-/9-/8-/SPI), so instructions should be fetched according to the data format shown below:

#### 80-system 18-bit Interface

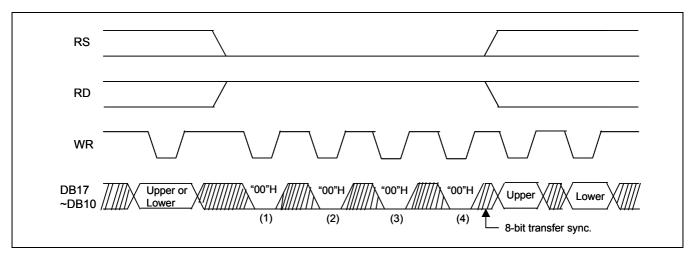

#### 80-system 16-bit Interface

#### 80-system 9-bit Interface

#### 80-system 8-bit Interface/SPI (2-transfer per pixel)

#### **Instruction Table**

#### Table 15. Instruction table 1

| Reg.<br>No | R/W | RS | DB<br>15 | DB<br>14 | DB<br>13 | DB<br>12 | DB<br>11  | DB<br>10  | DB<br>9   | DB<br>8   | DB<br>7   | DB<br>6   | DB<br>5 | DB<br>4   | DB<br>3 | DB<br>2 | DB<br>1 | DB<br>0 | Register Name /<br>Description                                                                                                                                                                                                                                                                               |

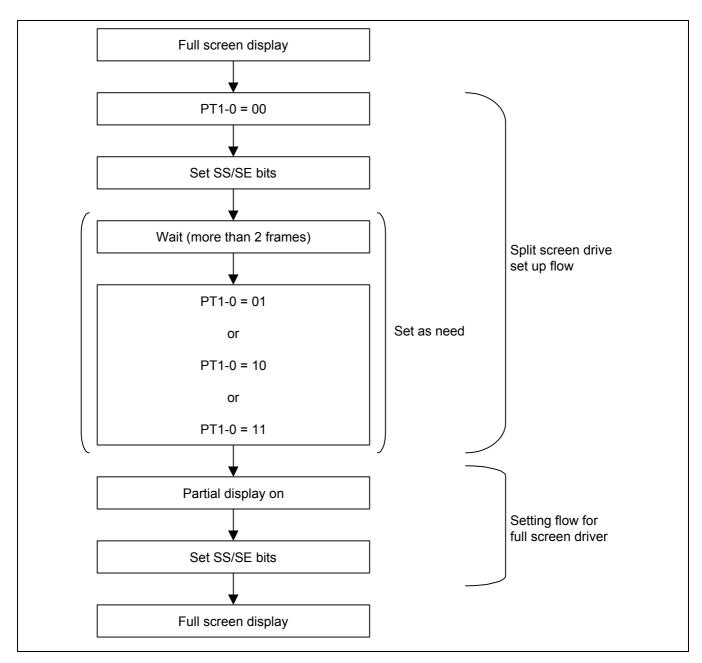

|------------|-----|----|----------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|---------|-----------|---------|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|