# **AS998/A**

# PWM Controller Preliminary Specification

#### **Features**

- Low start-up current 64 μA (Typ)

- Low running current 2 mA (Typ)

- Low power light load mode

- Low power standby when OV is activated

- Extended commercial operating temperature range: 0 to 105°C

- On-board fixed frequency oscillator 100 kHz (Typ)

- Frequency randomizer to reduce EMC emissions

- Dedicated OV shutdown pin

- On-board voltage ramp compensation

- On-board current sensing filtering

- Optional primary side regulation

### **Description**

The AS998/AS998A is an IC intended for use as a PWM controller for switch mode power supplies. The device is particularly suited as a primary side controller for adapter, printer, peripheral, mobile chargers and desktop auxiliary power supplies. The AS998/AS998A is manufactured in BICMOS technology and exhibits very low start-up and operating power. This allows the device to be suitable in applications where stringent standby or Blue Angel criteria are required.

Many of the external functions associated with PWM controllers have been integrated into the AS998/AS998A allowing the external component count to be significantly reduced. Features such as fixed internal oscillator, internal ramp compensation and current filters all reduce the external support components.

The AS998/AS998A has a typical output rise and fall time of 250/210 ns.

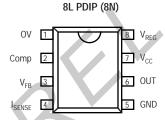

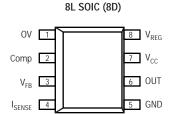

### Pin Configuration - Top View

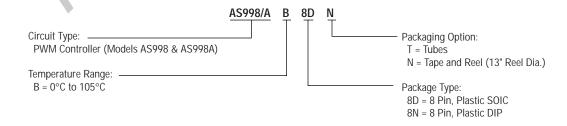

# **Ordering Information**

AS998/AS998A PWM Controller

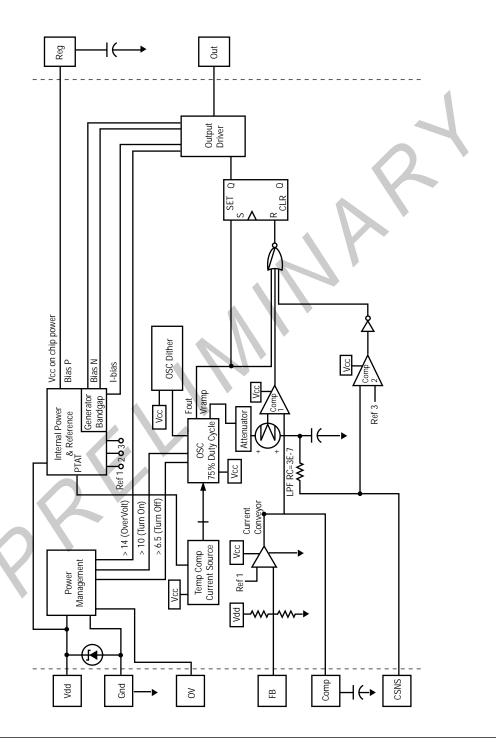

# **Functional Block Diagram**

PWM Controller AS998/AS998A

# **Pin Function Description**

| Pin Number         | Function | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | OV       | Overvoltage pin. The OV input/output function is implemented by an on-chip latch. This pin is driven to the Reg voltage if the on-chip circuitry senses a VDD level greater than the OV threshold (VDDov). This error condition stops the part from generating any more output pulses until VDD has been reduced to the VDDul level and then raised as in a normal power-on sequence.                   |

| OV condidescribed. |          | Alternatively, the OV error condition can be cleared by forcing the OV pin to near ground. The output is immediately enabled following an OV clear function. The OV error condition can also be generated externally by temporarily forcing the OV pin to a voltage greater than the VOV threshold. This will force the part to latch an tion and not generate any more output pulses unless cleared as |

| 2                  | COMP     | Compensation pin. This pin is the output of the error amplifier and can also be used as an input for an optocoupled control signal to the PWM comparator. Generally this pin is connected to a feedback network to FB. If an optocoupler feedback is used, COMP connects to the collector of the common emitter optocoupler, generally with a pull-up resistor to VDD or Reg.                           |

| 3                  | FB       | Feedback pin. Inverting input to the error amplifier. This pin is tied to an internal default divider which will tend to regulate VDD at a nominal 11V.                                                                                                                                                                                                                                                 |

| 4                  | CSNS     | Current sense input. The signal on this pin is fed via a low pass filter to the PWM com-parator. Superimposed on the input to the PWM is a slope compensation ramp derived from the main oscillator.                                                                                                                                                                                                    |

|                    |          | In addition to the above, the current sense signal is connected directly to an over-<br>current comparator that detects an overload condition and immediately terminates the<br>gate drive pulse with a minimum propagation delay.                                                                                                                                                                      |

| 5                  | GND      | Circuit common ground.                                                                                                                                                                                                                                                                                                                                                                                  |

| 6                  | OUT      | Gate drive output. The current source and sink capability of the output buffer is tailored to minimize EMI. When the IC is not running, this pin is held low so a pull down resistor on the FET gate is not required.                                                                                                                                                                                   |

| 7                  | VDD      | Positive supply voltage. An on-board shunt regulator allows this IC to be powered via a simple resistor from a widely varying bias supply.                                                                                                                                                                                                                                                              |

| 0                  |          | The ICs power management block keeps the part in startup current mode while VDD is ramping up until the part turns on at the UVLhigh threshold. The IC then draws the specified supply current while operating unless VDD drops below the UVLlow threshold. If VDD drops below UVLlow, then the part will return to startup current mode.                                                               |

| 8                  | REG      | Voltage regulator. Decoupling pin as required for internal low voltage supply. This pin may be used to source 1mA for the control optocoupler.                                                                                                                                                                                                                                                          |

AS998/AS998A PWM Controller

### **IC Block Diagram Description**

#### **Power Management**

This block contains reference generators and comparators to determine the under-voltage shutdown point, the power-on point, the primary regulation operating point, and the overvoltage shutdown point.

#### Internal Power / Reference

This block includes a course regulator for on-chip power and cascade voltages for HV circuitry, a bandgap for comparator references, a bias current generator, PTAT, BiasP and BiasN.

#### **Temperature Compensated Current Source**

This block generates a constant current as a function of voltage and temperature with no off-chip components.

#### Oscillator

Mirrored currents from the reference block are used to charge a capacitor to the threshold voltage at which point the direction is switched to an opposing 3X mirror to drive the capacitor to a lower threshold value. This generates a 75% duty cycle digital clock to the output latch, and a 100kHz ramp voltage to be used in the feedback control.

#### **Feedback Control**

This block senses one of the various feedback methods to control the output duty cycle. It includes a current sense, a low pass filter, current amplifier, summing amp, and comparators. This block sums the analog ramp from the OSC, sense, and compensation node voltages into a comparator which triggers the falling edge of the PWM clock signal. This provides supply voltage compensation and load regulation to the power converter system.

#### Out\_Drv

A high speed, high current bipolar output stage capable of providing approximately 500 mA sink and 250 mA source current to charge and discharge the gate of a large power FET. It is understood that the total delay from the comp pin to the output pin should be about 100 ns.

# **Absolute Maximum Ratings**

| Rating                                 | Symbol           | Rating      | Unit |

|----------------------------------------|------------------|-------------|------|

| Supply Voltage (Low Impedance Source)  | V <sub>DD</sub>  | 13          | V    |

| Supply Current (High Impedance Source) | I <sub>DD</sub>  | 15          | mA   |

| Output Peak Current                    | I <sub>OUT</sub> | 600         | mA   |

| Regulator Current                      | I <sub>REG</sub> | 10          | mA   |

| Continuous Power at 25°C 8L SOIC       | P <sub>D</sub>   | 750         | mW   |

| 8L PDIP                                |                  | 1000        | mW   |

| Junction Temperature                   | T <sub>J</sub>   | 150         | °C   |

| Storage Temperature                    | T <sub>STG</sub> | - 65 to 150 | °C   |

| Lead Temperature, Soldering 10 Seconds | T <sub>L</sub>   | 300         | °C   |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

PWM Controller AS998/AS998A

#### **Electrical Characteristics**

Electrical Characteristics are guaranteed over full junction temperature range (0 to 105°C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. Unless otherwise specified, the conditions of test are  $V_{DD} = 12 \text{ V}$ ; OV = 0V, CSNS = 0V. Cload = 1800pf, Creg = 100 nf (AVVD to GND). To start chip, Vdd must be raised above UVLhigh.

| Parameter             | Symbol              | Test Condition                 | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------|--------------------------------|------|------|------|------|

| Startup Current       | I <sub>DDO</sub>    | UVL <sub>HIGH</sub> Threshold  |      | 64   | 100  | μA   |

| Supply Current        | I <sub>DD</sub>     | No Load                        | 1    | 2    | 4    | mA   |

| Startup Threshold     | UVL <sub>HIGH</sub> | AS998                          | 9    | 10   | 11   | V    |

|                       |                     | AS998A                         | 9.5  | 10   | 10.5 | V    |

| UVL off Threshold     | UVL <sub>LOW</sub>  |                                | 7.6  | 8    | 8.4  | V    |

| Bias Current at POS   | V <sub>CLAMP</sub>  | I <sub>DD</sub> = 10mA No Load | 13   | 14   | 14.7 | V    |

| Int Regulator Voltage | V <sub>REG</sub>    | I <sub>REG</sub> = 1mA         | 5.5  | 6.25 | 7.0  | V    |

#### Oscillator

| Parameter                  | Symbol           | Test Condition                                      | Min. | Тур. | Max. | Unit   |

|----------------------------|------------------|-----------------------------------------------------|------|------|------|--------|

| Mean Period                | T <sub>OSC</sub> | 8.4V < V <sub>DD</sub> < 13.3V; 15 cycle avg AS998  | 7.3  | 9.3  | 11.7 | μs     |

|                            |                  | 8.4V < V <sub>DD</sub> < 13.3V; 15 cycle avg AS998A | 8.1  | 9.3  | 10.7 | μs     |

| Modulation Repetition Rate | T <sub>REP</sub> |                                                     |      | 15   |      | cycles |

| Peak-to-Peak Modulation    | T <sub>DEV</sub> | Peak-to-Peak change in period                       | 13.7 | 16.5 | 23   | %      |

| Max. Duty Cycle            | D <sub>MAX</sub> |                                                     | 70   | 75   | 78   | %      |

#### **Error Amplifier**

| Symbol             | Test Condition                                | Min.                                                                                                                                                                                                                             | Тур. | Max.                                                                                                                                                                                                                                                                                                                                                                                         | Unit                                                                                                                                                                                                                                                                                        |

|--------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFB                |                                               |                                                                                                                                                                                                                                  | 100  |                                                                                                                                                                                                                                                                                                                                                                                              | kΩ                                                                                                                                                                                                                                                                                          |

| VDD <sub>REG</sub> |                                               | 11.4                                                                                                                                                                                                                             | 12   | 12.6                                                                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                           |

| $V_{REF}$          | $COMP = FB, V_{DD} = 12V$                     | 2.37                                                                                                                                                                                                                             | 2.5  | 2.62                                                                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                           |

| AV <sub>OL</sub>   | No load on COMP                               |                                                                                                                                                                                                                                  | 85   |                                                                                                                                                                                                                                                                                                                                                                                              | dB                                                                                                                                                                                                                                                                                          |

| GBP                | No load on COMP                               |                                                                                                                                                                                                                                  | 10   |                                                                                                                                                                                                                                                                                                                                                                                              | MHz                                                                                                                                                                                                                                                                                         |

| V <sub>COMPH</sub> | FB = 2V                                       | 4.5                                                                                                                                                                                                                              |      |                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                           |

| V <sub>COMPL</sub> | FB = 3V                                       |                                                                                                                                                                                                                                  | 100  | 250                                                                                                                                                                                                                                                                                                                                                                                          | mV                                                                                                                                                                                                                                                                                          |

| I <sub>COMPH</sub> | COMP = 3V, FB = 2V                            | 25                                                                                                                                                                                                                               | 50   | 100                                                                                                                                                                                                                                                                                                                                                                                          | μA                                                                                                                                                                                                                                                                                          |

| I <sub>COMPL</sub> | COMP = 1V, FB = 3V                            | 25                                                                                                                                                                                                                               | 300  | 500                                                                                                                                                                                                                                                                                                                                                                                          | μA                                                                                                                                                                                                                                                                                          |

|                    | RFB VDDREG VREF AVOL GBP VCOMPH VCOMPL ICOMPH | RFB  VDD <sub>REG</sub> V <sub>REF</sub> COMP = FB, V <sub>DD</sub> = 12V  AV <sub>OL</sub> No load on COMP  GBP  No load on COMP  V <sub>COMPH</sub> FB = 2V  V <sub>COMPL</sub> FB = 3V  I <sub>COMPH</sub> COMP = 3V, FB = 2V | RFB  | RFB       100         VDD <sub>REG</sub> 11.4       12         V <sub>REF</sub> COMP = FB, V <sub>DD</sub> = 12V       2.37       2.5         AV <sub>OL</sub> No load on COMP       85         GBP       No load on COMP       10         V <sub>COMPH</sub> FB = 2V       4.5         V <sub>COMPL</sub> FB = 3V       100         I <sub>COMPH</sub> COMP = 3V, FB = 2V       25       50 | RFB 100  VDD <sub>REG</sub> 11.4 12 12.6  V <sub>REF</sub> COMP = FB, V <sub>DD</sub> = 12V 2.37 2.5 2.62  AV <sub>OL</sub> No load on COMP 85  GBP No load on COMP 10  V <sub>COMPH</sub> FB = 2V 4.5  V <sub>COMPL</sub> FB = 3V 100 250  I <sub>COMPH</sub> COMP = 3V, FB = 2V 25 50 100 |

#### **Current Sense Comparator**

| Parameter             | Symbol            | Test Condition | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------|----------------|------|------|------|------|

| Scaling of COMP       |                   | to CSNS input  |      | 0.4  |      |      |

| AC Input Impedance    | R <sub>CSAC</sub> | Fin ≥ FCO      |      | 100  |      | kΩ   |

| Input Filter          | F <sub>CS</sub>   | Time Constant  |      | 320  |      | ns   |

| Prop. Delay to Output | tpd1              |                |      | 700  |      | ns   |

# **Electrical Characteristics (cont.)**

| Parameter                   | Symbol            | Test Condition                      | Min. | Тур. | Max. | Unit |

|-----------------------------|-------------------|-------------------------------------|------|------|------|------|

| Comparator Threshold        | V <sub>CSTH</sub> | COMP = 1V, FB = 3V                  |      | 1.25 |      | V    |

| Propagation Delay to Output | tpd2              | FB = 2, Vcs step to 1.65V, from 50% |      | 100  | 150  | ns   |

|                             |                   | point on CSNS input to 90% point on |      |      |      |      |

|                             |                   | output H to L transistion           |      |      |      |      |

### Over Voltage Input

| Parameter                    | Symbol            | Test Condition                  | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------|---------------------------------|------|------|------|------|

| OV V <sub>DD</sub> Threshold | VDD <sub>OV</sub> | Forcing VDD pin                 | 13   | 14   | 14.7 | V    |

| OV Threshold                 | V <sub>OV</sub>   | Forcing OV pin                  |      | 3.5  |      | V    |

| OV Latch State Low           | OV <sub>RN</sub>  | OV = Reg - 1V, Equiv. R to Reg  | 4    | 8    | 16   | kΩ   |

| OV Latch State High          | OV <sub>RP</sub>  | OV = 1V, Equiv. R to Gnd        | 4    | 8    | 16   | kΩ   |

| OV Hi Impedance Pull-up      | OV <sub>HI</sub>  | OV = 1V, I <sub>DD</sub> = 10mA |      | 0.3  | 1    | μA   |

| OV Unlatch Threshold         | VDD <sub>UL</sub> | VDD dropped until latch fails   | 4.75 | 5    | 5.25 | V    |

### Output

| Parameter                | Symbol           | Test Condition           | Min. | Тур. | Max. | Unit |

|--------------------------|------------------|--------------------------|------|------|------|------|

| Max. "Off State" Voltage | V <sub>OFF</sub> | I <sub>OUT</sub> = 100μA |      |      | 1.7  | V    |

| Output Rise Time         | tr               | T = 25°C, 10% - 90%      | 170  | 250  | 290  | ns   |

| Output Fall Time         | tf               | T = 25°C, 10% - 90%      | 140  | 210  | 240  | ns   |

# This datasheet has been download from:

# www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com