#### **Objective specification**

## 900 MHz transmit modulator and 2.2 GHz fractional–N synthesizer

## SA9025

#### DESCRIPTION

This specification defines the requirements for a transmitter modulator and fractional–N synthesizer IC to be used in cellular telephones which employ the North American Dual Mode Cellular System (IS–136).

#### FEATURES

- Low current from 3.75V supply

- Low phase noise

- Main loop with internal charge pump and fractional compensation

- 3–line serial interface bus

- Power down for the synthesizers

- Speedup mode for faster switching

#### **APPLICATIONS**

- Cellular phones

- Portable battery-powered radio equipment.

#### **GENERAL DESCRIPTION**

The SA9025 BICMOS device integrates:

- Main channel synthesizer

- Auxiliary synthesizer

- Transmit offset synthesizer and oscillator

- I/Q modulator

- Power control

#### QUICK REFERENCE DATA

| • | Reference   | and | clock  | buffers |

|---|-------------|-----|--------|---------|

|   | 11010101100 | ana | 010010 | balloio |

• Control logic for programming and power down modes

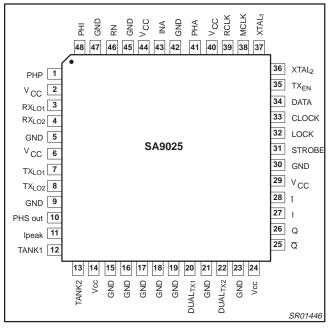

#### **PIN CONFIGURATION**

| SYMBOL               | PARAMETER                               | CONDITIONS         | MIN. | TYP. | MAX. | UNIT |

|----------------------|-----------------------------------------|--------------------|------|------|------|------|

| V <sub>CC</sub>      | Supply voltage                          | V <sub>CC</sub>    | 3.6  | 3.75 | 3.9  | V    |

| I <sub>CC</sub>      | Supply current                          |                    | -    | TBD  | -    | mA   |

| I <sub>CC_save</sub> | Total supply current in power–down mode |                    | -    | TBD  | _    | mA   |

| f <sub>VCO</sub>     | Input frequency                         |                    | 800  | -    | 2200 | MHz  |

| f <sub>AUX</sub>     | Input frequency                         |                    | 10   | -    | 500  | MHz  |

| f <sub>XTAL</sub>    | Crystal reference input frequency       |                    | 10   | -    | 40   | MHz  |

| f <sub>PC</sub>      | Maximum phase comparator frequency      | Main and Aux loops | -    | -    | 5    | MHz  |

| T <sub>amb</sub>     | Operating ambient temperature           |                    | -40  | -    | +85  | °C   |

#### **ORDERING INFORMATION**

| TYPE NUMBER | PACKAGE                                                                   |  |          |  |

|-------------|---------------------------------------------------------------------------|--|----------|--|

|             | NAME DESCRIPTION VERS                                                     |  |          |  |

| SA9025      | LQFP48 Plastic low profile quad flat package; 48 leads; body 7x7x1.4 mm S |  | SOT313-2 |  |

SA9025

# 900 MHz transmit modulator and 2.2 GHz fractional–N synthesizer

#### CONNECTIONS

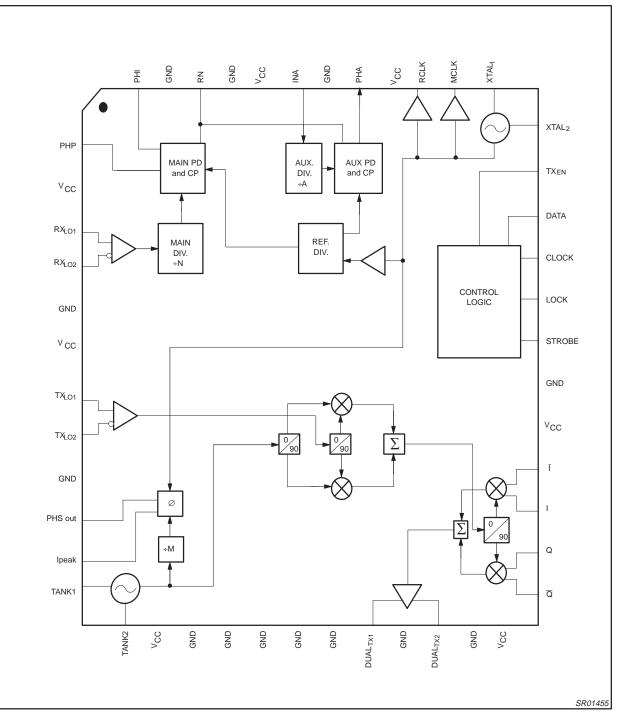

Figure 2. SA9025 Block Diagram

## SA9025

### **PIN DESCRIPTIONS**

| PIN<br>NO. | PIN               | DESCRIPTION                          |

|------------|-------------------|--------------------------------------|

| 1          | PHP               | Proportional charge pump output      |

| 2          | V <sub>CC</sub>   | Digital supply voltage               |

| 3          | RX <sub>LO1</sub> | Differential LO input                |

| 4          | RX <sub>LO2</sub> | Differential LO input                |

| 5          | GND               | Digital Ground                       |

| 6          | V <sub>CC</sub>   | Tank supply voltage                  |

| 7          | TX <sub>LO1</sub> | Differential Transmit LO Input       |

| 8          | TX <sub>LO2</sub> | Differential Transmit LO Input       |

| 9          | GND               | Tank Ground                          |

| 10         | PHS OUT           | Charge pump output (transmit offset) |

| 11         | I <sub>PEAK</sub> | PHS out current set resistor         |

| 12         | TANK1             | VCO differential tank                |

| 13         | TANK2             | VCO differential tank                |

| 14         | V <sub>CC</sub>   | Tx supply voltage                    |

| 15         | GND               | Tx Ground                            |

| 16         | GND               | Tx Ground                            |

| 17         | GND               | Tx Ground                            |

| 18         | GND               | Tx Ground                            |

| 19         | GND               | Tx Ground                            |

| 20         | DUALTX1           | Dual mode RF output                  |

| 21         | GND               | Tx Ground                            |

| 22         | DUALTX2           | Dual mode RF output                  |

| 23         | GND               | Tx Ground                            |

| 24 | V <sub>CC</sub>   | Tx supply voltage                       |

|----|-------------------|-----------------------------------------|

| 25 | Q                 | Inverting quadrature input              |

| 26 | Q                 | Non-Inverting quadrature input          |

| 27 | Ī                 | Non-inverting in phase modulation input |

| 28 | Ī                 | Inverting in phase modulation input     |

| 29 | V <sub>CC</sub>   | Tx supply voltage                       |

| 30 | GND               | Tx Ground                               |

| 31 | STROBE            | Data input latch enable                 |

| 32 | LOCK              | Lock detect                             |

| 33 | CLOCK             | Serial clock input                      |

| 34 | DATA              | Serial data input                       |

| 35 | ΤΧ <sub>ΕΝ</sub>  | Transmit enable                         |

| 36 | XTAL <sub>2</sub> | Crystal Oscillator emitter input        |

| 37 | XTAL <sub>1</sub> | Crystal Oscillator base Input           |

| 38 | MCLK              | Buffered oscillator output              |

| 39 | RCLK              | Buffered oscillator output              |

| 40 | V <sub>CC</sub>   | REF supply voltage                      |

| 41 | PHA               | Auxiliary charge pump output            |

| 42 | GND               | REF Ground                              |

| 43 | INA               | RX <sub>IF</sub> input                  |

| 44 | V <sub>CC</sub>   | CP supply voltage                       |

| 45 | GND               | CP Ground                               |

| 46 | RN                | CP current set resistor                 |

| 47 | GND               | CP Ground                               |

| 48 | PHI               | Integral charge pump output             |

### SA9025

#### **OPERATING MODES & POWER DOWN CONTROL**

There are two power saving modes of operation which the SA9025 can be put into, dependent on the status of the system. The intention of these different modes is to disable circuity that is not in use at the time in order to reduce power consumption. During sleep mode, only circuitry which is required to provide a master clock to

the digital portion of the system is enabled. During receive mode, circuitry which is used to perform the receive function and provide a master clock is enabled. In transmit mode all the functions of the chip are enabled which are required to perform transmit, receive and provide master clock.

| SA9025                                           | POWER MODE | <b>TRUTH TAB</b> | LE           |    |               |    |

|--------------------------------------------------|------------|------------------|--------------|----|---------------|----|

|                                                  | Sleep Mode |                  | Receive Mode |    | Transmit Mode |    |

| Enabled                                          | yes        | no               | yes          | no | yes           | no |

| Crystal Oscillator                               | 1          |                  | 1            |    | 1             |    |

| Phase detector and charge pump (transmit offset) |            | 1                |              | 1  | 1             |    |

| VCO                                              |            | 1                |              | 1  | 1             |    |

| SSB Up-converter                                 |            | 1                |              | 1  | 1             |    |

| MCLK Buffer                                      | 1          |                  | 1            |    | 1             |    |

| RCLK Buffer                                      |            | 1                | 1            |    | 1             |    |

| +M offset loop divider                           |            | 1                |              | 1  | 1             |    |

| TX <sub>LO</sub> Buffer                          |            | 1                |              | 1  | 1             |    |

| RX <sub>LO</sub> Buffer                          |            | 1                | 1            |    | 1             |    |

| I/Q Modulator                                    |            | 1                |              | 1  | 1             |    |

| Variable Gain Amp.                               |            | 1                |              | 1  | 1             |    |

| Control Logic                                    | ✓          |                  | 1            |    | 1             |    |

| Main Divider                                     |            | 1                | 1            |    | 1             |    |

| Reference Divider                                |            | 1                | 1            |    | 1             |    |

| Auxiliary Divider                                |            | 1                | 1            |    | 1             |    |

| Main Phase Detector and charge pump              |            | 1                | 1            |    | 1             |    |

| Auxiliary Phase Detector and charge pump         |            | 1                | 1            |    | 1             |    |

| Lock Detect                                      |            | √                | 1            |    | 1             |    |

### SA9025

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL            | PARAMETER                                          | VAL  | .UE                  | UNIT |

|-------------------|----------------------------------------------------|------|----------------------|------|

|                   |                                                    | MIN. | MAX.                 |      |

| V <sub>CC</sub>   | Supply voltage                                     | -0.3 | +4.5                 | V    |

| V <sub>IN</sub>   | Voltage applied to any other pin                   | -0.3 | V <sub>CC</sub> +0.3 | V    |

| P <sub>N</sub>    | Power dissipation, $T_A = 25^{\circ}C$ (still air) |      | 980                  | mW   |

| T <sub>JMAX</sub> | Operation junction temperature                     |      | TBD                  | °C   |

| P <sub>MAX</sub>  | Power input/output                                 |      | +10/+14              | dBm  |

| I <sub>MAX</sub>  | DC current into any I/O pin                        | -10  | +10                  | mA   |

| T <sub>STG</sub>  | Storage temperature                                | -65  | +150                 | °C   |

| To                | Operating temperature                              | -40  | +85                  | °C   |

#### DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = +3.75 V;  $T_A$  = 25°C; unless otherwise stated.

| SYMBO              | DADAMETED                                                 |                                      |                     | LIMITS               |                       |        |

|--------------------|-----------------------------------------------------------|--------------------------------------|---------------------|----------------------|-----------------------|--------|

| L                  | PARAMETER                                                 | TEST CONDITIONS                      | MIN                 | TYP                  | MAX                   | UNITS  |

| V <sub>CC</sub>    | Power supply range                                        |                                      | 3.6                 | 3.75                 | 3.9                   | V      |

|                    |                                                           | Sleep mode                           |                     | 2                    |                       |        |

|                    |                                                           | Standby mode                         |                     | 17                   |                       |        |

| I <sub>CC</sub>    | Supply current                                            | Operating: full power analog         |                     | 95                   |                       | mA     |

|                    |                                                           | Operating: full power digital        |                     |                      |                       |        |

|                    |                                                           | DUAL <sup>1</sup>                    |                     | 52                   |                       |        |

| I/Ī                | In-phase differential input                               | quiescent                            |                     | V <sub>CC</sub> /2   |                       | V      |

| Q / <u>Q</u>       | Quadrature phase differential input                       | quiescent                            |                     | V <sub>CC</sub> /2   |                       | V      |

| V <sub>IL</sub>    | Clock, Data, Strobe, TX <sub>EN</sub>                     | Input logic low                      | -0.3                |                      | $0.3 \times V_{CC}$   | V      |

| V <sub>IH</sub>    | Clock, data, strobe, TX <sub>EN</sub>                     | Input logic high                     | $0.7 \times V_{CC}$ |                      | V <sub>CC</sub> +0.3  | V      |

| T <sub>A</sub>     | Ambient temperature range                                 |                                      | -40                 | +25                  | +85                   | °C     |

| Digital Ou         | itputs Lock                                               | -                                    |                     |                      |                       |        |

| V <sub>OL</sub>    | Output voltage LOW                                        | $I_{O} = 2mA$                        |                     |                      | 0.4                   | V      |

| V <sub>OH</sub>    | Output voltage HIGH                                       | I <sub>O</sub> = -2mA                | $V_{CC} - 0.4$      |                      |                       | V      |

| Charge P           | ump Current Setting Resistor Input; RN,                   | R <sub>Ipeak</sub>                   | •                   |                      |                       |        |

| RN                 | External resistor to ground                               |                                      | 6                   | 7.5                  | 24                    | kΩ     |

| R <sub>lpeak</sub> | External resistor to ground                               |                                      |                     | 4.7                  |                       | kΩ     |

| V <sub>RN</sub>    | Regulated voltage                                         | RN = 7.5 kΩ                          |                     | 1.23                 |                       | V      |

| V <sub>Ipeak</sub> | Regulated voltage                                         | R <sub>ipeak</sub> = 4.7 kΩ          |                     | 1.3                  |                       | V      |

| I <sub>peak</sub>  | PHSOUT programming                                        | $R_{ipeak} = 4.7 \ k\Omega$          |                     | 0.26                 |                       | mA     |

| PHSgain            | PHSOUT gain                                               | $R_{ipeak} = 4.7 \text{ k}\Omega$    |                     | 24xl <sub>peak</sub> |                       | mA     |

| Κφ                 | PD phase gain                                             | Transmit offset PLL in phase lock    |                     | 4.33                 |                       | mA/rad |

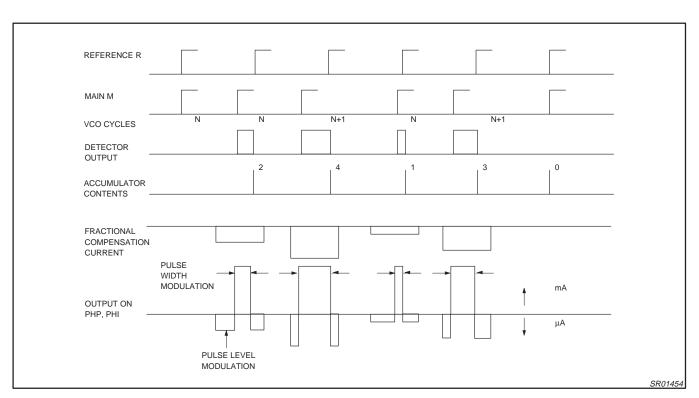

| Charge P           | ump Outputs (including fractional comp                    | ensation pump, not PHS) RN = 7.5     | δkΩ                 |                      |                       |        |

| I <sub>OPH</sub>   | Charge pump output current error versus expected current. |                                      | -15                 |                      | 15                    | %      |

| IMATCH             | Sink to source current matching                           | $V_{PHX} = V_{CC}/2$                 | -5                  |                      | 5                     | %      |

|                    | Current output variation versus V <sub>PHX</sub>          | V <sub>PHX</sub> in compliance range | -10                 |                      | 10                    | %      |

|                    | Charge pump off, leakage current                          | $V_{PHX} = V_{CC}/2$                 | -10                 | ±1                   | 10                    | nA     |

| V <sub>PH</sub>    | Charge pump voltage compliance <sup>3</sup>               |                                      | 0.7                 |                      | V <sub>CC</sub> – 0.8 | V      |

|                    | ump Outputs (only PHS) $R_{ipeak} = 4.7 \text{ k}\Omega$  |                                      |                     |                      | -                     |        |

| I <sub>OPH</sub>   | Charge pump output current error versus expected current. |                                      | -15                 |                      | 15                    | %      |

| IMATCH             | Sink to source current matching                           | $V_{PHS} = V_{CC}/2$                 | -10                 |                      | 10                    | %      |

### SA9025

|                 | Current output variation versus V <sub>PH</sub> | V <sub>PHS</sub> in compliance range | -25 | 25                   | % |

|-----------------|-------------------------------------------------|--------------------------------------|-----|----------------------|---|

| V <sub>PH</sub> | Charge pump voltage compliance                  |                                      | 0.5 | V <sub>CC</sub> -0.5 | V |

#### **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = +3.75 V;  $T_A$  = 25°C; unless otherwise stated.

| SYMBOL               | DADAMETED                                                                                                | TEST CONDITIONS                                                                 | LIMITS                    |                             |                   | UNITS                              |  |

|----------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|-----------------------------|-------------------|------------------------------------|--|

| STMBUL               | PARAMETER                                                                                                | TEST CONDITIONS                                                                 | MIN                       | TYP                         | MAX               |                                    |  |

| Modulator            |                                                                                                          |                                                                                 |                           |                             |                   |                                    |  |

| TX <sub>LO 1/2</sub> | Transmit LO input (AC-coupled; $50\Omega$ single-ended, $100\Omega$ differential)                        | Input power<br>Frequency range                                                  | -13<br>900                |                             | -10<br>1100       | dBm<br>MHz                         |  |

| VSWR                 |                                                                                                          |                                                                                 |                           | 2:1                         |                   |                                    |  |

| TANK1/2              | VCO tank differential inputs                                                                             | Frequency range                                                                 | 90                        |                             | 180               | MHz                                |  |

| ÷М                   | PLL offset divider                                                                                       | Maximum input frequency                                                         | 180                       |                             |                   | MHz                                |  |

| XTAL <sub>1</sub>    | Osc. transistor base                                                                                     | Osc. frequency                                                                  | 10                        |                             | 40                | MHz                                |  |

| XTAL <sub>2</sub>    | Osc. transistor emitter                                                                                  | Osc. frequency                                                                  | 10                        |                             | 40                | MHz                                |  |

| XO                   | Negative resistance                                                                                      |                                                                                 |                           | -100                        |                   | Ω                                  |  |

| RCLK,<br>MCLK        | Reference buffer output<br>Frequency range<br>Output levels<br>Harmonic content                          | Z <sub>LOAD</sub> = 5kΩ  7 pF                                                   | 10<br>0.7                 | 1.0                         | 40<br>1.4<br>–10  | MHz<br>V <sub>P–P</sub><br>dBc     |  |

| ΤΧ <sub>ΕΝ</sub>     | Transmit enable                                                                                          | Transmit enable<br>Transmit disable                                             |                           | $TX_{EN} = 1$ $TX_{EN} = 0$ |                   | Logic                              |  |

| Q/Q<br> /]           | Baseband in-phase differential inputs                                                                    | Maximum frequency<br>Diff. mod. level<br>Diff. input impedance<br>DC bias point | 1.8<br>0.8<br>10.0<br>1.8 | 0.9<br>V <sub>CC</sub> /2   | 1.0<br>2.55       | MHz<br>V <sub>P-P</sub><br>kΩ<br>V |  |

| TX <sub>RF</sub>     | TX <sub>RF</sub> operating range                                                                         |                                                                                 | 820                       |                             | 920               | MHz                                |  |

| DUAL <sub>TX</sub>   | DUAL output SE=1, TX <sub>EN</sub> =1 (with external matching) (50Ω)                                     | AMPS/DAMPS                                                                      | 820                       |                             | 853               | MHz                                |  |

| DUAL <sub>TX</sub>   | Differential output, (DUAL <sub>TX</sub> ) open-collector, matched to $200\Omega$ differential impedance | Output level (avg. min., I and Q<br>quad., 0dB VGA)<br>Gain flatness            | +9.0                      | +11.0                       | +13.0             | dBm<br>dB                          |  |

| DUAL <sub>TX</sub>   | Linearity worst case intermod. products<br>(0dB VGA OR +9 dBm, whichever is<br>less, I & Q in-phase)     | 3rd-order<br>5th-order<br>7th-order                                             |                           | -42<br>-55<br>-65           | -34<br>-45<br>-53 | dBc                                |  |

| DUAL <sub>TX</sub>   | Carrier suppression<br>(I & Q in quadrature)                                                             | VGA = 0dB<br>VGA = -38dB                                                        |                           | -45<br>-33                  | -35               | dBc                                |  |

| DUAL <sub>TX</sub>   | Sideband suppression<br>(I & Q in quadrature)                                                            |                                                                                 |                           | -45                         | -35               | dBc                                |  |

|                      |                                                                                                          | 2 to 284 MHz                                                                    |                           |                             | -45               |                                    |  |

|                      |                                                                                                          | 824 to 849 MHz                                                                  |                           |                             | -47               | dBc                                |  |

| DUAL <sub>TX</sub>   | Spurious output                                                                                          | 849 to 869 MHz                                                                  |                           |                             | -45               | ]                                  |  |

|                      |                                                                                                          | 869 to 894 MHz                                                                  |                           |                             | -104              | dBm                                |  |

|                      |                                                                                                          | 894 to 8490 MHz                                                                 |                           |                             | -45               | dBc                                |  |

|                      |                                                                                                          | TX <sub>LO</sub>                                                                |                           |                             | -21               |                                    |  |

|                      |                                                                                                          | Upper Side Band                                                                 |                           |                             | -21               |                                    |  |

| DUAL <sub>TX</sub>   | TX <sub>LO</sub> up-conversion products                                                                  | $TX_{LO} \pm 3 \times TX_{OFFSET}$                                              |                           |                             | -36               | dBc                                |  |

|                      |                                                                                                          | Harmonics ≤ 10th                                                                |                           |                             | -21               |                                    |  |

| DUAL <sub>TX</sub>   | Broad-band noise (0dB VGA or +9 dBm,<br>whichever is less)                                               | 869 to 894 MHz                                                                  |                           |                             | -123              | dBm/Hz                             |  |

| DUAL <sub>TX</sub>   | Adjacent channel noise power                                                                             | @ 30 kHz                                                                        |                           |                             | -95               | dBc/Hz                             |  |

| DUALTX               | Alternate channel noise power                                                                            | @ 60 kHz                                                                        |                           |                             | -101              | dBc/Hz                             |  |

## SA9025

|                           |                                                                                             | Main Divider         |                                                             |      |                  |

|---------------------------|---------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------|------|------------------|

| <i>f</i> <sub>MMAX</sub>  | Input frequency range                                                                       |                      | 800                                                         | 2200 | MHz              |

|                           | Input harmonics                                                                             | No multi–clocking    | -10                                                         |      | dBc              |

| RX <sub>LO 1/2</sub>      | Synthesizer LO input (AC-coupled;<br>external shunt 50Ω single-ended,<br>100Ω differential) | Input power          | -20                                                         | 0    | dBm              |

|                           | · · · · ·                                                                                   | Reference Divider    | · · ·                                                       |      |                  |

| f <sub>RMAX</sub>         | Input frequency RANGE                                                                       |                      | 10                                                          | 40   | MHz              |

|                           | Input harmonics                                                                             | No multi–clocking    | -10                                                         |      | dBc              |

|                           | · · · · · ·                                                                                 | Auxiliary Divider    | · · · ·                                                     |      | -                |

| <i>f</i> AMAX             | Input frequency RANGE                                                                       |                      | 10                                                          | 500  | MHz              |

|                           | Input harmonics                                                                             | No multi-clocking    | -10                                                         |      | dBc              |

| V <sub>INA</sub>          | Input signal amplitude                                                                      |                      | 0.200                                                       |      | V <sub>P-P</sub> |

|                           |                                                                                             | Serial Interface     |                                                             |      |                  |

| <i>f</i> <sub>CLOCK</sub> | Clock frequency                                                                             |                      |                                                             | 10   | MHz              |

| t <sub>SU</sub>           | Set-up time: DATA to CLOCK, CLOCK to STROBE                                                 |                      | 30                                                          |      | ns               |

| t <sub>H</sub>            | Hold time: CLOCK to DATA                                                                    |                      | 30                                                          |      | ns               |

|                           |                                                                                             | CLOCK                | 30                                                          |      |                  |

| t <sub>SW</sub>           | Pulse width                                                                                 | STROBE (B - D words) | 30                                                          |      | ns               |

|                           | Puise wiath                                                                                 | A word               | $\frac{1}{f_{\text{REF}} \cdot \text{NREF}} + t_{\text{W}}$ |      | 115              |

Transmit mode @ 33% duty cycle.

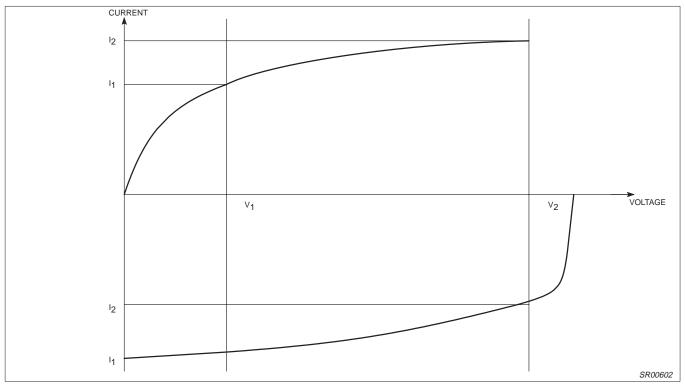

The relative output current variation is defined thus: Δl<sub>out</sub>/l<sub>out</sub>=2x(l<sub>2</sub>-l<sub>1</sub>)/|(l<sub>2</sub>+l<sub>1</sub>)|; with V<sub>1</sub>=0.7V, V<sub>2</sub>=V<sub>CC</sub>-0.8V (see figure 3)

Power supply current measured with f<sub>RX</sub> = 2100.54 MHZ, f<sub>REF</sub> = 19.44 MHZ, f<sub>INA</sub>= 109.92 MHZ, main phase detector bias resistor = 7.5 kΩ. Main phase detector reference frequency = 240 kHZ, auxiliary phase detector frequency = 240 kHZ.

Maximum and minimum levels guaranteed by design and random testing for temperature range of -40 to +85°C.

Power is rated at I/Q input level of 0.9V<sub>PP</sub>.

Figure 3. Output Current Definition

### SA9025

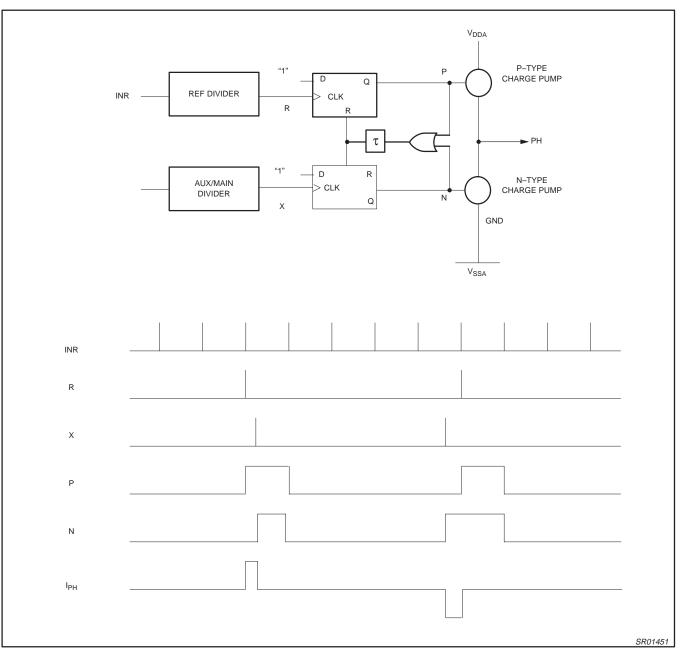

## Functional Description Main Channel Synthesizer & Auxiliary Synthesizer

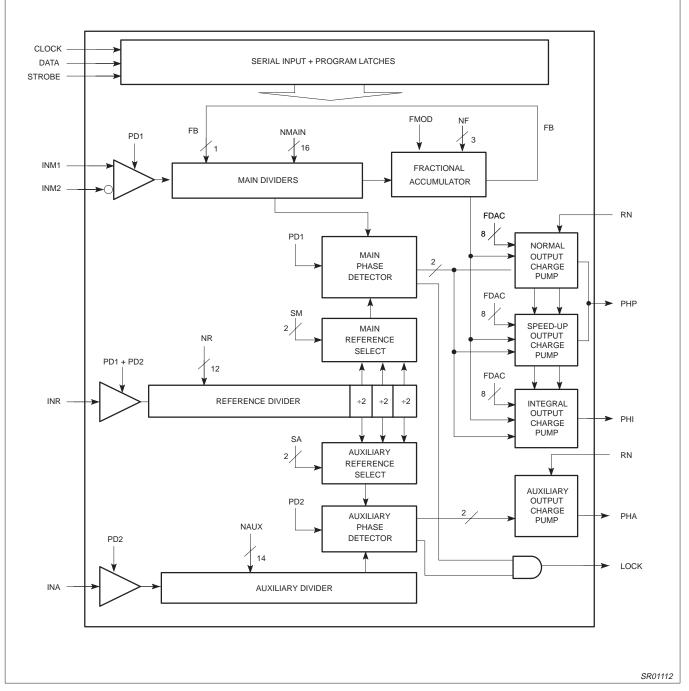

Figure 4. Synthesizer Block Diagram

#### Serial Programming Input

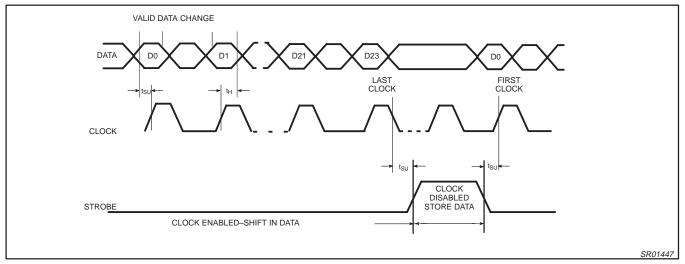

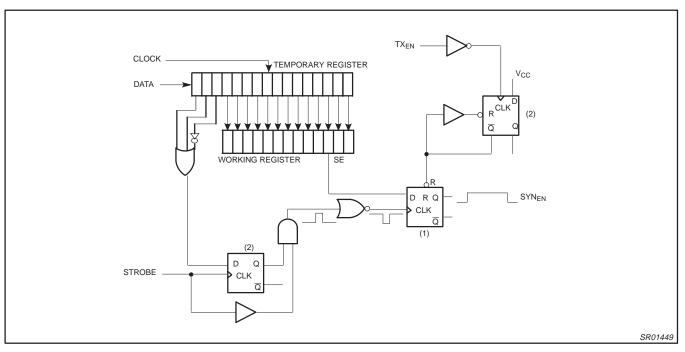

The serial input is a 3-wire input (CLOCK, DATA, STROBE) used to program all counter ratios, DACs, selection and enable bits. The programming data is structured into 24-bit words; each word includes 2 or 3 address bits. Figure [5] shows the timing diagram of the serial input. When STROBE = L, the clock driver is enabled and on positive edges of the CLOCK, the signal on DATA input is

clocked into a shift register. When STROBE = H, the clock is disabled and the data in the shift register remains stable.

Depending on the 2 or 3 address bits, data is latched into different working or temporary registers. In order to fully program the synthesizer, 3 words must be sent: A, B and C. The D word programs all other functions within the SA9025. Those functions are

### SA9025

power control, +M (offset loop), SE (Tx offset loop synthesizer enable), DUAL mode, Sleep Mode 1 and Sleep Mode 2.

The data for FDAC is stored by the B word into a temporary register. When the A word is loaded, the data in this temporary register is loaded together with the A word into the work registers to avoid false temporary main synthesizer output caused by changes in fractional compensation.

The A word contains new data for the main divider. The A word is loaded into the working registers only when a main divider synchronization signal is active to avoid phase jumps when reprogramming the main divider. The synchronization pulse is generated by the main divider when it has reached its terminal count, at which time a main divider output pulse is also sent to the main phase detector. This disables the loading of the A word each main divider cycle during maximum of (NREF /  $f_{REF}$ ) seconds. Therefore, to be sure that the A word will be correctly loaded, the STROBE signal must be high for at least (NREF /  $f_{REF}$ ) seconds. When programming the A word, the main charge pumps on output PHP and PHI are set into the speed–up mode as soon as the A word is latched into the working registers and remain so as long as STROBE is held high.

Figure 5. Serial Input Timing Sequence

## SA9025

#### Table 1. Function Table

| Symbol | Bits | Function                                                                                                                                 |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| FMOD   | 1    | Fractional-N modulus selection flag:<br>'0' = modulo 8<br>'1' = modulo 5                                                                 |

| NF     | 3    | Fractional-N increment                                                                                                                   |

| NMAIN  | 16   | Main divider ratio; 512 to 65,535 allowed                                                                                                |

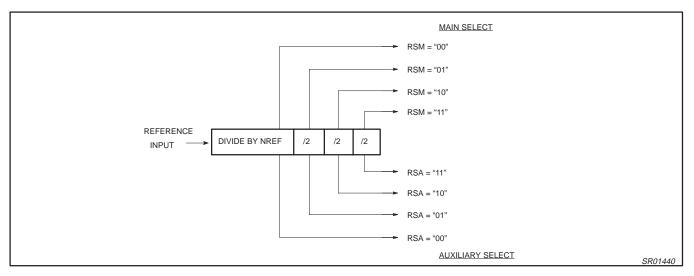

| NREF   | 10   | Reference divider ratio; 4 to 1,023 allowed,<br>RSM, RSA = "0 0"                                                                         |

| RSM    | 2    | Reference select for main phase detector                                                                                                 |

| RSA    | 2    | Reference select for auxiliary phase detector                                                                                            |

| FDAC   | 8    | Fractional compensation charge pump current DAC                                                                                          |

| NAUX   | 14   | Auxiliary divider ratio; 128 to 16,384 allowed                                                                                           |

| СР     | 2    | Charge pump current ratio select (see table 1)                                                                                           |

| LD     | 2    | Lock detect output select (see table 2)                                                                                                  |

| PD1    | 1    | PD1 = 0 for power down; shuts off power to<br>main divider and main chargepumps, anded<br>with PD2 to turn off ref. divider.             |

| PD2    | 1    | PD2 = 0 for power down; shuts off power to<br>auxiliary divider, and auxiliary charge pumps;<br>anded with PD1 to turn off ref. divider. |

| PC     | 8    | Power control (see note 3)                                                                                                               |

| М      | 2    | ÷M, M = 6, 7, 8, 9 (see note 4)                                                                                                          |

| SE     | 1    | Transmit offset synthesizer on/off                                                                                                       |

| ТМ     | 1    | Transmit mode: '0' = DUAL                                                                                                                |

| AD     | 1    | Mode control, 1 = digital; 0 = analog                                                                                                    |

| SM1    | 1    | Sleep mode 1                                                                                                                             |

| SM2    | 1    | Sleep mode 2                                                                                                                             |

Data bits are shifted in on the the leading clock edge, with the least significant bit (LSB) first and the most significant bit (MSB) last.

- On the rising edge of the strobe and with the address decoder output = 1, the contents of the input shift register are transferred to the working registers. The strobe rising edge comes one half clock period after the clock edge on which the MSB of a word is shifted in.

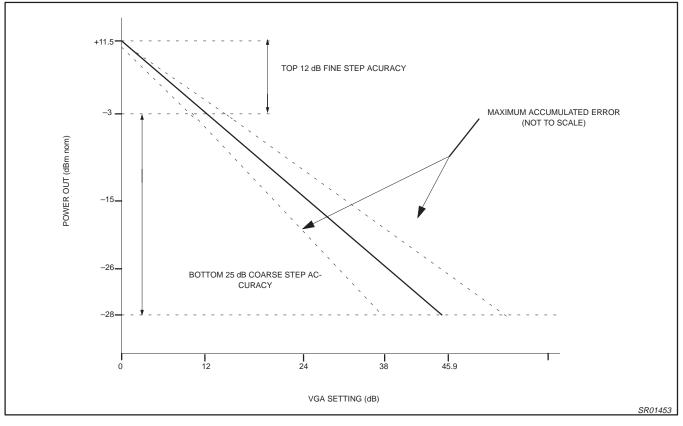

- 3. The PC bits are used for the power control function. Eight (8) bits of data allows for appropriate resolution of the power control. 00000000 = 0 dB: 11111111 = -45.9 dB (= 255 × 0.18).

- 4. The M bits are used to program the ÷M counter for integer values between 6 and 9. 00 = 6, 01 = 7, 10 = 8, 11 = 9.

- 5. The TM bit is used to put the SA9025 into DUAL mode operation. In DUAL mode (TM = 0).

- 6. The AD bit allows a reduction in the linearity of the DUAL output driver while in AMPS mode.

- 7. The SM1 bit is used to shut down the  $TX_{LO}$  buffers. SM1 = 1, buffers on; SM1 = 0, buffers off.

- 8. The SM2 bit is used to shut down the RCLK buffer. SM2 = 1, buffer on; SM2 = 0, buffer off.

- 9. The SE bit turns on and off the offset loop synthesizer circuits. SE = 1, synthesizer on; SE = 0, synthesizer off.

- 10. The LOCK bits determine what signal is present on the LOCK pin as follows:

#### Table 2.

|      | Lock Detect Output Select*                |

|------|-------------------------------------------|

| LOCK | LOCK Pin Function                         |

| 00   | Main, auxiliary and offset lock condition |

| 01   | Main and auxiliary lock condition         |

| 10   | Main lock detect condition                |

| 11   | Auxiliary lock condition                  |

\*When a section is in power down mode, the lock indicator for that section is high.

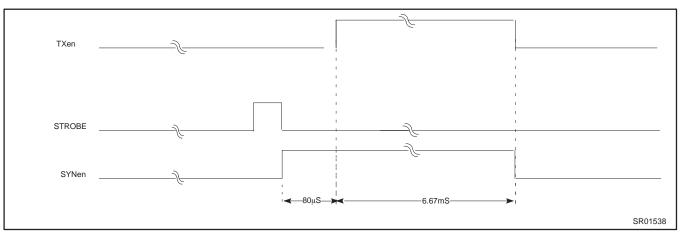

Figure 6. Transmit Offset Synthesizer Reset Circuit

In Figure 6, the falling edge of the strobe and address, inverted, toggles the Q output of flip-flop (1) to a '1' state, enabling the phase detector, VCO, divide by M, TX<sub>IF</sub> buffer and SSB up-converter. Approximately 80µs after the synthesizer is locked, the TX<sub>EN</sub> signal (enabled = 1) turns on the modulator and variable gain amplifier. The rising edge of TX<sub>EN</sub> has no effect on SYN<sub>EN</sub>, however, the falling (rising inverted) edge toggles the  $\overline{Q}$  output of D flip-flop (2) to a '0' state. This disables the synthesizer, modulator and variable gain amplifier. To insure that slow edges on TX<sub>EN</sub> do not cause improper operation, the TX<sub>EN</sub> is a Schmitt trigger design.

The address decoder for program word 'D' ANDed together with the strobe is used to load the contents of the temporary register into the working registers. D flip-flop (3) is used to prevent multiple strobe and address pulses in the event the address decoder output toggles on garbage bits during the time the strobe remains in a '1' state.

The temporary register is common to the transmit offset synthesizer, main channel synthesizer and auxiliary synthesizer.

Figure 7. Transmit Offset Synthesizer Timing Diagram

SA9025

### Data format Format of programmed data

| LAST IN |     | MSB | Ś   | SERIAL PROGRA | MMING FORMAT | Γ  | FIRST IN LSB |

|---------|-----|-----|-----|---------------|--------------|----|--------------|

| p23     | p22 | p21 | p20 | /             | /            | р1 | p0           |

#### A word, length 24 bits

| Last i | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |      |        |       | MSB                                                   |         |         |        |        |        |         |        |          |        |      |     |  |  | LSB | Fir | st IN |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--------|-------|-------------------------------------------------------|---------|---------|--------|--------|--------|---------|--------|----------|--------|------|-----|--|--|-----|-----|-------|

| Addre  | SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | fmod     | Frac | tional | -N    |                                                       |         |         |        | Mai    | n Divi | der ra  | tio– N | Imain    |        |      |     |  |  |     | Sp  | oare  |

| 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fmod     | NF2  | NF1    | NF0   | NF0 N15 N14 N13 N12 N11 N10 N9 N8 N7 N6 N5 N4 N3 N2 N |         |         |        |        |        |         |        | N1       | N0     | sk1  | sk2 |  |  |     |     |       |

| Defa   | Default:         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         1< |          |      |        |       |                                                       |         |         | 0      | 0      | 0      | 0       | 0      |          |        |      |     |  |  |     |     |       |

| A wor  | d sele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ct       |      |        | Fixed | to 00.                                                |         |         |        |        |        |         |        |          |        |      |     |  |  |     |     |       |

| Fracti | Fractional Modulus select FI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |      |        |       |                                                       | 8, 1=   | modu    | ılo 5. |        |        |         |        |          |        |      |     |  |  |     |     |       |

| Fracti | onal-l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N Increr | nent |        | NF2   | 0 Fractio                                             | onal N  | I Incre | ement  | value  | s 000  | to 11   | 1.     |          |        |      |     |  |  |     |     |       |

| N–Div  | N-Divider NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |      |        |       | I15, Maii                                             | n divio | der va  | lues 5 | 512 to | 6553   | 5 allov | ved fo | or divio | der ra | tio. |     |  |  |     |     |       |

#### B word, length 24 bits

| ADDR | RESS                                                       |    | F  | REFE | REN | CED | DIVID | ER I  | NREI     | F        |                                                       | R         | SM       | RS      | 6A       |       | FRA    | CTION   | AL CC  | MPEN | SATIO     | N DAC     | ;         |

|------|------------------------------------------------------------|----|----|------|-----|-----|-------|-------|----------|----------|-------------------------------------------------------|-----------|----------|---------|----------|-------|--------|---------|--------|------|-----------|-----------|-----------|

| 0    | 1                                                          | R9 | R8 | R7   | R6  | R5  | R4    | R3    | R2       | R1       | 1 R0 RSM RSM RSA RSA RSA Fdac Fdac Fdac Fdac Fdac A 3 |           |          |         |          |       |        |         |        |      | Fdac<br>2 | Fdac<br>1 | Fdac<br>0 |

| Defa | ault:                                                      | 0  | 0  | 0    | 1   | 0   | 1     | 0     | 0        | 0        | 1                                                     | 0         | 0        | 0       | 0        | х     | x      | х       | х      | х    | х         | х         | х         |

|      | B word select Fixed to 01                                  |    |    |      |     |     |       |       |          |          |                                                       |           |          |         |          |       | -      |         |        |      |           |           |           |

|      | R–Divider R0R9, Reference divider value                    |    |    |      |     |     |       | alue  | s 4 to 1 | 1023 al  | lowed fo                                              | or divide | er ratio | n.      |          |       |        |         |        |      |           |           |           |

| Cha  | Charge pump current<br>Ratio CP1, CP0: Charge pump current |    |    |      |     |     |       |       | irren    | t ratio, | see tab                                               | ole of ch | arge pi  | ump cu  | irrents. |       |        |         |        |      |           |           |           |

| М    | Main comparison RSM Comparison divider se select           |    |    |      |     |     |       |       |          | seleo    | ct for m                                              | iain pha  | ase dete | ector.  |          |       |        |         |        |      |           |           |           |

| Aux  | Aux comparison select RSA Comparison divider s             |    |    |      |     |     |       |       | selec    | t for au | uxiliary                                              | phase c   | letector | r.      |          |       |        |         |        |      |           |           |           |

| (    | Fractional Fdac70, Fractional compens<br>Compensation      |    |    |      |     |     |       | nsati | on cha   | irge pu  | mp curr                                               | ent DA    | C, valu  | es 0 to | 255. F   | DAC = | 77 for | best op | D MOD8 | 3.   |           |           |           |

#### C word, length 24 bits

| ADDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ESS |     |     |     |     | AU) | (ILIAF | RY DIV | /IDER  | NAU                  | Х                    |          |                    |        |                  | 0                | P   | LC  | оск | F   | PD  | SP  | ARE |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--------|--------|--------|----------------------|----------------------|----------|--------------------|--------|------------------|------------------|-----|-----|-----|-----|-----|-----|-----|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0   | A13 | A12 | A11 | A10 | A9  | A8     | A7     | A6     | A5                   | A4                   | A3       | A2                 | A1     | A0               | CP1              | CP0 | LD1 | LD0 | PD1 | PD2 | PD3 | LOD |

| Default         0         0         0         0         1         1         1         0         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1 </td <td>1</td> <th>0</th> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>TX<sub>EN</sub></td> <td>тх<sub>ел</sub></td> <td>0</td> <td>0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |     |     |     |     |        |        | 1      | 0                    | 1                    | 1        | 0                  | 0      | TX <sub>EN</sub> | тх <sub>ел</sub> | 0   | 0   |     |     |     |     |     |

| C word select Fixed to 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |     |     |     |        |        |        |                      |                      |          |                    |        |                  |                  |     |     |     |     |     |     |     |

| A–Divider A0A13, Auxiliary divider values 128 to 16384 allow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |     |     |     |     |        |        | wed f  | or div               | ider ra              | tio.     |                    |        |                  |                  |     |     |     |     |     |     |     |

| Charge pump current Ratio CP1, CP0: Charge pump current ratio, see table f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |     |     |     |     |        |        | ole fo | char                 | ge pu                | mp cu    | irrents            |        |                  |                  |     |     |     |     |     |     |     |

| Lock detect output         LD1 LD0           0         Combined main, aux. & offset loop lock detect signal           0         Combined main and aux. lock detect signal present at 10           Main lock detect signal present at the LOCK pin.         11           1         Auxiliary loop lock detect signal present at the LOCK when a section is in power down mode, the lock indicator for the lock indi |     |     |     |     |     |     |        |        |        |                      |                      |          | nt aṫ th<br>CK pir | ne LOO | CK pir           | ı.<br>'          |     |     |     |     |     |     |     |

| Power down PD1=1: power to N–divider, reference divider, main charge pumps, PD1=(<br>PD2=1: power to Aux divider, reference divider, Aux charge pump, PD2=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |     |     |     |     |        |        |        | :0 to po<br>0 to pov | wer dowr<br>ver down | ז.<br>ו. |                    |        |                  |                  |     |     |     |     |     |     |     |

### SA9025

#### Table 3.

#### Main and auxiliary chargepump currents

| CP1 | CP0 | I <sub>PHA</sub> | I <sub>PHP</sub> | I <sub>PHP-SU</sub> | I <sub>PHI_SU</sub> |

|-----|-----|------------------|------------------|---------------------|---------------------|

| 0   | 0   | 1.5xlset         | 3xlset           | 15xlset             | 36xlset             |

| 0   | 1   | 0.5xlset         | 1xlset           | 5xlset              | 12xlset             |

| 1   | 0   | 1.5xlset         | 3xlset           | 15xlset             | 0                   |

| 1   | 1   | 0.5xlset         | 1xlset           | 5xlset              | 0                   |

#### NOTES

I<sub>SET</sub> = Vset/RN; bias current for charge pumps.

CP1 is used to disable the PHI pump.

Iphp\_su is the total current out of PHP in speedup mode.

#### D word, length 24 bits

| A                                                             | ddres                                                                                    | s      |         |   | Po   | ower (   | Contro  | bl     |         |         | N<br>divi |          | SE      | тм      | AD       | Sle<br>Mo |         |        | Te      | est pa | _curre  | ent  |      |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------|---------|---|------|----------|---------|--------|---------|---------|-----------|----------|---------|---------|----------|-----------|---------|--------|---------|--------|---------|------|------|

| 1                                                             | 1 1 0 PC7 PC6 PC5 PC4 PC3 PC2 PC1 F                                                      |        |         |   |      |          |         |        |         |         | M1        | M0       | SE      | ΤM      | AD       | SM1       | SM2     | pai5   | pai4    | pai3   | pai2    | pai1 | pai0 |