#### CS-PD HAMBURG

## Datasheet

# **SAA7115** CVIP2

PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb Filter, High Performance Scaler, I2C Sliced Data Readback and SQ Pixel Output

PRELIMINARY

File under CS-PD Hamburg, PC-P

23 Oct 2001

Contents subject to change without notice.

### **Philips Semiconductors**

**PHILIPS**

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

#### **CONTENTS**

| 1 | DOC        | CUMEN          | Г INFO                                                                                       | 6  |

|---|------------|----------------|----------------------------------------------------------------------------------------------|----|

|   | 1.1        | Revision       | on History                                                                                   | 6  |

| 2 | FEA        | TURES          | ······································                                                       | 6  |

|   | 2.1        | Video          | Acquisition                                                                                  | 6  |

|   | 2.2        | Combf          | ilter Video Decoder                                                                          | 6  |

|   | 2.3        |                | Scaler                                                                                       |    |

|   | 2.4        |                | ata Slicer                                                                                   |    |

|   | 2.5<br>2.6 |                | Generation                                                                                   |    |

|   | 2.7        | Summ           | ary SAA7114 versus SAA7115ary                                                                | ۰٥ |

| 3 |            |                | DESCRIPTION                                                                                  |    |

| 4 |            |                | ERENCE DATA                                                                                  |    |

|   |            |                | INFORMATION                                                                                  |    |

| 5 |            |                |                                                                                              |    |

| 6 |            |                | GRAM                                                                                         |    |

| 7 | PINI       |                |                                                                                              |    |

|   | 7.1        | Pinnin         | g List and Pinning Diagram… <mark>…</mark>                                                   | 13 |

|   | 7.2        |                | onfigurations                                                                                |    |

|   | 7.3        |                | 15 Pin Strapping                                                                             |    |

| 8 | FUN        |                | AL DESCRIPTION                                                                               |    |

|   | 8.1        |                | er <mark></mark>                                                                             |    |

|   |            | 8.1.1          | Analog input processing.                                                                     |    |

|   |            |                | 8.1.1.1 Clamping                                                                             |    |

|   |            | 8.1.2          | Chrominance and luminance processing                                                         |    |

|   |            | 0.1.2          | 8.1.2.1 Chrominance path                                                                     |    |

|   |            |                | 8.1.2.2 Luminance path                                                                       | 32 |

|   |            |                | 8.1. <mark>2.3 Brightness Contrast Saturation (BCS) control and decoder output levels</mark> |    |

|   |            | 8.1.3          | Synchronization                                                                              |    |

|   |            | 8.1.4<br>8.1.5 | Clock generation circuit                                                                     |    |

|   | 8.2        |                | t Formatter                                                                                  |    |

|   | 8.3        |                |                                                                                              |    |

|   |            | 8.3.1          | Acquisition control and task handling (subaddresses 80H, 90H, 91H, 94H to 9FH and C4H to     |    |

|   |            |                | 50                                                                                           |    |

|   |            |                | 8.3.1.1 Input field processing                                                               |    |

|   |            |                | 8.3.1.2 Task handling                                                                        |    |

|   |            | 8.3.2          | Horizontal scaling.                                                                          |    |

|   |            | 0.0.2          | 8.3.2.1 Horizontal prescaler (subaddresses A0H to A7H and D0H to D7H)                        |    |

|   |            |                | 8.3.2.2 Horizontal fine scaling (variable phase delay filter; subaddresses A8H to AFH and    |    |

|   |            |                | D8H to DFH)60                                                                                |    |

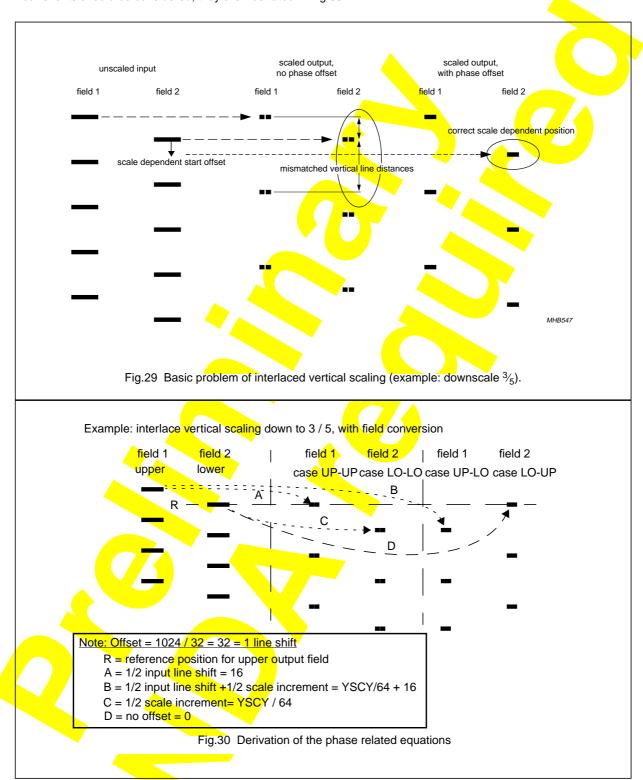

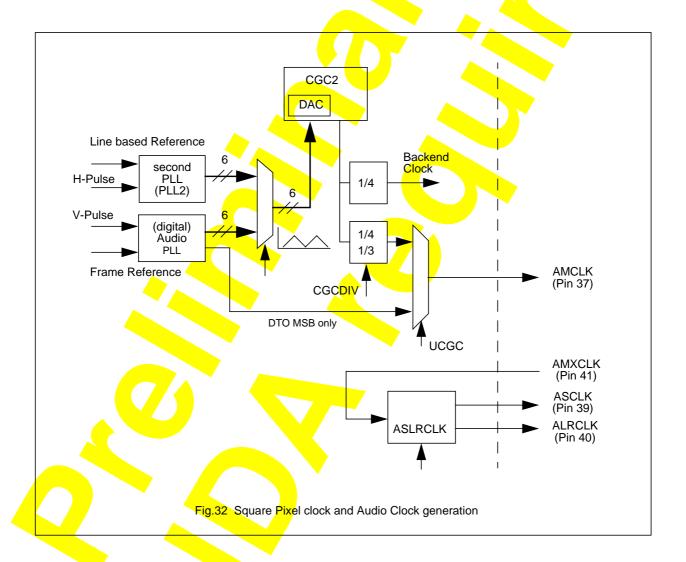

|   |            | 8.3.3          | Vertical sca <mark>ling</mark>                                                               |    |

|   |            |                | 8.3.3.1 Line FIFO buffer (subaddresses 91H, B4H and C1H, E4H)                                |    |

|   |            |                | 8.3.3.2 Vertical scaler (subaddresses B0H to BFH and E0H to EFH)                             |    |

|   | 8.4        | VBI-da         | ata decoder and capture (subaddresses 40H to 7FH)                                            |    |

|   |            | 8.4.1          | VBI Data Slicer                                                                              |    |

|   |            | 8.4.2          | I2C Readback of sliced VBI data                                                              | 67 |

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

|   |    |       | 8.4.3                    | Sliced VI    | BI Data Output at the I-Port                                                      |     |

|---|----|-------|--------------------------|--------------|-----------------------------------------------------------------------------------|-----|

|   |    |       |                          | 8.4.3.1      | Euro WST, US WST and NABTS Data                                                   |     |

|   |    |       |                          | 8.4.3.2      | WSS 625 Data                                                                      | 68  |

|   |    |       |                          | 8.4.3.3      | WSS 525 Data                                                                      | 68  |

|   |    |       |                          | 8.4.3.4      | VPS Data                                                                          |     |

|   |    |       |                          | 8.4.3.5      | Closed Caption                                                                    |     |

|   |    |       |                          | 8.4.3.6      | Moji Data                                                                         |     |

|   |    |       |                          |              |                                                                                   |     |

|   |    |       |                          | 8.4.3.7      | VITC Data                                                                         |     |

|   |    |       |                          | 8.4.3.8      | Open Data Types                                                                   |     |

|   |    | 8.5   | _                        |              | ut interface (subaddresses 84H to 87 <mark>H)</mark>                              |     |

|   |    |       | 8.5.1                    |              | utput formatter (subaddresses 93H a <mark>nd </mark> C3H)                         |     |

|   |    |       | 8.5.2                    | Video FII    | FO (subaddress 86H)                                                               | 71  |

|   |    |       | 8.5.3                    | Text FIF     | 0 <mark></mark>                                                                   | 72  |

|   |    |       | 8.5.4                    | Video / te   | ext arbitration and Data packing (subaddress 86H)                                 | 72  |

|   |    |       |                          | 8.5.4.1      | VBI insertion in SAV/EAV mode (bit SLDOM[3] = '1')                                | 72  |

|   |    |       |                          | 8.5.4.2      | Data Packing (bit IMPAK (86H) and programming of the pulse generator via addr     |     |

|   |    |       |                          |              | FBH)73                                                                            |     |

|   |    |       | 8.5.5                    | Data stre    | eam coding and reference signal generation (subaddresses 84H, 85H and 93H)        | 73  |

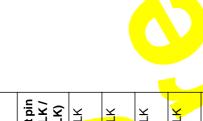

|   |    | 8.6   |                          |              | clock generation (subaddresses 30H to 3FH)                                        |     |

|   |    | 0.0   | 8.6.1                    |              | Pixel Clock Generation                                                            |     |

|   |    |       | 0.0.1                    | -            |                                                                                   |     |

|   |    |       |                          | 8.6.1.1      | The second PLL (PLL2)                                                             |     |

|   |    | 8.7   |                          | clock gene   | eration (subaddresses 30H to 3FH)                                                 | 82  |

|   |    |       | 8.7.1                    |              | ock genera <mark>tion without analog PL</mark> L (CGC2) enha <mark>ncement</mark> |     |

|   |    |       |                          | 8.7.1.1      | Master audio clock                                                                |     |

|   |    |       |                          | 8.7.1.2      | Signals ASCLK and ALRCLK                                                          |     |

|   |    |       | 8.7.2                    | Audio clo    | ock genera <mark>tion with</mark> analog PLL (CGC2) supp <mark>ort</mark>         | 84  |

|   |    |       | 8.7.3                    | Other co     | ntrol signa <mark>ls for audio clock generation</mark>                            | 89  |

| ç | 9  | INPL  | JT/OUT                   | PUT INTE     | RFACES AND PORTS.                                                                 | 90  |

| • |    |       |                          |              | ······································                                            |     |

|   |    | 9.1   | Analog                   | i terminais  | 6 <mark></mark>                                                                   | 90  |

|   |    | 9.2   |                          |              | als                                                                               |     |

|   |    | 9.3   |                          |              | me synchronization signals                                                        |     |

|   |    | 9.4   | Video (                  |              | port (X-port)                                                                     |     |

|   |    |       | 9.4.1                    |              | onfigured as output                                                               |     |

|   |    |       | 9.4.2                    | X-port co    | onfigured as input                                                                | 96  |

|   |    | 9.5   | Image                    | port (I-por  | rt)                                                                               | 96  |

|   |    | 9.6   | Host p                   | ort for 16-l | bit extension of video data I/O (H-port)                                          | 98  |

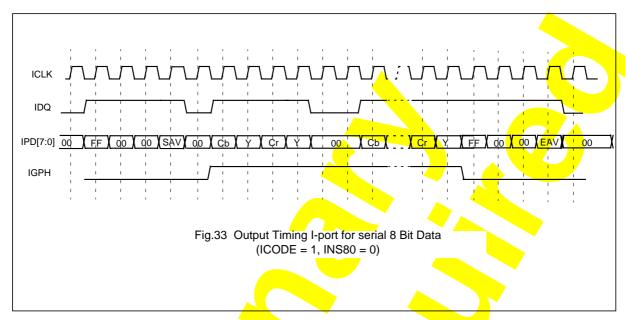

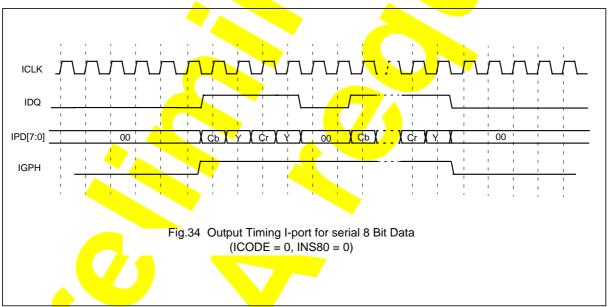

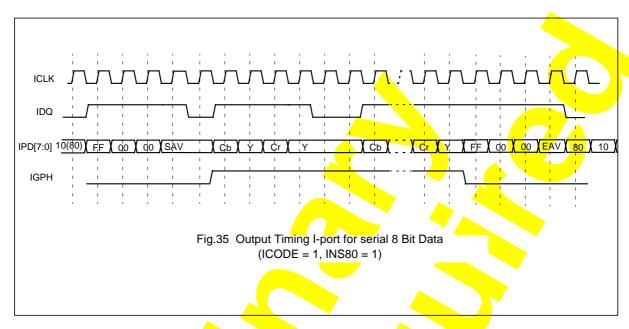

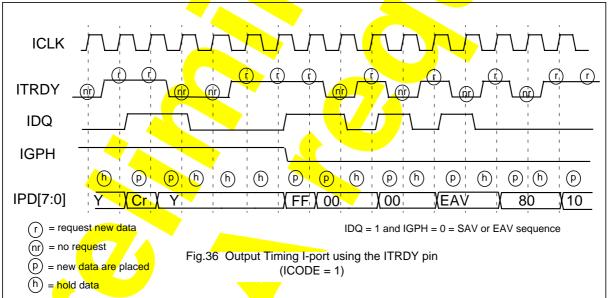

|   |    | 9.7   | Basic i                  | nput and c   | output timing diagrams I-port and X-port                                          | 99  |

|   |    |       |                          |              | tput timing                                                                       |     |

|   |    |       | 9.7.2                    |              | put timing                                                                        |     |

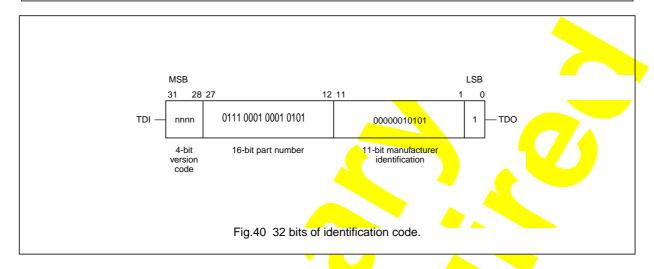

| , | 10 | DOL I | -                        |              | EST                                                                               |     |

|   |    |       |                          |              |                                                                                   |     |

|   |    | 10.1  | In <mark>itia</mark> liz | ation of bo  | oundary scan circuit                                                              | 104 |

|   |    |       |                          |              | tion codes                                                                        |     |

| 4 | 11 | LIMI  | TING V                   | ALUES        | , <mark>,</mark>                                                                  | 106 |

|   |    |       |                          |              |                                                                                   |     |

|   |    |       |                          |              | ERI <mark>stic</mark> s                                                           |     |

| 1 | 13 | CHA   | RACTE                    | RISTICS.     | <mark></mark>                                                                     | 107 |

|   |    |       |                          |              | RMATION                                                                           |     |

|   |    |       |                          |              |                                                                                   |     |

| 1 | 15 | DEV   | ICE PR                   | OGRAMM       | <mark>IING OVERVIEW</mark>                                                        | 116 |

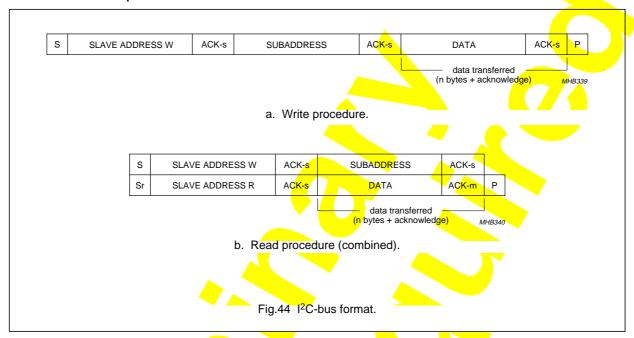

|   |    | 15.1  | I2C-bu                   | s descripti  | ion                                                                               | 116 |

|   |    |       |                          |              | <del></del>                                                                       |     |

|   |    |       | •                        |              |                                                                                   |     |

| 1 | 10 | ULI   | AILED L                  | JESCKIP      | TION OF THE CONTROL REGISTERS                                                     | 127 |

Confidential - NDA required

Filename: SAA7115\_Datasheet.fm

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

| 16.1 | Chip Version / Ident Register                                                              |                      |

|------|--------------------------------------------------------------------------------------------|----------------------|

|      | 16.1.1 Chip Version                                                                        |                      |

|      | 16.1.2 Chip ID                                                                             |                      |

| 16.2 | Programming Register Decoder                                                               |                      |

|      | 16.2.1 Subaddress 01 Analog Input Control 0, Increment Delay                               |                      |

|      | 16.2.2 Subaddress 02 Analog Input Control 1                                                | 29                   |

|      | 16.2.3 Subaddress 03 Analog Input Control 2                                                | 32                   |

|      | 16.2.4 Subaddress 04 Analog Input Control 3                                                | 33                   |

|      | 16.2.5 Subaddress 05 Analog Input Control 4                                                | 33                   |

|      | 16.2.6 Subaddress 06 Horizontal Sync Start                                                 | 33                   |

|      | 16.2.7 Subaddress 07 Horizontal Sync Stop                                                  | 34                   |

|      | 16.2.8 Subaddress 08 Sync Control                                                          |                      |

|      | 16.2.9 Subaddress 09 Luminance control                                                     |                      |

|      | 16.2.10 Subaddress 0A Decoder Brightness                                                   | 37                   |

|      | 16.2.11 Subaddress 0B Decoder Contrast                                                     |                      |

|      | 16.2.12 Subaddress 0C Decoder Saturation                                                   |                      |

|      | 16.2.13 Subaddress 0D Chrominance Hue                                                      |                      |

|      | 16.2.14 Subaddress 0E Chrominance Control 1                                                |                      |

|      | 16.2.15 Subaddress 0F Chrominance Gain Control                                             |                      |

|      | 16.2.16 Subaddress 10 Chrominance/Luminance Control 214                                    |                      |

|      | 16.2.17 Subaddress 11 Mode / Delay Control                                                 |                      |

|      | 16.2.18 Subaddress 12 RTS0/1 Output Control                                                |                      |

|      | 16.2.19 Subaddress 13 and 1B RT / X-port Output Control                                    |                      |

|      | 16.2.20 Subaddress 14 Analog / ADC / Auto/ Compatibility Control                           |                      |

|      | 16.2.21 Subaddress 15, 17VGATE Start                                                       |                      |

|      | 16.2.22 Subaddress 16, 17 VGATE Stop                                                       | 51                   |

|      | 16.2.23 Subaddress 17 Misc./VGATE-MSB's                                                    |                      |

|      | 16.2.24 Subaddress 18 Raw data Gain Control                                                |                      |

|      | 16.2.25 Subaddress 19 Raw data Offset Control                                              | 53<br>53             |

|      | 16.2.26 Subaddress 1A Color Killer Level Control                                           | 53<br>54             |

|      | 16.2.27 Subaddress 1B Misc. Chroma Control                                                 | 54                   |

|      | 16.2.28 Subaddress 1C Enhanced Combfilter Control 1                                        | 5 <del>4</del><br>55 |

|      | 16.2.29 Subaddress 1D Enhanced Combiller Control 2                                         |                      |

|      | 16.2.30 Subaddresses 1E, 1F Status Bytes Video Decoder (read-only register)                |                      |

| 16.2 | Programming Register Audio Clock Generation                                                |                      |

| 10.3 | 16.3.1 Subaddresses 30 to 32 AMCLK Cycles per Field                                        | 50<br>50             |

|      |                                                                                            |                      |

|      | 16.3.2 Subaddresses 34 to 36 AMCLK Nominal Increment                                       |                      |

|      | 16.3.4 Subaddress 39 Ratio ASCLK to ALRCLK                                                 |                      |

|      |                                                                                            |                      |

| 40.4 | 16.3.5 Subaddress 3A Audio Clock Control 15                                                |                      |

| 16.4 | Programming Register VBI data slicer                                                       |                      |

|      | 16.4.1 Subaddress 40 Basic Slicer Settings                                                 |                      |

|      | 16.4.2 Subaddress 41 to 57 Line Control Register                                           |                      |

|      | 16.4.3 Subaddress 58 Programmable Framing Code                                             |                      |

|      | 16.4.4 Subaddress 59 Horizontal Offset                                                     |                      |

|      | 16.4.5 Subaddress 5A Vertical Offset                                                       |                      |

|      | 16.4.6 Subaddress 5B Field Offset, MSB's H/V-Offsets                                       |                      |

|      | 16.4.7 Subaddress 5D; SLDOM Codes                                                          |                      |

|      | 16.4.8 Subaddress 5E SDID codes                                                            |                      |

|      | 16.4.9 Subaddress 5E (read-only register)                                                  |                      |

|      | 16.4.10 Subaddress 66 to 7F I2C Readback of decoded VBI Data (read-only register)          |                      |

|      | 16.4.10.1 Subaddress 66 to 6A I2C Readback of Closed Caption Data (CC525 and CC625) (read- | only                 |

|      | register)167                                                                               |                      |

|      | 16.4.10.2 Subaddress 6B to 71 I2C Readback of Closed Caption Data (WSS525 and WSS625)      |                      |

|      |                                                                                            |                      |

Confidential - NDA required page 4

Filename: SAA7115\_Datasheet.fm Last edited by H. Lambers

| Philips Semiconductors | CVIP2                | Date:    | 10/23/01 |

|------------------------|----------------------|----------|----------|

| CS-PD Hamburg          | Datasheet<br>SAA7115 | Version: | 0.67     |

|   |      | (read-only register)168                                                                  |     |

|---|------|------------------------------------------------------------------------------------------|-----|

|   |      | 16.4.10.3 Subaddress 72 to 76 I2C Readback of Gemstar1x Data (read-only register)        | 169 |

|   |      | 16.4.10.4 Subaddress 77 to 7F I2C Readback of Gemstar2x Data (read-only register)        | 170 |

|   | 16.5 | Programming Register - Interfaces and Scaler Part                                        | 171 |

|   |      | 16.5.1 Subaddress 80: Global Settings                                                    | 171 |

|   |      | 16.5.2 Subaddress 83 to 87: Global Interface Configurations                              | 173 |

|   |      | 16.5.3 Subaddress 88: Sleep and Power save control                                       | 180 |

|   |      | 16.5.4 Subaddress 8F (read-only register): status information scaler part                | 181 |

|   |      | 16.5.5 Subaddress 90: event handler control                                              |     |

|   |      | 16.5.6 Subaddress 91 to 93: scaler input and I-port output configuration                 |     |

|   |      | 16.5.7 Subaddress 94 to 9B: Scaler Input Acquisition Window Definition                   |     |

|   |      | 16.5.8 Subaddress 9C to 9F: Scaler Output Window Definition                              | 187 |

|   |      | 16.5.9 Subaddress A0 to A2: Prescaling and FIR filtering                                 |     |

|   |      | 16.5.10 Subaddress A4 to A6: Brightness, Contrast and Saturation Control                 |     |

|   |      | 16.5.11 Subaddress A8 to AE: Horizontal Phase Scaling                                    |     |

|   |      | 16.5.12 Subaddress B0 to BF: Vertical Scalin <mark>g C</mark> on <mark>trol</mark>       |     |

|   | 16.6 | Programming Register - second PLL (PLL2) <mark>and Puls</mark> e <mark>Ge</mark> nerator |     |

|   |      | 16.6.1 Subaddress F0 to F5 and FF: second PLL (PLL2) Programming Parameters              |     |

|   |      | 16.6.2 Subaddress F6 to FB: Pulse Generator Programming                                  |     |

| 7 | PRO  | OGRAMMING START SET-UP                                                                   | 201 |

|   | 17.1 | Decoder part                                                                             | 201 |

|   | 17.2 | Audio clock generation part                                                              | 206 |

|   |      | Data slicer and data type control part                                                   |     |

|   |      | Scaler and interfaces                                                                    |     |

|   |      | 17.4.1 Examples                                                                          | 209 |

|   | 17.5 | PLL2 and pulse generator control part                                                    | 212 |

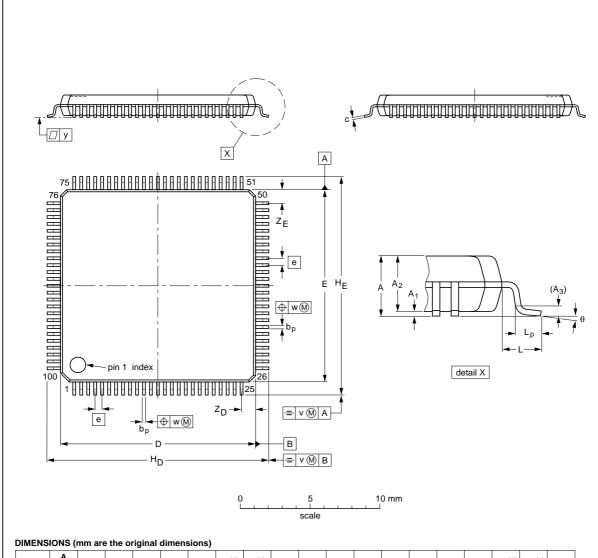

| 8 | PACI | KAGE OUTLINE                                                                             | 214 |

Confidential - NDA required page 5

Filename: SAA7115\_Datasheet.fm Last edited by H. Lambers

| Philips Semiconductors | CVIP2                | Date:    | 10/23/01 |

|------------------------|----------------------|----------|----------|

| CS-PD Hamburg          | Datasheet<br>SAA7115 | Version: | 0.67     |

#### 1 DOCUMENT INFO

#### 1.1 Revision History

| VERSION NO | REVISION<br>DATE | DESCRIPTION OF STATUS                                                               | ВУ            |

|------------|------------------|-------------------------------------------------------------------------------------|---------------|

| 0.5        | 5 Oct 2001       | Initial Version                                                                     | H. Lambers    |

| 0.51       | 9 Oct 2001       | Fixed LCBW recommended setting                                                      | H. Lambers    |

| 0.52       | 9 Oct 2001       | VBSL setting changed, scale <mark>r an</mark> d PLL2 examp <mark>les</mark> , sect. | A. Mittelberg |

| 0.6        | 10 Oct 2001      | Added application examples                                                          | H. Lambers    |

| 0.65       | 18 Oct 2001      | Status at CQS                                                                       | H. Lambers    |

| 0.66       | 19 Oct 2001      | Minor updates                                                                       | H. Lambers    |

| 0.67       | 23 Oct 2001      | Fixed application example drawing                                                   | H. Lambers    |

#### 2 FEATURES

#### 2.1 Video Acquisition

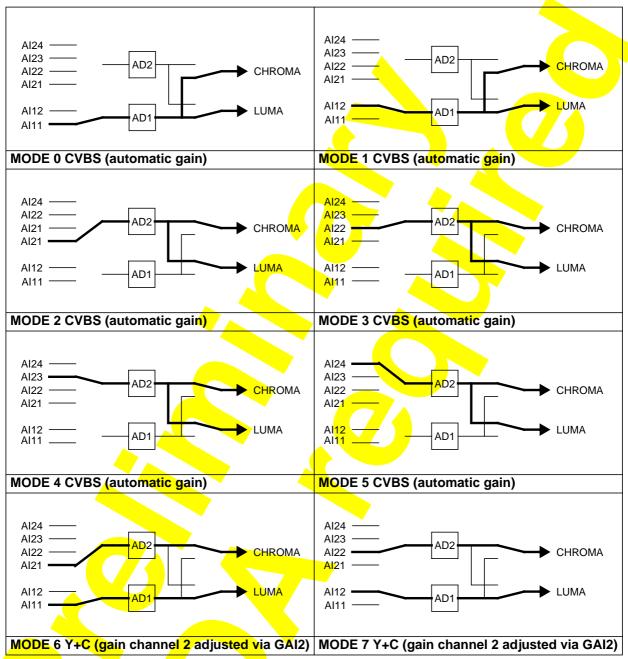

- Six analog inputs, internal analog source selectors, (e.g.: 6x CVBS or (2 x YC and 2 CVBS) or (1 x YC and 4xCVBS)

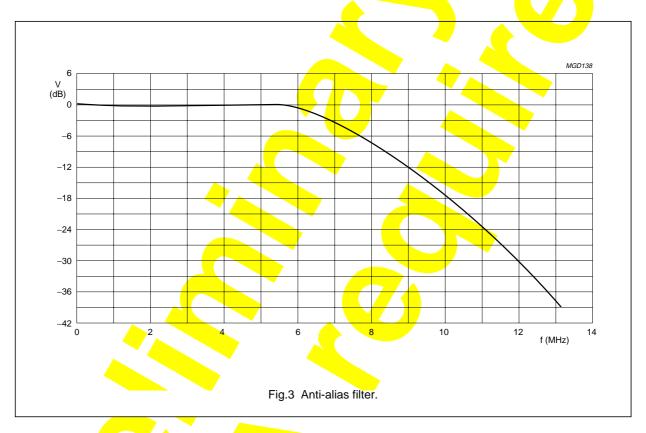

- Two built in analog anti-alias filters

- Two improved 9 Bit CMOS analog-to-digital converter in differential CMOS style at two-fold ITU-656 oversampling (27MHz)

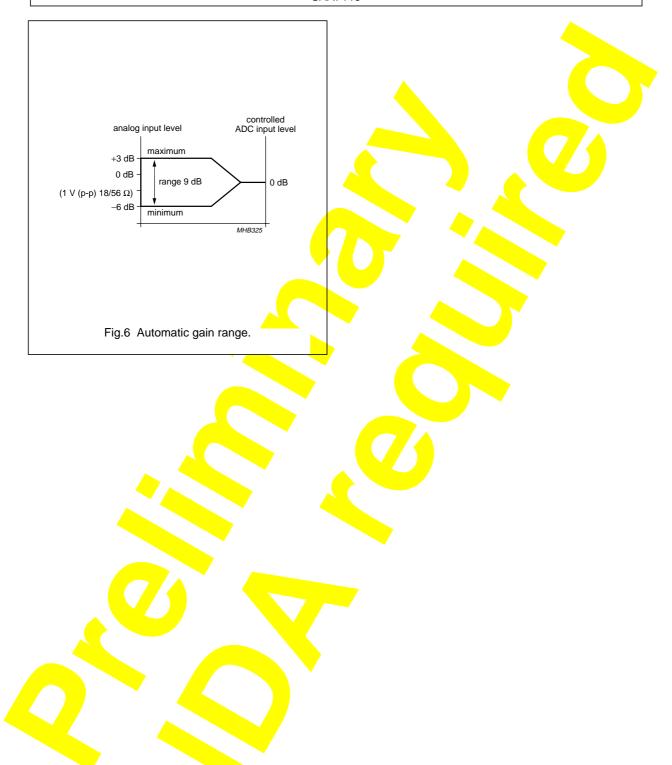

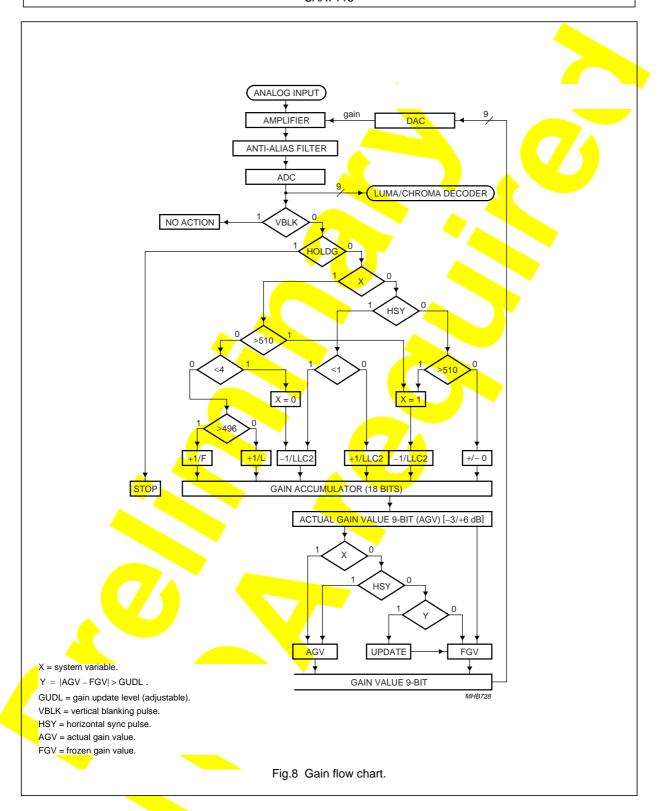

- Fully programmable static gain or automatic gain control (AGC) for the selected CVBS or Y/C channel

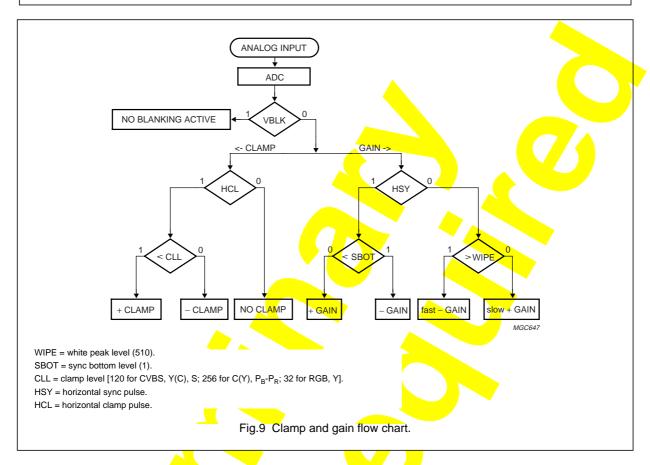

- Automatic Clamp Control (ACC) for CVBS, Y and C

- Switchable white Peak Control Two 9-bit Video CMOS AD Converters, digitized CVBS or Y/C

- signals are available on the expansion port (X-port)

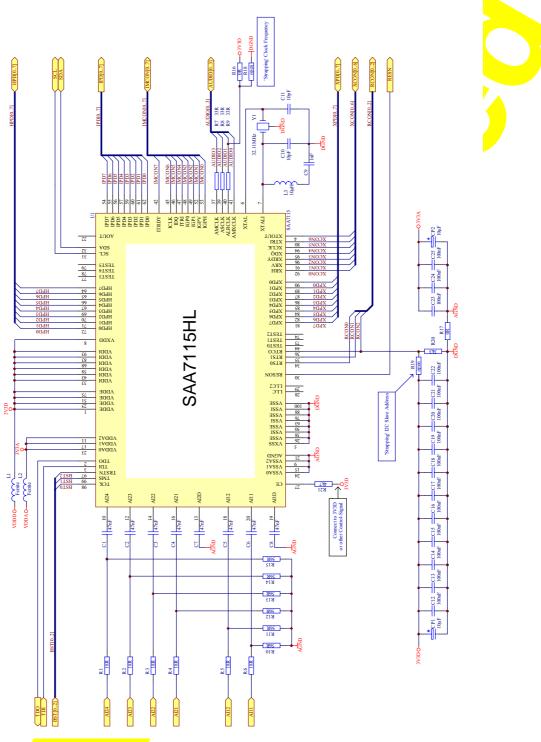

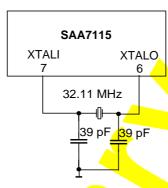

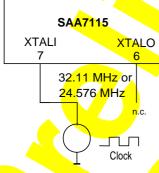

- Requires only one crystal (32.11 MHz or 24.576 MHz) for all standards

- Independent Gain and Offset adjustment for raw data path

#### 2.2 Combfilter Video Decoder

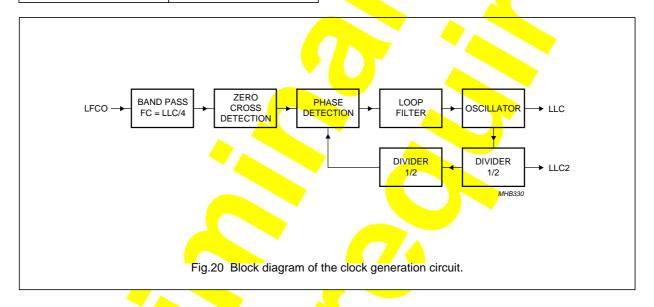

- Digital PLL for Synchronization and Clock Generation from all Standards and Non Standard Video Sources e.g. consumer grade VTR

- Automatic detection of 50/60Hz field frequency, and automatic recognition of all common broadcast standards

- Enhanced Horizontal and vertical Sync Detection

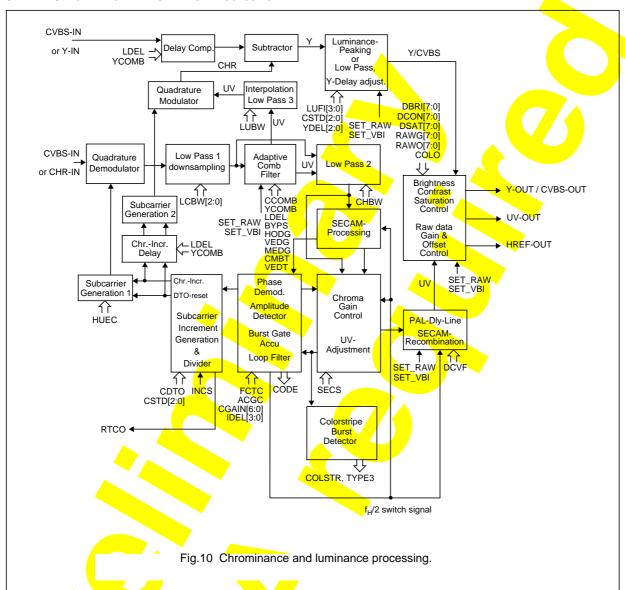

- Luminance and chrominance signal processing for

- PAL BGDHIN,

- Combination-PAL N,

- P<mark>AL M</mark>,

- NTSC M,

- NTSC-Japan,

- NTSC 4.43 and

- SECAM (50 Hz / 60 Hz)

- PAL delay line for correcting PAL phase errors

Confidential - NDA required

Filename: SAA7115\_Datasheet.fm

page 6

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

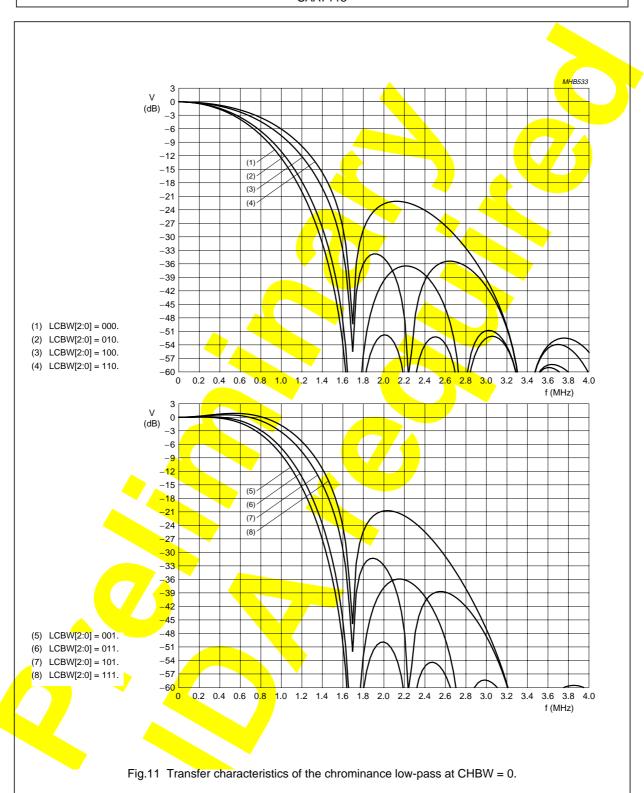

- Improved 2/4-line comb filter for two dimensional chrominance/luminance-separation operating with adaptive combfilter parameters.

- Increased Luminance and Chrominance Bandwidth for all PAL and NTSC-standards

- Reduced cross colour and cross luminance artefacts

- Independent Brightness Contrast Saturation (BCS) adjustment for decoder-part

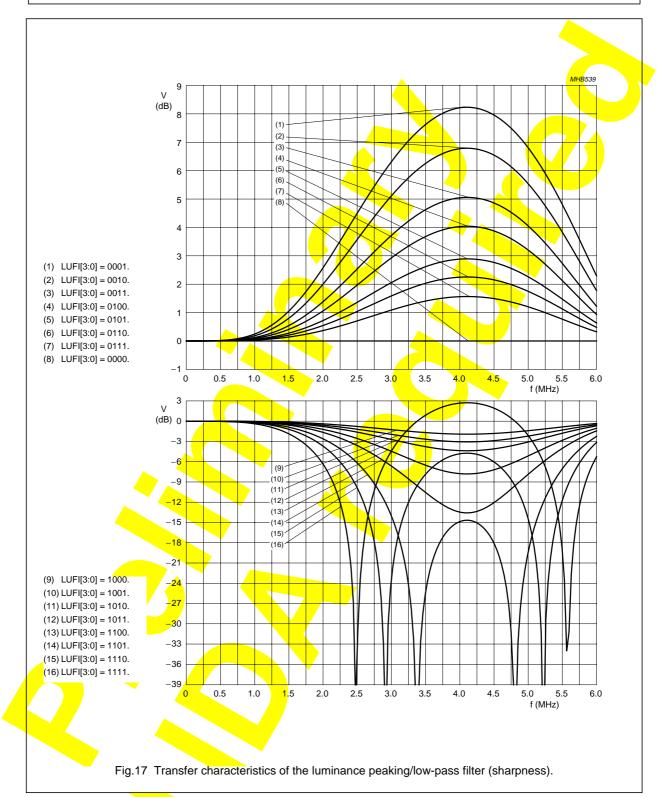

- User programmable sharpness control

- · Detection of Copy protected input signals:

- according to Macrovision standard

- indicating the level of protection

- Automatic TV/VCR detection

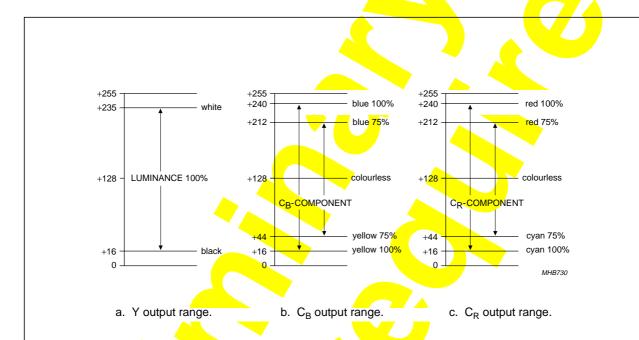

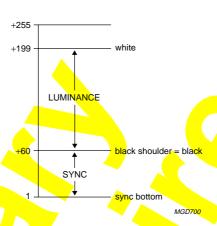

- 10 bit wide video output at combfilter video decoder

- X-port video output either as:

- Noise shaped 8 bit ITU-656 video or

- Full 10 bit ITU-656 interface (DC-performance 9 Bit)

#### 2.3 Video Scaler

ı

- Horizontal and Vertical Down-Scaling and Up-Scaling to randomly sized windows

- Horizontal and Vertical Scaling range: variable zoom to 1/64 (icon) (Note: H and V zoom are restricted by the transfer data rates)

- Vertical Scaling with Linear Phase Interpolation and Accumulating Filter for Anti-Aliasing (6 bit phase accuracy)

- Conversion to Square Pixel format

- Generation of a video output stream with improved synchronisation grid at the I-Port

- Two independent programming sets for scaler part, to define two "ranges" per field or sequences over frames

- Fieldwise switching between Decoder-part and Expansion port (X-port) input

- Brightness, contrast and saturation controls for scaled outputs

#### 2.4 VBI Data Slicer

- Versatile VBI-data decoder, slicer, clock regeneration and byte synchronization, e.g. for:

- WST525 / WST625 (CCST)

- VPS

- US / European Close Caption (CC),

- WSS525 (CGMS), WSS625,

- US NABTS

- VITC 525 / VITC 625

- GEMSTAR 1x

- GEMSTAR 2x

- Moji

- I<sup>2</sup>C Readback of the following decoded data types:

- US Close Caption (CC)

- European Close Caption (CC)

Confidential - NDA required

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

- WSS525 (CGMS)

- WSS625 (CGMS)

- GEMSTAR 1x

- GEMSTAR 2x

#### 2.5 Clock Generation

- On-Chip Line Locked Clock Generation according ITU601

- Generation of a frame locked Audio Master Clock to support a constant number of audio clocks per video field.

- · Second onboard analog PLL to be used for:

- On-Chip Line Locked Square Pixel Clock Generation for PAL and NTSC Square Pixel Video Output or

- optionally Generation of a low jitter frame locked Audio Clock from the Audio Master Clock through reuse of the analog Square Pixel PLL. Supported audio clock frequencies are 256\*fs, 384\*fs and 512\*fs (fs = 32 KHz, 44.1 KHz or 48 KHz).

#### 2.6 General Features

- CMOS 3.3 V device with 5 V tolerant digital inputs and I/O ports

- Programming via serial I<sup>2</sup>C-bus, full read-back ability by an external controller, bit rate up to 400 kbit/s

- Software controlled power saving stand-by modes

- Boundary Scan Test circuit complies to the IEEE Std. 1149.b1 -1994

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

#### 2.7 Summary SAA7114 versus SAA7115

Table 1 SAA7114 versus SAA7115

I

| ISSUE                                        | SAA7114                                                                   | SAA7115                                                                                                                                                                                      |

|----------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin compatibility                            | reference pinning                                                         | pin-compatible to SAA7114                                                                                                                                                                    |

| Analog Frontend                              | 2 x 9 bit A/D- converters                                                 | 2 x Low Noise 9 bit A/D- converters                                                                                                                                                          |

|                                              | 13.5 MHz CCIR sampling                                                    | 27 MHz CCIR 2x-oversampling                                                                                                                                                                  |

|                                              | Standard White-Peak Control watching raw data                             | Stand <mark>ard</mark> White-Peak Control watching raw data plus baseband luminance data                                                                                                     |

| Combfilter Decoder                           | 4 lines adaptive comb filter                                              | Improved 4 lines adaptive comb filter (reduced artifacts)                                                                                                                                    |

|                                              | Manual TV/VCR sw <mark>itc</mark> hing                                    | Automatic TV/VCR detection                                                                                                                                                                   |

|                                              | Semi-automatic color stan <mark>dard det</mark> ecti <mark>on</mark>      | Fully-automatic color standard detection                                                                                                                                                     |

|                                              | Regular SECAM 50 Hz                                                       | Regula <mark>r SECAM</mark> 50 Hz and SECAM 60<br>Hz (Vietnam)                                                                                                                               |

|                                              | Color overflow detection                                                  | Automatic color reducer (avoids color limitation with low burst)                                                                                                                             |

|                                              | Safe lock for VCR feature modes                                           | Extended safe lock for VCR feature modes                                                                                                                                                     |

|                                              | Fast frame lock (ca. 2 fields)                                            | Ultra-fast frame lock (almost 1 field)                                                                                                                                                       |

| Macrovision<br>Detection                     | 'Pseudo Sync.'Macrovision Detection only                                  | Comprehensive Macrovision Detection: - 'Pseudo Sync.' detection and/or - Split Burst detection (Type 2 / Type 3)                                                                             |

| Scaled Video Output                          | Generation of embedded ITU-656 auxiliary codes at the I-Port video output | Generation of embedded ITU-656  auxiliary codes at the I-Port video output with improved synchronization raster for VCR signals                                                              |

| Clock Generation                             | Scaling to Square Pixel Data representation                               | Scaling to Square Pixel Data<br>representation with extra integrated<br>clock-PLL (PLL2, CGC2) to generate<br>physical Square Pixel Clock signal of 29.5<br>MHz (PAL) or 24.5454 MHz (NTSC). |

|                                              | Field- locked audio clock (constant number of clock cycles per field)     | Frame- locked audio clock (constant number of clock cycles per frame), optionally through analog PLL (CGC2)                                                                                  |

| VBI Data <mark>Slic</mark> ing and<br>Output | Versatile VBI- data slicer                                                | Versatile VBI- data slicer, incl. CGMS (Line 20 NTSC) and GemStar 2x (EPG)                                                                                                                   |

|                                              | Output of sliced data embedded into I-Port output stream                  | Output of sliced data embedded into I-Port output stream and optionally per I2C register readback for CC, CGMS, Gemstar1x and Gemstar2x,                                                     |

|                                              |                                                                           |                                                                                                                                                                                              |

Confidential - NDA required page 9

Filename: SAA7115\_Datasheet.fm Last edited by H. Lambers

| Philips Semiconductors | CVIP2                | Date:    | 10/23/01 |

|------------------------|----------------------|----------|----------|

| CS-PD Hamburg          | Datasheet<br>SAA7115 | Version: | 0.67     |

#### 3 GENERAL DESCRIPTION

ı

The SAA7115 is a video capture device for various applications ranging from small screen products like e.g. digital settop boxes, personal video recording applications to big screen devices like e.g. LCD projectors due to it's improved combfilter performance and 10 bit video output capabilities.

The SAA7115 is a combination of a two channel analog preprocessing circuit including Source-Selection, Anti-Aliasing Filter and A/D-converter, an Automatic Clamp and Gain Control, two Clock Generation Circuits (CGC1, CGC2), a Digital Multi Standard Decoder containing two-dimensional chrominance/luminance separation by an improved adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and down scaling and a Brightness-Contrast- Saturation- Control circuit.

The decoder is based on the principle of line-locked clock decoding and is able to decode the colour of PAL, SECAM and NTSC signals into ITU-601 compatible colour component values. The SAA7115 accepts as analog inputs CVBS or S-Video (Y-C) from TV or VCR sources, including weak and distorted signals.

The expansion port (X-port) for digital video (bi-directional half duplex, D1 compatible) can be used either to output unscaled video using 10 bit or 8 bit dithered resolution or to connect to other external digital video sources for reuse of the SAA7115 scaler features.

The enhanced image port (I-port) of the 7115 supports 8 (16) bit wide output data with auxiliary reference data for interfacing to e.g. VGA controllers, settop box applications etc. It is also possible to output video in Square Pixel formats accompanied by a square pixel clock of the appropriate frequency.

In parallel SAA7115 incorporates also provisions for capturing the serially coded data in the vertical blanking interval (VBI-data) of several standards. Three basic options are available to transfer the VBI data to other devices:

- capturing raw video samples, after interpolation to the required output data rate, using the scaler and transferring the data to a device connected to the I-port,

- slicing the VBI data using the build in VBI data slicer (data recovery unit) and transferring the data to a device connected to the I-port

- slicing the VBI data using the build in VBI data slicer and reading out the sliced data via the I<sup>2</sup>C bus (for several slow VBI data type standards only)

SAA7115 incorporates also a frame locked audio clock generation. This function ensures that there is always the same number of audio samples associated with a frame, or a set of fields. This prevents the loss of sychronisation between video and audio, during capture or playback. Furthermore the second analog onboard PLL optionally can be used to enhance this audio clock to a low jitter frame locked audio clock.

The SAA7115 is controlled via I<sup>2</sup>C-bus (full write / read capability for all programming registers, bit rate up to 400 kbits/s)

Confidential - NDA required

Filename: SAA7115\_Datasheet.fm

page 10

| Philips Semiconductors | CVIP2                | Date:    | 10/23/01 |

|------------------------|----------------------|----------|----------|

| CS-PD Hamburg          | Datasheet<br>SAA7115 | Version: | 0.67     |

#### 4 QUICK REFERENCE DATA

I

I

| SYMBOL            | PARAMETER                                           | MIN | TYP    | MAX | UNIT |

|-------------------|-----------------------------------------------------|-----|--------|-----|------|

| V <sub>DDx</sub>  | digital supply voltage                              | 3.0 | 3.3    | 3.6 | ٧    |

| V <sub>DDCx</sub> | digital supply voltage range core                   | 3.0 | 3.3    | 3.6 | V    |

| $V_{DDA}$         | analog supply voltage range                         | 3.1 | 3.3    | 3.5 | ٧    |

| T <sub>amb</sub>  | ambient temperature range                           | 0   | -      | 70  | °C   |

| P <sub>A+D</sub>  | analog and digital power consumption <sup>(1)</sup> | -   | t.b.d. | -   | W    |

<sup>1.</sup> Power consumption is measured in CVBS-input mode (only one ADC active) and 8 bit image port output mode, expansion port is tristated

#### 5 ORDERING INFORMATION

| EXTENDED TYPE |      | PACI         | KAGE     |            |

|---------------|------|--------------|----------|------------|

| NUMBER        | PINS | PIN POSITION | MATERIAL | CODE       |

| SAA7115       | 100  | LQFP100      | Plastic  | SOT407-CD5 |

Confidential - NDA required page 11

Filename: SAA7115\_Datasheet.fm Last edited by H. Lambers

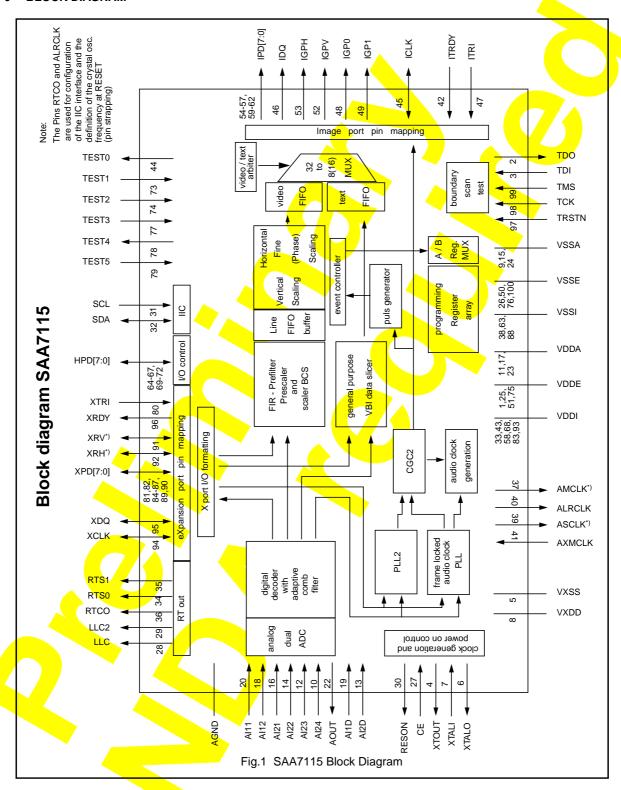

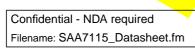

#### **6 BLOCK DIAGRAM**

I

Confidential - NDA required Filename: SAA7115\_Datasheet.fm

page 12

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

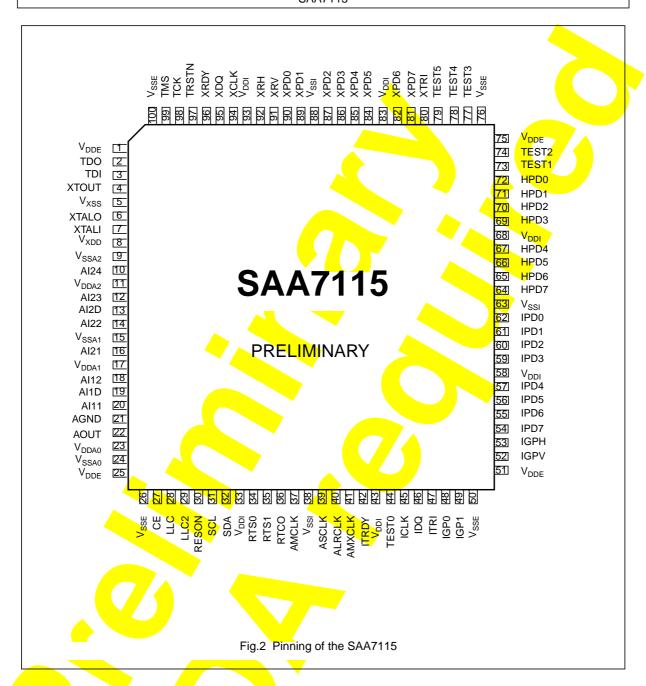

#### 7 PINNING

#### 7.1 Pinning List and Pinning Diagram

Table 2

Pinning List SAA7115

| SYMBOL            | PIN | I/O/P | DESCRIPTION                                                                                                                                 |

|-------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDE</sub>  | 1   | Р     | digital supply voltage 3.3 V (external pad supply)                                                                                          |

| TDO               | 2   | 0     | Test Data Output for Boundary Scan Test (2)                                                                                                 |

| TDI               | 3   | I     | Test Data Input for Boundary Scan Test (with internal pull-up)(2)                                                                           |

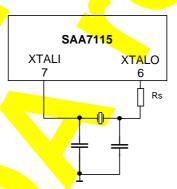

| XTOUT             | 4   | 0     | crystal oscillator output signal, auxiliary signal                                                                                          |

| V <sub>XSS</sub>  | 5   | Р     | ground pin for crystal oscillator                                                                                                           |

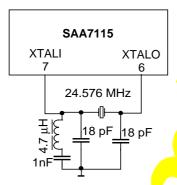

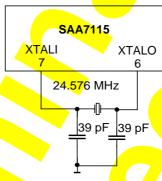

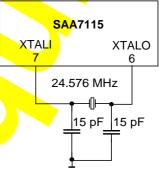

| XTALO             | 6   | 0     | 24.576 (32.11) MHz crystal oscillator output; not connected if XTALI is driven by an external single-ended oscillator.                      |

| XTALI             | 7   | I     | Input terminal for 24.576 (32.11) MHz crystal oscillator or connection of external oscillator with TTL compatible square wave clock signal. |

| $V_{XDD}$         | 8   | Р     | supply voltage pin of crystal oscillator                                                                                                    |

| $V_{\rm SSA2}$    | 9   | Р     | ground for analog inputs Al2x                                                                                                               |

| Al24              | 10  | I     | analog input 24                                                                                                                             |

| $V_{\rm DDA2}$    | 11  | Р     | analog supply voltage for analog inputs Al2x (3.3V)                                                                                         |

| Al23              | 12  |       | analog input 23                                                                                                                             |

| Al2D              | 13  | 1     | differential input for ADC channel 2 (pins Al24, Al23, Al22, Al21)                                                                          |

| Al22              | 14  | Ī     | analog input 22                                                                                                                             |

| $V_{\rm SSA1}$    | 15  | Р     | ground for analog inputs Al1x                                                                                                               |

| Al21              | 16  | ı     | analog input 21                                                                                                                             |

| $V_{DDA1}$        | 17  | Р     | analog supply voltage for analog inputs Al1x (3.3V)                                                                                         |

| Al12              | 18  | I     | analog input 12                                                                                                                             |

| AI1D              | 19  | ı     | differential input for ADC channel 1 (pins Al12, Al11)                                                                                      |

| Al11              | 20  | I_    | analog input 11                                                                                                                             |

| AGND              | 21  | Р     | analog ground connection                                                                                                                    |

| AOUT              | 22  | 0     | Analog test output (do not connect)                                                                                                         |

| $V_{DDA0}$        | 23  | Р     | analog positive supply voltage for both internal CGC (Clock Generation Circuit) (3.3V)                                                      |

| V <sub>SSA0</sub> | 24  | Р     | analog ground for internal CGC                                                                                                              |

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

| SYMBOL           | PIN | I/O/P  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DDE}$        | 25  | Р      | digital supply voltage 3.3 V (external pad supply)                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SSE</sub> | 26  | Р      | digital ground (external pad supply)                                                                                                                                                                                                                                                                                                                                                                                       |

| CE               | 27  | I      | Chip Enable or RESET input (with internal pull up)                                                                                                                                                                                                                                                                                                                                                                         |

| LLC              | 28  | 0      | line-locked system clock output (27 MHz nominal), for backward compatibility, do not use for new applications                                                                                                                                                                                                                                                                                                              |

| LLC2             | 29  | 0      | line locked clock/2 out <mark>put (13.5 MHz nominal)</mark> for backward compatibility, do not use for new applications                                                                                                                                                                                                                                                                                                    |

| RESON            | 30  | 0      | RESet Output Not signal                                                                                                                                                                                                                                                                                                                                                                                                    |

| SCL              | 31  | I (/O) | IIC serial clock line (with inactive output path)                                                                                                                                                                                                                                                                                                                                                                          |

| SDA              | 32  | I/O    | IIC serial data line                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DDI</sub> | 33  | Р      | digital supply voltage 3.3 V internal core supply)                                                                                                                                                                                                                                                                                                                                                                         |

| RTS0             | 34  | 0      | real time status or sync information, controlled by subaddr. "11h and 12h"                                                                                                                                                                                                                                                                                                                                                 |

| RTS1             | 35  | 0      | real time status or sync information, controlled by subaddr. "11h and 12h"                                                                                                                                                                                                                                                                                                                                                 |

| RTCO             | 36  | (1/) 0 | Real Time Control Output: contains information about actual system clock frequency, field rate, odd/even sequence, decoder status, subcarrier phase and frequency and PAL sequence (according to RTC level 3.1, refer to external document "RTC Functional Specification" for details), can be strapped to supply via a 3.3 kOhm resistor to change the default IIC-wr-addresses from 42/43 (internal pull down) to 40/41. |

| AMCLK            | 37  | 0      | audio master clock output                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SSI</sub> | 38  | Р      | digital ground (internal core supply)                                                                                                                                                                                                                                                                                                                                                                                      |

| ASCLK            | 39  | 0      | audio serial clock output                                                                                                                                                                                                                                                                                                                                                                                                  |

| ALRCLK           | 40  | (I/) O | audio left/right clock output, Can be strapped to supply via a 3.3 kOhm resistor indicate that the default 24.576 MHz crystal (internal pull down) has been replaced by a 32.11 MHz crystal.                                                                                                                                                                                                                               |

| AMXCLK           | 41  | ı      | audio m <mark>aster e</mark> xternal clock input (typing error corrected)                                                                                                                                                                                                                                                                                                                                                  |

| ITRDY            | 42  | I_     | target ready input, image port (with internal pull up)                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DDI</sub> | 43  | Р      | digital supply voltage 3.3 V (internal core supply)                                                                                                                                                                                                                                                                                                                                                                        |

| TEST0            | 44  | 0      | do not connect, reserved for future extensions and for <b>Testing</b> : scan output                                                                                                                                                                                                                                                                                                                                        |

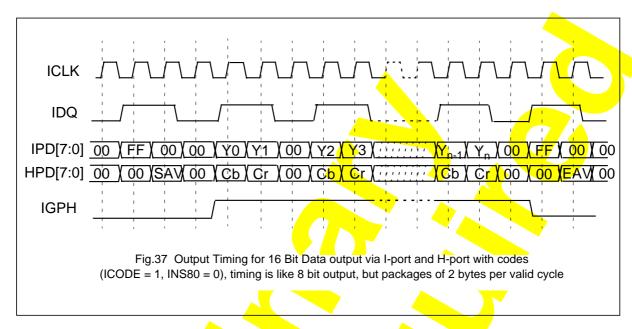

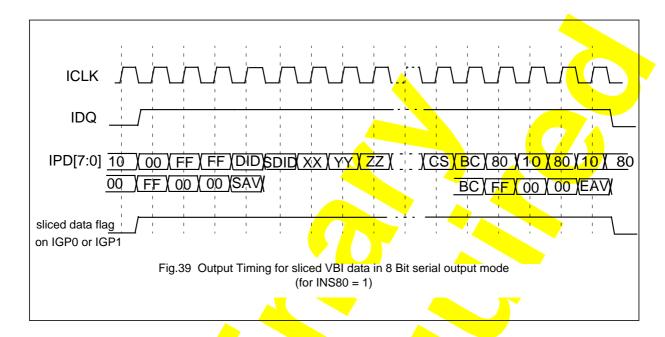

| ICLK             | 45  | 1/0    | clock output signal for image-port, LCLK of LPB image port mode, or optional asynchron. backend clock input                                                                                                                                                                                                                                                                                                                |

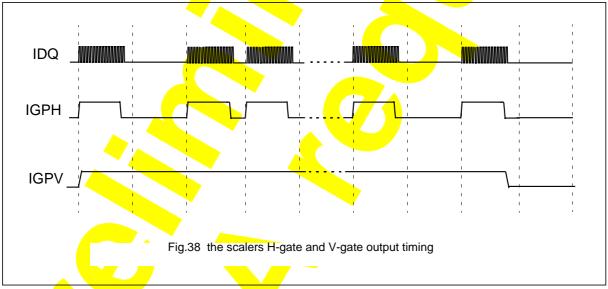

| IDQ              | 46  | 0      | output data qualifier for image port (optional: gated clock output)                                                                                                                                                                                                                                                                                                                                                        |

ı

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

| SYMBOL           | PIN | I/O/P  | DESCRIPTION                                                                                                                                                                                              |

|------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ITRI             | 47  | I (/O) | image-port output control signal, effects all I-port pins incl. ICLK, enable and active polarity is under software control (bits IPE in subaddr. "87") output path used for <b>Testing</b> : scan output |

| IGP0             | 48  | 0      | general purpose output signal 0; image-port (controlled by subaddr. "84","85")                                                                                                                           |

| IGP1             | 49  | 0      | general purpose output signal 1; image-port (controlled by subaddr. "84","85"), same functions as IGP0                                                                                                   |

| V <sub>SSE</sub> | 50  | Р      | digital ground (external pad supply)                                                                                                                                                                     |

| V <sub>DDE</sub> | 51  | Р      | digital supply voltage 3.3 V (external pad supply)                                                                                                                                                       |

| IGPV             | 52  | 0      | multi purpose vertical reference output signal; image-port (controlled by subaddr. "84","85")                                                                                                            |

| IGPH             | 53  | 0      | multi purpose horizontal reference output signal; image-port (controlled by subaddr. "84","85")                                                                                                          |

| IPD7             | 54  | 0      |                                                                                                                                                                                                          |

| IPD6             | 55  | 0      | image port data output                                                                                                                                                                                   |

| IPD5             | 56  | 0      | image port data output                                                                                                                                                                                   |

| IPD4             | 57  | 0      |                                                                                                                                                                                                          |

| V <sub>DDI</sub> | 58  | Р      | digital supply voltage 3.3 V (internal core supply)                                                                                                                                                      |

| IPD3             | 59  | 0      |                                                                                                                                                                                                          |

| IPD2             | 60  | 0      | image part date output                                                                                                                                                                                   |

| IPD1             | 61  | 0      | image port data output                                                                                                                                                                                   |

| IPD0             | 62  | 0      |                                                                                                                                                                                                          |

| V <sub>SSI</sub> | 63  | Р      | digital ground (internal core supply)                                                                                                                                                                    |

| HPD7             | 64  | 1/Q    |                                                                                                                                                                                                          |

| HPD6             | 65  | I/O    | Host port data I/O, carries UV chrominance information in 16 bit video I/O                                                                                                                               |

| HPD5             | 66  | I/O    | modes                                                                                                                                                                                                    |

| HPD4             | 67  | I/O    |                                                                                                                                                                                                          |

| V <sub>DDI</sub> | 68  | Р      | digital supply voltage 3.3 V (internal core supply)                                                                                                                                                      |

| HPD3             | 69  | I/O    |                                                                                                                                                                                                          |

| HPD2             | 70  | I/O    | Host port data I/O, carries UV chrominance information in 16 bit video I/O                                                                                                                               |

| HPD1             | 71  | I/O    | modes                                                                                                                                                                                                    |

| HPD0             | 72  | I/O    |                                                                                                                                                                                                          |

| TEST1            | 73  | 1      | do not connect, reserved for future extensions and for Testing: scan input                                                                                                                               |

CS-

I

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

| SYMBOL           | PIN | I/O/P            | DESCRIPTION                                                                                                                                                               |

|------------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST2            | 74  | I                | do not connect, reserved for future extensions and for Testing: scan input                                                                                                |

| V <sub>DDE</sub> | 75  | Р                | digital supply voltage 3.3 V (external pad supply)                                                                                                                        |

| V <sub>SSE</sub> | 76  | Р                | digital ground (external pad supply)                                                                                                                                      |

| TEST3            | 77  | I                | do not connect, reserved fo <mark>r future extensi</mark> ons and for <b>Testing:</b> scan input                                                                          |

| TEST4            | 78  | 0                | do not connect, reserve <mark>d fo</mark> r future extensi <mark>ons</mark> and for <b>Testing:</b> scan output                                                           |

| TEST5            | 79  | I                | do not connect, reserved for future extensions and for Testing: scan input                                                                                                |

| XTRI             | 80  | I                | X-port output control signal, effects all X-port pins (XPD[7:0], XRH, XRV, XDQ and XCLK) enable and active polarity is under software control (bits XPE in subaddr. "83") |

| XPD7             | 81  | I/O              | expansion-port data: In eight bit video output mode: these signal represent the video bits 7 to 6.                                                                        |

| XPD6             | 82  | I/O              | In ten bit video output mode: these signal represent the video bits 7 to 6.                                                                                               |

| V <sub>DDI</sub> | 83  | Р                | digital supply voltage 3.3 V (internal core supply)                                                                                                                       |

| XPD5             | 84  | I/O <sup>4</sup> |                                                                                                                                                                           |

| XPD4             | 85  | I/O              | expansion-port data: In eight bit video output mode: these signal represent the video bits 5 to 2.                                                                        |

| XPD3             | 86  | I/O              | In ten bit video output mode: these signal represent the video bits 3 to 2.  In ten bit video output mode: these signal represent the video bits 7 to 4.                  |

| XPD2             | 87  | 1/0              |                                                                                                                                                                           |

| V <sub>SSI</sub> | 88  | Р                | digital ground (internal c <mark>ore</mark> supply)                                                                                                                       |

| XPD1             | 89  | 1/0              | expansion-port data:                                                                                                                                                      |

| XPD0             | 90  | 1/0              | In eight bit video output mode: these signal represent the video bits 1 to 0. In ten bit video output mode: these signal represent the video bits 3 to 2.                 |

| XRV              | 91  | I/O              | vertical reference I/O expansion-port: In ten bit video output mode: this signal represents the video bit 0.                                                              |

| XRH              | 92  | 1/0              | horizontal reference I/O expansion-port: In ten bit video output mode: this signal represents the video bit 1.                                                            |

| V <sub>DDI</sub> | 93  | Р                | digital supply voltage 3.3 V (internal core supply)                                                                                                                       |

| XCLK             | 94  | I/O              | clock I/O expansion port                                                                                                                                                  |

| XDQ              | 95  | 1/0              | data qualifier I/O expansion port                                                                                                                                         |

| XRDY             | 96  | 0                | task flag or read signal from scaler, controlled by XRQT (subaddr. 83H)                                                                                                   |

| TRSTN            | 97  | -                | Test ReSeT Not for Boundary Scan Test (with internal pull-up); for board design without Boundary Scan connect TRSTN to 'ground'(1)                                        |

| Philips Semiconductors | CVIP2                | Date:    | 10/23/01 |

|------------------------|----------------------|----------|----------|

| CS-PD Hamburg          | Datasheet<br>SAA7115 | Version: | 0.67     |

| SYMBOL           | PIN | I/O/P | DESCRIPTION                                                                     |

|------------------|-----|-------|---------------------------------------------------------------------------------|

| TCK              | 98  | I     | Test Clock for Boundary Scan Test (with internal pull-up) <sup>(2)</sup>        |

| TMS              | 99  | I     | Test Mode Select for Boundary Scan Test or Scan Test (with internal pull-up)(2) |

| V <sub>SSE</sub> | 100 | Р     | digital ground (external pad supply)                                            |

#### Notes

I

- 1. This pin provides easy initialization of BST circuitry. TRSTN can be used to force the TAP (Test Access Port) controller to the Test-Logic-Reset state (normal operation) at once

- 2. According to the IEEE1149.b1-1994 standard the pads TDI and TMS are input pads with a internal pull-up transistor and TDO a tri-state output pad. TCK, TRSTN are also build with internal pull\_up

Confidential - NDA required page 17

Filename: SAA7115\_Datasheet.fm Last edited by H. Lambers

ı

| Philips Semiconductors | CVIP2     | Date:    | 10/23/01 |

|------------------------|-----------|----------|----------|

| CS-PD Hamburg          | Datasheet | Version: | 0.67     |

|                        | SAA7115   |          |          |

#### 7.2 Pin Configurations

Table 3

Pin Configurations

| pin no                  | pin name | 8 bit input<br>modes       | 16 bit<br>input<br>modes | alternative<br>input<br>functions | 8 bit output<br>modes                                  | 16 bit<br>output<br>modes | alternative<br>output<br>functions | I/O configur <mark>atio</mark> n prog. bits                                  |

|-------------------------|----------|----------------------------|--------------------------|-----------------------------------|--------------------------------------------------------|---------------------------|------------------------------------|------------------------------------------------------------------------------|

| 81,82<br>84-87<br>89,90 | XPD70    | D1<br>data<br>input        | Y data<br>input          |                                   | D1 decoder output [7:0]                                |                           |                                    | XCODE[92[3]]<br>XPE[83[1:0]]<br>+ pin XTR!<br>OFTS[1B[4], 13[2:0]]           |

|                         |          |                            |                          |                                   | D1 decoder<br>output [9:2]<br>10-bit mode              |                           |                                    | XCODE[92[3]]<br>XPE[83[1:0]]<br>+ pin XTRI<br>OFTS[1B[4], 13[2:0]]           |

| 94                      | XCLK     | clock<br>input             |                          | gated<br>clock<br>input           | decoder<br>clock output                                |                           |                                    | XPE[83[1:0]}<br>+ pin XTRI<br>XPCK[83[5:4]]<br>XCKS[92[0]],                  |