## **ADVANCED INFORMATION**

March 2004

# SC14428 Baseband Processor for FP & PP DECT and WDCT

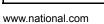

## 1.0 General description

.The SC14428 is a CMOS IC optimized to handle all the audio, signal and data processing needed within a DECT (1.9 GHz) or 2.4GHz ISM digital band base stations and handsets.

A four channel ADPCM transcoder, a very low power 16 bit Codec and Analog Frontend are integrated. Direct connections towards PSTN or ISDN line interface are possible.

The SC14428 has a programmable Generic DSP optimized for telecom applications.

The SC14428 is designed to fit to any radio interface. A dedicated TDMA controller handles all physical layer slot formats and radio control.

National Semiconductor's standard CompactRISC<sup>TM</sup> CR16C microprocessor takes care of all the higher protocol stack.

## 2.0 Features

- Complies with DECT ETS 300 175-2,3 & 8 SWAP-CA V1.3 Rev 1.3 20000616

- 1.8Volt operating voltage with 2.65V (typ) IO pads.

- Two chip low drop voltage regulators

- 16 bit CompactRISCTM CR16C Microprocessor with programmable clock speeds up to 20.736 MHz.

- Four channel DMA controller.

- Serial Debug interface, Nexus Class-1 compliant.

- 16kbyte shared, 6kbyte non shared RAM

- 4kbyte shared RAM for TAM DSP

- Versions with ROM, FLASH and data FLASH

- Programmable 16 bits system bus interface with bus master and slave operation.

- User programmable GENeric DSP with fixed telecom processing routines.

- Four full duplex 32 kbits/sec ADPCM transcoder.

- On-chip Dedicated Instruction Processor (DiP) for all TDMA based events, which supports DCT 1.152MHz, 0.576MHz and 0.288MHz data rates.

- ISM band and DECT with 9.216, 10.368 and 13.824 MHz xtals.

- Protected and unprotected full and double slot B-fields

- Flexible 1.152 Mbit/sec three wire interface to radio front synthesizer.

- One 16-bit linear CODEC

- Selectable Fast Antenna Diversity operation or RSSI measurement with peak hold ADC.

- Three input general purpose 8 bit ADC

- Two general purpose timers and watch dog timer.

- Two Capture timers for frequency measurement for e.g. metering, ringing and call progress tone detection.

- Three general purpose I/O ports with two edge/level programmable interrupts

- Full duplex UART and MICROWIRE<sup>TM</sup> interface.

- SPI<sup>TM</sup> interface (Master/Slave).

- Flexible 8 kHz synchronous Serial interface to external codecs and ISDN interface circuits.

- Three programmable chip selects

- Integrated opamp for caller-id

- (80 pin PFQP and 80,)128,160 pins TQFP packages.

LMX9820

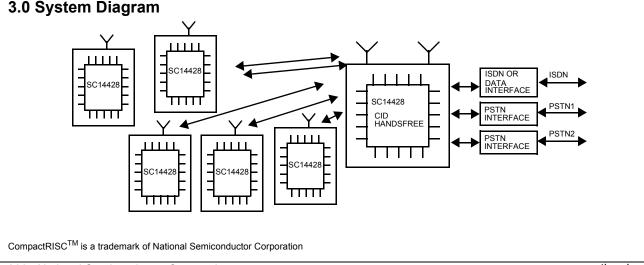

## 3.0 System Diagram (Continued)

## 4.0 Specifications

All min/max specification limits are guaranteed by design, or production test, or statistical methods.

#### Parameter Description Conditions Min Max Units Vbat1 max Max Battery supply voltage VBAT1 5.5 V Vbat2\_max Max Battery supply voltage VBAT2 5.5 V Ibat1 max Max negative current into VBAT1 300 mΑ Max negative current into VBAT2 300 Ibat2 max mΑ lvddiotot max Max total current into VDDIOs 90 mΑ Max current through I/O pins 20 Ivddio max mΑ Max Core supply voltage (VDD-VSS / AVD-AVS / AVD2-AVS / VDDRF-VSSRF) Vdd\_max 2.0 V Vddiof\_max Max I/O Supply voltage for devices with FLASH 3.0 V Note<sup>2</sup> (VDDIO-VSS) Vddio\_max Max I/O supply voltage for devices without FLASH V 3.6 Note<sup>3</sup> (VDDIO-VSS) VSS-0.3 5.25 V VIdo1\_ctrl\_max Max voltage on pin LDO1\_CTRL Note<sup>4</sup> VSS-0.3 V VIdo2 ctrl max Max voltage on pin LDO2 CTRL 5.25 Note<sup>4</sup> VSS-0.3 Vpon\_max Max voltage on pin PON 2.85 V Max voltage on pin CHARGE VSS-0.3 2.85 V Vcharge\_max V Vbat3 max Max voltage on pin VBAT3 VSS-0.3 2.85 Vadc1\_max Max voltage on pin ADC1 VSS-0.3 2.85 V Max voltage on pin RDI digital mode (max 3.6V) VDDIO+0.3 v Vrdidig\_max VSS-0.3 V Vrdiana\_max Max voltage on pin RDI analog mode VSS-0.3 2.0 V VSS-0.3 VDDIO+0.3 Vdig\_max Max voltage on digital Input pins (max 3.6V) Max voltage on any other input (incl analog pads) VSS-0.3 2.0 V Vana max Iprot\_max Max current through prot. diodes on any pin to VDDIO 100 mΑ Max current through prot. diode pins CID+/- to AGND 1.0 Iprotcid\_max mΑ Iprotmic\_max Current through prot. diode pin MIC+/- to AGND 2.4 mΑ Max current through prot. circuit of PON pin. 0.6 Iprotpon\_max Note<sup>5</sup> mΑ Max current through prot. circuit of CHARGE pin. 0.6 mΑ Iprotcharge\_max Note<sup>5</sup> Iprotvbat3\_max Max current through prot. circuit of VBAT3 pin. Note<sup>5</sup> 0.6 mΑ lprotadc1 max Max current through prot. circuit of ADC1 pin. 0.6 mΑ Tstorage Storage temperature -65 +150 °C Package power dissipation @ 25 °C 500 mW Ppackage Latch-up current all pins according JEDEC 78 TA = 65 °C 100 llu mΑ TA = 25 °C llu\_rdi\_25 Latch-up current RDI pin 100 mΑ Latch-up current RDI pin llu rdi 60 TA = 65 °C 50 mΑ ESD voltage according to man machine model Vesd mm 100 V ESD voltage according to human body model 1000 Vesd\_hbm V

### Table 1. ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

1.Absolute maximum ratings are those values that may be applied for maximum 50 hours. Beyond these values, damage to the device may occur.

2.A voltage between 2.8V and 3.0V may applied for a maximum time of 1 hour in order to guarantee the device specifications.

3.A voltage between 3.3V and 3.6V may applied for a maximum time of 50 hours in order to guarantee the device specifications.

4.For LDO1\_CTRL, LDO2\_CTRL, with 5V input protection, VDD must be between 1.75V and 2.0V or Vbat 1 >2.0V or Vbat2>2.8V.

## 4.0 Specifications (Continued)

5. The protection current can be calculated as follows:

In case P1[6]/PON, P1[7]/CHARGE, VBAT3, P2[3]/ADC1 is input, Iprotxxx\_max = (Vext - 2.55)/(500+Rext)

Rext is an external resistor which is needed if the external voltage Vext exceeds the 2.8V.

(A lower protection current value of e.g. 100 uA is recommended in case power saving is important)

In case P1[6]/PON, P1[7]/CHARGE , P2[3]/ADC1 is output, Iprotxxx\_max = (VDDIO - 2.55)/(500)

| PARAMETER                                 | DESCRIPTION                                                       | CONDITIONS              | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|-------------------------------------------------------------------|-------------------------|------|------|------|-------|

| Vbat1                                     | Battery supply voltage VBAT1-AVS                                  |                         | 2.0  |      | 5.0  | V     |

| /bat2 Battery supply voltage VBAT2-AVS    |                                                                   |                         | 2.8  |      | 5.0  | V     |

| Vdd                                       | /dd Digital core supply voltage<br>VDD-VSS                        |                         | 1.75 | 1.8  | 1.98 | V     |

| Avd Analog core supply voltage<br>AVD-AVS |                                                                   | Note <sup>2</sup>       | 1.75 | 1.8  | 1.98 | V     |

| Avd2                                      | Analog core supply voltage<br>AVD2-AVS                            | Note <sup>2</sup>       | 1.75 | 1.8  | 1.98 | V     |

| Vddrf                                     | Analog xtal and RFCLK supply<br>voltage VDDRF-VSSRF               | Note <sup>2</sup>       | 1.75 | 1.8  | 1.98 | V     |

| Vddiof                                    | Digital I/O supply voltage VDDIO-VSS<br>for devices with FLASH    |                         | 2.5  | 2.65 | 2.8  | V     |

| Vddio                                     | Digital I/O supply voltage VDDIO-VSS<br>for devices without FLASH |                         | 1.75 |      | 3.3  | V     |

| Vdcs                                      | Voltage on DC_Sense pin                                           |                         |      |      | 2.0  | V     |

| Vpon                                      | Voltage on PON                                                    | All states <sup>3</sup> |      |      | 2.8  | V     |

| Vcharge                                   | Voltage on CHARGE                                                 | All states <sup>3</sup> |      |      | 2.8  | V     |

| Vbat3                                     | Voltage on VBAT3                                                  | Note <sup>3</sup>       |      |      | 2.8  | V     |

| Vadc1                                     | Voltage on ADC1                                                   | Note <sup>3</sup>       |      |      | 2.8  | V     |

| Vprot_mic                                 | Voltage on pins MICn, CIDp/n if protec-<br>tion enabled           | Note <sup>4</sup>       | 0.4  |      | 1.4  | V     |

| Iprotpon                                  | Current through protection circuit of PON pin.                    | Note <sup>3</sup>       |      |      | 0.5  | mA    |

| Iprotcharge                               | Current through protection circuit of CHARGE pin.                 | Note <sup>3</sup>       |      |      | 0.5  | mA    |

| lprotvbat3                                | Current through protection circuit of<br>VBAT3/RINGING pin.       | Note <sup>3</sup>       |      |      | 0.5  | mA    |

| lprotadc1                                 | Current through protection circuit of ADC1 pin.                   | Note <sup>3</sup>       |      |      | 0.5  | mA    |

| Vldo1_ctrl                                | Voltage on LDO1_CTRL                                              |                         |      |      | 5.0  | V     |

| Vldo2_ctrl                                | Maximum voltage on LDO2_CTRL                                      |                         |      |      | 5.0  | V     |

| Fpll_range                                | PLL operating range                                               |                         | 28   |      | 48   | MHz   |

| ТА                                        | Ambient temperature                                               | Note <sup>5</sup>       | -10  |      | 60   | °C    |

#### Table 2. OPERATING CONDITIONS <sup>1</sup>

1. Within the specified limits, a life time of 10 years is guaranteed.

2.Full operating mode; the differences between AVD, VDD may never be more than 300mV; during a short period of time e.g. during power up more than 300mV difference is allowed. Analog performance is only guaranteed from 1.75-1.98V

3. The protection current can be calculated as follows:

In case P1[6]/PON, P1[7]/CHARGE, VBAT3, P2[3]/ADC1 is input, Iprotxxx max = (Vext - 2.55)/(500+Rext)

Rext is an external resistor which is needed if the external voltage Vext exceeds the 2.8V. (A lower protection current value of e.g. 100 uA is recommended in case power saving is important) In case P1[6]/PON, P1[7]/CHARGE, P2[3]/ADC1 is output, Iprotxxx max = (VDDIO - 2.55)/(500)

- 4.For pads with the protection circuit enabled, the protection current **must** be limited with external source resistor Rext if the input voltage exceeds 0.4V resp 1.4V. Rext can be calculated as follows: Rext >(Vext-1.4)/Iprotxxx).

- 5. Within this temperature range full operation is guaranteed. Upto +70 degrees Celsius analog performance is not guaranteed.

## **5.0 Product Status Definitions**

| Datasheet Status        | Product Status         | Definition                                                                                                                                                                                                                                                                         |

|-------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information     | Formative or in Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                                |

| Preliminary             | First Production       | This data sheet contains preliminary data. Supplementa-<br>ry data will be published at a later date. National Semi-<br>conductor Corporation reserves the right to make<br>changes at any time without notice in order to improve<br>design and supply the best possible product. |

| No Identification Noted | Full production        | This data sheet contains final specifications. National<br>Semiconductor Corporation reserves the right to make<br>changes at any time without notice in order to improve<br>design and supply the best possible product.                                                          |

| Obsolete                | Not in Production      | This data sheet contains specifications on a product that<br>has been discontinued by National Semiconductor Cor-<br>poration. The datasheet is printed for reference informa-<br>tion only.                                                                                       |

6.0 National Semiconductor B.V reserves the right to make changes without notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the right of others.

#### 7.0 Package information inches (millimeters) unless otherwise noted 17.20±0.25 TYP OPTIONAL PIN 1 CORNER 16° TOP & BOTTOM PIN #1 IDENT R0 13 MIN R0.13-0.30 — 0.65 TYP - 0.22-0.38 TYP 2.45 MAX GAGE PLANE -SEE DETAIL A 0.10 -0.25 MAX 0° - 7 2.0±0 0.88±0.1 EATING PLANE 0.20 MIN □14.0±0.1 (1.6) DETAIL A 0.11-0.23 TYP VJE80A (Rev E) DIMENSIONS ARE IN MILLIMETERS

Figure 2. 80 Pins PQFP. NS Package number: VJE80A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor EuropeCustomer Support Center

Fax:

+49 (0) 180-530 85 86

Email:

europe.support@insc.com

Deutsch Tel:

+49 (0) 69 9508 6208

English Tel:

+44 (0) 870 24 0 2171

Francais Tel:

+33 (0) 141 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com