N**ational** Semiconductor

#### 捷多邦,专业PCB打样工厂,24小时加急出货

November 2004

SCAN921821 - Dual 18-Bit Serializer with Pre-emphasis,

1149.1 (JTAG), and At-Speed BIS

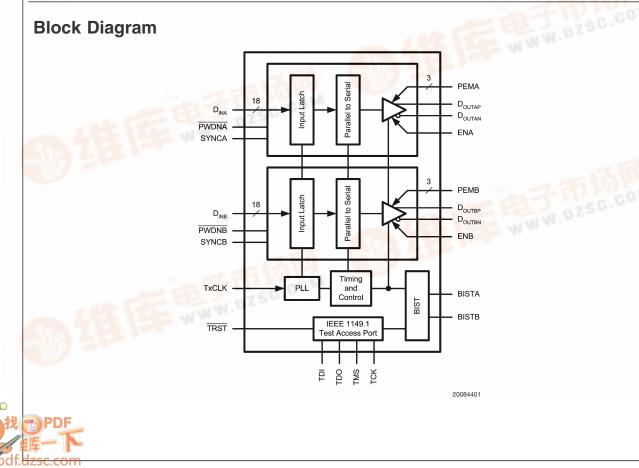

# SCAN921821 Dual 18-Bit Serializer with Pre-emphasis, IEEE 1149.1 (JTAG), and At-Speed BIST **General Description**

The SCAN921821 is a dual channel 18-bit serializer featuring signal conditioning, boundary SCAN, and at-speed BIST. Each serializer block transforms an 18-bit parallel LVCMOS/ LVTTL data bus into a single Bus LVDS data stream with embedded clock. This single serial data stream with embedded clock simplifies PCB design and reduces PCB cost by narrowing data paths that in turn reduce PCB size and layers. The single serial data stream also reduces cable size, the number of connectors, and eliminates clock-to-data and data-to-data skew.

Each channel also has an 8-level selectable pre-emphasis feature that significantly extends performance over lossy interconnect. Each channel also has its own powerdown pin that saves power by reducing supply current when the channel is not being used.

The SCAN921821 also incorporates advanced testability features including IEEE 1149.1 and at-speed BIST PRBS pattern generation to facilitate verification of board and link integrity

#### Features

- 15-66 MHz Dual 18:1 Serializer with 2.376 Gbps total throughput

- 8-level selectable pre-emphasis on each channel drives lossy cables and backplanes

- >15kV HBM ESD protection on Bus LVDS I/O pins

- Robust BLVDS serial data transmission with embedded clock for exceptional noise immunity and low EMI

- Power saving control pin for each channel

- IEEE 1149.1 "JTAG" Compliant

- At-Speed BIST PRBS generation

- No external coding required

- Internal PLL, no external PLL components required

- Single +3.3V power supply

- Low power: 260 mW (typ) per channel at 66 MHz with PRBS-15 pattern

- Single 3.3 V supply

- Fabricated with advanced CMOS process technology

- Industrial -40 to +85°C temperature range

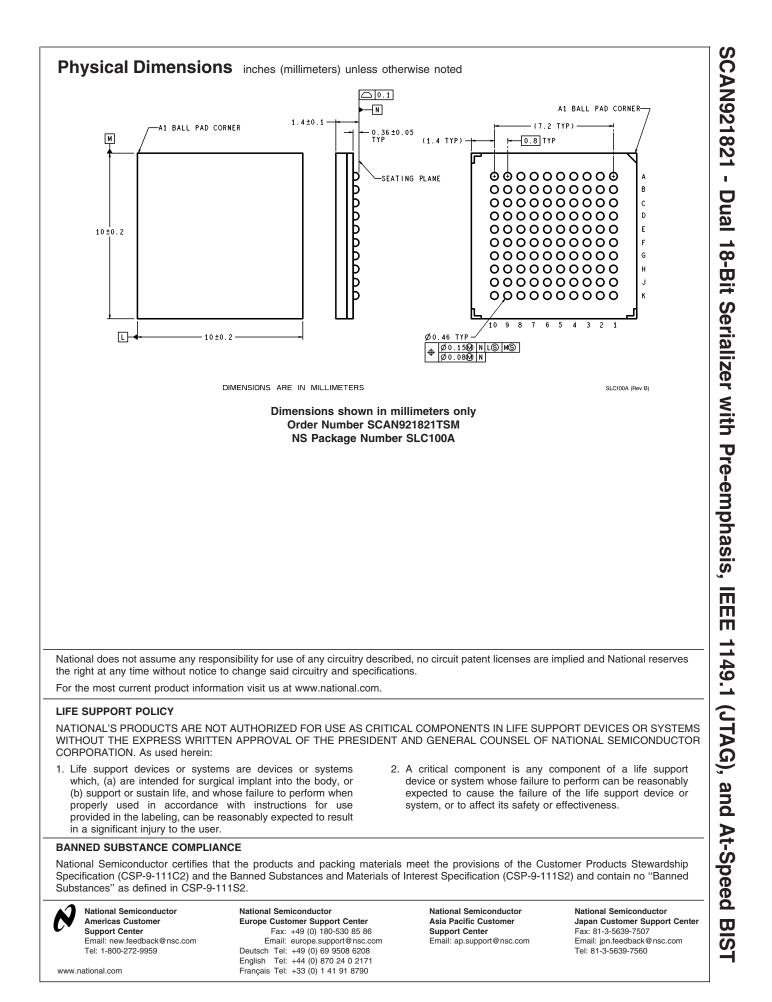

- Compact 100-ball FBGA package

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>DD</sub> ) -0.3V to +4V |                                  |  |  |  |  |

|------------------------------------------------|----------------------------------|--|--|--|--|

| Supply Voltage (V <sub>DD</sub> )              |                                  |  |  |  |  |

| Ramp Rate                                      | < 30 V/ms                        |  |  |  |  |

| LVCMOS/LVTTL Input                             |                                  |  |  |  |  |

| Voltage                                        | –0.3V to (V <sub>DD</sub> +0.3V) |  |  |  |  |

| LVCMOS/LVTTL Output                            |                                  |  |  |  |  |

| Voltage                                        | –0.3V to (V <sub>DD</sub> +0.3V) |  |  |  |  |

| Bus LVDS Driver Output                         |                                  |  |  |  |  |

| Voltage                                        | -0.3V to +3.9V                   |  |  |  |  |

| Bus LVDS Output Short                          |                                  |  |  |  |  |

| Circuit Duration                               | 10ms                             |  |  |  |  |

| Junction Temperature                           | +150°C                           |  |  |  |  |

| Storage Temperature                            | –65°C to +150°C                  |  |  |  |  |

| Lead Temperature                               |                                  |  |  |  |  |

| (Soldering, 4 seconds)                         | +220°C                           |  |  |  |  |

| Maximum Package Power                          | Dissipation at 25°C              |  |  |  |  |

| FBGA-100                                       | 3.57 W                           |  |  |  |  |

| Derating Above 25°C 28.57 mW            |          |  |  |  |

|-----------------------------------------|----------|--|--|--|

| Thermal resistance $\theta_{JA}$ 35°C/V |          |  |  |  |

| $\theta_{\text{JC}}$                    | 11.1°C/W |  |  |  |

| ESD Rating                              |          |  |  |  |

| HBM, 1.5 KΩ, 100 pF                     |          |  |  |  |

| All pins                                | >8 kV    |  |  |  |

| Bus LVDS pins                           | >15 kV   |  |  |  |

| MM, 0Ω, 200 pF                          | >1200 V  |  |  |  |

| CDM                                     | >2 kV    |  |  |  |

# Recommended Operating Conditions

|                                                     | Min  | Nom | Max  | Units  |

|-----------------------------------------------------|------|-----|------|--------|

| Supply Voltage ( $V_{DD}$ )                         | 3.15 | 3.3 | 3.45 | V      |

| Operating Free Air<br>Temperature (T <sub>A</sub> ) | -40  | +25 | +85  | °C     |

| Clock Rate                                          | 15   |     | 66   | MHz    |

| Supply Noise                                        |      |     | 100  | mV p-p |

#### **DC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                       | Conditions                                                    | Min  | Тур  | Max             | Units |

|------------------|---------------------------------|---------------------------------------------------------------|------|------|-----------------|-------|

| VCMOS/           | LVTTL Input DC Specifica        | ations                                                        |      |      | •               |       |

| V <sub>IH</sub>  | High Level Input<br>Voltage     |                                                               | 2.0  |      | V <sub>DD</sub> | V     |

| $V_{IL}$         | Low Level Input<br>Voltage      |                                                               | GND  |      | 0.8             | v     |

| $V_{CL}$         | Input Clamp Voltage             | $I_{CL} = -18 \text{ mA}$                                     | -1.5 | -0.7 |                 | V     |

| I <sub>INH</sub> | High Level Input<br>Current     | $V_{IN} = V_{DD} = V_{DDMAX}$                                 | -20  | ±2   | +20             | μA    |

| I <sub>INL</sub> | Low Level Output<br>Current     | $V_{IN} = V_{SS}, V_{DD} = V_{DDMAX}$                         | -10  | ±2   | +10             | μA    |

| 149.1 (JT        | AG) DC Specifications           |                                                               |      |      |                 | •     |

| V <sub>IH</sub>  | High Level Input<br>Voltage     |                                                               | 2.0  |      | V <sub>DD</sub> | V     |

| V <sub>IL</sub>  | Low Level Input<br>Voltage      |                                                               | GND  |      | 0.8             | v     |

| V <sub>CL</sub>  | Input Clamp Voltage             | I <sub>CL</sub> = -18 mA                                      | -1.5 | -0.7 |                 | V     |

| I <sub>INH</sub> | High Level Input<br>Current     | $V_{IN} = V_{DD} = V_{DDMAX}$                                 | -20  |      | +20             | μA    |

| I <sub>INL</sub> | Low Level Output<br>Current     | $V_{IN} = V_{SS}, V_{DD} = V_{DDMAX}$                         | -200 |      | +200            | μA    |

| V <sub>OH</sub>  | High Level Output<br>Voltage    | $I_{OH} = -9 \text{ mA}$                                      | 2.3  |      | V <sub>DD</sub> | mV    |

| V <sub>OL</sub>  | Low Level Output<br>Voltage     | I <sub>OL</sub> = 9 mA                                        | GND  |      | 0.5             | mV    |

| I <sub>OS</sub>  | Output Short Circuit<br>Current | V <sub>OUT</sub> = 0 V                                        | -100 | -80  | -50             | mA    |

| i                | Output Tri-state                | $\overline{\text{PWDN}}$ or EN = 0.8V, V <sub>OUT</sub> = 0 V | -10  |      | +10             | μA    |

| l <sub>oz</sub>  | Current                         | PWDN or EN = 0.8V, V <sub>OUT</sub> = VDD                     | -30  |      | +30             | μA    |

www.national.com

| Symbol            | Parameter                                       | Con                                  | Min                                                             | Тур      | Max  | Units |       |

|-------------------|-------------------------------------------------|--------------------------------------|-----------------------------------------------------------------|----------|------|-------|-------|

| -                 |                                                 |                                      |                                                                 |          |      | I     |       |

| us LVDS           | Output DC Specificati                           | ons                                  |                                                                 |          |      | 1     |       |

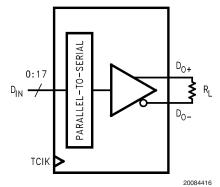

| V <sub>OD</sub>   | Output Differential<br>Voltage (DO+) -<br>(DO-) | Figure 10                            | 0, R <sub>L</sub> = 100Ω                                        | 450      | 500  | 550   | mV    |

| $\Delta V_{OD}$   | Output Differential<br>Voltage Unbalance        |                                      |                                                                 |          | 2    | 15    | mV    |

| Vos               | Offset Voltage                                  |                                      |                                                                 | 1.05     | 1.2  | 1.25  | V     |

| $\Delta V_{OS}$   | Offset Voltage<br>Unbalance                     |                                      |                                                                 |          | 2.7  | 15    | mV    |

|                   |                                                 | Pre-Empha                            | asis Level = 1                                                  | 1.10     | 1.24 | 1.35  |       |

|                   |                                                 | Pre-Empha                            | asis Level = 2                                                  | 1.35     | 1.47 | 1.55  |       |

|                   | Pre-Emphasis Output                             | Pre-Empha                            | asis Level = 3                                                  | 1.55     | 1.70 | 1.80  |       |

| Q <sub>POV</sub>  | Voltage Ratio                                   | Pre-Empha                            | asis Level = 4                                                  | 1.80     | 1.91 | 1.95  |       |

|                   | V <sub>ODPRE</sub> / V <sub>OD</sub>            | Pre-Empha                            | asis Level = 5                                                  | 1.95     | 2.08 | 2.20  |       |

|                   |                                                 | Pre-Empha                            | 2.10                                                            | 2.21     | 2.35 | 1     |       |

|                   |                                                 | Pre-Emphasis Level =                 |                                                                 | 2.15     | 2.30 | 2.50  |       |

| I <sub>OS</sub>   | Output Short Circuit<br>Current                 | DO = 0V, $Din = H$ ,                 | -10                                                             | -25      | -75  | mA    |       |

| 1                 | TRI-STATE Output                                | $\overline{PWDN}$ or $EN = 0.8$      | 3V, DO = 0V (Note 4)                                            | -10      | ± 1  | +10   | μA    |

| l <sub>oz</sub>   | Current                                         | $\overline{PWDN}$ or $EN = 0.8$      | -55                                                             | ± 6      | +55  | μA    |       |

| ower Su           | pply Current (DVDD, P\                          | DD and AVDD Pins)                    |                                                                 |          |      |       |       |

|                   | Total Supply Current                            |                                      | f = 66 MHz, PRBS-15<br>Pattern                                  |          | 160  | 225   | mA    |

| I <sub>DD</sub>   | (includes load<br>current)                      | $C_L = 15pF,$<br>$R_L = 100 \Omega$  | f = 66 MHz, Worst<br>Case Pattern<br>(Checker-Board<br>Pattern) |          | 180  |       | mA    |

|                   | Total Supply Current                            |                                      | f = 66 MHz, PRBS-15<br>Pattern                                  |          | 240  |       | mA    |

| I <sub>DDP</sub>  | with Pre-Emphasis<br>(includes load<br>current) | $C_L = 15 pF,$<br>$R_L = 100 \Omega$ | f = 66 MHz, Worst<br>Case Pattern<br>(Checker-Board<br>Pattern) |          | 280  | 325   | mA    |

| I <sub>DDX</sub>  | Supply Current<br>Powerdown                     | $\overline{PWDN} = 0.$               | 8V, EN = 0.8V                                                   |          | 1.0  | 3.0   | mA    |

|                   | ng Requiremen                                   |                                      | anges unless otherwise sp                                       | ecified. |      |       |       |

| Symbol            | Parameter                                       |                                      | ditions                                                         | Min      | Тур  | Max   | Units |

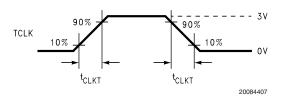

| t <sub>TCP</sub>  | Transmit Clock<br>Period                        |                                      |                                                                 | 15.2     | Т    | 66.7  | ns    |

| t <sub>TCIH</sub> | Transmit Clock High<br>Time                     |                                      |                                                                 | 0.4T     | 0.5T | 0.6T  | ns    |

| t <sub>TCIL</sub> | Transmit Clock Low<br>Time                      |                                      |                                                                 | 0.4T     | 0.5T | 0.6T  | ns    |

|                   |                                                 |                                      |                                                                 |          | 1    | 1     |       |

ns

ps (RMS)

3

6

80

(Note 5)

TCLK Input

Transition Time TCLK Input Jitter

$t_{\rm CLKT}$

t<sub>JIT</sub>

#### **AC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                  | Conditions                                           | Min                    | Тур                    | Max                    | Units      |

|-------------------|--------------------------------------------|------------------------------------------------------|------------------------|------------------------|------------------------|------------|

| Serializer        | AC Specifications                          |                                                      |                        |                        |                        |            |

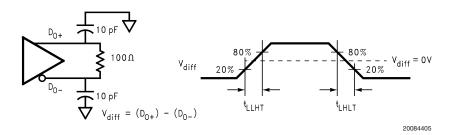

| t <sub>LLHT</sub> | Bus LVDS<br>Low-to-High<br>Transition Time | <i>Figure 2</i> , (Note 5)<br>R <sub>L</sub> = 100Ω, |                        | 0.3                    | 0.4                    | ns         |

| t <sub>LHLT</sub> | Bus LVDS<br>High-to-Low<br>Transition Time | $C_L = 10022$ ,<br>$C_L = 10$ pF to GND              |                        | 0.3                    | 0.4                    | ns         |

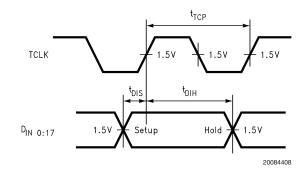

| t <sub>DIS</sub>  | DIN (0-17) Setup to<br>TCLK                | Figure 4, (Note 5)<br>$R_{L} = 100\Omega$ ,          | 1.9                    |                        |                        | ns         |

| t <sub>DIH</sub>  | DIN (0-17) Hold from<br>TCLK               | $C_L = 10022$ ,<br>$C_L = 10$ pF to GND              | 0.6                    |                        |                        | ns         |

| t <sub>HZD</sub>  | DO ± HIGH to<br>TRI-STATE Delay            |                                                      |                        | 3.9                    | 10                     | ns         |

| t <sub>LZD</sub>  | DO ± LOW to<br>TRI-STATE Delay             | Figure 5<br>$R_{\rm L} = 100\Omega$ ,                |                        | 3.5                    | 10                     | ns         |

| t <sub>zhD</sub>  | DO ± TRI-STATE to<br>HIGH Delay            | $C_L=10pF$ to GND                                    |                        | 3.2                    | 10                     | ns         |

| t <sub>ZLD</sub>  | DO ± TRI-STATE to<br>LOW Delay             |                                                      |                        | 2.4                    | 10                     | ns         |

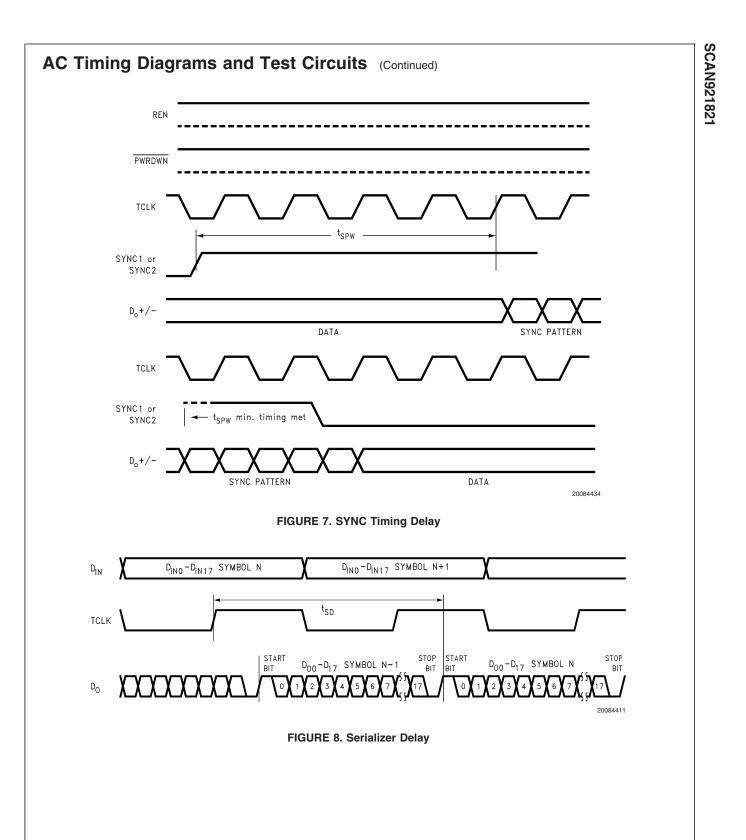

| t <sub>SPW</sub>  | SYNC Pulse Width                           | Figure 7,<br>$R_L = 100\Omega$                       | 5*t <sub>TCP</sub>     |                        | 6*t <sub>TCP</sub>     | ns         |

| t <sub>PLD</sub>  | Serializer PLL Lock<br>Time                | Figure 6,<br>$R_L = 100\Omega$                       | 510*t <sub>TCP</sub>   |                        | 1024*t <sub>TCP</sub>  | ns         |

| t <sub>SD</sub>   | Serializer Delay                           | Figure 8 , $R_L = 100\Omega$                         | t <sub>TCP</sub> + 2.5 | t <sub>TCP</sub> + 4.5 | t <sub>TCP</sub> + 6.5 | ns         |

| t <sub>sкcc</sub> | Channel to Channel<br>Skew                 |                                                      |                        | 70                     |                        | ps         |

| t <sub>RJIT</sub> | Random Jitter                              | Room Temperature, V <sub>DD</sub> = 3.3V,<br>66 MHz  |                        | 6.1                    |                        | ps<br>(RMS |

| t                 | Deterministic Jitter                       | 15 MHz                                               | -390                   |                        | 320                    | ps         |

| t <sub>DJIT</sub> | Figure 9, (Note 5)                         | 66 MHz                                               | -60                    |                        | 30                     | ps         |

| 149.1 (JT         | AG) AC Specifications                      |                                                      |                        |                        |                        |            |

| f <sub>MAX</sub>  | Maximum TCK Clock<br>Frequency             |                                                      | 25                     |                        |                        | MHz        |

| t <sub>s</sub>    | TDI or TMS Setup to<br>TCK, H or L         |                                                      | 2.4                    |                        |                        | ns         |

| t <sub>H</sub>    | TDI or TMS Hold<br>from TCK, H or L        | $C_L = 15 pF$ ,                                      | 2.8                    |                        |                        | ns         |

| t <sub>W1</sub>   | TCK Pulse Width, H<br>or L                 | $R_L = 500 \ \Omega$                                 | 10                     |                        |                        | ns         |

| t <sub>W2</sub>   | TRST Pulse Width, L                        |                                                      | 10                     |                        |                        | ns         |

| t <sub>REC</sub>  | Recovery Time,<br>TRST to TCK              |                                                      | 2                      |                        |                        | ns         |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: Typical values are given for V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25 $^{\circ}$ C.

**Note 3:** Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VOD,  $\triangle$ VOD, VTH and VTL which are differential voltages.

Note 4: I<sub>OZ</sub> is measured at each pin. The DOUT pin not under test is floated to isolate the TRI-STATE current flow.

Note 5: Guaranteed by Design (GBD) using statistical analysis.

## AC Timing Diagrams and Test Circuits

FIGURE 1. "Worst Case" Serializer IDD Test Pattern

#### FIGURE 2. Serializer Bus LVDS Distributed Output Load and Transition Times

FIGURE 4. Serializer Setup/Hold Times

#### AC Timing Diagrams and Test Circuits (Continued) Parasitic package and trace capacitance D<sub>O+</sub> 50Ω +1.2V 50Ω D<sub>O-</sub> DEN 3٧ DEN 1.5V 1.5V 0٧ t<sub>HZD</sub> t<sub>ZHD</sub> V<sub>OH</sub> 50% 50% - 1.1V - t<sub>LZD</sub> t<sub>ZLD</sub> $D_{0\pm}$ 1.1V 50% 50% $\rm V_{OL}$ 20084409 FIGURE 5. Serializer TRI-STATE Test Circuit and Timing PWRDN 2.0V 0.87 t<sub>HZD</sub> or t<sub>LZD</sub> TCLK t<sub>ZHD</sub> or t<sub>PLD</sub> $t_{ZLD}$ TRI-STATE TRI-STATE D<sub>0±</sub> Output Active 20084410 FIGURE 6. Serializer PLL Lock Time, and PWRDN TRI-STATE Delays

#### AC Timing Diagrams and Test Circuits (Continued) Ideal Bit Start Ideal Bit Stop t<sub>DJIT</sub> Max. t<sub>DJIT</sub> Min. t<sub>DJIT</sub> Typ. t<sub>DJIT</sub> Max. $\mathbf{t}_{\text{DJIT}}$ Min. $\mathbf{t}_{\text{DJIT}}$ Typ. t<sub>BIT</sub> . Negative Positive Negative Positive Deterministic Deterministic Deterministic Deterministic Jitter Jitter Jitter Jitter + \_ + \_ 0 0 20084429 FIGURE 9. Deterministic Jitter and Ideal Bit Position

$\label{eq:VOD} V_{OD} = (DO^+) - (DO^-).$  Differential output signal is shown as (DO+)-(DO-), device in Data Transfer mode.

### **Pre-emphasis Truth Table**

| PEM LEVEL | PEM2 | PEM1 | PEM0 |

|-----------|------|------|------|

| 0         | L    | L    | L    |

| 1         | L    | L    | Н    |

| 2         | L    | Н    | L    |

| 3         | L    | Н    | н    |

| 4         | Н    | L    | L    |

| 5         | Н    | L    | Н    |

| 6         | Н    | Н    | L    |

| 7         | Н    | Н    | Н    |

| Pin Diagra       | ım               |                        |                  |                     |                        |                        |                  |                        |                  |  |

|------------------|------------------|------------------------|------------------|---------------------|------------------------|------------------------|------------------|------------------------|------------------|--|

| -                |                  |                        |                  |                     | 1821TVV<br>View        |                        |                  |                        |                  |  |

| A1               | A2               | A3                     | A4               | A5                  | A6                     | A7                     | A8               | (A9)                   | (A10)            |  |

| BISTB            | PV <sub>SS</sub> | DOUTBN                 | AV <sub>DD</sub> | ENB                 | AV <sub>DD</sub>       | DOUTAN                 | DOUTAP           | AV <sub>DD</sub>       | ENA              |  |

| B1               | B2               | B3                     | B4               | B5                  | B6                     | B7                     | B8               | B9                     | BI0              |  |

| DINB16           | SYNCB            | AV <sub>DD</sub>       | DOUTBP           | AV <sub>DD</sub>    | PEMB1                  | AV <sub>SS</sub>       | PEMB0            | PEMA1                  | BISTA            |  |

| C1               | C2               | C3                     | C4               | C5                  | C6                     | C7                     | C8               | C9                     | C10              |  |

| DINB14           | DV <sub>DD</sub> | DV <sub>SS</sub>       | AV <sub>SS</sub> | AV <sub>SS</sub>    | AV <sub>SS</sub>       | AV <sub>DD</sub>       | PEMA2            | SYNCA                  | DINA16           |  |

| D1               | D2               | D3                     | D4               | D5                  | D6                     | D7                     | D8               | D9                     | D10              |  |

| DINB13           | DINB12           | DINB17                 | DV <sub>DD</sub> | PV <sub>DD</sub>    | PEMA0                  | AV <sub>SS</sub>       | DINA17           | DINA15                 | DINA13           |  |

| E1               | E2               | E3                     | E4               | E5                  | E6                     | E7                     | E8               | E9                     | E10              |  |

| DINB11           | DINB9            | DINB15                 | DV <sub>SS</sub> | DINB8               | PEMB2                  | DV <sub>SS</sub>       | DINA14           | DINA12                 | DINA9            |  |

| F1               | F2               | F3                     | F4               | F5                  | F6                     | F7                     | F8               | F9                     | F10              |  |

| DINB10           | DINB7            | DINB5                  | DV <sub>SS</sub> | PV <sub>DD</sub>    | DINA11                 | DV <sub>SS</sub>       | DINA4            | DINA10                 | DINA8            |  |

| G1               | G2               | G3                     | G4               | G5                  | G6                     | G7                     | G8               | G9                     | G10              |  |

| DINB6            | DINB4            | DINB2                  | DV <sub>SS</sub> | DV <sub>DD</sub>    | DV <sub>DD</sub>       | DINA1                  | DINA2            | DINA7                  | DINA6            |  |

| H1               | H2               | H3                     | H4               | H5                  | H6                     | H7                     | H8               | H9                     | H10              |  |

| DINB3            | DINB1            | TxCLK                  | DV <sub>SS</sub> | TCK                 | PV <sub>DD</sub>       | PV <sub>SS</sub>       | DV <sub>SS</sub> | DINA0                  | DINA5            |  |

| J1<br>DINB0      | J2<br>PWDNA      | J3<br>DV <sub>DD</sub> | J4<br>TRST       | $\bigcup_{PV_{DD}}$ | J6<br>PV <sub>SS</sub> | J7<br>PV <sub>DD</sub> | J8<br>NC         | J9<br>DV <sub>DD</sub> | J10<br>DINA3     |  |

| K1               | K2               | K3                     | K4               | K5                  | K6                     | K7                     | K8               | K9                     | K10              |  |

| DV <sub>SS</sub> | TDI              | TMS                    | DV <sub>SS</sub> | TDO                 | DV <sub>DD</sub>       | PV <sub>SS</sub>       | PV <sub>SS</sub> | PWDNB                  | DV <sub>DD</sub> |  |

|                  |                  |                        |                  |                     |                        |                        |                  |                        | 20084402         |  |

|                  |                  |                        |                  |                     |                        |                        |                  |                        |                  |  |

|                  |                  |                        |                  |                     |                        |                        |                  |                        |                  |  |

#### **Pin Descriptions**

| Pin Name   | Pin Count   | I/O, Type | Description                                                                                                                                                       |  |  |  |  |

|------------|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DATA PINS  | 1           |           |                                                                                                                                                                   |  |  |  |  |

| DINA0-17   | 18          |           | Transmitter inputs. There is a pull-down circuitry on each of these pins which are                                                                                |  |  |  |  |

| DINB0-17   | 18          | I, LVCMOS | active if respective PWDNA or PWDNB pin is pulled high.                                                                                                           |  |  |  |  |

| DOUTAP     | 1           |           |                                                                                                                                                                   |  |  |  |  |

| DOUTAN     | 1           |           |                                                                                                                                                                   |  |  |  |  |

| DOUTBP     | 1           | O,BLVDS   | Inverting and non-inverting differential transmitter outputs.                                                                                                     |  |  |  |  |

| DOUTAN     | 1           |           |                                                                                                                                                                   |  |  |  |  |

|            | ONTROL PINS | 1         |                                                                                                                                                                   |  |  |  |  |

| TxCLK      | 1           | I, LVCMOS | Transmitter reference clock. Used to strobe data at the inputs and to drive the transmitter PLL. There is a pull-up circuitry on this pin which is always active. |  |  |  |  |

| ENA        | 1           |           | Transmitter outputs enable pins. There is a pull-down circuitry on each of these pins that are active if corresponding PWDNA or PWDNB pin is pulled high.         |  |  |  |  |

| ENB        | 1           | I, LVCMOS | When these pins are set to LOW, the transmitter outputs will be disabled. The PLL will remain locked.                                                             |  |  |  |  |

| PWDNA      | 1           |           | Stand-by mode pins. There is a pull-down circuitry on each of these pins that ar                                                                                  |  |  |  |  |

| PWDNB      | 1           | I, LVCMOS | always active. When these pins are set to LOW, the transmitter will be put in low<br>power mode and the PLL will lose lock.                                       |  |  |  |  |

| SYNCA      | 1           | I, LVCMOS | Transmitter synchronization pins. There is a pull-down circuitry on each of these pins that are active if corresponding PWDNA or PWDNB pin is pulled high.        |  |  |  |  |

| SYNCB      | 1           |           | When these pins are set to HIGH, the transmitter will ignore incoming data and send SYNC patterns to provide a locking reference to receiver(s).                  |  |  |  |  |

| PRE-EMPHAS | IS PINS     |           | ·                                                                                                                                                                 |  |  |  |  |

| PEMA0-2    | 3           |           | 8-level pre-emphasis selection pins. There is a pull-down circuitry on each of                                                                                    |  |  |  |  |

| PEMB0-2    | 3           | I, LVCMOS | these pins which are active if corresponding PWDNA or PWDNB pin is pulled high.                                                                                   |  |  |  |  |

| JTAG PINS  | 1           |           | 5                                                                                                                                                                 |  |  |  |  |

| TDI        | 1           | I, LVCMOS | Test Data Input to support IEEE 1149.1. There is a pull-up circuitry on this pin which is always active.                                                          |  |  |  |  |

| TDO        | 1           | O, LVCMOS | Test Data Output to support IEEE 1149.1.                                                                                                                          |  |  |  |  |

| TMS        | 1           | I, LVCMOS | Test Mode Select Input to support IEEE 1149.1. There is a pull-up circuitry on this pin which is always active.                                                   |  |  |  |  |

| ТСК        | 1           | I, LVCMOS | Test Clock Input to support IEEE 1149.1. There is no failsafe circuitry on this pil                                                                               |  |  |  |  |

| TRST       | 1           | I, LVCMOS | Test Reset Input to support IEEE 1149.1. There is a pull-up circuitry on this pin which is always active.                                                         |  |  |  |  |

| BIST PINS  |             | •         |                                                                                                                                                                   |  |  |  |  |

| BISTA      | 1           | I, LVCMOS | BIST selection pins. These pins select which transmitter will generate a PRBS                                                                                     |  |  |  |  |

| BISTB      | 1           | -         | like data. There is a pull-down circuitry on these pins which are active if corresponding PWDNA or PWDNB pin is pulled high.                                      |  |  |  |  |

| POWER PINS |             |           |                                                                                                                                                                   |  |  |  |  |

| AVDD       | 6           | I, POWER  | Power Supply for the LVDS circuitry.                                                                                                                              |  |  |  |  |

| DVDD       | 8           | I, POWER  | Power Supply for the digital circuitry.                                                                                                                           |  |  |  |  |

| PVDD       | 5           | I, POWER  | Power Supply for the PLL and BG circuitry.                                                                                                                        |  |  |  |  |

| AVSS       | 5           | I, POWER  | Ground reference for the LVDS circuitry.                                                                                                                          |  |  |  |  |

| DVSS       | 10          | I, POWER  | Ground reference for the digital circuitry.                                                                                                                       |  |  |  |  |

| PVSS       | 5           | I, POWER  | Ground reference for the PLL and BG circuitry.                                                                                                                    |  |  |  |  |

| OTHER PINS |             |           | •                                                                                                                                                                 |  |  |  |  |

| NC         | 1           | N/A       | Not connected.                                                                                                                                                    |  |  |  |  |