# **SIEMENS**

# 2.6 MBit Dynamic Sequential Access Memory for Television Applications (TV-SAM)

**SDA 9253**

### **Preliminary Data**

CMOS IC

#### **Features**

- $212 \times 64 \times 16 \times 12$ -bit organization

- Triple port architecture

- One 16 × 12-bit input shift register

- Two 16 × 12-bit output shift registers

- Shift registers independently and simultaneously accessible

- Continuous data flow even at maximum speed

- 40-MHz shift rate 0.96-Gbit/s total data rate

- All inputs and outputs TTL-compatible

- Tristate outputs

- Random access of groups of 16 x 12 bits for a wide range of applications

- Refresh-free operation possible

- 5 V  $\pm$  10 % power supply

- 0 ... 70 °C operating temperature range

- Low power dissipation: 700 mW active, 28 mW standby

- Suitable for all common TV standards

- Allows flicker and noise reduction simultaneously with only one field memory

- Applications: TV, VCR, image processing, video printers, data compressors, delay lines, time base correctors, HDTV

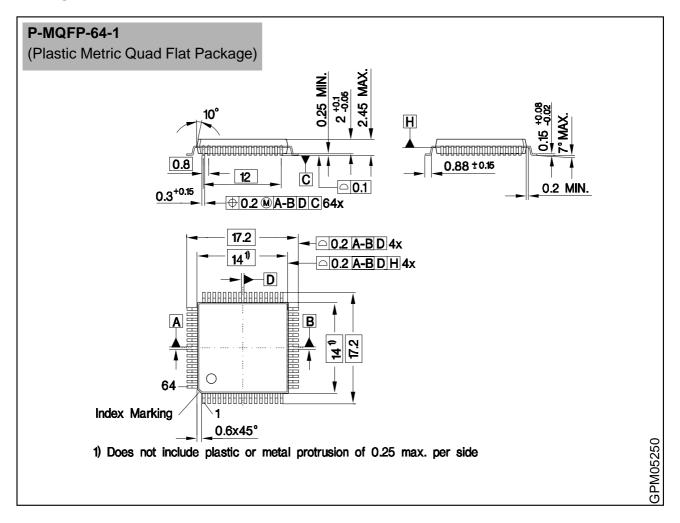

| Туре     | Ordering Code | Package     |  |  |

|----------|---------------|-------------|--|--|

| SDA 9253 | Q67101-H5171  | P-MQFP-64-1 |  |  |

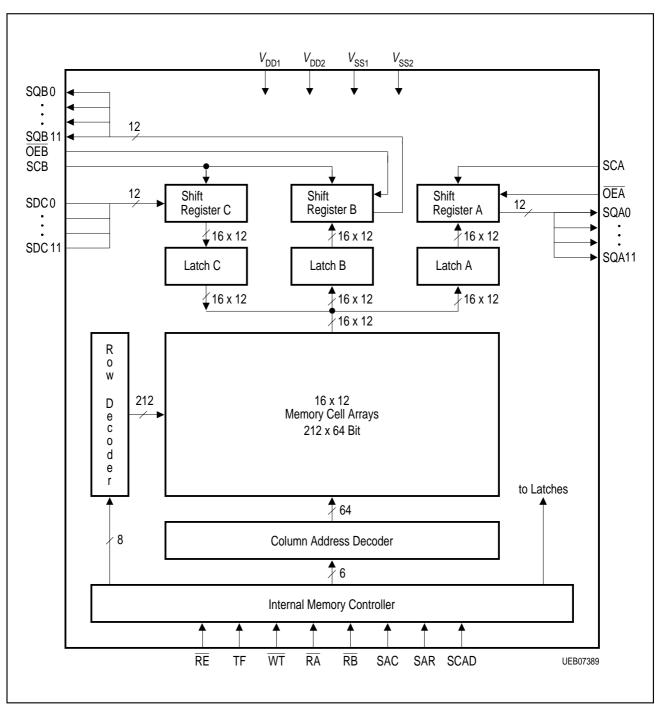

#### **Functional Description**

The SDA 9253 is a triple port 2605056 bit dynamic sequential-access memory for high-data-rate video applications. It is organized as 212 rows by 64 columns by 16 arrays by 12 bit to allow for the storage of 12-bit planes of a TV field (NTSC, PAL, SECAM, MAC) in standard or studio quality (13.5-MHz basic sample rate) or 12-bit planes of parts of a HDTV field. The memory is fabricated using the same CMOS technology used for 4-Mbit standard dynamic random access memories.

The extremely high maximum data rate is achieved by three internal shift registers, each of 16-bit length and 12-bit width, which perform a serial to parallel conversion between the asynchronous input/output data streams and the memory array. The parallel data transfer from the  $16 \times 12$ -bit input shift register C to an addressed location of the memory array and from the memory array to one of the  $16 \times 12$ -bit output shift registers A or B is controlled by the serial row-(SAR) and column address (SAC) which contains the desired column address and an instruction code (mode bits) for transfer and refresh.

#### **Circuit Description**

#### **Memory Architecture**

As shown in the block diagram, the TV-SAM comprises 192 memory arrays, which are accessed in parallel. Each memory array has a size of 212 rows by 64 columns. The rows and columns of the 192 arrays can be randomly addressed, reading or writing  $16 \times 12$  bits at a time. To obtain the extremely high data rate at the 12-bit wide data input (SDC) and outputs (SQA, SQB), a parallel to serial conversion is done using shift registers of 16-bit length and 12-bit width. In this way the memory speed is increased by a factor of 16. (This is independent on the number of ports if the total data rate is regarded.)

Independent operation of the serial input and the two serial outputs is guaranteed by using three shift registers. The decoupling from the common  $16 \times 12$ -bit memory data bus is done by three latches which allow a flexible memory timing and a flying real-time data transfer.

A real-time data transfer is necessary to ensure a continuous data flow at the data pins even at maximum clock speed.

To save pins without loosing speed, the TV-SAM is addressed serially using a serial 8-bit row address and a serial 8-bit column address which includes two mode control bits. The serial row and column addresses are converted to parallel addresses internally, then latched and fed to the row and column decoders. The internal memory controller is responsible for the timing of the memory read/write access and the refresh operation.

#### Data Input (SDC, SCB)

Data are shifted in through the serial port C (SDC0, ..., SDC11) at the rising edge of the shift clock SCB. After 16 clock pulses the data have to be transferred from shift register C to latch C. If more than 16 clock pulses occur before latching the data, only the last sixteen 12-bit data values are accepted.

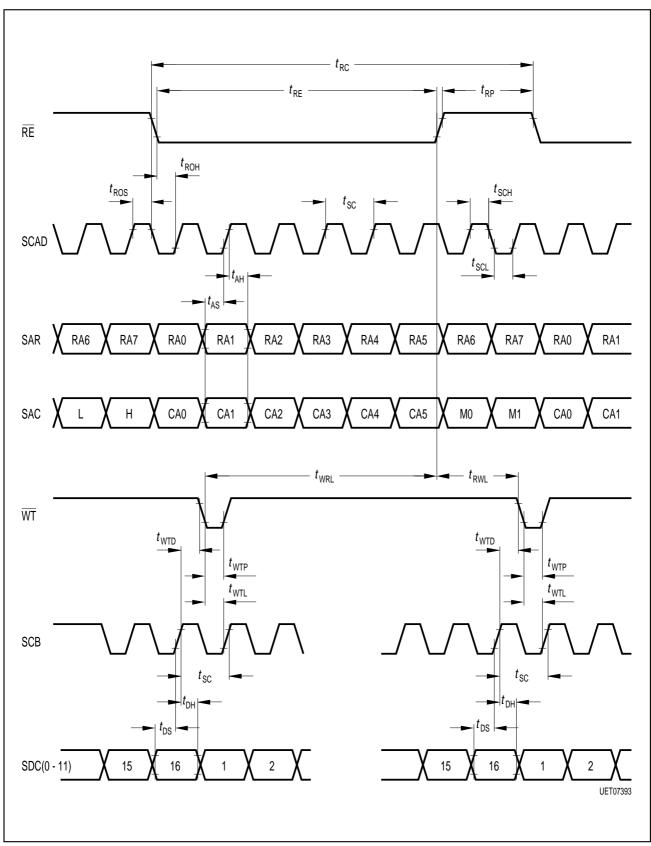

#### Data Transfer from Shift Register C to Latch C (WT)

The contents of the shift register C are transferred to latch C at the falling edge of the write transfer signal  $\overline{WT}$ . If the timing restrictions between  $\overline{WT}$  and the clock SCB are respected, a continuous data flow at input SDC is possible without loosing data. This transfer operation may be asynchronous to all other transfer operations except for a small forbidden window conditioned by the latch C to memory transfer, see **diagram 4**.

#### Write Transfer from Latch C to Memory (RE)

The data of latch C are transferred to the preaddressed location of the memory array at the rising edge of  $\overline{RE}$ , if the mode bits were set to H (M1) and L (M0), see "Addressing and Mode Control."

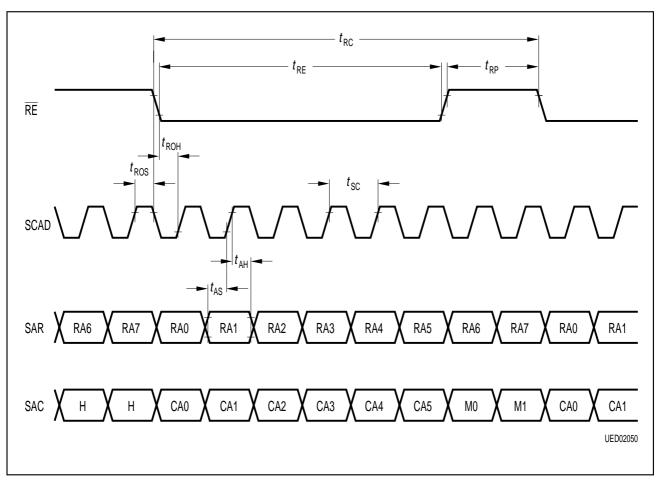

### Addressing and Mode Control (SAR, SAC, SCAD, RE)

The serial 8-bit row address SAR and the 8-bit column address/mode code SAC are serially shifted into the TV-SAM (LSB first) at rising edge of the address clock SCAD. After 8 SCAD cycles, the falling edge of  $\overline{RE}$  internally latches SAR and SAC. The column address itself needs only 6 bits. The last 2 bits of SAC are defined as mode bits and determine the read/write and refresh operation of the memory arrays to be triggered by the  $\overline{RE}$  signal.

| Mode Bit M1 | Mode Bit M0 | Operation                             |  |  |  |  |

|-------------|-------------|---------------------------------------|--|--|--|--|

| L           | L           | Read transfer from memory to latch A  |  |  |  |  |

| L           | Н           | Read transfer from memory to latch B  |  |  |  |  |

| Н           | L           | Write transfer from latch C to memory |  |  |  |  |

| Н           | Н           | Refresh with internal row address     |  |  |  |  |

# Read Transfer from Memory to Latch A or B (RE)

Memory data from a preaddressed location are transferred to latch A or B at the falling edge of RE, depending on the mode control bits, see "Addressing and Mode Control".

#### Data Transfer from Latch A to Shift Register A (RA)

The contents of latch A are transferred to shift register A at the falling edge of the read transfer signal  $\overline{RA}$ . If the timing restrictions between  $\overline{RA}$  and the shift clock SCA are taken into account, a continuous data flow at output SQA without interrupts is possible. This transfer operation is independent on all other transfer operations except for a small forbidden time window conditioned by the memory to latch A transfer.

#### Data Transfer from Latch B to Shift Register B (RB)

The contents of latch B are transferred to shift register B at the falling edge of the read transfer signal  $\overline{RB}$ . If the timing restrictions between  $\overline{RB}$  and the shift clock SCB are taken into account, a continuous data flow at output SQB without interrupts is possible. This transfer operation is independent on all other transfer operations except for a small forbidden time window conditioned by the memory to latch B transfer.

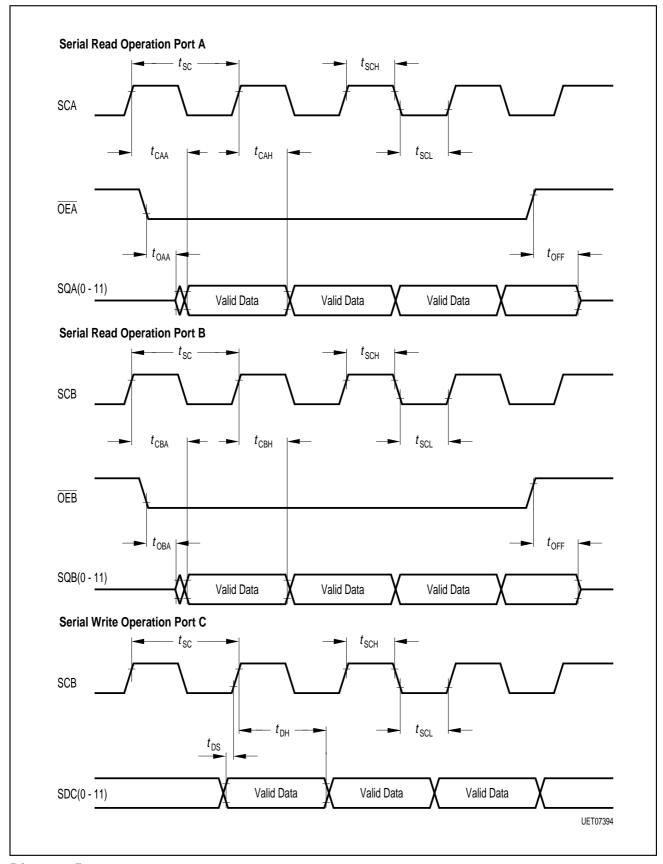

#### Data Output A (SQA, SCA, OEA)

Data is shifted out through the serial port A (SQA0 ... SQA11) at the rising edge of the shift clock SCA. After 16 clock cycles new data have to be transferred from latch A to shift register A. Otherwise data values are cyclically repeated.

Via the output enable  $\overline{OEA}$  the output buffers can be switched into tristate.

The shift clock SCA may be completely independent on the shift clock for port B and C (SCB).

#### Data Output B (SQB, SCB, OEB)

Data is shifted out through the serial port B (SQB0 ... SQB11) at the rising edge of the shift clock SCB. After 16 clock cycles new data have to be transferred from latch B to shift register B. Otherwise data values are cyclically repeated. The shift clock SCB is also used for the input port C. Via the output enable  $\overline{\text{OEB}}$  the output buffers can be switched into tristate.

#### Refresh

Either 256 refresh cycles or read/write cycles on 212 consecutive row addresses beginning with address 0 have to be executed within an 16 ms interval to maintain the data in the memory arrays. A refresh cycle is determined by the mode control bits, see "Addressing and Mode Control". In the refresh mode, the row and column addresses are ignored.

#### Initialization

The device incorporates an on-chip substrate bias generator as well as dynamic circuitry. Therefore an initial pause of 200  $\mu$ s is required after power on, followed by eight  $\overline{\text{RE}}$ -cycles before proper device operation is achieved.

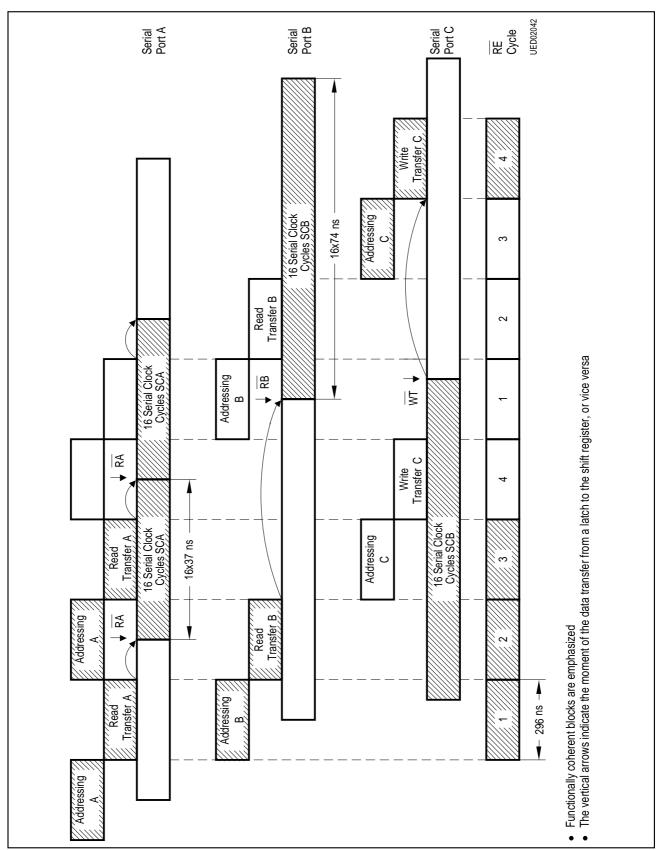

#### **Typical Memory Cycle Sequence**

A typical application of the TV-SAM is a real-time interfield image processing combined with flicker reduction. This can be achieved, for example, by writing and reading with 13.5-MHz clock rate via port C and B and by simultaneously reading port A with 27-MHz double speed clock. A main cycle of 4 consecutive  $\overline{\text{RE}}$  cycles of transfer is needed:

1st. Read transfer from memory to latch A

2nd. Read transfer from memory to latch B

3rd.  $\overline{RE}$ -cycle: Same as 1st.  $\overline{RE}$  cycle

4th. RE-cycle: Write transfer from latch C to memory

Each transfer cycle is preceded by an address cycle as shown in the diagram page 6:

For the clock rates mentioned this means a serial cycle time of 74 ns at port B and C and 37 ns at port A. The addressing cycle time for each port is given by 16 times the serial data rate. Thus we have an addressing cycle time of approx. 1184 ns for port B and port C. The address for port A must be loaded every 592 ns. Since all addresses are shifted in sequentially, a  $\overline{RE}$  cycle time of approx. 296 ns is necessary.

The beginning of a block of 16 serial data at port A or B is determined by  $\overline{RA}$  and  $\overline{RB}$ , respectively. The end of the serial input data block at port C is controlled by  $\overline{WT}$ . Since  $\overline{RA}$ ,  $\overline{RB}$  and  $\overline{WT}$  can be independently chosen (except for small forbidden time windows when memory transfers are executed), the serial data streams can be shifted against each other without influencing the  $\overline{RE}$  cycles.

Figure 1

Typical Memory Cycle Sequence

# **SIEMENS**

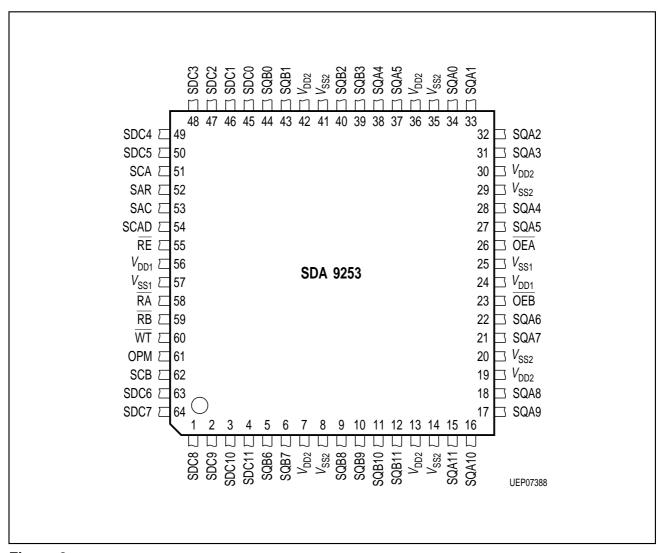

### **Pin Configuration**

(top view)

Figure 2

### **Pin Definitions and Functions**

| Pin No.                  | Symbol        | Input (I)<br>Output (O) | Function                                                           |  |  |  |

|--------------------------|---------------|-------------------------|--------------------------------------------------------------------|--|--|--|

| 34<br>33<br>16<br>15     | SQA0<br>SQA11 | 0<br>0<br>0             | Serial data output for port A                                      |  |  |  |

| 51                       | SCA           | 1                       | Serial clock input for port A                                      |  |  |  |

| 58                       | RA            | I                       | Read transfer control input (latch A to shift register A)          |  |  |  |

| 26                       | OEA           | I                       | Output enable input for port A                                     |  |  |  |

| 44<br>43<br>11<br>12     | SQB0<br>SQB11 | 0 0 0                   | Serial data output for port B                                      |  |  |  |

| 62                       | SCB           | 1                       | Serial clock input for port B and C                                |  |  |  |

| 59                       | RB            | I                       | Read transfer control input (latch B to shift register B)          |  |  |  |

| 23                       | OEB           | ı                       | Output enable input for port B                                     |  |  |  |

| 45<br>46<br>3<br>4       | SDC0<br>SDC11 |                         | Serial data input for port C                                       |  |  |  |

| 60                       | WT            | ı                       | Write transfer control input (shift register C to latch C)         |  |  |  |

| 52                       | SAR           | ı                       | Serial row address input                                           |  |  |  |

| 53                       | SAC           | 1                       | Serial column address and mode control input                       |  |  |  |

| 54                       | SCAD          | I                       | Serial address clock input                                         |  |  |  |

| 55                       | RE            | I                       | RAM-enable input (also latches the addresses)                      |  |  |  |

| 7, 13, 19,<br>30, 36, 42 | $V_{DD2}$     |                         | Data output power supply (+ 5 V)                                   |  |  |  |

| 8, 14, 20,<br>29, 35, 41 | $V_{ m SS2}$  |                         | Data output power supply (GND)                                     |  |  |  |

| 24, 56                   | $V_{DD1}$     |                         | Memory power supply (+ 5 V), must be connected to $V_{ m DD2}$     |  |  |  |

| 25, 57                   | $V_{ m SS1}$  |                         | Memory power supply (GND), must be connected to $V_{\mathrm{SS2}}$ |  |  |  |

| 61                       | ОРМ           |                         | Test function (for factory use only)                               |  |  |  |

Figure 3 Block Diagram

# **SIEMENS**

# **Absolute Maximum Ratings**

| Parameter                        | Symbol     | Lim        | it Values | Unit | Remarks              |

|----------------------------------|------------|------------|-----------|------|----------------------|

|                                  |            | min.       | max.      |      |                      |

| Storage temperature              | $T_{stg}$  | - 55       | 125       | °C   |                      |

| Soldering temperature            | $T_{sold}$ |            | 260       | °C   |                      |

| Soldering time                   | $t_{sold}$ |            | 10        | s    |                      |

| Input/output voltage             | $V_{I/Q}$  | <b>-1</b>  | 7         | V    |                      |

| Test function input voltage      | $V_{I}$    | <b>– 1</b> | 7         | V    | For factory use only |

| Power supply voltage             | $V_{DD}$   | <b>- 1</b> | 7         | V    |                      |

| Data out current (short circuit) | $I_{Q}$    |            | 10        | mA   |                      |

| Total power dissipation          | $P_{tot}$  |            | 1.2       | W    |                      |

| Power dissipation per output     | $P_{Q}$    |            | 60        | mW   |                      |

# **Operating Range**

| Parameter           | Symbol             |       | Limit Val | Unit |    |

|---------------------|--------------------|-------|-----------|------|----|

|                     |                    | min.  | typ.      | max. |    |

| Supply voltage      | $V_{DD1}$          | 4.5   | 5.0       | 5.5  | V  |

| Supply voltage      | $V_{DD2}$          | 4.5   | 5.0       | 5.5  | V  |

| Supply voltage      | $V_{\mathtt{SS1}}$ |       | 0         |      | V  |

| Supply voltage      | $V_{\mathtt{SS2}}$ |       | 0         |      | V  |

| H-input voltage     | $V_{IH}$           | 2.0   |           | 6.5  | V  |

| L-input voltage     | $V_{IL}$           | - 1.0 |           | 0.8  | V  |

| Ambient temperature | $T_{A}$            | 0     | 25        | 70   | °C |

### **DC Characteristics**

$V_{\rm DD}$  = 5 V  $\pm$  10 %;  $T_{\rm A}$  = 0 to 70  $^{\circ}{\rm C}$

| Parameter                      | Symbol        | L           | imit Valu         | es     | Unit | Test Condition                                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------------|---------------|-------------|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                |               | min.        | typ.              | max.   |      |                                                                                                                                                                                                                                                                                                                                                                       |  |

| Test enable input high voltage | $V_{IH}$ OPM  | 4.5         |                   | 5.5    | V    | At normal operation the pin OPM has to be connected to 1/2 $V_{\rm DD1}$ OPM level or left unconnected.                                                                                                                                                                                                                                                               |  |

| Test disable input low voltage | $V_{IL}OPM$   | - 10 %      | $1/2 V_{\rm DD1}$ | + 10 % | V    | See test enable input high voltage                                                                                                                                                                                                                                                                                                                                    |  |

| H-output voltage               | $V_{QH}$      | 2.4         |                   |        | V    | $I_{\rm OUT} = -2.5 \; {\rm mA}$                                                                                                                                                                                                                                                                                                                                      |  |

| L-output voltage               | $V_{QL}$      |             |                   | 0.4    | V    | $I_{\text{OUT}}$ = 2.1 mA                                                                                                                                                                                                                                                                                                                                             |  |

| Input leakage current          | $I_{I(L)}$    | <b>– 10</b> |                   | 10     | μΑ   | $0 \ V \le V_1 \le 6.5 \ V$                                                                                                                                                                                                                                                                                                                                           |  |

| Output leakage current         | $I_{ m Q(L)}$ | - 10        |                   | 10     | μΑ   | $\overline{OEA} = \overline{OEB} = V_IH$                                                                                                                                                                                                                                                                                                                              |  |

| Average supply current         | $I_{CCa}$     |             |                   | 200    | mA   | $(t_{\rm SC} \ {\rm port} \ {\rm A} = t_{\rm SC} \ {\rm min})$ $(t_{\rm SC} \ {\rm port} \ {\rm B} = 2 \ t_{\rm SC} \ {\rm min})$ $(t_{\rm SC} \ {\rm port} \ {\rm C} = 2 \ t_{\rm SC} \ {\rm min})$ $(t_{\rm RC} = t_{\rm RC} \ {\rm min})$ $I_{\rm CCa} \ {\rm depends \ on \ cycle \ rate}$ and on output loading. Specified values are measured with open output. |  |

| Standby supply current         | $I_{CCb}$     |             |                   | 5      | mA   | $(\overline{\text{RE}} = \overline{\text{OEA}} = \overline{\text{OEB}} = V_{\text{DD1}})$<br>$t_{\text{SC}}$ (SCA, SCB, SCAD) = max. $(t_{\text{SC}})$                                                                                                                                                                                                                |  |

# **SIEMENS**

**AC Characteristics**

$V_{\rm DD}$  = 5 V  $\pm$  10 %;  $T_{\rm A}$  = 0 to 70 °C

| Parameter                             | Symbol          |      | Limit Val | lues   | Unit | Test Condition                                                                                                                                                             |

|---------------------------------------|-----------------|------|-----------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       |                 | min. | typ.      | max.   |      |                                                                                                                                                                            |

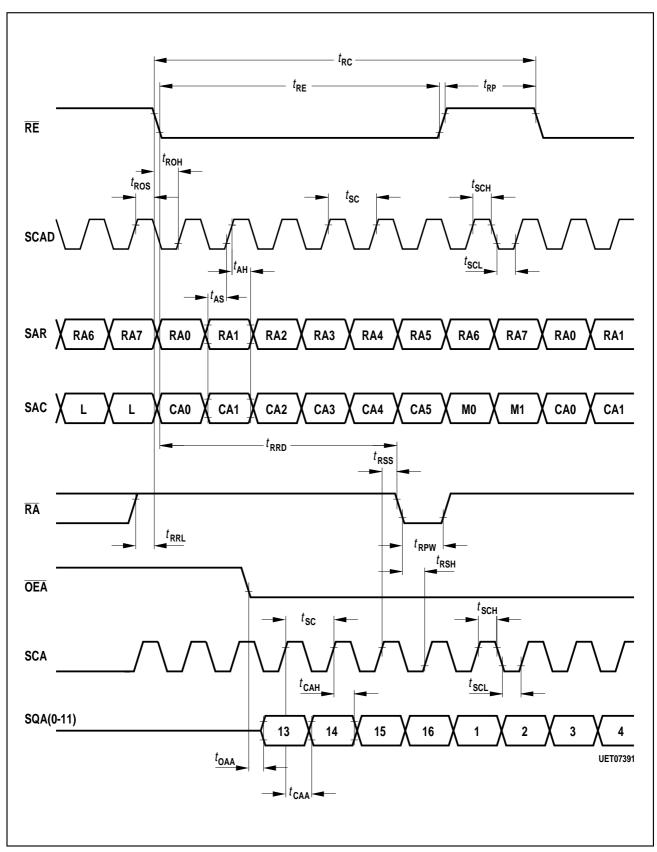

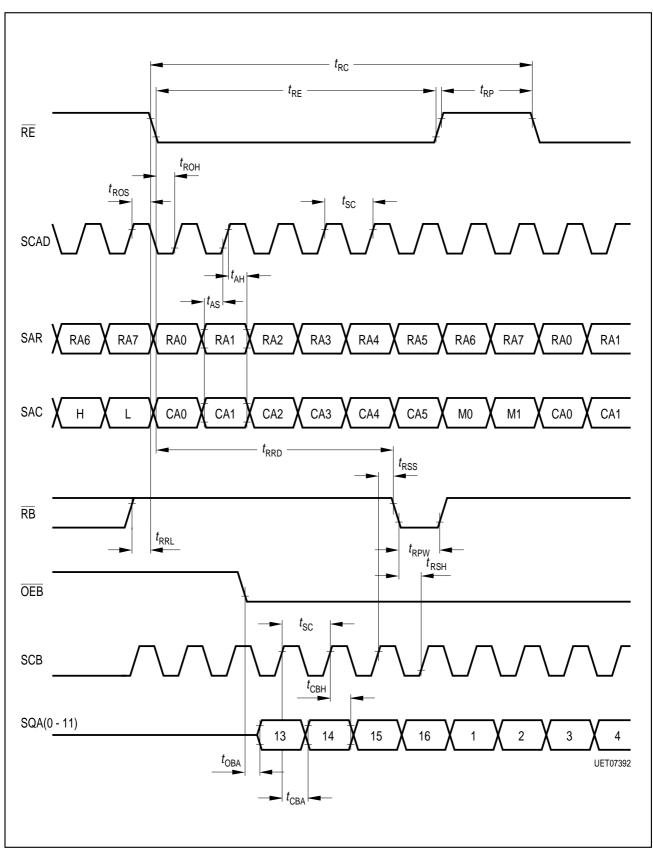

| Memory read or write cycle time       | t <sub>RC</sub> | 240  |           | 100000 | ns   | Operation with $t_{RC} \ge t_{RCmin}$ ensures that 8-bit serial data are shifted out within one $\overline{RE}$ cycle taking $t_{SC} = t_{SCmin}$ . See diagram 2, 3, 4, 6 |

| RE low time                           | $t_{RE}$        | 100  |           | 100000 | ns   | See diagram 2, 3, 4, 6                                                                                                                                                     |

| Serial port cycle time                | $t_{\rm SC}$    | 30   |           | 100000 | ns   | See diagram 2 – 6                                                                                                                                                          |

| RE precharge time                     | $t_{RP}$        | 100  |           |        | ns   | See diagram 2, 3, 4, 6                                                                                                                                                     |

| Address setup time                    | t <sub>AS</sub> | 5    |           |        | ns   | See diagram 2, 3, 4, 6                                                                                                                                                     |

| Address hold time                     | t <sub>AH</sub> | 6    |           |        | ns   | See diagram 2, 3, 4, 6                                                                                                                                                     |

| SCAD to RE set-up time                | $t_{ROS}$       | 3    |           |        | ns   | See diagram 2, 3, 4, 6                                                                                                                                                     |

| RE to SCAD hold time                  | $t_{ROH}$       | 10   |           |        | ns   | See diagram 2, 3, 4, 6                                                                                                                                                     |

| RE to RA or RB delay time             | $t_{RRD}$       | 90   |           |        | ns   | <ul> <li>t<sub>RRD</sub> and t<sub>RRL</sub> are restrictive operating parameters only in memory read transfer cycles.</li> <li>See diagram 2, 3</li> </ul>                |

| RA or RB to RE lead time              | $t_{RRL}$       | - 30 |           |        | ns   | See RE to RA or RB delay time.  See diagram 2, 3                                                                                                                           |

| RA to SCA<br>RB to SCB<br>set-up time | $t_{RSS}$       | 0    |           |        | ns   | See diagram 2, 3                                                                                                                                                           |

| RA or RB pulse width                  | $t_{RPW}$       | 10   |           |        | ns   | See diagram 2, 3                                                                                                                                                           |

| RA to SCA<br>RB to SCB<br>hold time   | $t_{RSH}$       | 15   |           |        | ns   | See diagram 2, 3                                                                                                                                                           |

# AC Characteristics (cont'd)

$V_{\rm DD}$  = 5 V  $\pm$  10 %;  $T_{\rm A}$  = 0 to 70 °C

| Parameter                                                  | Symbol           | Limit Values |      |      | Unit | Test Condition                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------|------------------|--------------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            |                  | min.         | typ. | max. |      |                                                                                                                                                                                                                                                                                                   |

| WT to RE lead time                                         | $t_{WRL}$        | 30           |      |      | ns   | $t_{\rm WRL}$ and $t_{\rm RWL}$ are restrictive operating parameters only in memory write transfer cycles. In that case $t_{\rm WRL}$ applies if the write transfer from shifter C to latch C occurs before the rising edge of $\overline{\rm RE}$ . Otherwise $t_{\rm RWL}$ has to be satisfied. |

| $\overline{\text{RE}}$ to $\overline{\text{WT}}$ lead time | $t_{RWL}$        | 50           |      |      | ns   | See WT to RE lead time                                                                                                                                                                                                                                                                            |

| Output buffer turn-<br>off delay                           | t <sub>OFF</sub> | 0            |      | 20   | ns   | t <sub>OFF</sub> (max) defines the time at which the output achieves the open-circuit condition and is not referenced to output voltages levels.                                                                                                                                                  |

| WT to SCB delay time                                       | $t_{WTD}$        | 0            |      |      | ns   | See diagram 4                                                                                                                                                                                                                                                                                     |

| WT to SCB lead time                                        | $t_{ m WTL}$     | 15           |      |      | ns   | See diagram 4                                                                                                                                                                                                                                                                                     |

| WT pulse width                                             | $t_{WTP}$        | 10           |      |      | ns   | See diagram 4                                                                                                                                                                                                                                                                                     |

| OEA to output A access time                                | t <sub>OAA</sub> |              |      | 25   | ns   | See diagram 2, 5                                                                                                                                                                                                                                                                                  |

| OEB to output B access time                                | t <sub>OBA</sub> |              |      | 25   | ns   | See diagram 3, 5                                                                                                                                                                                                                                                                                  |

| Access time from SCA                                       | $t_{CAA}$        |              |      | 25   | ns   | See diagram 2                                                                                                                                                                                                                                                                                     |

| Access time from SCB                                       | $t_{CBA}$        |              |      | 25   | ns   | See diagram 3                                                                                                                                                                                                                                                                                     |

| Data input set-up time to SCB                              | $t_{ m DS}$      | 5            |      |      | ns   | See diagram 5                                                                                                                                                                                                                                                                                     |

| Data input hold time to SCB                                | $t_{DH}$         | 6            |      |      | ns   | See diagram 5                                                                                                                                                                                                                                                                                     |

# AC Characteristics (cont'd)

$V_{\rm DD} = 5 \text{ V} \pm 10 \text{ %}; T_{\rm A} = 0 \text{ to } 70 \text{ °C}$

| Parameter                                     | Symbol                 |      | Limit Val | lues | Unit | Test Condition                                                                                                                                  |  |

|-----------------------------------------------|------------------------|------|-----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                               |                        | min. | typ.      | max. |      |                                                                                                                                                 |  |

| Refresh period                                | $t_{REF}$              |      |           | 16   | ms   | Either 256 refresh cycles or read/write cycles on 212 consecutive row addresses have to be performed within the 16 ms interval to maintain data |  |

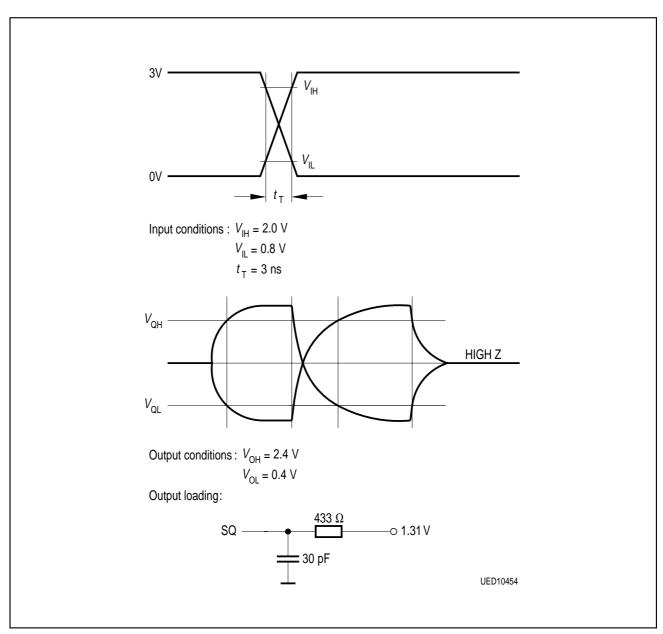

| Transition time (rise/fall)                   | $t_{T}$                | 2    |           | 10   | ns   | Transition times are measured between $V_{\rm IL}$ and $V_{\rm IL}$ . See diagram 1                                                             |  |

| L-serial clock time                           | $t_{ m SCL}$           | 10   |           |      | ns   | See diagram 2                                                                                                                                   |  |

| H-serial clock time                           | $t_{SCH}$              | 10   |           |      | ns   | See diagram 2                                                                                                                                   |  |

| Hold time from SCA                            | $t_{CAH}$              | 6    |           |      | ns   | See diagram 2                                                                                                                                   |  |

| Hold time from SCB                            | $t_{CBH}$              | 6    |           |      | ns   | See diagram 3                                                                                                                                   |  |

| Input capacitance (SCA, SCB)                  | <i>C</i> <sub>11</sub> |      |           | 7    | pF   | f = 1 MHz                                                                                                                                       |  |

| Input capacitance (all other pins)            | $C_{12}$               |      |           | 5    | pF   | f = 1 MHz                                                                                                                                       |  |

| Output capacitance<br>(SQA 0-11,<br>SQB 0-11) | $C_{Q}$                |      |           | 7    | pF   | f = 1 MHz                                                                                                                                       |  |

# **SIEMENS**

### **Operation Truth Table**

|      | R          | E Cycle N  |    | RE Cycle N + n, n = 1, 2, 3 |     |     |     |     |    |    |    |                                         |

|------|------------|------------|----|-----------------------------|-----|-----|-----|-----|----|----|----|-----------------------------------------|

| SCAD | SAR        | SAC        | Мс | ode                         | OEA | OEB | SCA | SCB | RA | RB | WT | Operation                               |

|      |            |            | M0 | M1                          |     |     |     |     |    |    |    |                                         |

|      | RA0RA<br>7 | CA0CA<br>5 | L  | L                           | Х   | Х   | Х   | Х   | \  | Х  | Х  | Read transfer from memory to shifter A  |

|      | RA0RA<br>7 | CA0CA<br>5 | Н  | L                           | Х   | Х   | Х   | Х   | Х  |    | Х  | Read transfer from memory to shifter B  |

|      | RA0RA<br>7 | CA0CA<br>5 | L  | Н                           | Х   | Х   | Х   | Х   | Х  | Х  |    | Write transfer from shifter C to memory |

|      | Х          | Х          | Н  | Н                           | Х   | Х   | Х   | Х   | Х  | Х  | Х  | Refresh with internal row address       |

| X    | Х          | X          | Х  | Х                           | L   | Х   |     | Х   | Х  | Х  | Х  | Serial read port A                      |

| X    | Х          | Х          | Х  | Х                           | Х   | L   | Х   |     | Х  | Х  | Х  | Serial read port B                      |

| X    | Х          | Х          | Х  | Х                           | Х   | Х   | Х   |     | Х  | Х  | Х  | Serial read port C                      |

**Note:** X = Don't care

Row address, column address and mode bits have to be  $V(\text{TF}) = 1/2 \ V_{\text{DD1}} \ (\text{TF})$  or not connected defined in  $\overline{\text{RE}}$  cycle N in order to become effective in  $\overline{\text{RE}}$ cycle N + 1

Diagram 1 AC-Timing Measuring Conditions

Diagram 2 Read Transfer Memory to Port A

Diagram 3

Read Transfer Memory to Port B

Diagram 4

Write Transfer from Port C to Memory

# **SIEMENS**

Diagram 5

Diagram 6 Refresh with External Row Address

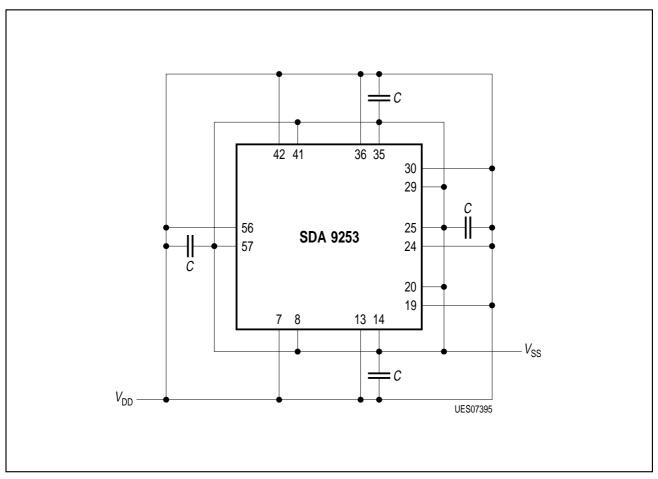

#### **Application Circuit**

For best performance and operation within the specified AC parameter limits it is mandatory to use separate decoupling capacitors for  $V_{\rm SS1}/V_{\rm DD1}$  and  $V_{\rm SS2}/V_{\rm DD2}$  with  $V_{\rm SS1}$  shorted to  $V_{\rm DD2}$  on the board as shown in figure below.

Decoupling capacitors  $C_1$  and  $C_2$  of low inductance multilayer type (at least 0.1  $\mu$ F) should be used. To avoid malfunction or even permanent damage of the device it is strongly recommended not to use any other supply configuration.

Figure 4

# **SIEMENS**

#### **Application Information**

#### Digital Storage of a TV Field

As standard for digital TV systems, CCIR recommendation 601 defines a field of 288 lines with 720 pixels per line. The sampling frequency is 13.5 MHz with a resolution of 8 bit per pixel.

Information is stored in 3 different channels: one channel for luminance (Y), two channels for chrominance (U and V).

The bandwidth ratio between the different channels is either Y:U:V = 4:1:1, 4:2:2 or 4:4:4 depending on the coding method.

The following table shows the memory requirements for the field buffer and the number of memory chips when the SDA 9253 and the SDA 9251 are used.

Table 1

Memory Requirements and Number of Memory Chips for a Digital TV-Field Buffer

| Y:U:V | Clock Rate<br>13.5 MHz | Number of Required Memory Devices | Bus Width |

|-------|------------------------|-----------------------------------|-----------|

| 4:1:1 | 2.37 Mbit              | 1 SDA 9253                        | 12 bit    |

| 4:2:2 | 3.16 bit               | 1 SDA 9253 +<br>1 SDA 9251        | 16 bit    |

| 4:4:4 | 4.75 bit               | 2 SDA 9253                        | 24 bit    |

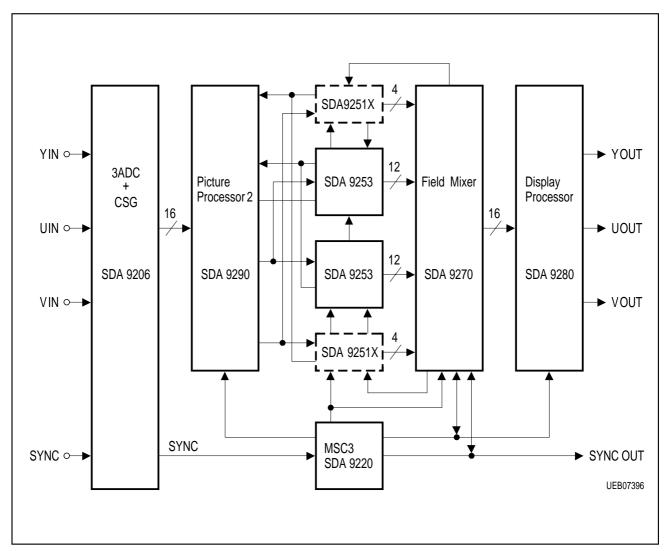

A typical application for the SDA 9253 is as field memory device in the Siemens MEGAVISION system. The memory capacity of the SDA 9253 is 3 times that of SDA 9251 and therefore able to substitute 3 SDA 9251. For a 4:1:1 sampling format there is need for 1 device in an application without Line Flicker Reduction and 2 devices for an application with Line Flicker Reduction (see figure).

Figure 5

MEGAVISION Block Diagram of Line Flicker Reduction

#### **Package Outlines**

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device