**SL34063A**

# DC-TO-DC CONVERTER CONTROL CIRCUITS

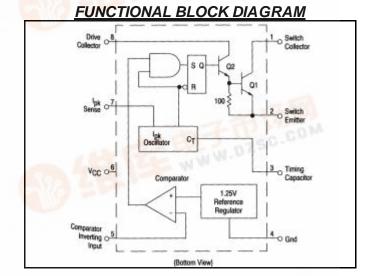

The SL34063A is a monolithic control circuit containing the primary functions required for DC-to-DC converters. These devices consist of an internal temperature compensated reference, comparator, controlled duty cycle oscillator with an active current limit circuit, driver and high current output switch. This series was specifically designed to be incorporated in Step-Down and Step-Up and Voltage-Inverting applications with a minimum number of external components.

# **FEATURES**

- Low Standby Current

Current Limiting

- Output Switch Current to 1.5 A

- Output Voltage Adjustable

- Frequency Operation to 100 kHz

- Precision 2% Reference

## **MAXIMUM RATINGS**

| Rating                                           | Symbol                 | Value       | Unit    |

|--------------------------------------------------|------------------------|-------------|---------|

| Power Supply Voltage                             | V <sub>cc</sub>        | 40          | Vdc     |

| Comparator Input Voltage Range                   | V <sub>IR</sub>        | -0.3 to +40 | Vdc     |

| Switch Collector Voltage                         | V <sub>C(switch)</sub> | 40          | Vdc     |

| Switch Emitter Voltage (Vpin 1 = 40 V)           | V <sub>E(switch)</sub> | 40          | Vdc     |

| Switch Collector to Emitter Voltage              | $V_{CE(switch)}$       | 40          | Vdc     |

| Driver Collector Voltage                         | I <sub>C(driver)</sub> | 40          | Vdc     |

| Driver Collector Current (Note 1)                | I <sub>C(driver)</sub> | 100         | mA      |

| Switch Current                                   | $I_{SW}$               | 1.5         | A       |

| Power Dissipation and Thermal Characteristics    |                        |             | = 47h W |

| Ceramic Package, U Suffix T <sub>A</sub> = +25°C | $P_{D}$                | 1.25        | W       |

| Thermal Resistance                               | $R_{\theta JA}$        | 100         | °C/W    |

| Plastic Package, P Suffix T <sub>A</sub> = +25°C | P <sub>D</sub>         | 1.25        | W       |

| Thermal Resistance                               | $R_{\theta JA}$        | 100         | °C/W    |

| SOIC Package, D Suffix TA = +25°C                | P <sub>D</sub>         | 625         | mW °C/  |

| Thermal Resistance                               | $R_{\theta JA}$        | 160         | W       |

| Operating Junction Temperature                   | TJ                     | +150        | °C      |

| Operating Ambient Temperature Range              | T <sub>A</sub>         | 0 to +70    | °C      |

| Storage Temperature Range                        | Tstg                   | -65to+150   | °C      |

# **SL34063A**

#### ORDERING INFORMATION

| Device   | Temperature Range | Package     |

|----------|-------------------|-------------|

| 34063AD  | 0° to +70°C       | SO-8        |

| 34063AP1 |                   | Plastic DIP |

# Pin connection Switch 1 Switch 2 Finiter 2 Timing 3 Capacitor 3 Gnd 4 (Top View) Priver Collector 7 Ipk Sense 6 VCC Comparator Inverting Input

### **ELECTRICAL CHARACTERICISTICS**

$(V_{CC} = 5.0 \text{ V}, T_A = 0 \text{ to } +70^{\circ}\text{C} \text{ unless otherwise specified.})$

| Characteristics                                                                                                                                | Symbol                | Min    | Тур  | Max    | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|------|--------|------|

| OSCILI                                                                                                                                         | ATOR                  |        |      |        |      |

| Frequency ( $V_{Pin 5} = 0 \text{ V}, C_T = 1.0 \text{ nF}, T_A = 25^{\circ}\text{C}$ )                                                        | fosc                  | 24     | 33   | 42     | kHz  |

| Charge Current ( $V_{CC} = 5.0 \text{ V to } 40 \text{ V}, T_A = 25^{\circ}\text{C}$ )                                                         | Ichg                  | 24     | 33   | 42     | μΑ   |

| Discharge Current (V <sub>CC</sub> = 5.0 V to 40 V, T <sub>A</sub> = 25°C)                                                                     | Idischg               | 140    | 200  | 260    | μΑ   |

| Discharge to Charge Current Ratio (Pin7 to Vcc, T <sub>A</sub> =25°C)                                                                          | Idischg/Ichg          | 5.2    | 6.2  | 7.5    | _    |

| Current Limit Sense Voltage (Ichg = Idischg, T <sub>A</sub> = 25°C)                                                                            | Vlpk(sense)           | 250    | 300  | 350    | mV   |

| OUTPUT SWI                                                                                                                                     | TCH (Note 3)          |        |      |        |      |

| Saturation Voltage, Darlington Connection (I <sub>SW</sub> = 1.0 A, Pins 1, 8 connected)                                                       | V <sub>CE</sub> (sat) | _      | 1.0  | 1.3    | V    |

| Saturation Voltage ( $I_{SW} = 1.0 \text{ A}$ , $R_{Pin 8} = 82 \Omega$ to $V_{CC}$ .<br>Forced $\beta = 20$ )                                 | V <sub>CE</sub> (sat) | _      | 0.45 | 0.7    | V    |

| DC Current Gain ( $I_{SW} = 1.0 \text{ A}, V_{CE} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$ )                                                 | h <sub>FE</sub>       | 50     | 120  | _      | _    |

| Collector Off-State Current (V <sub>CE</sub> = 40V)                                                                                            | I <sub>C</sub> (off)  | _      | 0.01 | 100    | μΑ   |

| COMPA                                                                                                                                          | RATOR                 |        |      |        |      |

| Threshold Voltage (T <sub>A</sub> = 25°C)                                                                                                      | Vth                   | 1.225  | 1.25 | 1.275  | V    |

| $(T_A = T_{LOW} \text{ to } T_{HIGH})$                                                                                                         |                       | 1.21   | _    | 1.29   |      |

| Threshold Voltage (T <sub>A</sub> = 25°C) **                                                                                                   | Vth                   | 1.2375 | 1.25 | 1.2625 | V    |

| Threshold Voltage Line Regulation (V <sub>CC</sub> = 3 0 V to 40 V)                                                                            | Regime                |        | 1.4  | 5.0    | mV   |

| Input Bias Current (Vin=0V)                                                                                                                    | I <sub>IB</sub>       |        | -40  | -400   | nA   |

| TOTAL I                                                                                                                                        | DEVICE                |        |      |        |      |

| Supply Current ( $V_{CC} = 5 \ 0 \ V$ to 40 V, $C_T = 1 \ 0 \ nF$ , $V_{pin7} = V_{CC}$ . $V_{Pin5} > Vth$ , Pin 2 = Gnd, Remaining pins open) | I <sub>cc</sub>       |        | 2.5  | 4.0    | mA   |

#### NOTES:

- 1. Maximum package power dissipation limits must be observed.

- 2.Low duty cycle pulse techniques are used during test to maintain Junction temperature as close to ambient temperature as possible

- 3.If the output switch is driven into hard saturation (non Darlington configuration) at low switch currents (< 300 mA) and high driver currents (>30 mA), it may take up to 2.0  $\mu$ s to come out of saturation This condition will shorten the off' time at frequencies > 30 kHz, and is magnified at high temperatures This condition does not occur with a Darlington configuration, since the output switch cannot saturate If a non Darlington configuration is used, the following output drive condition is recommended

Forced  $\beta$  of output switch =  $I_C$ , output/( $I_C$ , driver -7.0 mA\*) > 10

- \*The 100  $\Omega$ . resistor in the emitter of the driver device requires about 7.0 mA before the output switch conducts

- \*\*Possible version for shipment

\_