PRELIMINARY INFORMATION

(subject to change without notice)

September 24, 2003

<mark>捷多邦,专业PCB打样</mark>工厂,24小时加急出货

# **SLA7060M THRU SLA7062M**

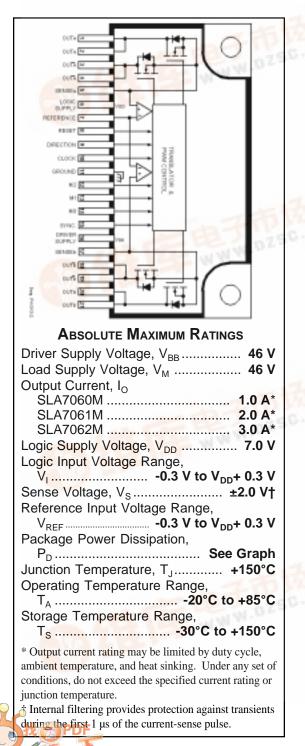

## **UNIPOLAR STEPPER-MOTOR** TRANSLATOR/DRIVERS

Combining low-power CMOS logic with high-current, high-voltage power FET outputs, the Series SLA7060M translator/drivers provide complete control and drive for a two-phase unipolar stepper motor with internal fixed off time and pulse-width modulation (PWM) control of the output current in a power multi-chip module (PMCM<sup>TM</sup>). There are no phase-sequence tables, high-frequency control lines, or complex interfaces to program.

The CMOS logic section provides the sequencing logic, direction, control, synchronous/asynchronous PWM operation, and a "sleep" function. The minimum CLOCK input is an ideal fit for applications where a complex uP is unavailable or overburdened. TTL or LSTTL may require the use of appropriate pull-up resistors to ensure a proper input-logic high. For PWM current control, the maximum output current is determined by the user's selection of a reference voltage and sensing resistor. The NMOS outputs are capable of sinking up to 1, 2, or 3 A (depending on device) and withstanding 46 V in the off state. Clamp diodes provide protection against inductive transients. Special power-up sequencing is not required.

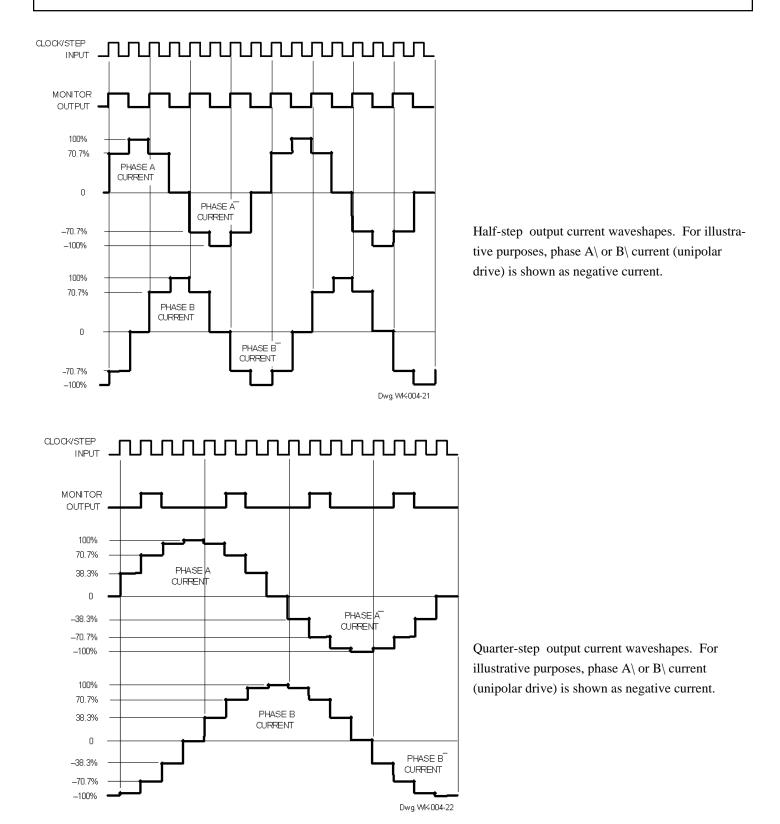

Half-, quarter-, eighth-, and sixteenth-step operation are externally selectable for the SLA7060/61/62M. Half-step excitation alternates between the one-phase and two-phase modes (AB-B-AB-A-AB-B-AB- $\overline{A}$ ), providing an eight-step sequence.

The Series SLA7060M is supplied in a 21-pin single in-line powertab package with leads formed for vertical mounting (suffix LF2102). The tab is at ground potential and needs no insulation. For high-current or high-frequency applications, external heat sinking may be required. This device is rated for continuous operation between -20°C and +85°C.

#### **FEATURES**

- To 3 A Output Rating

- Internal Sequencer for Microstepping Operation

- PWM Constant-Current Motor Drive

- Cost-Effective, Multi-Chip Solution

- 100 V, Avalanche-Rated NMOS

- Low  $r_{_{\text{DS(on)}}}$  NMOS Outputs Advanced, Improved Body Diodes

- Inputs Compatible with 3.3 V or 5 V Control Signals

- Sleep Mode

- Internal Clamp Diodes

Always order by complete part number, e.g., SLA7060MLF2102 .

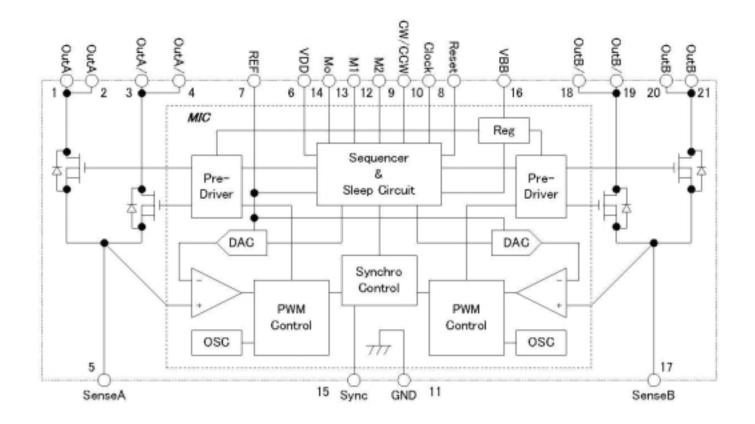

#### **Functional block diagram**

#### **Recommended operating conditions**

| Load Supply Voltage, $V_{BB}$ 10 to 44 V                 | , |

|----------------------------------------------------------|---|

| Logic Supply Voltage, $V_{\text{DD}}$ 3.0 V to 5.5 V     | , |

| Reference Input Voltage, $V_{\text{REF}}$ 0.1 V to 1.0 V | , |

| Tab Temperature (no heat sink), T <sub>T</sub> <90°C     |   |

## **Electrical characteristics:** unless otherwise noted at $T_A = +25$ °C, $V_{BB} = 24$ V, $V_{DD} = 5.0$ V.

|                           |                      |                                               |                        | Limits    |                      |       |

|---------------------------|----------------------|-----------------------------------------------|------------------------|-----------|----------------------|-------|

| Characteristic            | Symbol               | Test Conditions                               | Min.                   | Тур.      | Max.                 | Units |

| Output drivers            |                      | •                                             | •                      |           |                      |       |

| Driver Supply Volt. Range | V <sub>BB</sub>      | Operating                                     | 10                     | _         | 44                   | V     |

| Drain-Source Breakdown    | V <sub>(BR)DS</sub>  | V <sub>BB</sub> = 44 V, I <sub>D</sub> = 1 mA | 100                    | _         | _                    | V     |

| Output On Resistance      | r <sub>DS(on)</sub>  | SLA7060M, I <sub>O</sub> = 1.0 A              | _                      | 700       | 850                  | mΩ    |

|                           | - ( - )              | SLA7061M, I <sub>O</sub> = 2.0 A              | _                      | 250       | 400                  | mΩ    |

|                           |                      | SLA7062M, I <sub>O</sub> = 3.0 A              | _                      | 180       | 240                  | mΩ    |

| Body Diode Forward Volt.  | V <sub>F</sub>       | SLA7060M, I <sub>F</sub> = 1.0 A              | _                      | 0.85      | 1.1                  | V     |

|                           |                      | SLA7061M, I <sub>F</sub> = 2.0 A              | _                      | 0.95      | TBD                  | V     |

|                           |                      | SLA7062M, I <sub>F</sub> = 3.0 A              | _                      | 0.95      | TBD                  | V     |

| Driver Supply Current     | I <sub>BB</sub>      |                                               |                        | _         | 15                   | mA    |

|                           |                      | V <sub>REF</sub> > 2.0 V (sleep mode)         | _                      | _         | 100                  | μA    |

| Control logic             | •                    |                                               | •                      |           |                      |       |

| Logic Supply Volt. Range  | V <sub>DD</sub>      | Operating                                     | 3.0                    | 5.0       | 5.5                  | V     |

| Logic Input Voltage       | V <sub>IH</sub>      |                                               | 0.75V <sub>DD</sub>    | _         | _                    | V     |

|                           | V <sub>IL</sub>      |                                               |                        | _         | 0.25V <sub>DD</sub>  | V     |

| Logic Input Current       | I <sub>IH</sub>      |                                               | —                      | ±1.0      | _                    | μA    |

|                           | I <sub>IL</sub>      | CLOCK, RESET, CW/CCW, and SYNC.               |                        | ±1.0      | _                    | μA    |

|                           |                      | M1 and M2                                     | -25                    | -50       | -75                  | μA    |

| Max. Clock Frequency      | f <sub>clk</sub>     |                                               | 250*                   | _         | _                    | kHz   |

| PWM Off Time              | t <sub>off</sub>     | 70 to 100%I <sub>trip</sub> max               | —                      | 12        | _                    | μs    |

|                           |                      | 38 to 64%l <sub>trip</sub> max                | _                      | 9.0       |                      | μs    |

|                           |                      | 9 to 30%I <sub>trip</sub> max                 |                        | 7.0       | _                    | μs    |

| PWM Min. On Time          | t <sub>on(min)</sub> |                                               |                        | 1.8       | _                    | μs    |

| Ref. Input Voltage Range  | V <sub>REF</sub>     | Operating                                     | 0                      | _         | 1.5                  | V     |

|                           |                      | Sleep mode                                    | 2.0                    | _         | V <sub>DD</sub>      | V     |

| Ref. Input Current        | I <sub>REF</sub>     |                                               | _                      | ±10       | _                    | μA    |

| Monitor Output Voltage    | V <sub>MoH</sub>     |                                               | V <sub>DD</sub> - 1.25 | _         | _                    | V     |

|                           | V <sub>MoL</sub>     |                                               | —                      | _         | 1.25                 | V     |

| Monitor Output Current    | I <sub>Mo</sub>      |                                               | —                      | _         | ±3.0                 | mA    |

| Sense Voltage             | Vs                   | Trip point at 100% I <sub>o</sub>             | 0.95V <sub>REF</sub>   | $V_{REF}$ | 1.05V <sub>REF</sub> | V     |

| Sense Input Current       | I <sub>SENSE</sub>   |                                               | —                      | ±10       | _                    | μA    |

| Propagation Delay Time    | t <sub>PLH</sub>     | Clock rising edge to output on                |                        | 2.0       | _                    | μs    |

|                           | t <sub>PHL</sub>     | Clock rising edge to output off               |                        | 1.5       | _                    | μs    |

| Logic Supply Current      | I <sub>DD</sub>      |                                               |                        | _         | 4.0                  | mA    |

Typical values are given for circuit design information only.

\*Operation at a clock frequency greater than the specified minimum value is possible but not warranted.

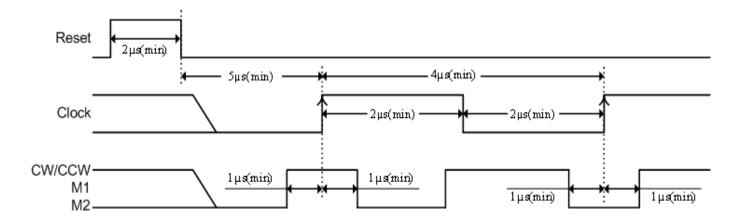

Logic input timing

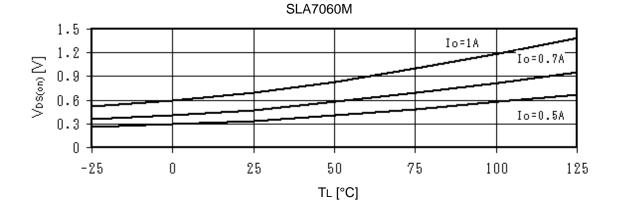

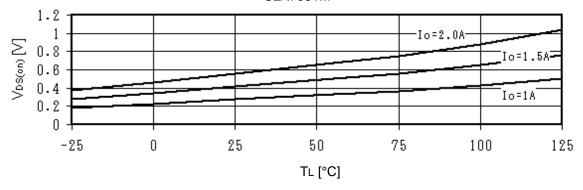

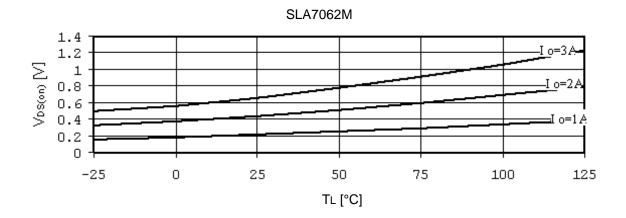

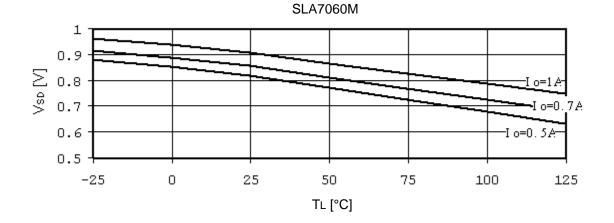

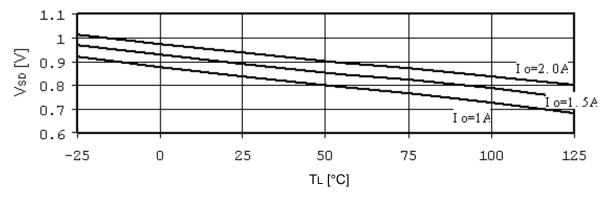

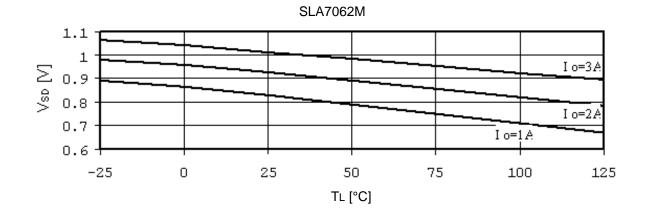

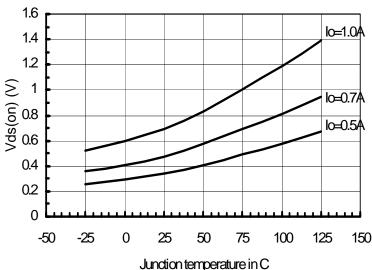

#### **Typical MOSFET characteristics**

SLA7061M

#### Typical body diode characteristics

SLA7061M

#### **Functional description**

**Device operation.** These devices are complete microstepping motor drivers with built in translator for easy operation with minimal control lines. They are designed to operate unipolar stepper motors in half-, quarter-, eighth-, and sixteenth-step modes. The current in each of the four outputs, all n-channel DMOS, is regulated with fixed off time pulse-width modulated (PWM) control circuitry. The current at each step is set by the value of an external current-sense resistor ( $R_s$ ), a reference voltage ( $V_{REF}$ ), and the DAC's output voltage controlled by the output of the translator.

At  $V_{DD}$  power up, or reset, the translator sets the DACs to the home state (see figures for reset conditions). When a step command signal occurs on the CLOCK input the translator automatically sequences the DACs to the next level (see table 2 for the current level sequence). The microstep resolution is set by inputs M1 and M2 as shown in table 1.

**RESET input.** The RESET input sets the translator to a predefined home state (see table 2) and turns off all of the DMOS outputs. The monitor output (MO) goes low and all STEP inputs are ignored until the RESET input goes low. A low-pass filter is integrated into the reset circuit; therefore a 5  $\mu$ s delay is required between the falling edge of the RESET input and the rising edge of the CLOCK input.

**Monitor output (MO).** A logic output indicator of the initial/home state of the translator ( $45^\circ$ ). At power up the translator is reset to the home state (phase A and phase B output currents are both at the half-step position or 70.7%). This output is also high at the 135°, 225°, and 315° positions.

**CLOCK (step) input.** A low-to-high transition on the clock input sequences the translator, which controls the input to the DACs and advances the motor one increment. The size of the increment is determined by the state of inputs M1 and M2 (see table 1). The hold state is done by stopping the CLOCK input regardless of the input level

**Microstep select (M1 and M2).** These logic-level inputs set the translator step mode per table 1. Changes to these inputs do not take effect until the rising edge of the clock input.

**Direction (CW/CCW) input.** This logic-level input sets the translator step direction. Changes to this input do not take effect until the rising edge of the clock input.

**Internal PWM current control.** Each pair of outputs is controlled by a fixed off-time (7 to 12  $\mu$ s, depending on step) PWM current-control circuit that limits the load current to a desired value ( $I_{TRIP}$ ). Initially, an output is enabled and current flows through the motor winding and  $R_s$ . When the voltage across the current-sense resistor equals the DAC output voltage, the current-sense comparator resets the PWM latch, which turns off the driver for the fixed off time during which the load inductance causes the current to recirculate for the off time period. The driver is then re-enabled and the cycle repeats.

**Synchronous operation mode.** This function prevents occasional motor noise during a "hold" state, which normally results from asynchronous PWM operation of both motor phases. A logic high at the SYNC input is synchronous operation; a logic low is asynchronous operation. The use of synchronous operation during normal stepping is not recommended because it produces less motor torque and can cause motor vibration due to stair-case current.

**Sleep mode.** Applying a voltage greater than 2 V to the REF pin disables the outputs and puts the motor in a free state (coast). This function is used to minimize power consumption when not in use. Although it disables much of the internal circuitry including the output MOSFETs and regulator, the sequencer/translator circuit is active and therefore a microcontroller can set the step starting point for the next operation during the sleep mode. When coming out of sleep mode, wait 100 µs before issuing a step command to allow the internal circuitry to stabilize.

| Table | • <b>1</b> . | Step | Modes |  |

|-------|--------------|------|-------|--|

| IUNIC |              | OLOP | modeo |  |

| Input<br>M1 | Input<br>M2 | Step Mode      |

|-------------|-------------|----------------|

| Н           | Н           | Half Step      |

| Н           | L           | Quarter Step   |

| L           | Н           | Eighth Step    |

| L           | L           | Sixteenth Step |

|                |                   |                  | (CW/CCW = |                          | Phase B or B\            |               |

|----------------|-------------------|------------------|-----------|--------------------------|--------------------------|---------------|

| Half           | Ouerter           | Fishth           | Civtoonth | Phase A or A             |                          | Ctor.         |

| Half<br>Step # | Quarter<br>Step # | Eighth<br>Stop # | Sixteenth | Current                  | Current                  | Step<br>Angle |

| -              |                   | Step #           | Step #    | [%l <sub>trip</sub> max] | [%l <sub>trip</sub> max] | -             |

| 0              | 0                 | 0                | 0         | 70.7                     | 70.7                     | 45*           |

|                |                   |                  | 1         | 77.3                     | 63.4                     |               |

|                |                   | 1                | 2         | 83.1                     | 55.5                     |               |

|                |                   |                  | 3         | 88.2                     | 47.1                     |               |

|                | 1                 | 2                | 4         | 92.4                     | 38.2                     | 67.5          |

|                |                   | -                | 5         | 95.7                     | 29.0                     |               |

|                |                   | 3                | 6         | 98.1                     | 19.5                     |               |

| 1              | 2                 | 4                | 7<br>8    | 100                      | 9.8                      | 00            |

| I              | 2                 | 4                | 8<br>9    | 100<br>100               | 0<br>-9.8                | 90            |

|                |                   | 5                | 9<br>10   | 98.1                     | -9.8                     |               |

|                |                   | 0                | 11        | 95.7                     | -29.0                    |               |

|                | 3                 | 6                | 12        | 92.4                     | -38.2                    | 102.5         |

|                | Ŭ                 | 0                | 13        | 88.2                     | -47.1                    | 102.0         |

|                |                   | 7                | 14        | 83.1                     | -55.5                    |               |

|                |                   |                  | 15        | 77.3                     | -63.4                    |               |

| 2              | 4                 | 8                | 16        | 70.7                     | -70.7                    | 135†          |

| -              | т                 | 0                | 17        | 63.4                     | -77.3                    | 1001          |

|                |                   | 9                | 18        | 55.5                     | -83.1                    |               |

|                |                   |                  | 19        | 47.1                     | -88.2                    |               |

|                | 5                 | 10               | 20        | 38.2                     | -92.4                    | 157.5         |

|                |                   |                  | 21        | 29.0                     | -95.7                    |               |

|                |                   | 11               | 22        | 19.5                     | -98.1                    |               |

|                |                   |                  | 23        | 9.8                      | -100                     |               |

| 3              | 6                 | 12               | 24        | 0                        | -100                     | 180           |

|                |                   |                  | 25        | -9.8                     | -100                     |               |

|                |                   | 13               | 26        | -19.5                    | -98.1                    |               |

|                | _                 |                  | 27        | -29.0                    | -95.7                    |               |

|                | 7                 | 14               | 28        | -38.2                    | -92.4                    | 202.5         |

|                |                   |                  | 29        | -47.1                    | -88.2                    |               |

|                |                   | 15               | 30        | -55.5                    | -83.1                    |               |

|                |                   |                  | 31        | -63.4                    | -77.3                    |               |

| 4              | 8                 | 16               | 32        | -70.7                    | -70.7                    | 225†          |

|                |                   |                  | 33        | -77.3                    | -63.4                    |               |

|                |                   | 17               | 34        | -83.1                    | -55.5                    |               |

|                | 0                 | 40               | 35        | -88.2                    | -47.1                    | 047 5         |

|                | 9                 | 18               | 36        | -92.4                    | -38.2                    | 247.5         |

|                |                   | 19               | 37<br>38  | -95.7<br>-98.1           | -29.0<br>-19.5           |               |

|                |                   | 19               | 39        | -100                     | -9.8                     |               |

| 5              | 10                | 20               | 40        | -100                     | -9.8                     | 270           |

| 5              | 10                | 20               | 40        | -100                     | 9.8                      | 210           |

|                |                   | 21               | 41        | -98.1                    | 19.5                     |               |

|                |                   | - '              | 43        | -95.7                    | 29.0                     |               |

|                | 11                | 22               | 44        | -92.4                    | 38.2                     | 292.5         |

|                |                   |                  | 45        | -88.2                    | 47.1                     |               |

|                |                   | 23               | 46        | -83.1                    | 55.5                     |               |

|                |                   |                  | 47        | -77.3                    | 63.4                     |               |

| 6              | 12                | 24               | 48        | -70.7                    | 70.7                     | 315†          |

| -              | -                 |                  | 49        | -63.4                    | 77.3                     | 1             |

|                |                   | 25               | 50        | -55.5                    | 83.1                     |               |

|                |                   |                  | 51        | -47.1                    | 88.2                     |               |

|                | 13                | 26               | 52        | -38.2                    | 92.4                     | 337.5         |

|                |                   |                  | 53        | -29.0                    | 95.7                     |               |

|                |                   | 27               | 54        | -19.5                    | 98.1                     |               |

|                |                   |                  | 55        | -9.8                     | 100                      |               |

| 7              | 14                | 28               | 56        | 0                        | 100                      | 360           |

|                |                   |                  | 57        | 9.8                      | 100                      |               |

|                |                   | 29               | 58        | 19.5                     | 98.1                     |               |

|                |                   |                  | 59        | 29.0                     | 95.7                     |               |

|                | 15                | 30               | 60        | 38.2                     | 92.4                     | 22.5          |

|                |                   | <u>c</u> :       | 61        | 47.1                     | 88.2                     |               |

|                |                   | 31               | 62        | 55.5                     | 83.1                     |               |

|                | 16                | 32               | 63<br>64  | <u>63.4</u><br>70.7      | 77.3                     | 45*           |

| 8              |                   |                  |           |                          |                          |               |

## Table 2. Step Sequencing

\* Home state; MO output high. † MO output high.

115 Northaget Cutoff Day 15026

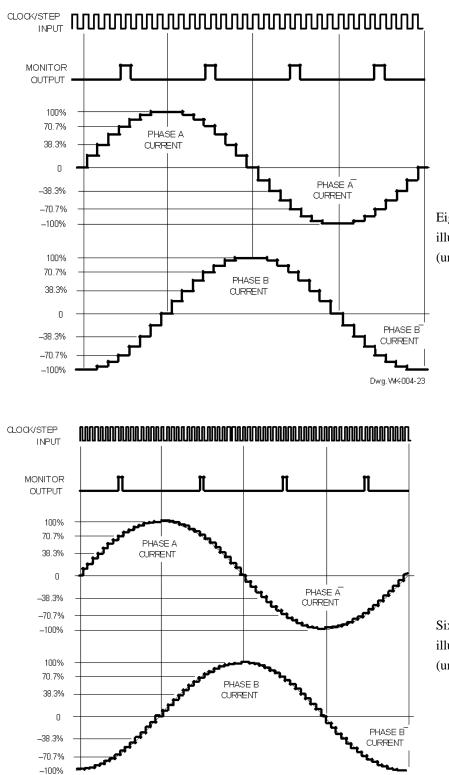

Eighth-step output current waveshapes. For illustrative purposes, phase  $A \setminus \text{or } B \setminus \text{current}$  (unipolar drive) is shown as negative current.

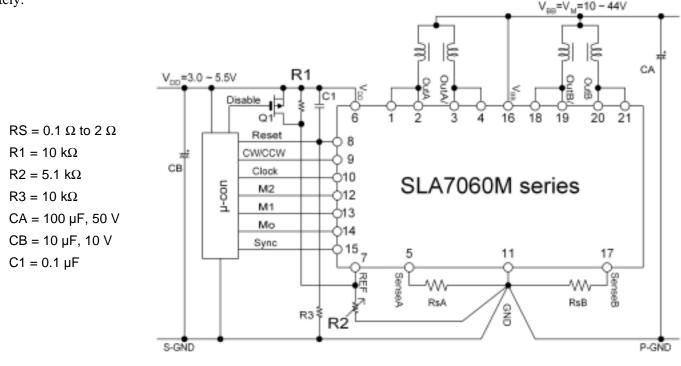

Sixteenth-step output current waveshapes. For illustrative purposes, phase A\ or B\ current (unipolar drive) is shown as negative current.

5 Northaast Cutoff Day 15026

Dwg. WK-004-24

#### **Applications information**

#### Layout.

The printed wirting board should use a heavy ground plane.

For optimum electrical and thermal performance, the driver should be soldered directly into the board.

The driver supply terminal, VBB, should be decoupled with an electrolytic capacitor (>47  $\mu$ F is recommended) placed as close to the device as possible.

To avoid problems due to capacitive coupling of the high dv/dt switching transients, route the high-level, output traces away from the sensitive, low-level logic traces. Always drive the logic inputs with a low source impedance to increase noise immunity.

Grounding. A star ground system located close to the driver is recommended. The logic supply return and the driver supply return should be connected together at only a single point — the star ground.

Logic supply voltage,  $V_{DD}$ . Transients at this terminal should be held to less than 0.5 V to avoid malfunctioning operation. Both  $V_{BB}$  and  $V_{DD}$  may be turned on or off separately.

Logic inputs. Unused logic inputs (CW/CCW, M1, M2, RESET, or SYNC) must be connected to either ground or the logic supply voltage.

**Current sensing.** To minimize inaccuracies caused by ground-trace IR drops in sensing the output current level, the current-sense resistors, R<sub>s</sub>, should have an independent ground return to the star ground of the device. This path should be as short as possible. For low-value sense resistors, the IR drops in the printed wiring board sense resistor's traces can be significant and should be taken into account. The use of sockets should be avoided as they can introduce variation in R<sub>s</sub> due to their contact resistance.

**PWM current control.** The maximum value of current limiting  $(I_{TRIP})$  is set by the selection of  $R_s$  and the voltage at the REF input with a transconductance function approximated by:

$$I_{\text{TRIP}} = V_{\text{REF}}/R_{\text{S}}$$

The required  $V_{REF}$  should not be less than 0.1 V. If it is, R<sub>s</sub> should be increased for a proportionate increase in V<sub>REF</sub>.

44V

#### Applications Information (cont'd)

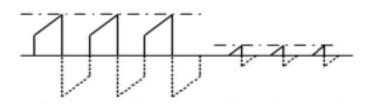

**Reference voltage.** In the Typical Application shown, resistors  $R_1$  and  $R_2$  set the reference voltage as:

$$V_{\text{REF}} = (V_{\text{DD}} \times R_2)/(R_1 + R_2)$$

The trimming of  $R_2$  allows for the resistor tolerances and REF input current. The sum of  $R_1+R_2$  should be less than 50 k $\Omega$  to minimize the effect of  $I_{REF}$ .

**Minimum output current.** The Series SLA7060M uses fixed off-time PWM current control. Due to internal logic and switching delays, the actual load current peak will be slightly higher than the calculated  $I_{TRIP}$  value (especially for low-inductance loads). These delays, plus the minimum recommended  $V_{REF}$ , limit the minimum value the current-control circuitry can regulate. An application with this device should maintain continuous PWM control in order to obtain optimum torque out of the motor. The boundary of the load current ( $I_{O(min)}$ ) between continuous and discontinuous operation is:

$$I_{O(min)} = [(V_M + V_{SD})/R_m] \times [(1/e^{toff/[R_m \times L_m]}) - 1]$$

where  $V_M = load$  supply voltage

$V_{\rm F}^{\rm M}$  = body diode forward voltage

$R_m = motor winding resistance$

$t_{off} = PWM$  off time

$L_{m}^{n}$  = motor winding inductance

To produce zero current in a motor, the REF input should be pulled above 2 V, turning off all drivers.

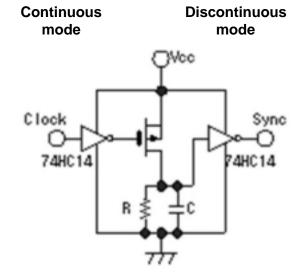

**Synchronous operation mode.** If an external signal is not available to control the synchronous operation mode, a simple circuit can keep the SYNC input low while the CLOCK input is active; the SYNC input will go high (synchronous operation) when the CLOCK input stays low ("hold"). The RC time constant determines the sync trransition timing.

NOTE –The use of this function except at 0, 70.7, or  $100\%I_{trip}$  max (half-step positions 0 through 8) is not recommended.

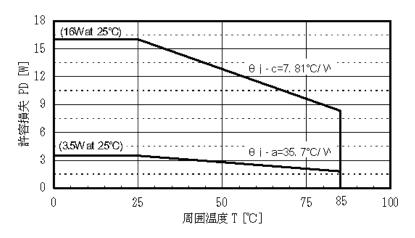

**Temperature effects on FET outputs.** Analyzing safe, reliable operation includes a concern for the relationship of NMOS on resistance to junction temperature. Device package power calculations must include the increase in on resistance (producing higher on voltages)

#### Normalized FET on resistance

N 4 4 C 4 C D 15026

#### Applications Information (cont'd)

caused by increased operating junction temperatures. The figure provides a normalized on-resistance curve, and all thermal calculations should consider increases from the given  $+25^{\circ}$ C limits, which may be caused by internal heating during normal operation.

These power MOSFET outputs feature an excellent combination of fast switching, ruggedized device design, low on resistance, and cost effectiveness.

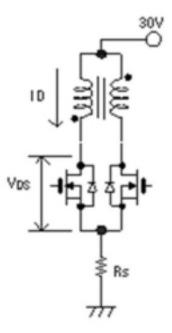

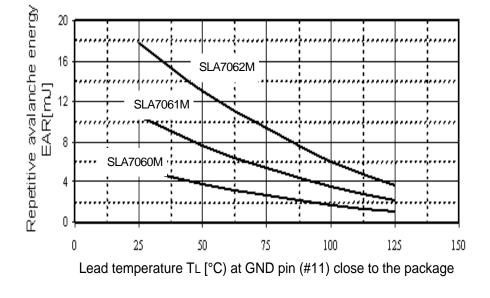

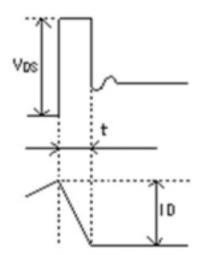

**Avalanche energy capability.** There is a surge voltage expected when the output MOSFET turns off, and this voltage may exceed the MOSFET breakdown voltage  $(V_{(BR)DS})$ . However, the MOSFETs are avalanche type and as long as the energy  $(E_{(AV)})$ , which is imposed on the MOSFET by the surge voltage, is less than the maximum allowable value, it is considered to be within its safe operating area. Note that the maximum allowable avalanche energy is reduced as a function of temperature.

In application, the avalanche energy  $(E_{(AV)})$  dissipated by the MOSFET is approximated as

$$\mathbf{E}_{(\mathrm{AV})} = \mathbf{V}_{\mathrm{DS}(\mathrm{AV})} \ge 0.5 \ge \mathbf{I}_{\mathrm{D}} \ge 0.5$$

Output circuit for avalanche energy calculations

Allowable avalanche energy

Waveforms during avalanche breakdown

#### **Terminal list**

| Pin    | Terminal<br>Name | Terminal Description                            |

|--------|------------------|-------------------------------------------------|

| 1, 2   | OUTA             | Driver outputs for phase A                      |

| 3, 4   | OUTA\            | Driver outputs for phase A\                     |

| 5      | SENSEA           | Phase A current sense                           |

| 6      | VDD              | Logic power supply, $V_{DD}$                    |

| 7      | REF              | Current set & "sleep" control                   |

| 8      | RESET            | Logic control input                             |

| 9      | CW/CCW           | Forward/reverse logic control input             |

| 10     | CLOCK            | Step clock input                                |

| 11     | GND              | Supply negative return                          |

| 12     | M2               | Step mode logic control input                   |

| 13     | M1               | Step mode logic control input                   |

| 14     | МО               | Monitor logic output                            |

| 15     | SYNC             | Synchronous PWM control input                   |

| 16     | VBB              | Driver power supply, $\mathrm{V}_{\mathrm{BB}}$ |

| 17     | SENSEB           | Phase B current sense                           |

| 18, 19 | OUTB\            | Driver outputs for phase B\                     |

| 20, 21 | OUTB             | Driver outputs for phase B                      |

|        |                  |                                                 |

The products described herein are manufactured in Japan by Sanken Electric Co., Ltd. for sale by Allegro MicroSystems, Inc.

Sanken and Allegro reserve the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Therefore, the user is cautioned to verify that the information in this publication is current before placing any order.

When using the products described herein, the applicability and suitability of such products for the intended purpose shall be reviewed at the users responsibility.

Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure and defect of semiconductor products at a certain rate is inevitable.

Users of Sanken products are requested to take, at their own risk, preventative measures including safety design of the equipment or systems against any possible injury, death, fires or damages to society due to device failure or malfunction.

Sanken products listed in this publication are designed and intended for use as components in general-purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.). Their use in any application requiring radiation hardness assurance (e.g., aerospace equipment) is not supported.

When considering the use of Sanken products in applications where higher reliability is required (transportation equipment and its control systems or equipment, fire- or burglar-alarm systems, various safety devices, etc.), contact a Sanken sales representative to discuss and obtain written confirmation of your specifications.

The use of Sanken products without the written consent of Sanken in applications where extremely high reliability is required (aerospace equipment, nuclear power-control stations, life-support systems, etc.) is strictly prohibited.

The information included herein is believed to be accurate and reliable. Application and operation examples described in this publication are given for reference only and Sanken and Allegro assume no responsibility for any infringement of industrial property rights, intellectual property rights, or any other rights of Sanken or Allegro or any third party that may result from its use.

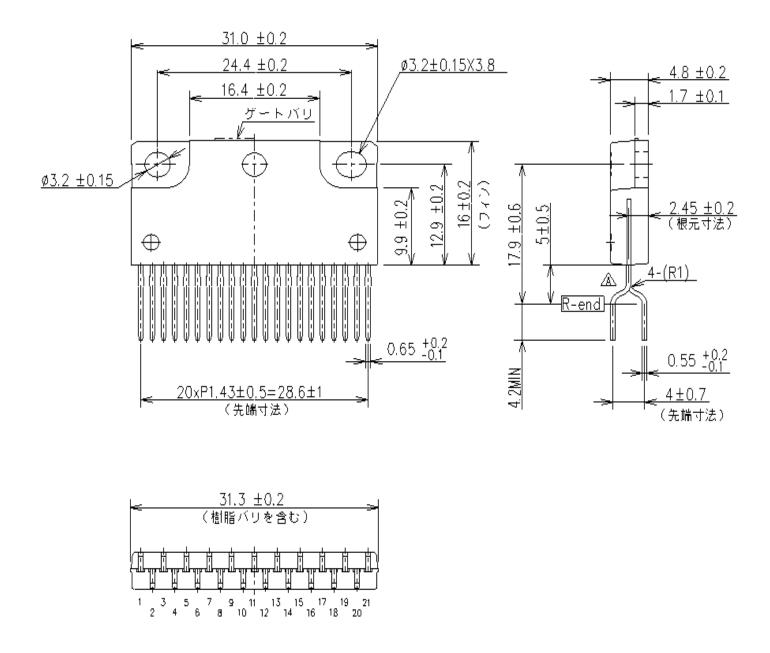

SLA706xMLF2102 Dimensions in millimeters

NOTES: 1. Exact body and lead configuration at vendor's option within limits shown.

- 2. Lead spacing tolerance is non-cumulative.

- 3. Recommended mounting hardware torque: 0.490 0.822 Nm.

- 4. Recommended use of metal-oxide-filled, alkyl-degenerated oil-base silicone grease: Dow Corning SC102, Toshiba YG6260, Shin-Etsu G746, or equivalent.

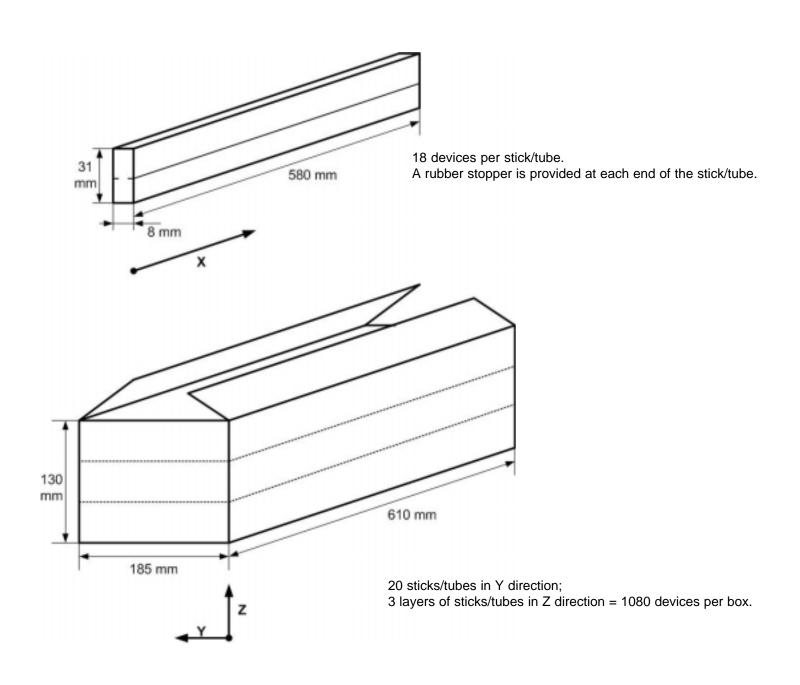

#### **Packing information**