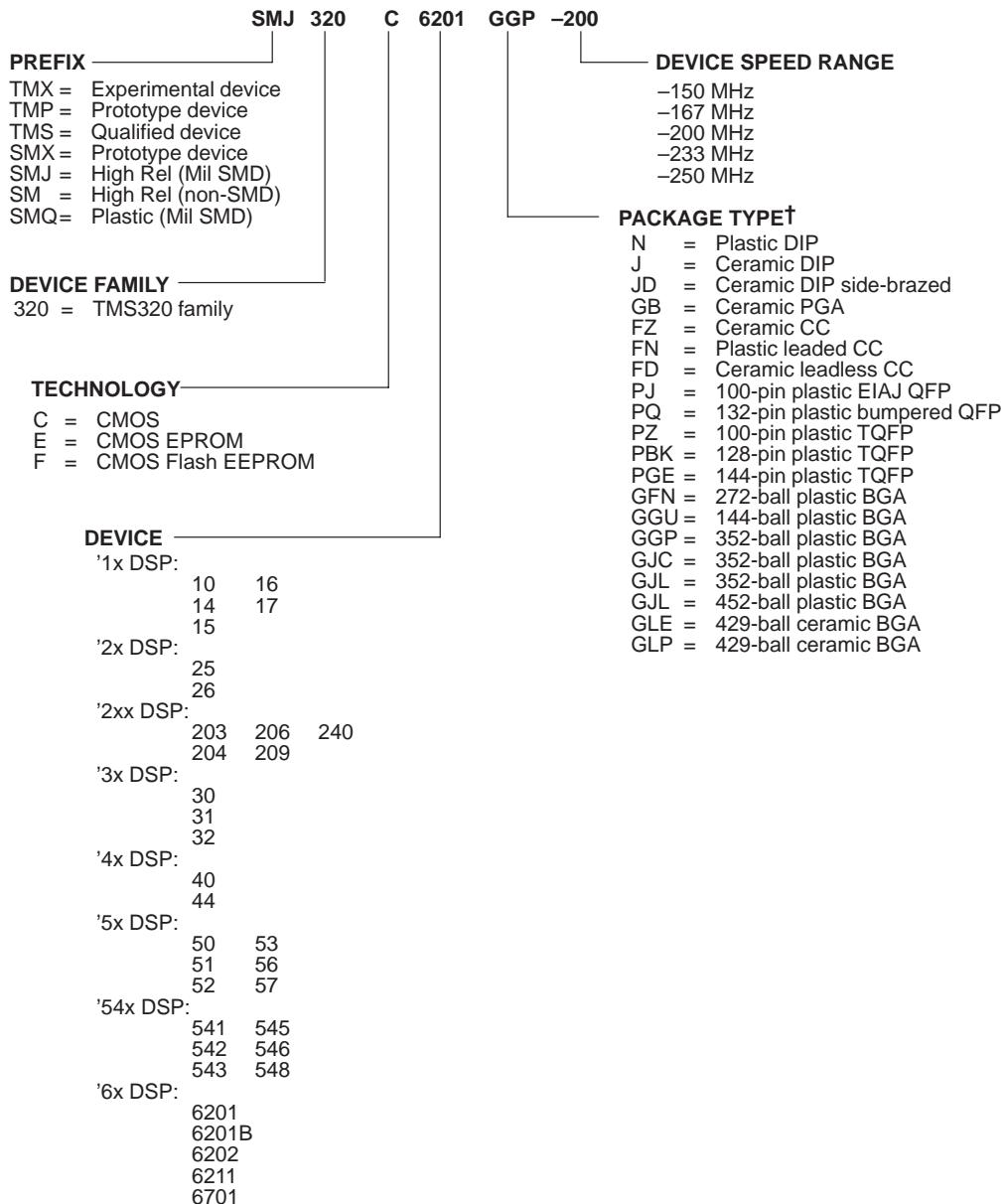

- Highest Performance Fixed-Point Digital Signal Processor (DSP) SM320C6201

- 6.67-ns Instruction Cycle Time

- 150-MHz Clock Rate

- Eight 32-Bit Instructions/Cycle

- 1200 MIPS

- Highest Performance Fixed-Point Digital Signal Processor (DSP) SM320C6201B

- 6.67-ns Instruction Cycle Time

- 150-MHz Clock Rate

- Eight 32-Bit Instructions/Cycle

- 1200 MIPS

- VelociTI™ Advanced Very Long Instruction Word (VLIW) 'C6200 CPU Core

- Eight Independent Functional Units:

- Six ALUs (32-/40-Bit)

- Two 16-Bit Multipliers (32-Bit Results)

- Load-Store Architecture With 32 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Instruction Set Features

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 32-Bit Address Range

- 8-Bit Overflow Protection

- Saturation

- Bit-Field Extract, Set, Clear

- Bit-Counting

- Normalization

- 1M-Bit On-Chip SRAM

- 512K-Bit Internal Program/Cache (16K 32-Bit Instructions)

- 512K-Bit Dual-Access Internal Data (64K Bytes) Organized as a Single Block ('6201)

- 512K-Bit Dual-Access Internal Data (64K Bytes) Organized as Two Blocks for Improved Concurrency ('6201B)

- 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

- Glueless Interface to Asynchronous Memories: SRAM and EPROM

- Four-Channel Bootloading Direct-Memory-Access (DMA) Controller with an Auxiliary Channel

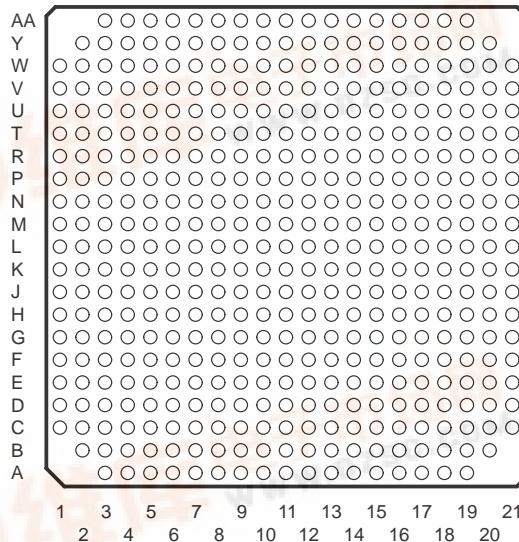

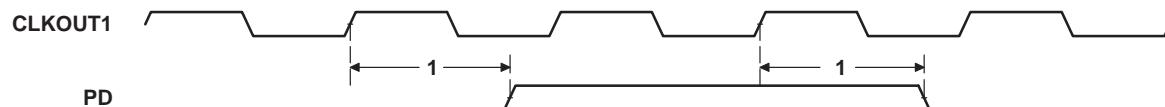

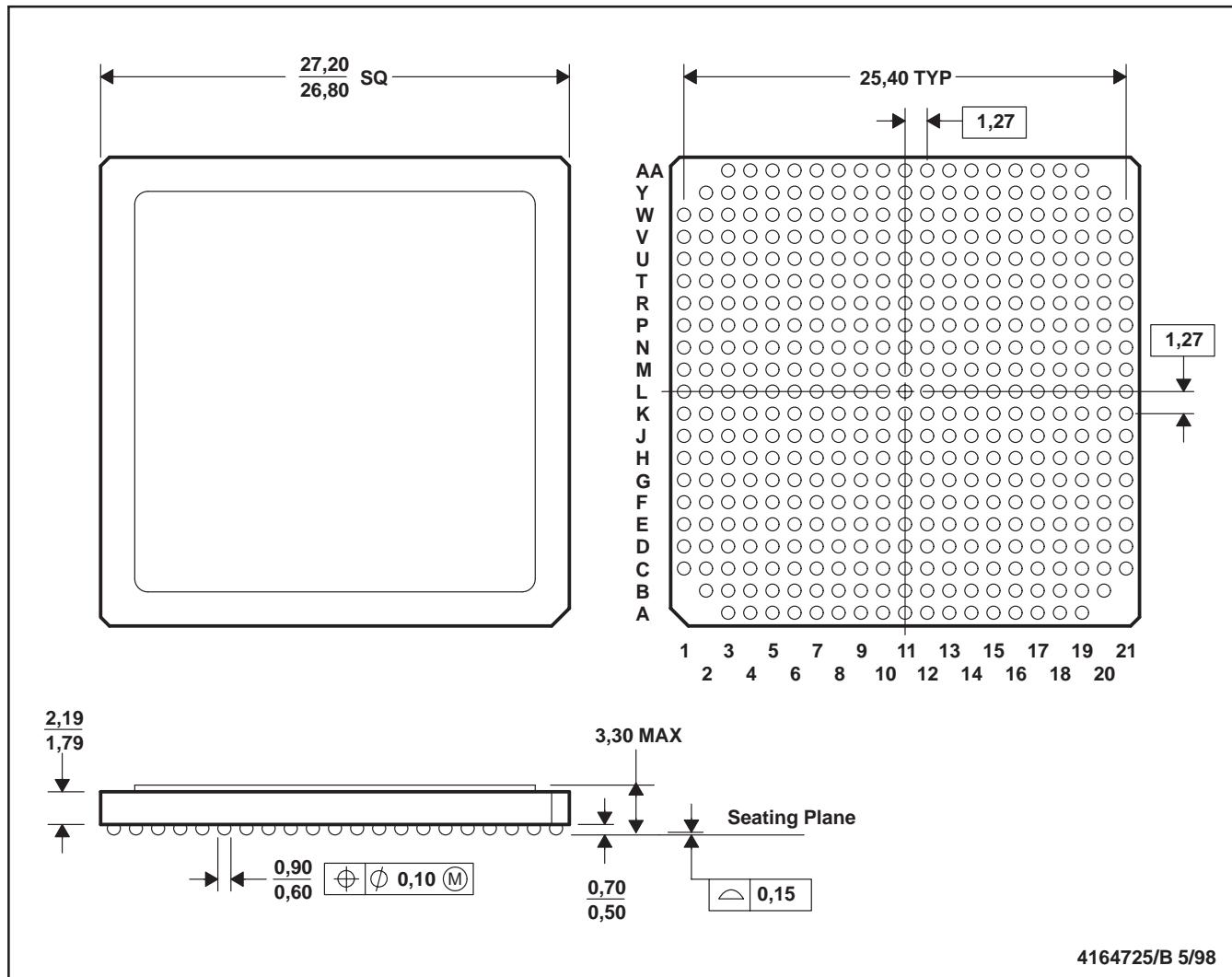

GLE and GLP PACKAGES

(BOTTOM VIEW)

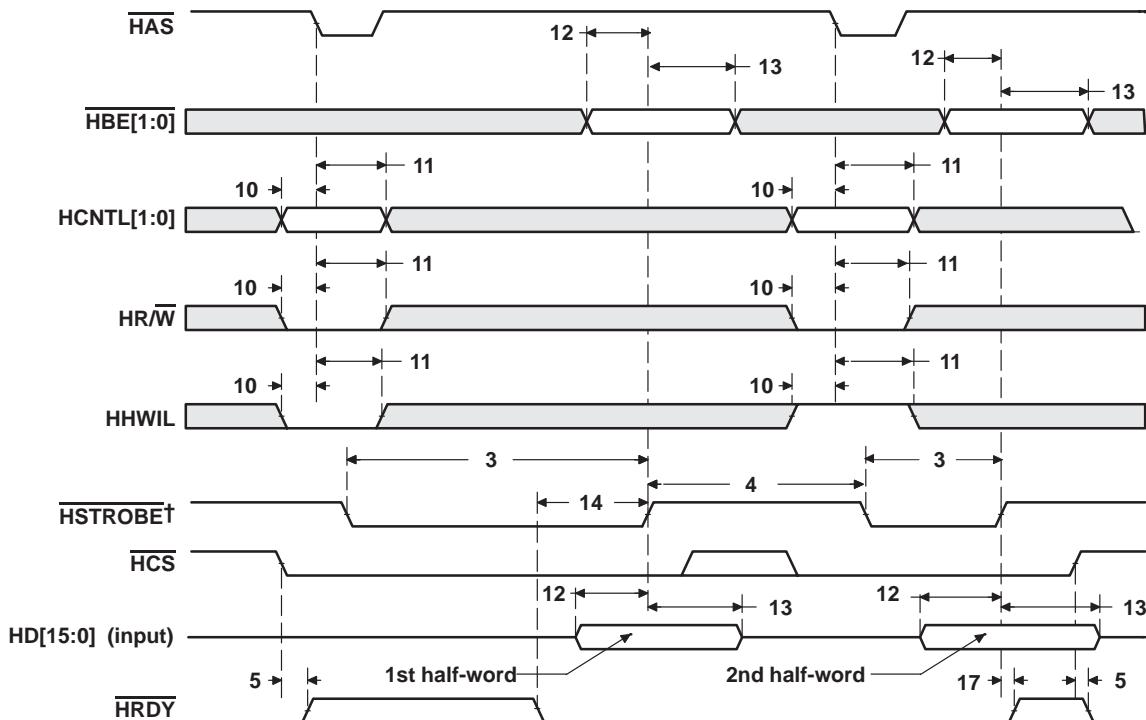

- 16-Bit Host-Port Interface (HPI)

- Access to Entire Memory Map

- Two Multichannel Buffered Serial Ports (McBSPs)

- Direct Interface to T1/E1, MVIP, SCSA Framers

- ST-Bus-Switching Compatible

- Up to 256 Channels Each

- AC97-Compatible

- Serial Peripheral Interface (SPI) Compatible (Motorola™)

- Two 32-Bit General-Purpose Timers

- Flexible Phase-Locked Loop (PLL) Clock Generator

- IEEE-1149.1 (JTAG†) Boundary-Scan Compatible

- 429-Pin BGA Package (GLE Suffix) ('6201)

- 429-Pin BGA Package (GLP Suffix) ('6201B)

- CMOS Technology

- 0.25- $\mu$ m/5-Level Metal Process ('6201)

- 0.18- $\mu$ m/5-Level Metal Process ('6201B)

- 3.3-V I/Os, 2.5-V Internal ('6201)

- 3.3-V I/Os, 1.8-V Internal ('6201B)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

VelociTI is a trademark of Texas Instruments Incorporated.

Motorola is a trademark of Motorola, Inc.

JTAG is a trademark of IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions

| SIGNAL<br>NAME        | NO. | TYPE <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                              |

|-----------------------|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CLOCK/PLL</b>      |     |                   |                                                                                                                                                                                                                                          |

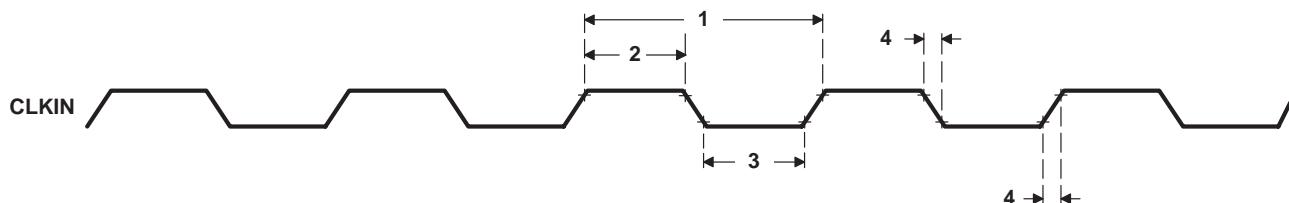

| CLKIN                 | A14 | I                 | Clock Input                                                                                                                                                                                                                              |

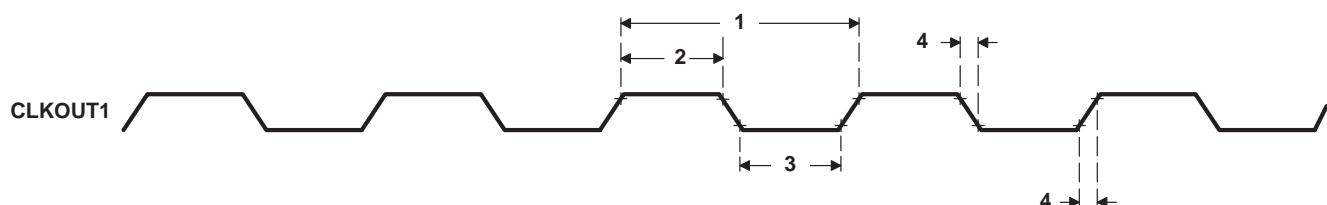

| CLKOUT1               | Y6  | O                 | Clock output at full device speed                                                                                                                                                                                                        |

| CLKOUT2               | V9  | O                 | Clock output at half of device speed                                                                                                                                                                                                     |

| CLKMODE1              | B17 | I                 | Clock mode select <ul style="list-style-type: none"> <li>• Selects whether the output clock frequency = input clock freq x4 or x1</li> </ul>                                                                                             |

| CLKMODE0              | C17 | I                 |                                                                                                                                                                                                                                          |

| PLLREQ3               | C13 | I                 | PLL frequency range (3, 2, and 1) <ul style="list-style-type: none"> <li>• Selects one of three frequency ranges bounding the CLKOUT1 signal.</li> <li>• CLKOUT1 frequency determines the 3-bit value for the PLLREQ pins.</li> </ul>    |

| PLLREQ2               | G11 | I                 |                                                                                                                                                                                                                                          |

| PLLREQ1               | F11 | I                 |                                                                                                                                                                                                                                          |

| PLLV <sup>‡</sup>     | D12 | A <sup>§</sup>    | PLL analog V <sub>CC</sub> connection for the low-pass filter                                                                                                                                                                            |

| PLLG <sup>‡</sup>     | G10 | A <sup>§</sup>    | PLL analog GND connection for the low-pass filter                                                                                                                                                                                        |

| PLLF                  | C12 | A <sup>§</sup>    | PLL low-pass filter connection to external components and a bypass capacitor                                                                                                                                                             |

| <b>JTAG EMULATION</b> |     |                   |                                                                                                                                                                                                                                          |

| TMS                   | K19 | I                 | JTAG test port mode select (features an internal pull-up)                                                                                                                                                                                |

| TDO                   | R12 | O/Z               | JTAG test port data out                                                                                                                                                                                                                  |

| TDI                   | R13 | I                 | JTAG test port data in (features an internal pull-up)                                                                                                                                                                                    |

| TCK                   | M20 | I                 | JTAG test port clock                                                                                                                                                                                                                     |

| TRST                  | N18 | I                 | JTAG test port reset (features an internal pull-down)                                                                                                                                                                                    |

| EMU1                  | R20 | I/O/Z             | Emulation pin 1, pull-up with a dedicated 20-k $\Omega$ resistor                                                                                                                                                                         |

| EMU0                  | T18 | I/O/Z             | Emulation pin 0, pull-up with a dedicated 20-k $\Omega$ resistor                                                                                                                                                                         |

| <b>CONTROL</b>        |     |                   |                                                                                                                                                                                                                                          |

| RESET                 | J20 | I                 | Device reset                                                                                                                                                                                                                             |

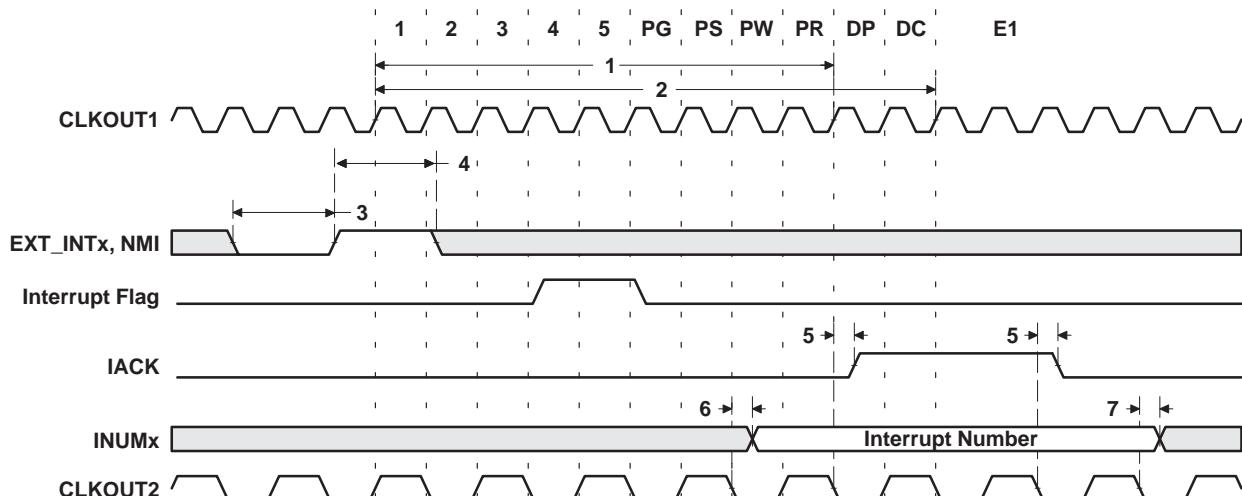

| NMI                   | K21 | I                 | Nonmaskable interrupt <ul style="list-style-type: none"> <li>• Edge-driven (rising edge)</li> </ul>                                                                                                                                      |

| EXT_INT7              | R16 | I                 |                                                                                                                                                                                                                                          |

| EXT_INT6              | P20 | I                 | External interrupts <ul style="list-style-type: none"> <li>• Edge-driven (rising edge)</li> </ul>                                                                                                                                        |

| EXT_INT5              | R15 | I                 |                                                                                                                                                                                                                                          |

| EXT_INT4              | R18 | I                 |                                                                                                                                                                                                                                          |

| IACK                  | R11 | O                 | Interrupt acknowledge for all active interrupts serviced by the CPU                                                                                                                                                                      |

| INUM3                 | T19 | O                 | Active interrupt identification number <ul style="list-style-type: none"> <li>• Valid during IACK for all active interrupts (not just external)</li> <li>• Encoding order follows the interrupt service fetch packet ordering</li> </ul> |

| INUM2                 | T20 | O                 |                                                                                                                                                                                                                                          |

| INUM1                 | T14 | O                 |                                                                                                                                                                                                                                          |

| INUM0                 | T16 | O                 |                                                                                                                                                                                                                                          |

| LENDIAN               | G20 | I                 | If high, selects little-endian byte/half-word addressing order within a word<br>If low, selects big-endian addressing                                                                                                                    |

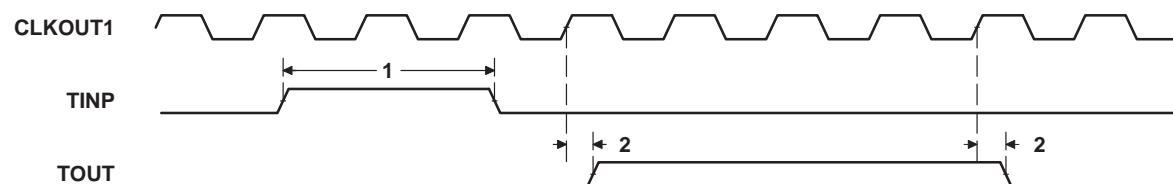

| PD                    | D19 | O                 | Power-down mode 3 (active if high)                                                                                                                                                                                                       |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

<sup>‡</sup>PLLV and PLLG signals are not part of external voltage supply or ground. See the CLOCK/PLL documentation for information on how to connect those pins.

<sup>§</sup>A = Analog Signal (PLL Filter)

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME                   | NO. | TYPE <sup>†</sup> | DESCRIPTION                                                                         |

|----------------------------------|-----|-------------------|-------------------------------------------------------------------------------------|

| <b>HOST PORT INTERFACE (HPI)</b> |     |                   |                                                                                     |

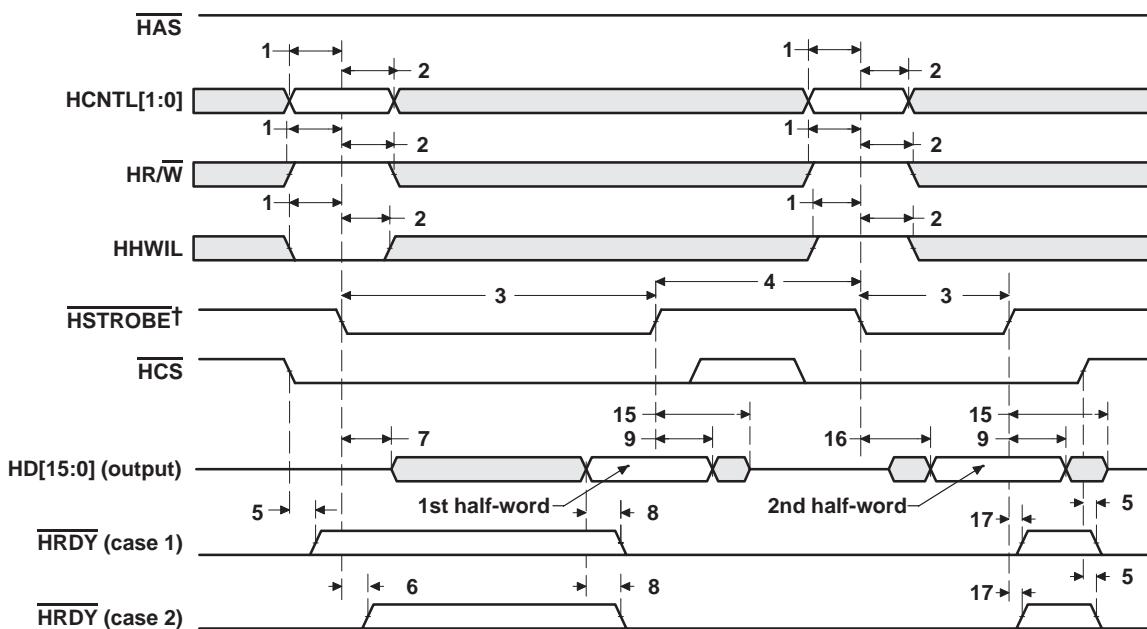

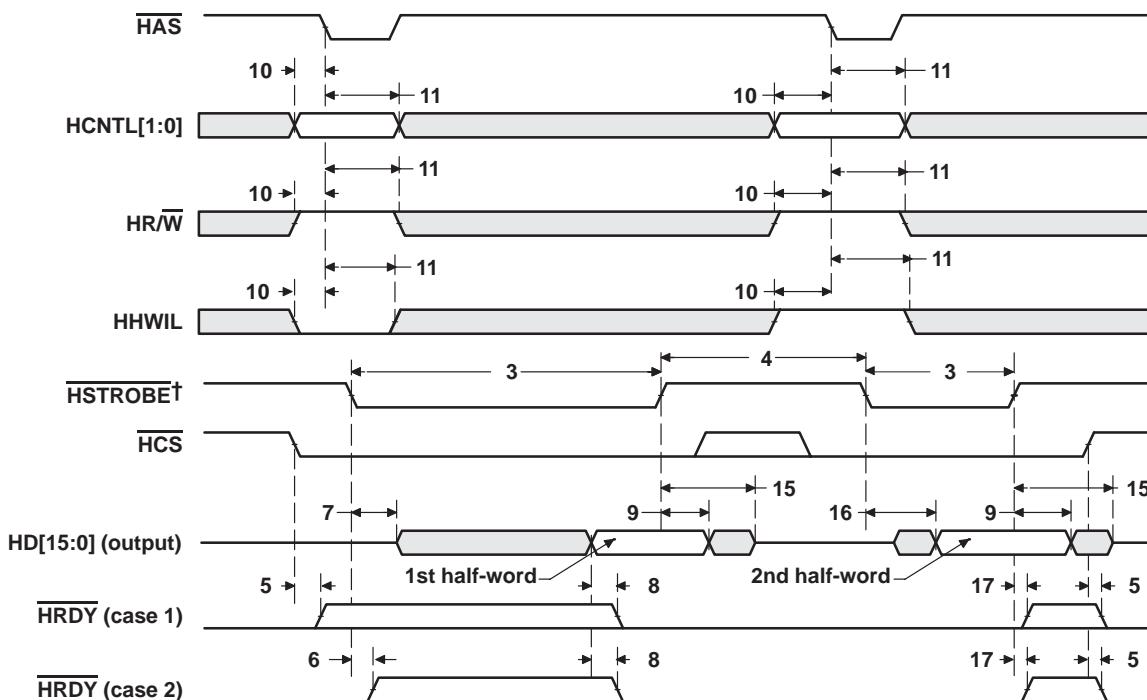

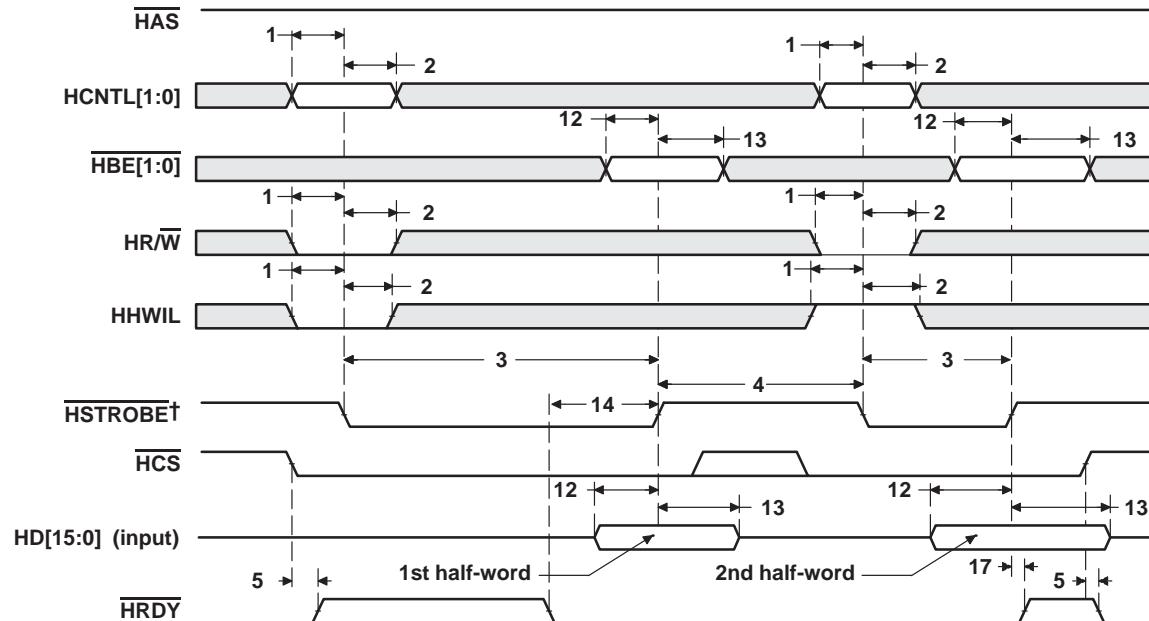

| HINT                             | H2  | O/Z               | Host interrupt (from DSP to host)                                                   |

| HCNTL1                           | J6  | I                 | Host control – selects between control, address or data registers                   |

| HCNTL0                           | H6  | I                 | Host control – selects between control, address or data registers                   |

| HHWIL                            | E4  | I                 | Host halfword select – first or second halfword (not necessarily high or low order) |

| HBE1                             | G6  | I                 | Host byte select within word or half-word                                           |

| HBE0                             | F6  | I                 | Host byte select within word or half-word                                           |

| HR/W                             | D4  | I                 | Host read or write select                                                           |

| HD15                             | D11 | I/O/Z             | Host port data (used for transfer of data, address and control)                     |

| HD14                             | B11 |                   |                                                                                     |

| HD13                             | A11 |                   |                                                                                     |

| HD12                             | G9  |                   |                                                                                     |

| HD11                             | D10 |                   |                                                                                     |

| HD10                             | A10 |                   |                                                                                     |

| HD9                              | C10 |                   |                                                                                     |

| HD8                              | B9  |                   |                                                                                     |

| HD7                              | F9  |                   |                                                                                     |

| HD6                              | C9  |                   |                                                                                     |

| HD5                              | A9  |                   |                                                                                     |

| HD4                              | B8  |                   |                                                                                     |

| HD3                              | D9  |                   |                                                                                     |

| HD2                              | D8  |                   |                                                                                     |

| HD1                              | B7  |                   |                                                                                     |

| HD0                              | C7  |                   |                                                                                     |

| HAS                              | L6  | I                 | Host address strobe                                                                 |

| HCS                              | C5  | I                 | Host chip select                                                                    |

| HDS1                             | C4  | I                 | Host data strobe 1                                                                  |

| HDS2                             | K6  | I                 | Host data strobe 2                                                                  |

| HRDY                             | H3  | O                 | Host ready (from DSP to host)                                                       |

| <b>BOOT MODE</b>                 |     |                   |                                                                                     |

| BOOTMODE4                        | B16 | I                 | Boot mode                                                                           |

| BOOTMODE3                        | G14 |                   |                                                                                     |

| BOOTMODE2                        | F15 |                   |                                                                                     |

| BOOTMODE1                        | C18 |                   |                                                                                     |

| BOOTMODE0                        | D17 |                   |                                                                                     |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME                                              | NO. | TYPE† | DESCRIPTION                     |

|-------------------------------------------------------------|-----|-------|---------------------------------|

| <b>EMIF – CONTROL SIGNALS COMMON TO ALL TYPES OF MEMORY</b> |     |       |                                 |

| CE3                                                         | Y5  | O/Z   |                                 |

| CE2                                                         | V3  | O/Z   |                                 |

| CE1                                                         | T6  | O/Z   |                                 |

| CE0                                                         | U2  | O/Z   |                                 |

| BE3                                                         | R8  | O/Z   |                                 |

| BE2                                                         | T3  | O/Z   |                                 |

| BE1                                                         | T2  | O/Z   |                                 |

| BE0                                                         | R2  | O/Z   |                                 |

| <b>EMIF – ADDRESS</b>                                       |     |       |                                 |

| EA21                                                        | L4  | O/Z   | External address (word address) |

| EA20                                                        | L3  |       |                                 |

| EA19                                                        | J2  |       |                                 |

| EA18                                                        | J1  |       |                                 |

| EA17                                                        | K1  |       |                                 |

| EA16                                                        | K2  |       |                                 |

| EA15                                                        | L2  |       |                                 |

| EA14                                                        | L1  |       |                                 |

| EA13                                                        | M1  |       |                                 |

| EA12                                                        | M2  |       |                                 |

| EA11                                                        | M6  |       |                                 |

| EA10                                                        | N4  |       |                                 |

| EA9                                                         | N1  |       |                                 |

| EA8                                                         | N2  |       |                                 |

| EA7                                                         | N6  |       |                                 |

| EA6                                                         | P4  |       |                                 |

| EA5                                                         | P3  |       |                                 |

| EA4                                                         | P2  |       |                                 |

| EA3                                                         | P1  |       |                                 |

| EA2                                                         | P6  |       |                                 |

† I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

**SM320C6201, SMJ320C6201B

DIGITAL SIGNAL PROCESSORS**

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

**Signal Descriptions (Continued)**

| SIGNAL<br>NAME                            | NO.  | TYPE <sup>†</sup> | DESCRIPTION                       |

|-------------------------------------------|------|-------------------|-----------------------------------|

| <b>EMIF – DATA</b>                        |      |                   |                                   |

| ED31                                      | U18  | I/O/Z             | External data                     |

| ED30                                      | U20  |                   |                                   |

| ED29                                      | T15  |                   |                                   |

| ED28                                      | V18  |                   |                                   |

| ED27                                      | V17  |                   |                                   |

| ED26                                      | V16  |                   |                                   |

| ED25                                      | T12  |                   |                                   |

| ED24                                      | W17  |                   |                                   |

| ED23                                      | T13  |                   |                                   |

| ED22                                      | Y17  |                   |                                   |

| ED21                                      | T11  |                   |                                   |

| ED20                                      | Y16  |                   |                                   |

| ED19                                      | W15  |                   |                                   |

| ED18                                      | V14  |                   |                                   |

| ED17                                      | Y15  |                   |                                   |

| ED16                                      | R9   |                   |                                   |

| ED15                                      | Y14  |                   |                                   |

| ED14                                      | V13  |                   |                                   |

| ED13                                      | AA13 |                   |                                   |

| ED12                                      | T10  |                   |                                   |

| ED11                                      | Y13  |                   |                                   |

| ED10                                      | W12  |                   |                                   |

| ED9                                       | Y12  |                   |                                   |

| ED8                                       | Y11  |                   |                                   |

| ED7                                       | V10  |                   |                                   |

| ED6                                       | AA10 |                   |                                   |

| ED5                                       | Y10  |                   |                                   |

| ED4                                       | W10  |                   |                                   |

| ED3                                       | Y9   |                   |                                   |

| ED2                                       | AA9  |                   |                                   |

| ED1                                       | Y8   |                   |                                   |

| ED0                                       | W9   |                   |                                   |

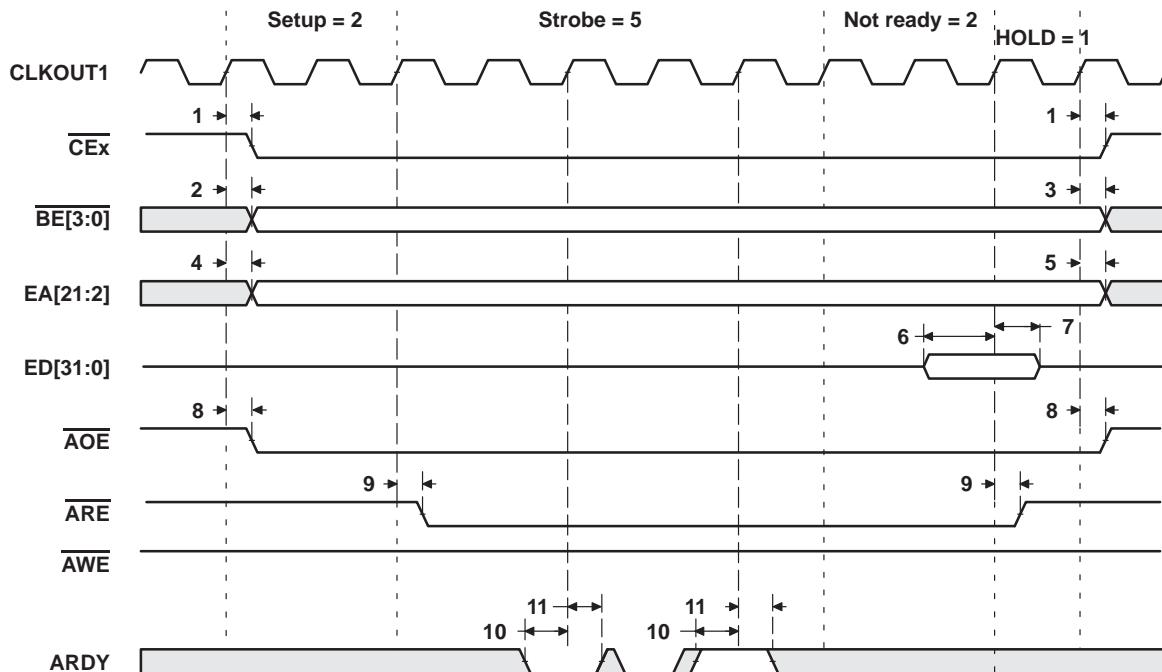

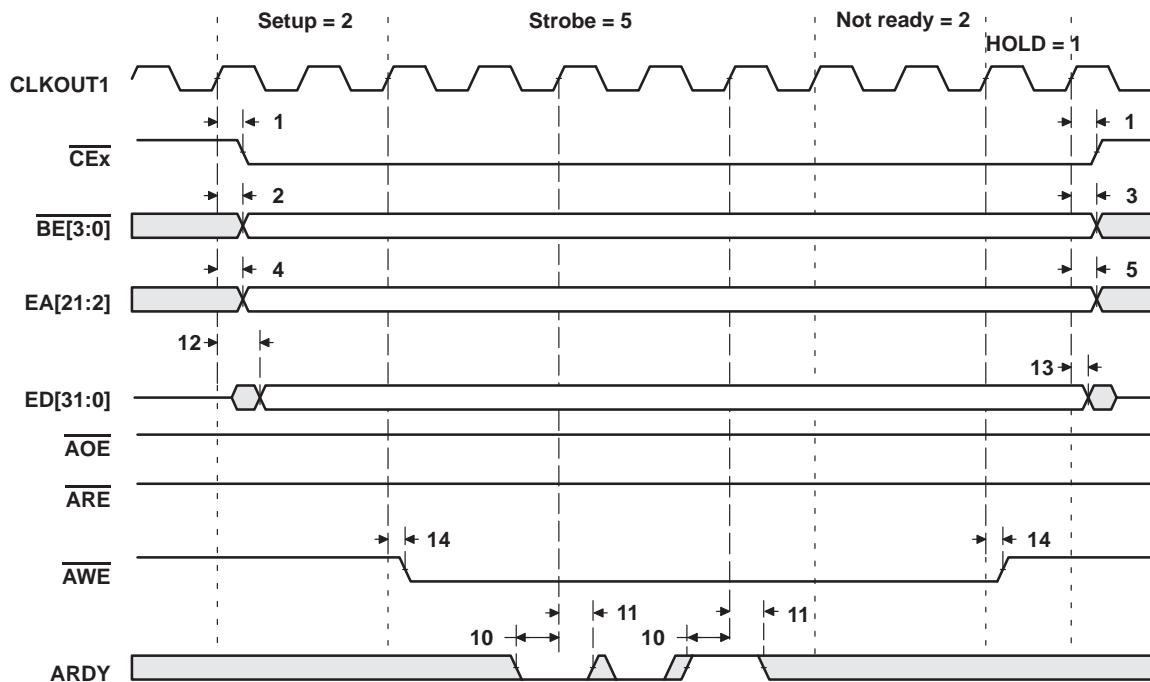

| <b>EMIF – ASYNCHRONOUS MEMORY CONTROL</b> |      |                   |                                   |

| ARE                                       | R7   | O/Z               | Asynchronous memory read enable   |

| AOE                                       | T7   | O/Z               | Asynchronous memory output enable |

| AWE                                       | V5   | O/Z               | Asynchronous memory write enable  |

| ARDY                                      | R4   | I                 | Asynchronous memory ready input   |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME                                      | NO. | TYPE <sup>†</sup> | DESCRIPTION                                        |

|-----------------------------------------------------|-----|-------------------|----------------------------------------------------|

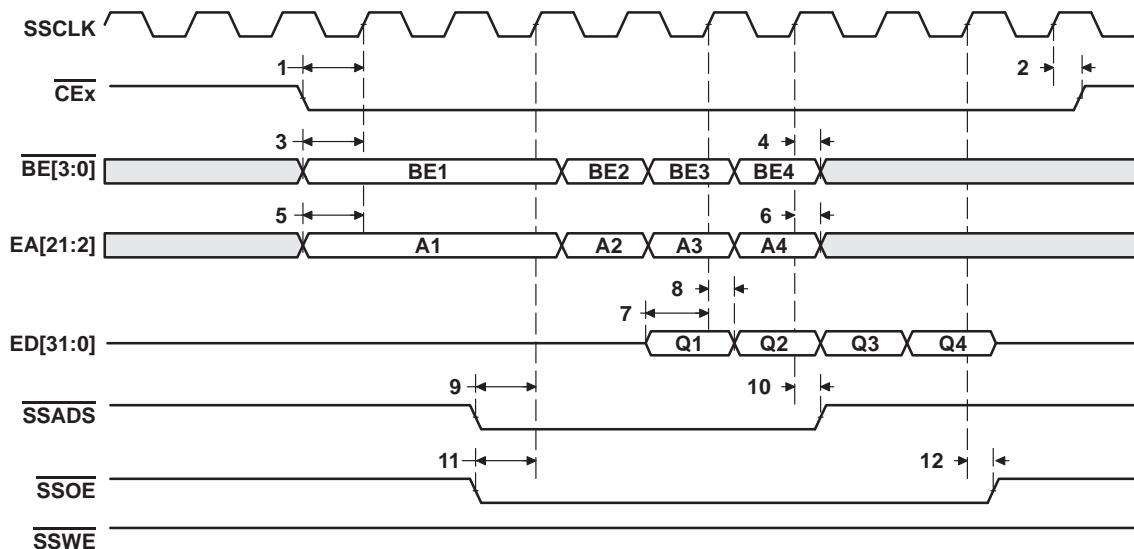

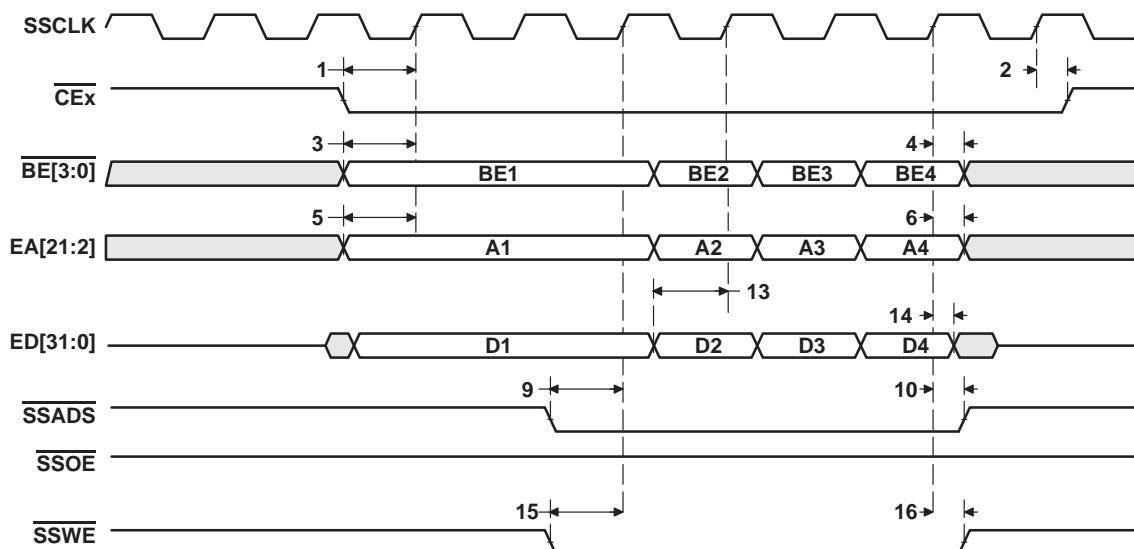

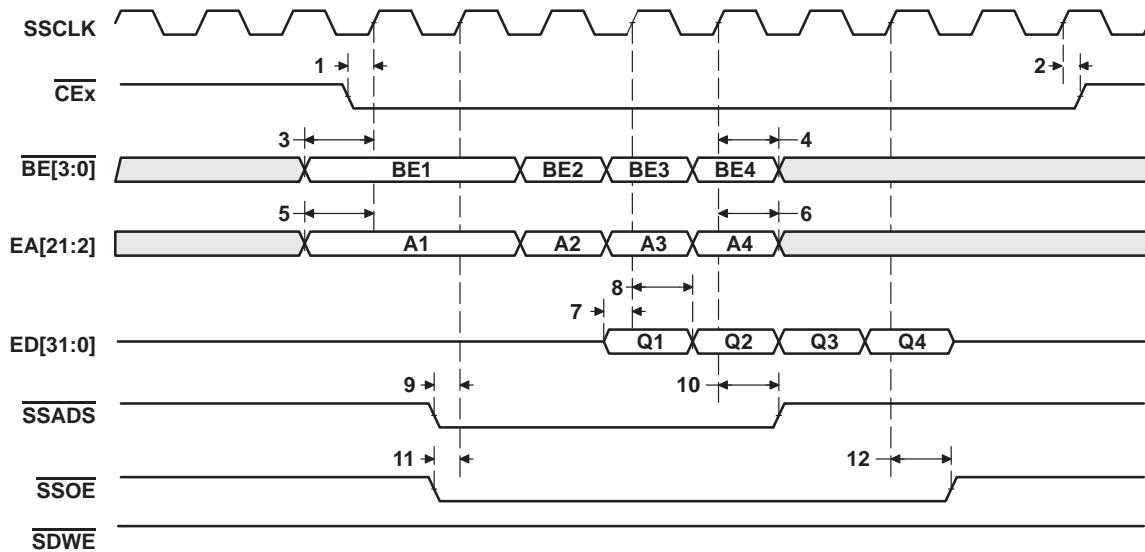

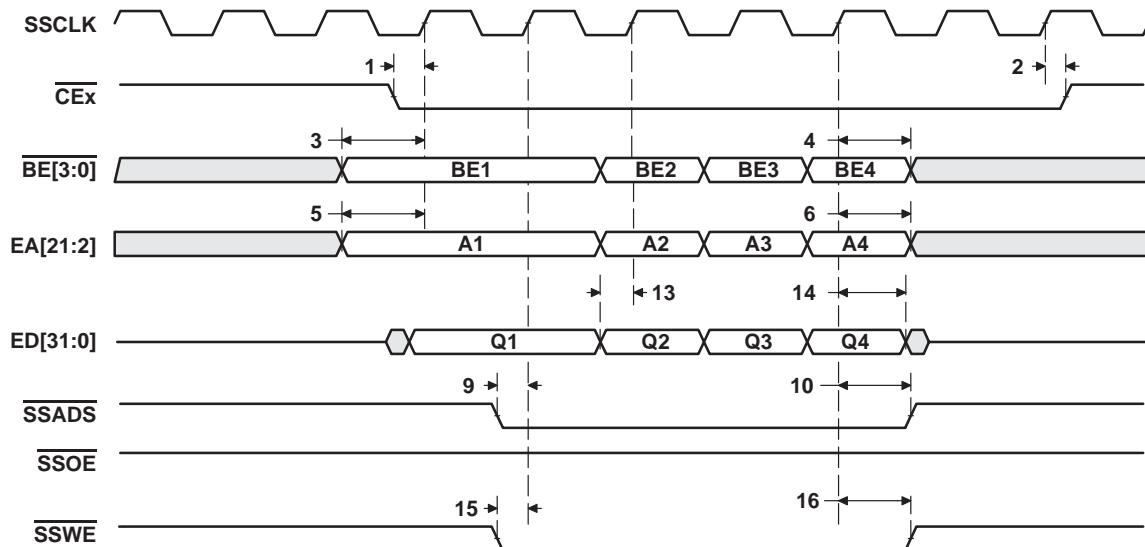

| <b>EMIF – SYNCHRONOUS BURST SRAM CONTROL</b>        |     |                   |                                                    |

| SSADS                                               | V8  | O/Z               | SBSRAM address strobe                              |

| SSOE                                                | W7  | O/Z               | SBSRAM output enable                               |

| SSWE                                                | Y7  | O/Z               | SBSRAM write enable                                |

| SSCLK                                               | AA8 | O/Z               | SBSRAM clock                                       |

| <b>EMIF – SYNCHRONOUS DRAM CONTROL</b>              |     |                   |                                                    |

| SDA10                                               | V7  | O/Z               | SDRAM address 10 (separate for deactivate command) |

| SDRAS                                               | V6  | O/Z               | SDRAM row address strobe                           |

| SDCAS                                               | W5  | O/Z               | SDRAM column address strobe                        |

| SDWE                                                | T8  | O/Z               | SDRAM write enable                                 |

| SDCLK                                               | T9  | O/Z               | SDRAM clock                                        |

| <b>EMIF – BUS ARBITRATION</b>                       |     |                   |                                                    |

| HOLD                                                | R6  | I                 | Hold request from the host                         |

| HOLDA                                               | B15 | O                 | Hold request acknowledge to the host               |

| <b>TIMERS</b>                                       |     |                   |                                                    |

| TOUT1                                               | G2  | O/Z               | Timer 1 or general-purpose output                  |

| TINP1                                               | K3  | I                 | Timer 1 or general-purpose input                   |

| TOUT0                                               | M18 | O/Z               | Timer 0 or general-purpose output                  |

| TINP0                                               | J18 | I                 | Timer 0 or general-purpose input                   |

| <b>DMA ACTION COMPLETE</b>                          |     |                   |                                                    |

| DMAC3                                               | E18 | O                 | DMA action complete                                |

| DMAC2                                               | F19 |                   |                                                    |

| DMAC1                                               | E20 |                   |                                                    |

| DMAC0                                               | G16 |                   |                                                    |

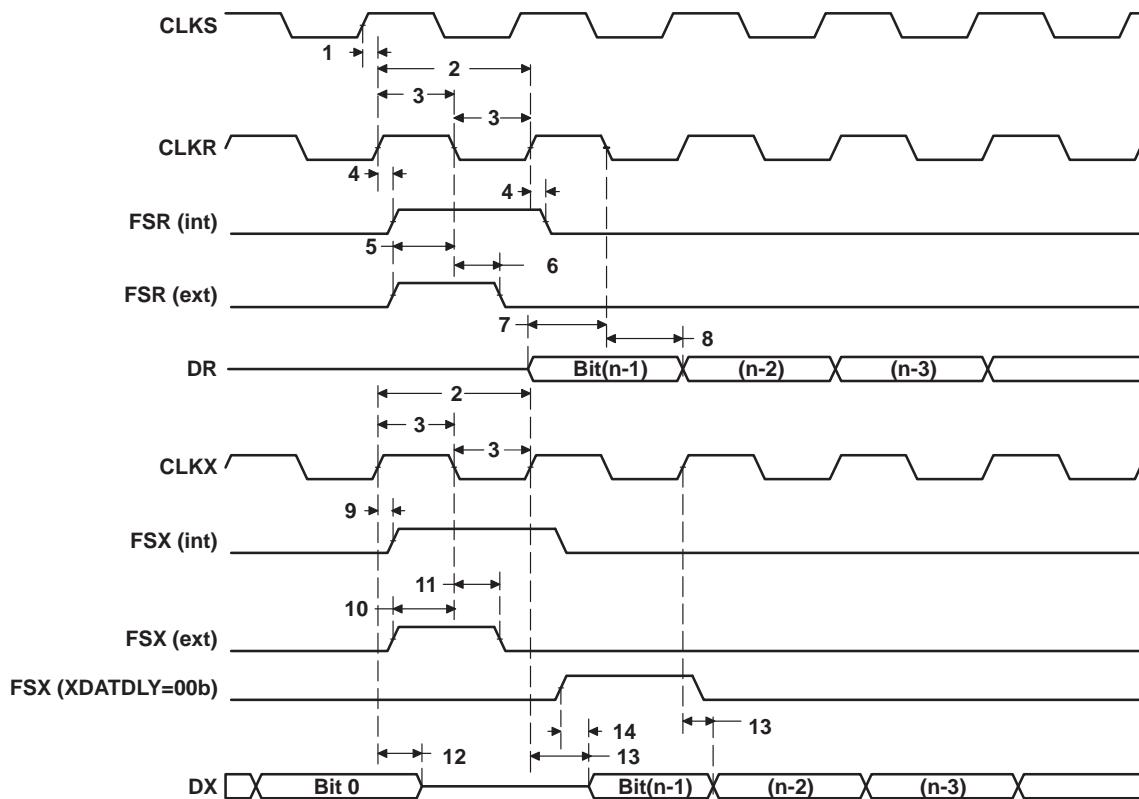

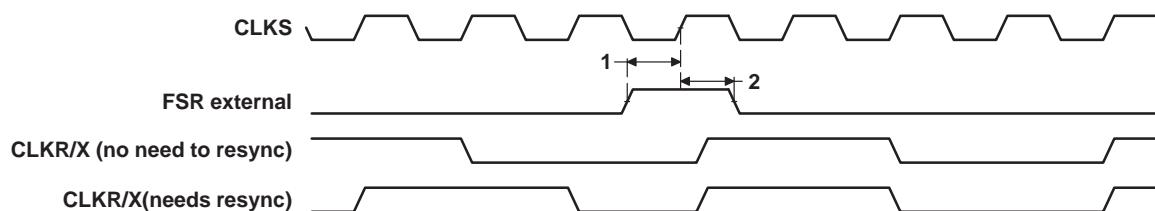

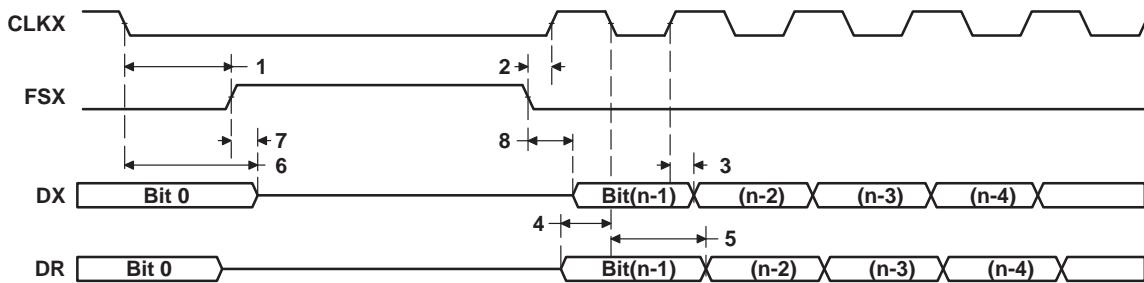

| <b>MULTICHANNEL BUFFERED SERIAL PORT 1 (McBSP1)</b> |     |                   |                                                    |

| CLKS1                                               | F4  | I                 | External clock source (as opposed to internal)     |

| CLKR1                                               | H4  | I/O/Z             | Receive clock                                      |

| CLKX1                                               | J4  | I/O/Z             | Transmit clock                                     |

| DR1                                                 | E2  | I                 | Receive data                                       |

| DX1                                                 | G4  | O/Z               | Transmit data                                      |

| FSR1                                                | F3  | I/O/Z             | Receive frame sync                                 |

| FSX1                                                | F2  | I/O/Z             | Transmit frame sync                                |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME                                      | NO. | TYPE <sup>†</sup> | DESCRIPTION                                                                   |

|-----------------------------------------------------|-----|-------------------|-------------------------------------------------------------------------------|

| <b>MULTICHANNEL BUFFERED SERIAL PORT 0 (McBSP0)</b> |     |                   |                                                                               |

| CLKS0                                               | K18 | I                 | External clock source (as opposed to internal)                                |

| CLKR0                                               | L21 | I/O/Z             | Receive clock                                                                 |

| CLKX0                                               | K20 | I/O/Z             | Transmit clock                                                                |

| DR0                                                 | J21 | I                 | Receive data                                                                  |

| DX0                                                 | M21 | O/Z               | Transmit data                                                                 |

| FSR0                                                | P16 | I/O/Z             | Receive frame sync                                                            |

| FSX0                                                | N16 | I/O/Z             | Transmit frame sync                                                           |

| <b>RESERVED FOR TEST</b>                            |     |                   |                                                                               |

| RSV0                                                | N21 | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| RSV1                                                | K16 | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| RSV2                                                | B13 | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| RSV3                                                | B14 | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| RSV4                                                | F13 | I                 | Reserved for testing, <b><i>pull-down</i></b> with a dedicated 20-kΩ resistor |

| RSV5                                                | C15 | O                 | Reserved (leave unconnected, <b><i>do not</i></b> connect to power or ground) |

| RSV6                                                | F7  | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| RSV7                                                | D7  | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| RSV8                                                | B5  | I                 | Reserved for testing, pull-up with a dedicated 20-kΩ resistor                 |

| <b>SUPPLY VOLTAGE PINS</b>                          |     |                   |                                                                               |

| DVDD                                                | C14 | S                 | 3.3-V supply voltage                                                          |

|                                                     | C8  |                   |                                                                               |

|                                                     | E19 |                   |                                                                               |

|                                                     | E3  |                   |                                                                               |

|                                                     | H11 |                   |                                                                               |

|                                                     | H13 |                   |                                                                               |

|                                                     | H9  |                   |                                                                               |

|                                                     | J10 |                   |                                                                               |

|                                                     | J12 |                   |                                                                               |

|                                                     | J14 |                   |                                                                               |

|                                                     | J19 |                   |                                                                               |

|                                                     | J3  |                   |                                                                               |

|                                                     | J8  |                   |                                                                               |

|                                                     | K11 |                   |                                                                               |

|                                                     | K13 |                   |                                                                               |

|                                                     | K15 |                   |                                                                               |

|                                                     | K7  |                   |                                                                               |

|                                                     | K9  |                   |                                                                               |

|                                                     | L10 |                   |                                                                               |

|                                                     | L12 |                   |                                                                               |

|                                                     | L14 |                   |                                                                               |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME                  | NO. | TYPE† | DESCRIPTION                                                         |

|---------------------------------|-----|-------|---------------------------------------------------------------------|

| SUPPLY VOLTAGE PINS (CONTINUED) |     |       |                                                                     |

| DV <sub>DD</sub>                | L8  | S     | 3.3-V supply voltage                                                |

|                                 | M11 |       |                                                                     |

|                                 | M13 |       |                                                                     |

|                                 | M15 |       |                                                                     |

|                                 | M7  |       |                                                                     |

|                                 | M9  |       |                                                                     |

|                                 | N10 |       |                                                                     |

|                                 | N12 |       |                                                                     |

|                                 | N14 |       |                                                                     |

|                                 | N19 |       |                                                                     |

|                                 | N3  |       |                                                                     |

|                                 | N8  |       |                                                                     |

|                                 | P11 |       |                                                                     |

|                                 | P13 |       |                                                                     |

|                                 | P9  |       |                                                                     |

|                                 | U19 |       |                                                                     |

|                                 | U3  |       |                                                                     |

| CV <sub>DD</sub>                | W14 | S     | 2.5-V supply voltage for 'C6201<br>1.8-V supply voltage for 'C6201B |

|                                 | W8  |       |                                                                     |

|                                 | A12 |       |                                                                     |

|                                 | A13 |       |                                                                     |

|                                 | B10 |       |                                                                     |

|                                 | B12 |       |                                                                     |

|                                 | B6  |       |                                                                     |

|                                 | D15 |       |                                                                     |

|                                 | D16 |       |                                                                     |

|                                 | F10 |       |                                                                     |

|                                 | F14 |       |                                                                     |

|                                 | F8  |       |                                                                     |

|                                 | G13 |       |                                                                     |

|                                 | G7  |       |                                                                     |

|                                 | G8  |       |                                                                     |

|                                 | K4  |       |                                                                     |

|                                 | M3  |       |                                                                     |

|                                 | M4  |       |                                                                     |

|                                 | A3  |       |                                                                     |

|                                 | A5  |       |                                                                     |

|                                 | A7  |       |                                                                     |

|                                 | A16 |       |                                                                     |

†I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

**SM320C6201, SMJ320C6201B

DIGITAL SIGNAL PROCESSORS**

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

**Signal Descriptions (Continued)**

| SIGNAL<br>NAME                         | NO.  | TYPE <sup>†</sup> | DESCRIPTION                                                         |

|----------------------------------------|------|-------------------|---------------------------------------------------------------------|

| <b>SUPPLY VOLTAGE PINS (CONTINUED)</b> |      |                   |                                                                     |

| CV <sub>DD</sub>                       | A18  | S                 | 2.5-V supply voltage for 'C6201<br>1.8-V supply voltage for 'C6201B |

|                                        | AA4  |                   |                                                                     |

|                                        | AA6  |                   |                                                                     |

|                                        | AA15 |                   |                                                                     |

|                                        | AA17 |                   |                                                                     |

|                                        | AA19 |                   |                                                                     |

|                                        | B2   |                   |                                                                     |

|                                        | B4   |                   |                                                                     |

|                                        | B19  |                   |                                                                     |

|                                        | C1   |                   |                                                                     |

|                                        | C3   |                   |                                                                     |

|                                        | C20  |                   |                                                                     |

|                                        | D2   |                   |                                                                     |

|                                        | D21  |                   |                                                                     |

|                                        | E1   |                   |                                                                     |

|                                        | E6   |                   |                                                                     |

|                                        | E8   |                   |                                                                     |

|                                        | E10  |                   |                                                                     |

|                                        | E12  |                   |                                                                     |

|                                        | E14  |                   |                                                                     |

|                                        | E16  |                   |                                                                     |

|                                        | F5   |                   |                                                                     |

|                                        | F17  |                   |                                                                     |

|                                        | F21  |                   |                                                                     |

|                                        | G1   |                   |                                                                     |

|                                        | H5   |                   |                                                                     |

|                                        | H17  |                   |                                                                     |

|                                        | K5   |                   |                                                                     |

|                                        | K17  |                   |                                                                     |

|                                        | M5   |                   |                                                                     |

|                                        | M17  |                   |                                                                     |

|                                        | P5   |                   |                                                                     |

|                                        | P17  |                   |                                                                     |

|                                        | R21  |                   |                                                                     |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME                  | NO.  | TYPE† | DESCRIPTION                                                         |

|---------------------------------|------|-------|---------------------------------------------------------------------|

| SUPPLY VOLTAGE PINS (CONTINUED) |      |       |                                                                     |

| CV <sub>DD</sub>                | T1   | S     | 2.5-V supply voltage for 'C6201<br>1.8-V supply voltage for 'C6201B |

|                                 | T5   |       |                                                                     |

|                                 | T17  |       |                                                                     |

|                                 | U6   |       |                                                                     |

|                                 | U8   |       |                                                                     |

|                                 | U10  |       |                                                                     |

|                                 | U12  |       |                                                                     |

|                                 | U14  |       |                                                                     |

|                                 | U16  |       |                                                                     |

|                                 | U21  |       |                                                                     |

|                                 | V1   |       |                                                                     |

|                                 | V20  |       |                                                                     |

|                                 | W2   |       |                                                                     |

|                                 | W19  |       |                                                                     |

|                                 | W21  |       |                                                                     |

|                                 | Y3   |       |                                                                     |

|                                 | Y18  |       |                                                                     |

|                                 | Y20  |       |                                                                     |

|                                 | AA11 |       |                                                                     |

|                                 | AA12 |       |                                                                     |

|                                 | F20  |       |                                                                     |

|                                 | G18  |       |                                                                     |

|                                 | H16  |       |                                                                     |

|                                 | H18  |       |                                                                     |

|                                 | L18  |       |                                                                     |

|                                 | L19  |       |                                                                     |

|                                 | L20  |       |                                                                     |

|                                 | N20  |       |                                                                     |

|                                 | P18  |       |                                                                     |

|                                 | P19  |       |                                                                     |

|                                 | R10  |       |                                                                     |

|                                 | R14  |       |                                                                     |

|                                 | U4   |       |                                                                     |

|                                 | V11  |       |                                                                     |

|                                 | V12  |       |                                                                     |

|                                 | V15  |       |                                                                     |

|                                 | W13  |       |                                                                     |

† I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

**SM320C6201, SMJ320C6201B

DIGITAL SIGNAL PROCESSORS**

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

**Signal Descriptions (Continued)**

| SIGNAL<br>NAME     | NO.  | TYPE <sup>†</sup> | DESCRIPTION |

|--------------------|------|-------------------|-------------|

| <b>GROUND PINS</b> |      |                   |             |

| VSS                | C11  | GND               | Ground pins |

|                    | C16  |                   |             |

|                    | C6   |                   |             |

|                    | D5   |                   |             |

|                    | G3   |                   |             |

|                    | H10  |                   |             |

|                    | H12  |                   |             |

|                    | H14  |                   |             |

|                    | H7   |                   |             |

|                    | H8   |                   |             |

|                    | J11  |                   |             |

|                    | J13  |                   |             |

|                    | J7   |                   |             |

|                    | J9   |                   |             |

|                    | K8   |                   |             |

|                    | L7   |                   |             |

|                    | L9   |                   |             |

|                    | M8   |                   |             |

|                    | N7   |                   |             |

|                    | R3   |                   |             |

|                    | A4   |                   |             |

|                    | A6   |                   |             |

|                    | A8   |                   |             |

|                    | A15  |                   |             |

|                    | A17  |                   |             |

|                    | A19  |                   |             |

|                    | AA3  |                   |             |

|                    | AA5  |                   |             |

|                    | AA7  |                   |             |

|                    | AA14 |                   |             |

|                    | AA16 |                   |             |

|                    | AA18 |                   |             |

|                    | B3   |                   |             |

|                    | B18  |                   |             |

|                    | B20  |                   |             |

|                    | C2   |                   |             |

|                    | C19  |                   |             |

|                    | C21  |                   |             |

|                    | D1   |                   |             |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME          | NO. | TYPE† | DESCRIPTION |

|-------------------------|-----|-------|-------------|

| GROUND PINS (CONTINUED) |     |       |             |

| V <sub>SS</sub>         |     | GND   | Ground pins |

† I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

**SM320C6201, SMJ320C6201B

DIGITAL SIGNAL PROCESSORS**

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

**Signal Descriptions (Continued)**

| SIGNAL<br>NAME                 | NO. | TYPE <sup>†</sup> | DESCRIPTION |

|--------------------------------|-----|-------------------|-------------|

| <b>GROUND PINS (CONTINUED)</b> |     |                   |             |

| V <sub>SS</sub>                | W1  | GND               | Ground pins |

|                                | W3  |                   |             |

|                                | W20 |                   |             |

|                                | Y2  |                   |             |

|                                | Y4  |                   |             |

|                                | Y19 |                   |             |

|                                | F18 |                   |             |

|                                | G19 |                   |             |

|                                | H15 |                   |             |

|                                | J15 |                   |             |

|                                | J16 |                   |             |

|                                | K10 |                   |             |

|                                | K12 |                   |             |

|                                | K14 |                   |             |

|                                | L11 |                   |             |

|                                | L13 |                   |             |

|                                | L15 |                   |             |

|                                | M10 |                   |             |

|                                | M12 |                   |             |

|                                | M14 |                   |             |

|                                | N11 |                   |             |

|                                | N13 |                   |             |

|                                | N15 |                   |             |

|                                | N9  |                   |             |

|                                | P10 |                   |             |

|                                | P12 |                   |             |

|                                | P14 |                   |             |

|                                | P15 |                   |             |

|                                | P7  |                   |             |

|                                | P8  |                   |             |

|                                | R19 |                   |             |

|                                | T4  |                   |             |

|                                | W11 |                   |             |

|                                | W16 |                   |             |

|                                | W6  |                   |             |

<sup>†</sup>I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## Signal Descriptions (Continued)

| SIGNAL<br>NAME             | NO.                                                                                                                           | TYPE† | DESCRIPTION      |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------------------|

| REMAINING UNCONNECTED PINS |                                                                                                                               |       |                  |

| NC                         | D13<br>D14<br>D18<br>D3<br>D6<br>F12<br>F16<br>G12<br>G15<br>H19<br>H20<br>H21<br>L16<br>M16<br>M19<br>V19<br>V4<br>W18<br>W4 |       | Unconnected pins |

† I = Input, O = Output, Z = High Impedance, S = Supply Voltage, GND = Ground

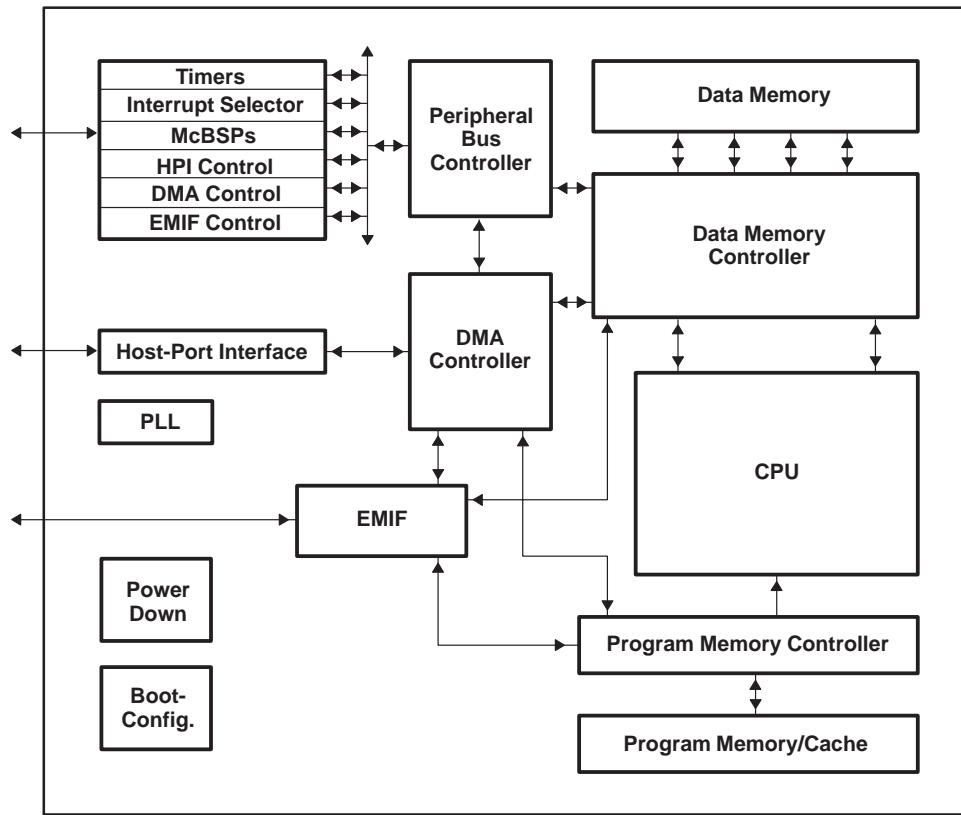

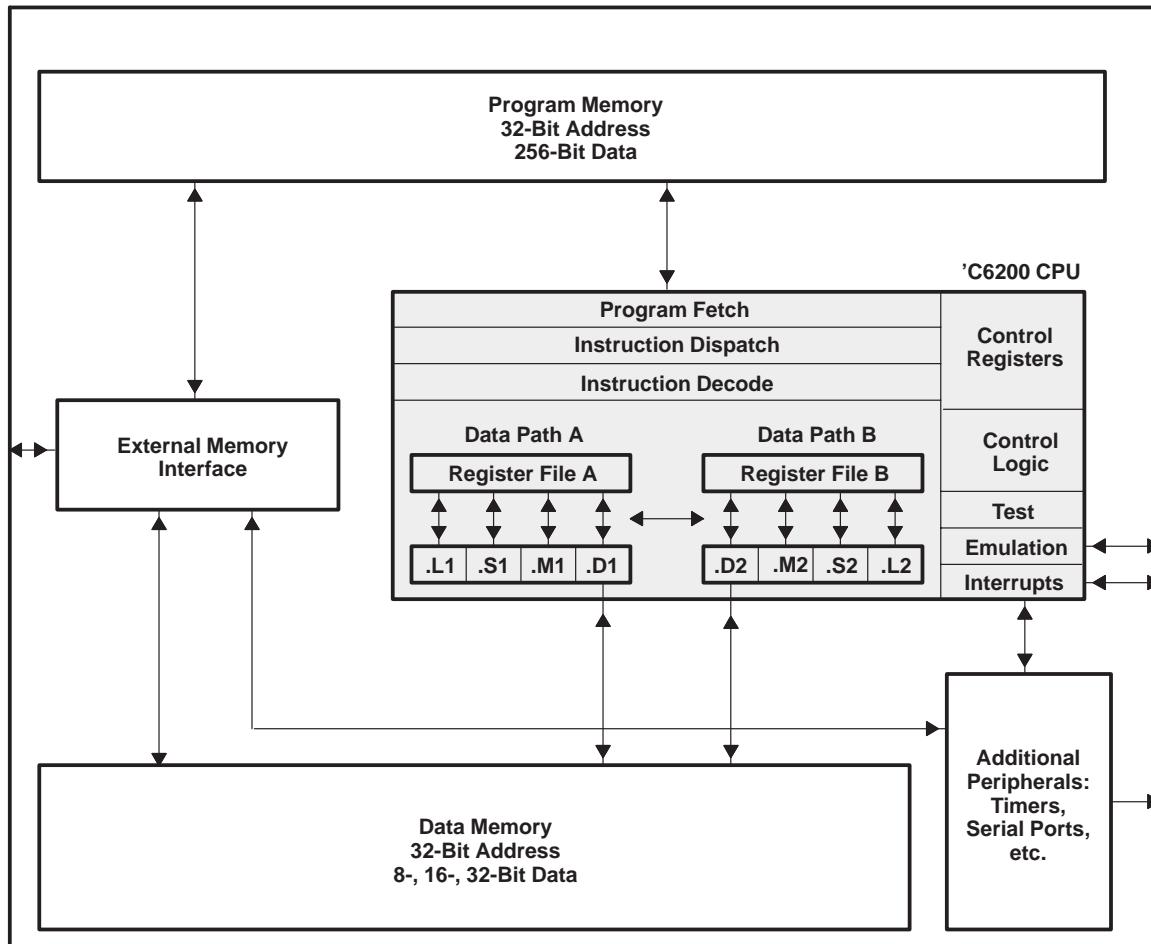

functional block diagram

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## signal groups

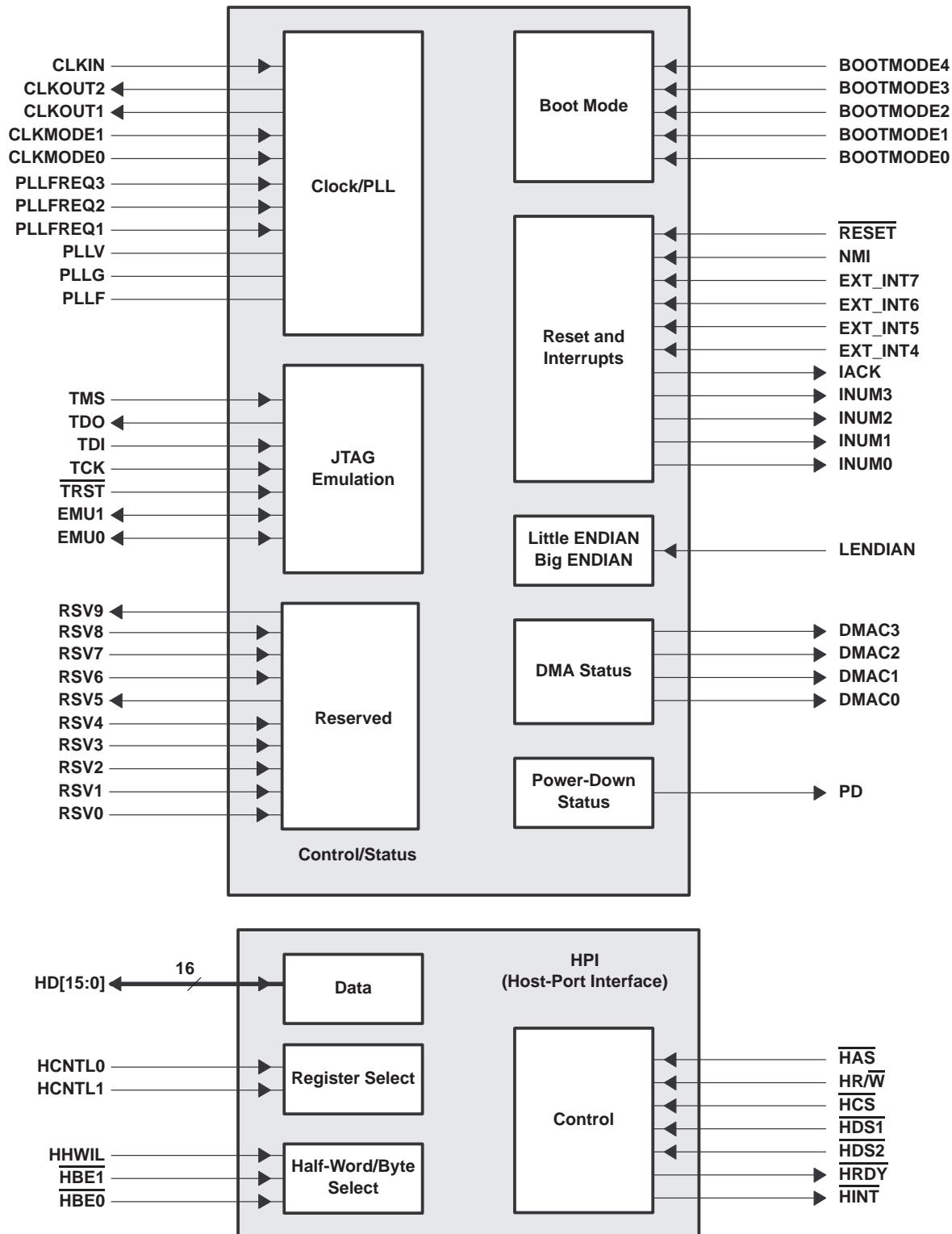

Figure 1. CPU and Peripheral Signals

signal groups (continued)

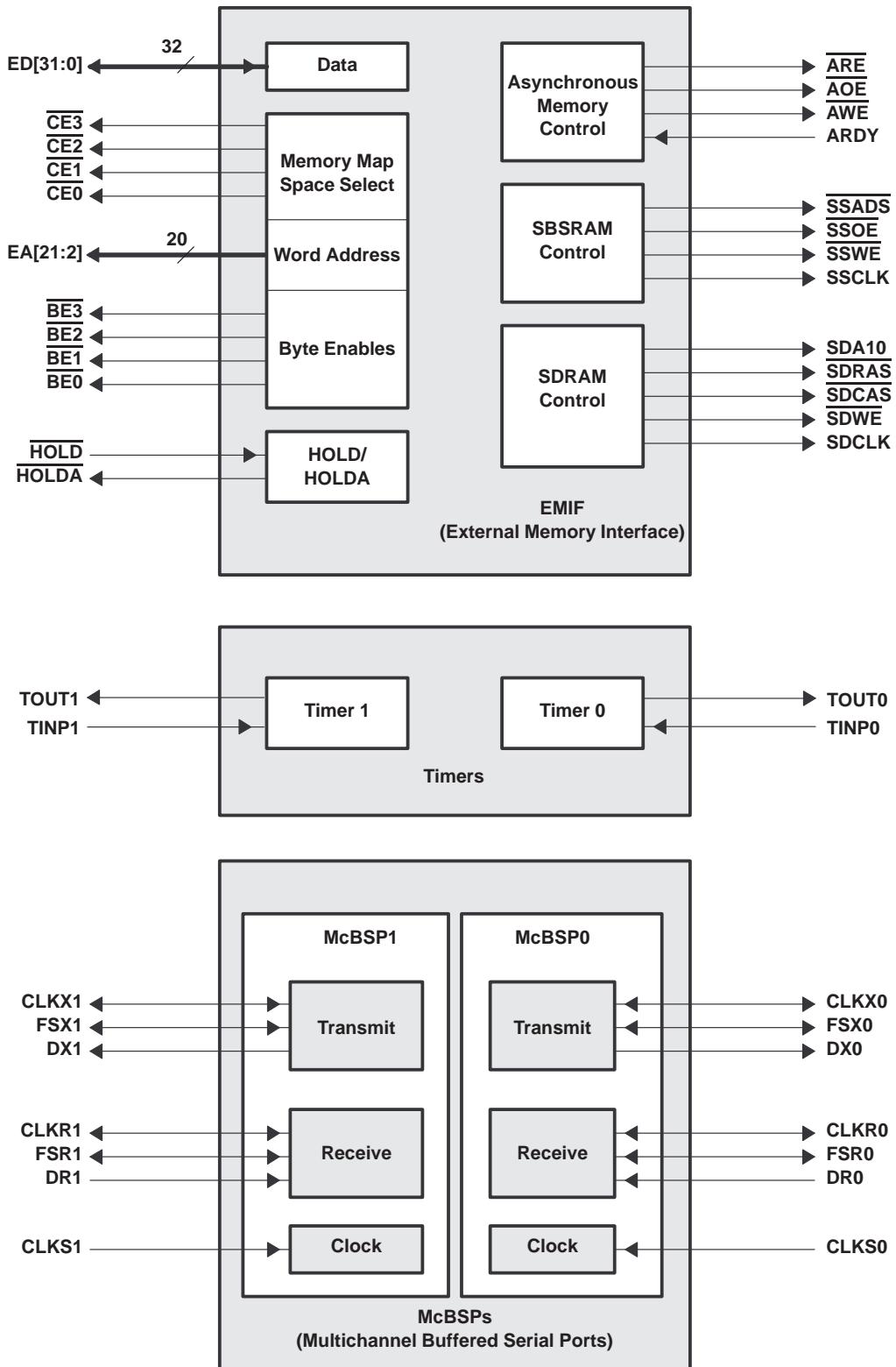

Figure 2. Peripheral Signals

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## CPU description

The CPU fetches VelociTI advanced very-long instruction words (VLIW) (256 bits wide) to supply up to eight 32-bit instructions to the eight functional units during every clock cycle. The VelociTI VLIW architecture features controls by which all eight units do not have to be supplied with instructions if they are not ready to execute. The first bit of every 32-bit instruction determines if the next instruction belongs to the same execute packet as the previous instruction, or whether it should be executed in the following clock as a part of the next execute packet. Fetch packets are always 256 bits wide; however, the execute packets can vary in size. The variable-length execute packets are a key memory-saving feature, distinguishing the 'C6200<sup>†</sup> CPU from other VLIW architectures.

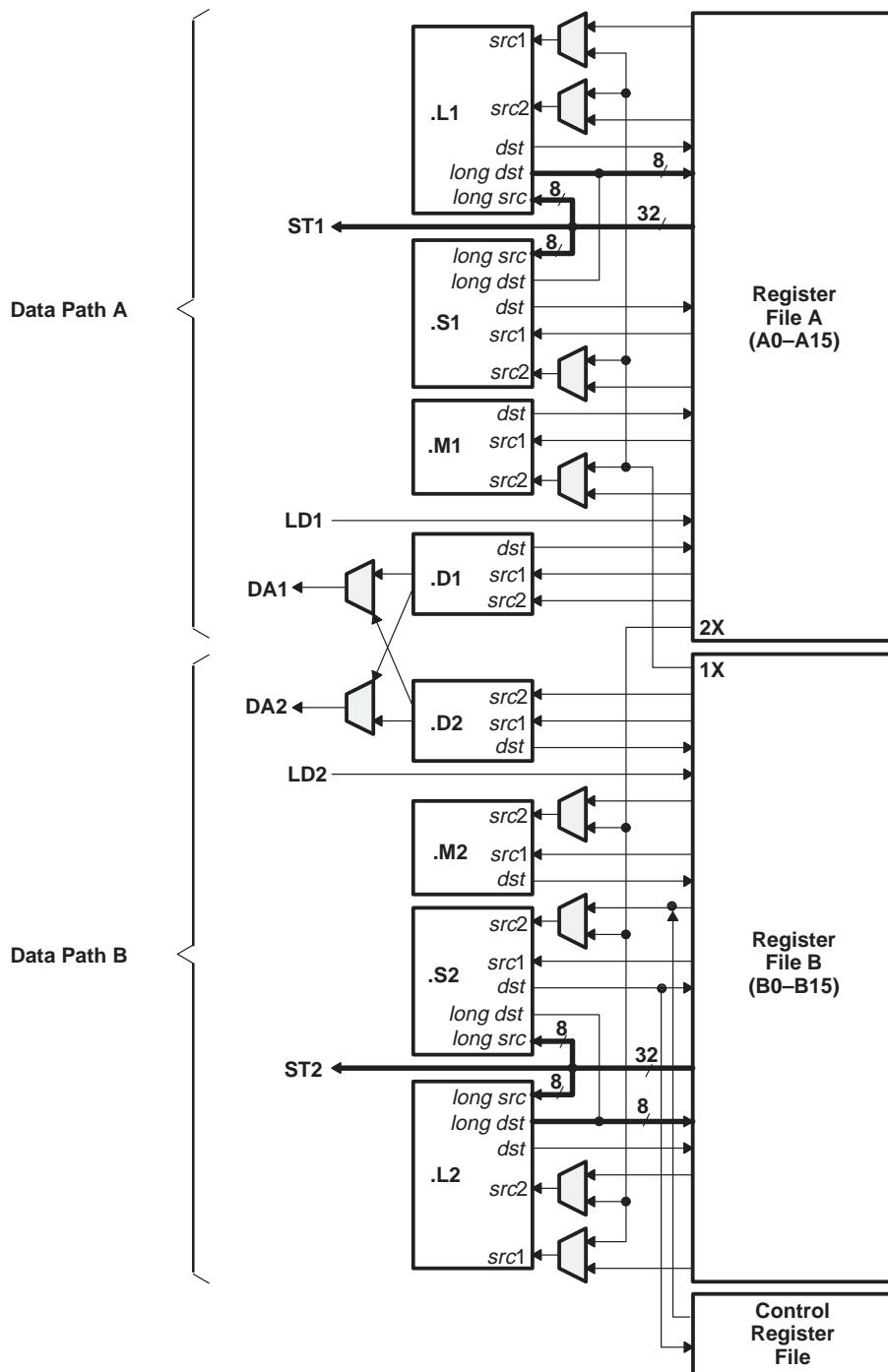

The CPU features two sets of functional units. Each set contains four units and a register file. One set contains functional units .L1, .S1, .M1, and .D1; the other set contains units .D2, .M2, .S2, and .L2. The two register files each contain 16 32-bit registers for a total of 32 general-purpose registers. The two sets of functional units, along with two register files, compose sides A and B of the CPU (see Figure 3 and Figure 4). The four functional units on each side of the CPU can freely share the 16 registers belonging to that side. Additionally, each side features a single data bus connected to all the registers on the other side, by which the two sets of functional units can access data from the register files on the opposite side. While register access by functional units on the same side of the CPU as the register file can service all the units in a single clock cycle, register access using the register file across the CPU supports one read and one write per cycle.

Another key feature of the 'C6200 CPU is the load/store architecture, where all instructions operate on registers (as opposed to data in memory). Two sets of data-addressing units (.D1 and .D2) are responsible for all data transfers between the register files and the memory. The data address driven by the .D units allows data addresses generated from one register file to be used to load or store data to or from the other register file. The 'C6200 CPU supports a variety of indirect addressing modes using either linear- or circular-addressing modes with 5- or 15-bit offsets. All instructions are conditional, and most can access any one of the 32 registers. Some registers, however, are singled out to support specific addressing or to hold the condition for conditional instructions (if the condition is not automatically “true”). The two .M functional units are dedicated for multiplies. The two .S and .L functional units perform a general set of arithmetic, logical, and branch functions with results available every clock cycle.

The processing flow begins when a 256-bit-wide instruction fetch packet is fetched from a program memory. The 32-bit instructions destined for the individual functional units are “linked” together by “1” bits in the least significant bit (LSB) position of the instructions. The instructions that are “chained” together for simultaneous execution (up to eight in total) compose an execute packet. A “0” in the LSB of an instruction breaks the chain, effectively placing the instructions that follow it in the next execute packet. If an execute packet crosses the fetch packet boundary (256 bits wide), the assembler places it in the next fetch packet, while the remainder of the current fetch packet is padded with NOP instructions. The number of execute packets within a fetch packet can vary from one to eight. Execute packets are dispatched to their respective functional units at the rate of one per clock cycle and the next 256-bit fetch packet is not fetched until all the execute packets from the current fetch packet have been dispatched. After decoding, the instructions simultaneously drive all active functional units for a maximum execution rate of eight instructions every clock cycle. While most results are stored in 32-bit registers, they can be subsequently moved to memory as bytes or half-words as well. All load and store instructions are byte-, half-word, or word-addressable.

<sup>†</sup> Where unique device characteristics are specified, SM320C6201 and SMJ320C6201B identifiers are used. For generic characteristics, no identifiers are needed, 'C62xx is used, or 'C6200 is used.

CPU description (continued)

Figure 3. SM320C6200 CPU Block Diagram

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## CPU description (continued)

Figure 4. SM320C6200 CPU Data Paths

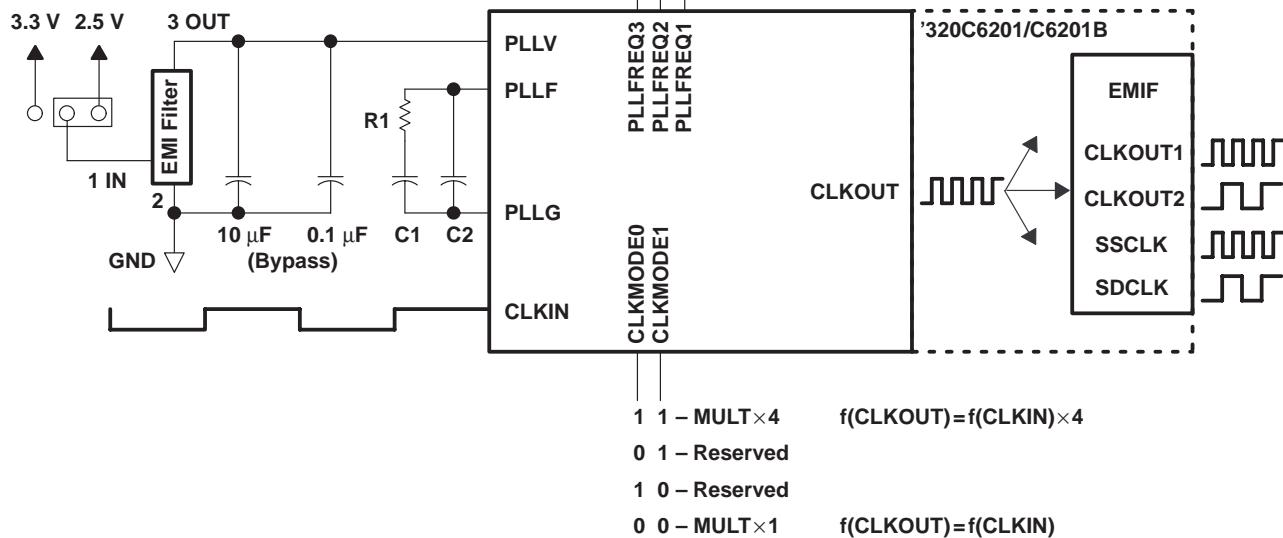

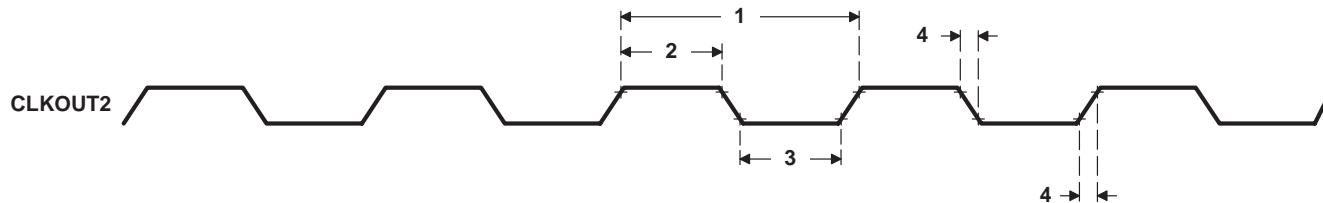

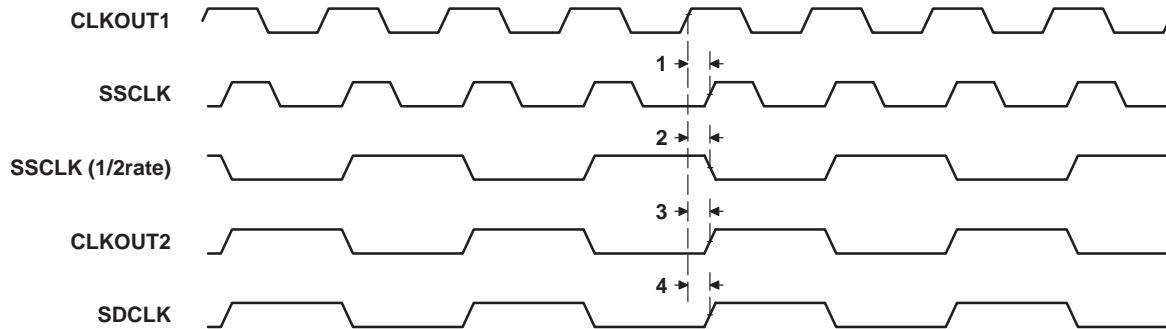

## clock PLL

All of the 'C62xx clocks are generated from a single source through the CLKIN pin. This source clock either drives the PLL, which generates the internal CPU clock, or bypasses the PLL to become the CPU clock.

To use the PLL to generate the CPU clock, the filter circuit shown in Figure 5 must be properly designed. Note that for 'C6201, the EMI filter must be powered by the core voltage (2.5 V), and for 'C6201B, it must be powered by the I/O voltage (3.3 V).

To configure the 'C62xx PLL clock for proper operation, see Figure 5 and Table 1. To minimize the clock jitter, a single clean power supply should power both the 'C62x device and the external clock oscillator circuit. The minimum CLKIN rise and fall times should also be observed. See the *input and output clocks* section for input clock timing requirements.

'C6201 CLKOUT1 Frequency Range 40–200 MHz – 0 1 0 – 'C6201B CLKOUT1 Frequency Range 130–233 MHz

'C6201 CLKOUT1 Frequency Range 35–160 MHz – 0 0 1 – 'C6201B CLKOUT1 Frequency Range 65–200 MHz

'C6201 CLKOUT1 Frequency Range 25–135 MHz – 0 0 0 – 'C6201B CLKOUT1 Frequency Range 50–140 MHz

NOTES:

- For the 'C6201 CLKMODE x4, values for C1, C2, and R1 depend on CLKIN and CLKOUT frequencies. For the 'C6201B CLKMODE x4, values for C1, C2, and R1 are fixed and apply to all valid frequency ranges of CLKIN and CLKOUT.

- For CLKMODE x1, the PLL is bypassed and all six external PLL components can be removed. For this case, the PLLV terminal has to be connected to a clean supply and the PLLG and PLLF terminals should be tied together.

- Due to overlap of frequency ranges when choosing the PLLFREQ, more than one frequency range can contain the CLKOUT frequency. Choose the lowest frequency range that includes the desired frequency. For example, CLKOUT1 = 133 MHz, a PLLFREQ value of 000b should be used for both the 'C6201 and the 'C6201B. For CLKOUT1 = 200 MHz, PLLFREQ should be set to 010b for the 'C6201 or 001b for the 'C6201B. PLLFREQ values other than 000b, 001b, and 010b are reserved.

- EMI filter manufacturer TDK part number ACF451832-153-T

- For the 'C6201B, the 3.3-V supply for the EMI filter (and PLLV) must be from the same 3.3-V power plane supplying the I/O voltage, DVDD.

Figure 5. PLL Block Diagram

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## clock PLL (continued)

**Table 1. SM320C6201 PLL Component Selection Table†**

| CYCLE TIME (ns) | CLKMODE | CLKIN (MHz) | CLKOUT1 (MHz) | R1 (Ω) | C1 (μF) | C2 (pF) | EMI FILTER PART NO.‡ | TYPICAL LOCK TIME (μs)§ |

|-----------------|---------|-------------|---------------|--------|---------|---------|----------------------|-------------------------|

| 5               | x4      | 50          | 200           | 16.9   | 0.15    | 2700    | TDK #153             | 59                      |

| 5.5             | x4      | 45.5        | 181.8         | 13.7   | 0.18    | 3900    | TDK #153             | 49                      |

| 6               | x4      | 41.6        | 166.7         | 17.4   | 0.15    | 3300    | TDK #153             | 68                      |

| 6.5             | x4      | 38.5        | 153.8         | 16.2   | 0.18    | 3900    | TDK #153             | 70                      |

| 7               | x4      | 35.7        | 142.9         | 15     | 0.22    | 3900    | TDK #153             | 72                      |

| 7.5             | x4      | 33.3        | 133.3         | 16.2   | 0.22    | 3900    | TDK #153             | 84                      |

| 8               | x4      | 31.3        | 125           | 14     | 0.27    | 4700    | TDK #153             | 77                      |

| 8.5             | x4      | 29.4        | 117.7         | 11.8   | 0.33    | 6800    | TDK #153             | 67                      |

| 9               | x4      | 27.7        | 111.1         | 11     | 0.39    | 6800    | TDK #153             | 68                      |

| 9.5             | x4      | 26.3        | 105.3         | 10.5   | 0.39    | 8200    | TDK #153             | 65                      |

| 10              | x4      | 25          | 100           | 10     | 0.47    | 8200    | TDK #153             | 68                      |

† For CLKMODE x1, the PLL is bypassed and all six external PLL components can be removed. For this case, the PLLV terminal has to be connected to a clean supply and the PLLG and PLLF terminals should be tied together.

‡ Full EMI filter part number : ACF 451832-153-T

§ Under some operating conditions, the maximum PLL lock time may vary as much as 150% from the specified typical value. For example, if the typical lock time is specified as 100 μs, the maximum value may be as long as 250 μs.

**Table 2. SM320C6201B PLL Component Selection Table†**

| CLKMODE | R1 (Ω) | C1 (nF) | C2 (pF) | EMI FILTER PART NO.‡ | TYPICAL LOCK TIME (μs)§ |

|---------|--------|---------|---------|----------------------|-------------------------|

| x4      | 60.4   | 27      | 560     | TDK #153             | 75                      |

† For CLKMODE x1, the PLL is bypassed and all six external PLL components can be removed. For this case, the PLLV terminal has to be connected to a clean supply and the PLLG and PLLF terminals should be tied together.

‡ Full EMI filter part number : ACF 451832-153-T

§ Under some operating conditions, the maximum PLL lock time may vary as much as 150% from the specified typical value. For example, if the typical lock time is specified as 100 μs, the maximum value may be as long as 250 μs.

## power supply sequencing

For the 'C6201 device, the 2.5-V supply powers the core and the 3.3-V supply powers the I/O buffers. For the 'C6201B device, the 1.8-V supply powers the core and the 3.3-V supply powers the I/O buffers. The core supply should be powered up first, or at the same time as the I/O buffers. This is to ensure that the I/O buffers have valid inputs from the core before the output buffers are powered up, thus preventing bus contention with other chips on the board.

# SM320C6201, SMJ320C6201B DIGITAL SIGNAL PROCESSORS

SGUS028A – NOVEMBER 1998 – REVISED JANUARY 1999

## development support

Texas Instruments (TI™) offers an extensive line of development tools for the 'C6200 generation of DSPs, including tools to evaluate the performance of the processors, generate code, develop algorithm implementations, and fully integrate and debug software and hardware modules.

The following products support development of 'C6200-based applications:

### Software Development Tools:

Assembly optimizer

Assembler/Linker

Simulator

Optimizing ANSI C compiler

Application algorithms

C/Assembly debugger and code profiler

### Hardware Development Tools:

Extended development system (XDS™) emulator (supports 'C6200 multiprocessor system debug)

EVM (Evaluation Module)

The *TMS320 DSP Development Support Reference Guide* (SPRU011) contains information about development-support products for all TMS320 family member devices, including documentation. See this document for further information on TMS320 documentation or any TMS320 support products from Texas Instruments. An additional document, the *TMS320 Third-Party Support Reference Guide* (SPRU052), contains information about TMS320-related products from other companies in the industry. To receive TMS320 literature, contact the Literature Response Center at 800/477-8924.

See Table 3 for a complete listing of development-support tools for the 'C6200. For information on pricing and availability, contact the nearest TI field sales office or authorized distributor.

**Table 3. TMS320C6xx Development-Support Tools**

| DEVELOPMENT TOOL                               | PLATFORM            | PART NUMBER    |

|------------------------------------------------|---------------------|----------------|

| <b>Software</b>                                |                     |                |

| C Compiler/Assembler/Linker/Assembly Optimizer | Win32™              | TMDX3246855-07 |

| C Compiler/Assembler/Linker/Assembly Optimizer | SPARC™ Solaris™     | TMDX324655-07  |

| Simulator                                      | Win32               | TMDS3246851-07 |

| Simulator                                      | SPARC Solaris       | TMDS3246551-07 |

| XDS510™ Debugger/Emulation Software            | Win32, Windows NT™  | TMDX324016X-07 |

| <b>Hardware</b>                                |                     |                |

| XDS510 Emulator†                               | PC                  | TMDS00510      |

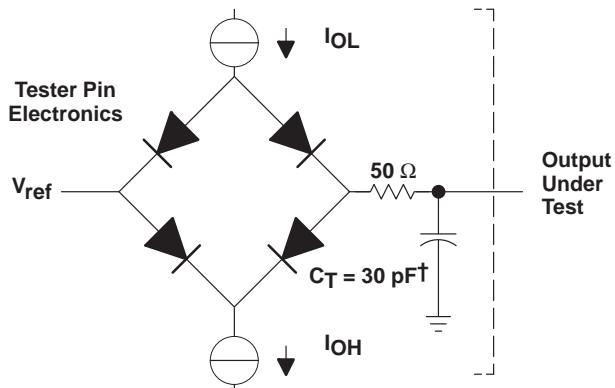

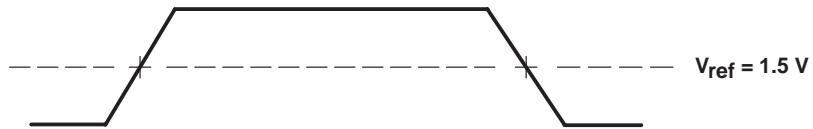

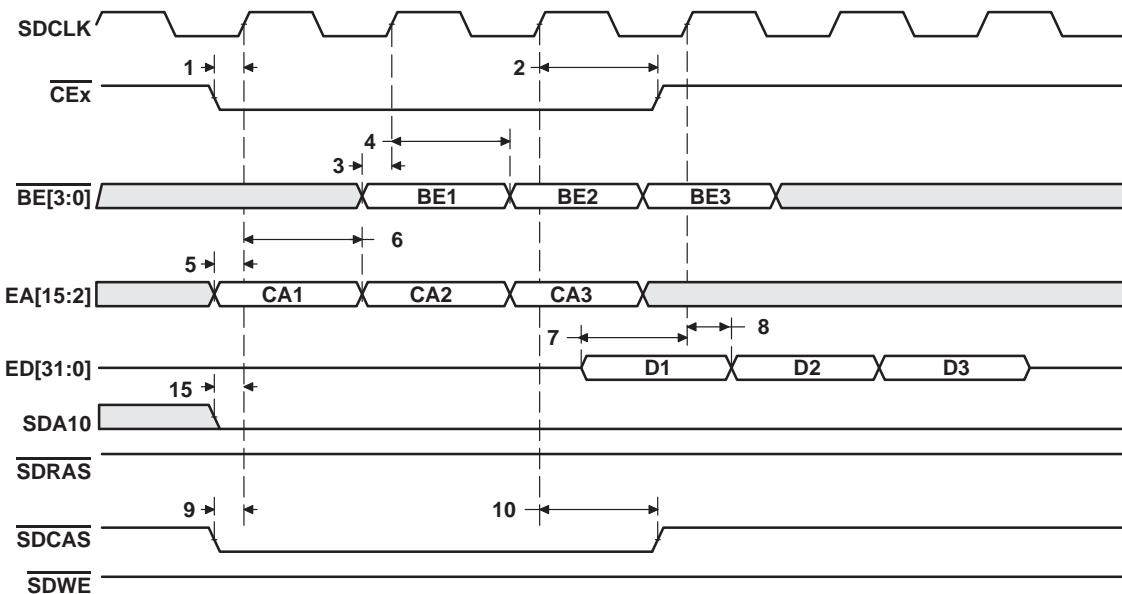

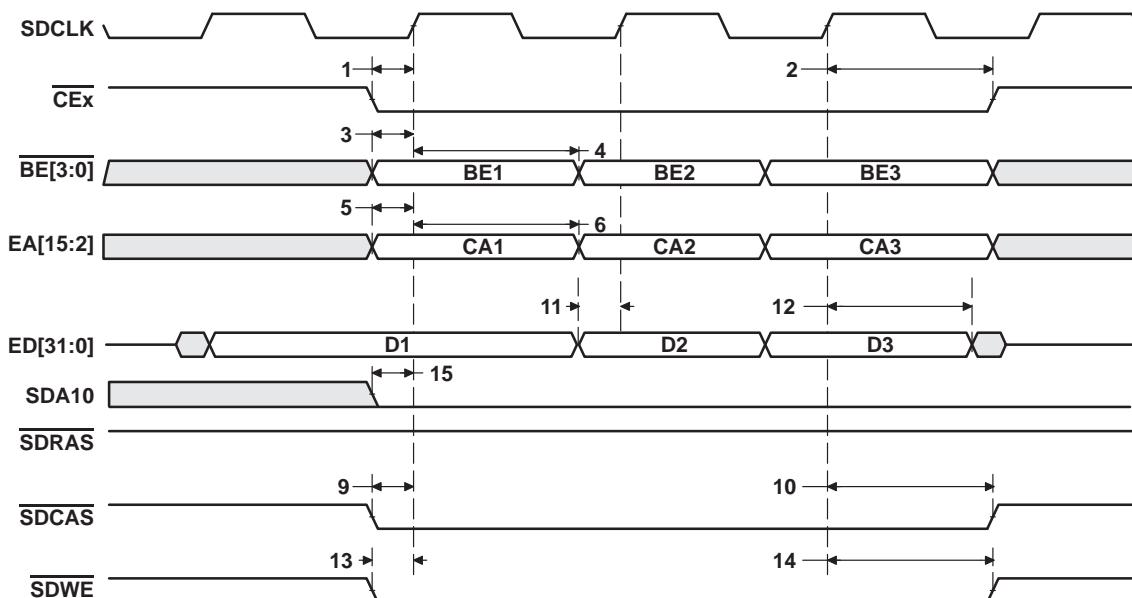

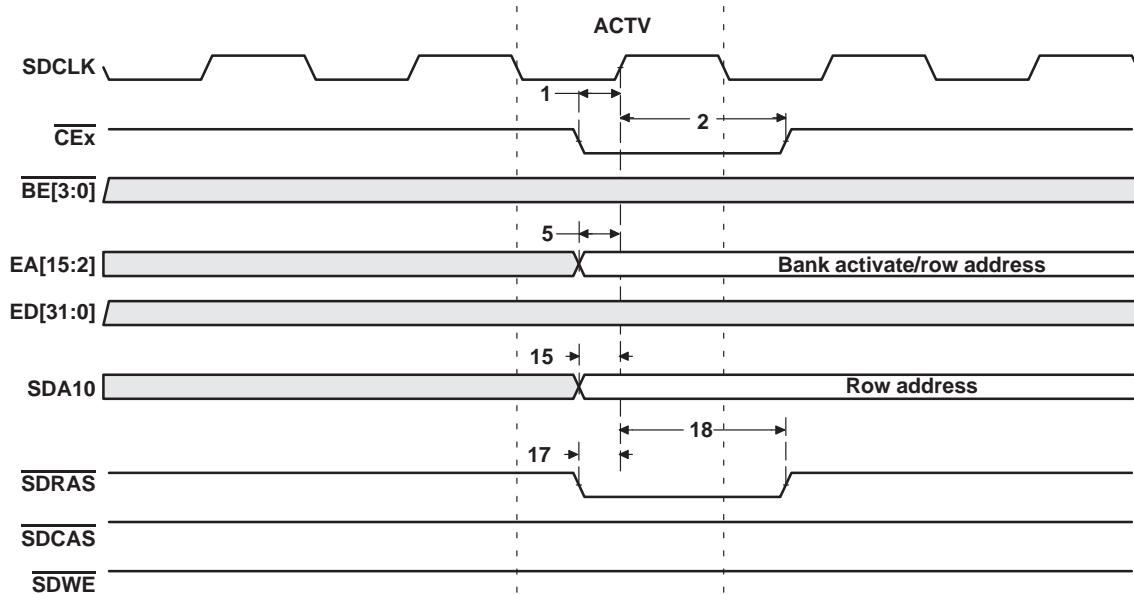

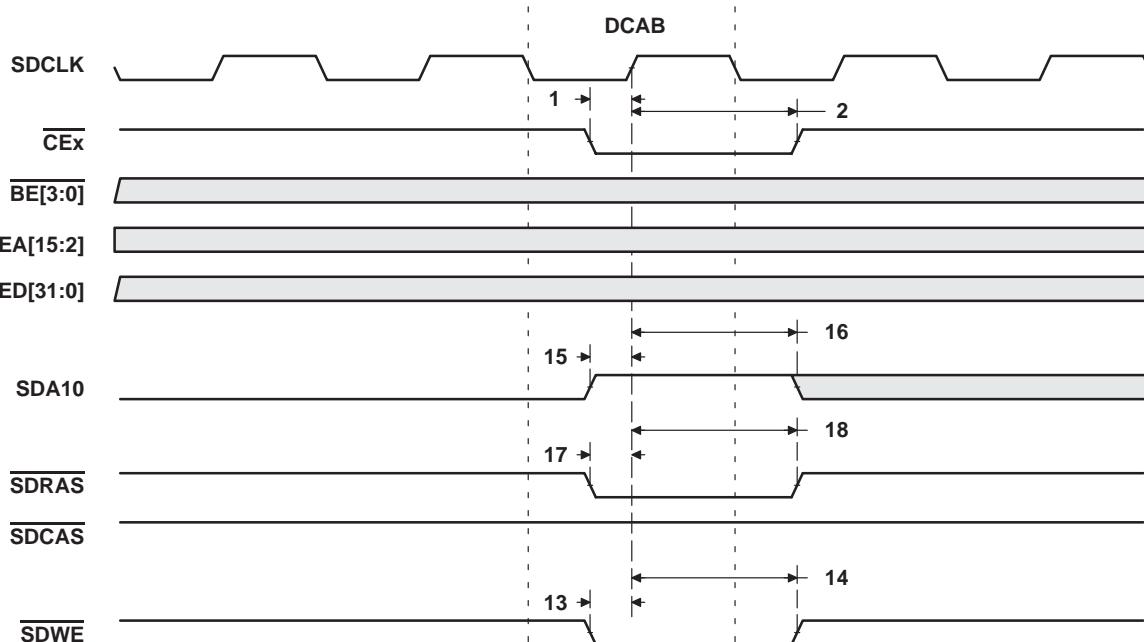

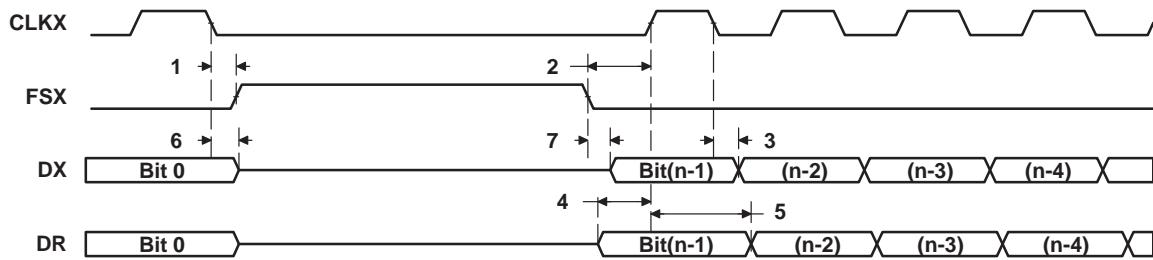

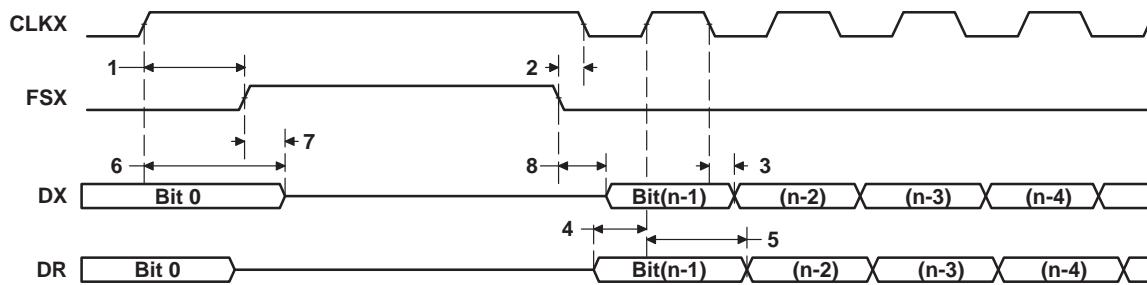

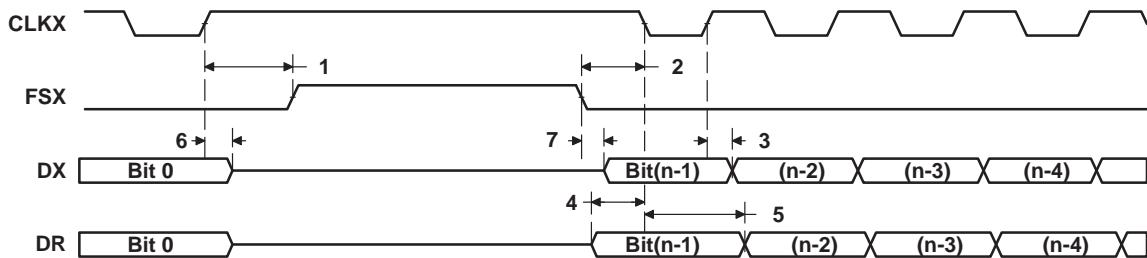

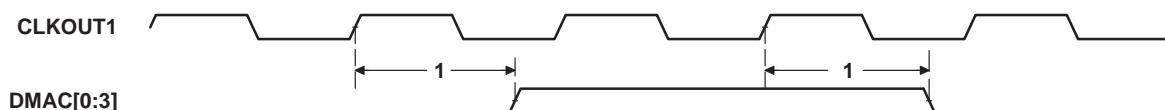

| XDS510WS™ Emulator‡                            | SCSI                | TMDS00510WS    |