## **OVERVIEW**

The SM5142AP/AM is a 20 MHz frequency synthesizer PLL IC, fabricated using NPC's unique Molybdenum-gate CMOS process. It is ideal for tuners that use double-conversion receivers.

## **FEATURES**

- 20 MHz direct frequency division

- 4 selectable reference frequencies (1, 5, 9 and 10 kHz)

- Built-in transistor for low-pass filter

- 60 kHz and 8 Hz outputs for external application

- Package

- 14-pin plastic SSOP

- 14-pin plastic DIP

- Molybdenum-gate CMOS process

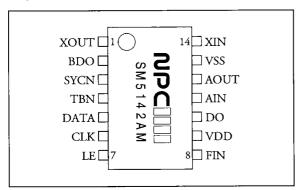

## **PINOUTS**

## 14-pin SSOP

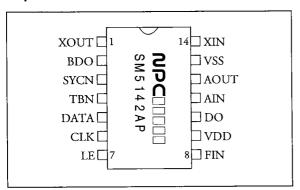

# 14-pin DIP

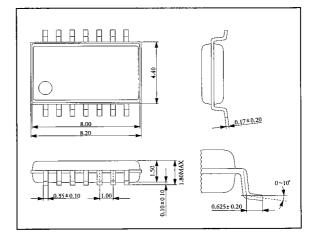

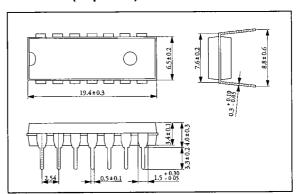

# **PACKAGE DIMENSIONS**

Unit: mm

#### SM5142AM (14-pin SSOP)

## SM5142AP (14-pin DIP)

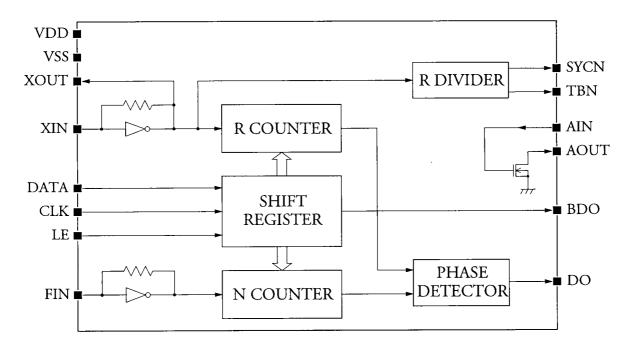

# **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| Number | Name | 1/0 | Description                                                                                                                                                                                    |                                                                    |  |  |

|--------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| 1      | XOUT | 0   | Crystal oscillator element and capacitor connection pin. The signal from this pin can be input to a 2nd mixer stage.                                                                           |                                                                    |  |  |

| 2      | BDO  | 0   | Shift register output pin                                                                                                                                                                      |                                                                    |  |  |

| 3      | SYCN | 0   | 60 kHz controller clock output pin.  N-channel open-drain output. A diode is built-in for electrostatic breakdown protection, so the voltage on this pin should not exceed the supply voltage. |                                                                    |  |  |

| 4      | TBN  | 0   | 8 Hz time-base clock output pin. N-channel open-drain output. A diode is buil on this pin should not exceed the supply vol                                                                     | It-in for electrostatic breakdown protection, so the voltage tage. |  |  |

| 5      | DATA | 1   | Shift register data input pin                                                                                                                                                                  |                                                                    |  |  |

| 6      | CLK  | ı   | Clock input pin                                                                                                                                                                                | Frequency divider and mode select input pins                       |  |  |

| 7      | LE   | ī   | Latch write enable signal input pin                                                                                                                                                            |                                                                    |  |  |

| 8      | FIN  | ı   | Programmable divider input pin. A feedback resistor is built-in, and inputs car                                                                                                                | n be coupled capacitively.                                         |  |  |

| 9      | VDD  | -   | 4.5 to 5.5 V supply pin                                                                                                                                                                        |                                                                    |  |  |

| 10     | DO   | 0   | Phase comparator output pin. An active filter charge pump circuit is built-in                                                                                                                  | 1.                                                                 |  |  |

| 11     | AIN  | 1   | Low-pass filter amplifier input pin                                                                                                                                                            |                                                                    |  |  |

| 12     | AOUT | 0   | Low-pass filter amplifier output pin. N-channel open-drain output.                                                                                                                             |                                                                    |  |  |

| 13     | VSS  | _   | Ground pin                                                                                                                                                                                     |                                                                    |  |  |

| 14     | XIN  |     | Crystal oscillator element and capacitor connection pin. Feedback resistor built-in.                                                                                                           |                                                                    |  |  |

# **SPECIFICATIONS**

# **Absolute Maximum Ratings**

$V_{SS} = 0 V$

| Parameter                   | Symbol           | Condition              | Rating                        | Unit |

|-----------------------------|------------------|------------------------|-------------------------------|------|

| Supply voltage range        | V <sub>DD</sub>  |                        | -0.3 to 6.5                   | ٧    |

| Input voltage range         | V <sub>IN</sub>  |                        | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| AOUT output current range   | l <sub>out</sub> |                        | 0 to 5.0                      | mA   |

| AOUT output voltage range   | V <sub>OUT</sub> |                        | -0.3 to 15.0                  | V    |

| Power dissipation           | P <sub>D</sub>   | T <sub>a</sub> ≤ 85 °C | 150                           | mW   |

| Operating temperature range | T <sub>opr</sub> |                        | -30 to 85                     | °C   |

| Storage temperature range   | T <sub>stg</sub> |                        | -55 to 125                    | °C   |

| Soldering temperature       | T <sub>sld</sub> |                        | 255                           | °C   |

| Soldering time              | t <sub>sid</sub> |                        | 10                            | s    |

# **Electrical Characteristics**

$V_{SS} = 0 \text{ V}, T_a = -30 \text{ to } 85 \text{ }^{\circ}\text{C}$

|                                               | Symbol               | Condition                         |                       | Rating |                 |       |

|-----------------------------------------------|----------------------|-----------------------------------|-----------------------|--------|-----------------|-------|

| Parameter                                     |                      |                                   | min                   | typ    | max             | Unit  |

| Supply voltage                                | V <sub>DD</sub>      | -                                 | 4.5                   | _      | 5.5             | ٧     |

| Current consumption <sup>1</sup>              | I <sub>DD1</sub>     |                                   | -                     | -      | 12              | mA    |

| Standby mode current consumption <sup>2</sup> | I <sub>DD2</sub>     |                                   | -                     | 2      | 5               | mA    |

| FIN maximum operating frequency               | f <sub>MAX1</sub>    |                                   | 20                    |        | -               | MHz   |

| FIN minimum operating input amplitude         | V <sub>IN1 MIN</sub> | f <sub>FIN</sub> = 20 MHz         | 100                   | -      | -               | mVrms |

| FIN minimum operating frequency               | f <sub>MIN1</sub>    | V <sub>FIN</sub> = 100 mVrms      | -                     | -      | 5               | · MHz |

| XIN maximum operating frequency               | f <sub>MAX2</sub>    | Crystal oscillator                | 12                    | -      | -               | MHz   |

| FIN HIGH-level input current                  | l <sub>IH1</sub>     | $V_{1H} = V_{DD}$                 |                       | -      | 40              | μА    |

| FIN LOW-level input current                   | l <sub>iL1</sub>     | V <sub>IL</sub> = V <sub>SS</sub> | -                     | _      | 40              | μА    |

| XIN HIGH-level input current                  | I <sub>IH2</sub>     | $V_{IH} = V_{DD}$                 | -                     | _      | 20              | μΑ    |

| XIN LOW-level input current                   | 1 <sub>11.2</sub>    | V <sub>IL</sub> = V <sub>SS</sub> | -                     | -      | 20              | μА    |

| CLK, DATA and LE HIGH-level input voltage     | V <sub>IH</sub>      |                                   | 2.0                   | _      | V <sub>DD</sub> | V     |

| CLK, DATA and LE LOW-level input voltage      | V <sub>IL</sub>      |                                   | 0                     | _      | 0.5             | V     |

| AOUT output voltage                           | V <sub>OUT1</sub>    |                                   | -                     | _      | 13              | V     |

| Output voltage (all pins except AOUT)         | V <sub>OUT2</sub>    |                                   | -                     | _      | V <sub>DD</sub> | V     |

| DO HIGH-level output voltage                  | V <sub>OH1</sub>     | I <sub>OH</sub> = 0.5 mA          | V <sub>DD</sub> - 1.0 | -      | -               | v     |

| DO LOW-level output voltage                   | V <sub>OL1</sub>     | I <sub>OL</sub> = 0.5 mA          | -                     | _      | 1.0             | ٧     |

| SYCN and TBN LOW-level output voltage         | V <sub>OL2</sub>     | I <sub>OL</sub> = 0.5 mA          | -                     | _      | 1.0             | V     |

| BDO HIGH-level output voltage                 | V <sub>OH3</sub>     | 1 <sub>OH</sub> = 1.0 mA          | V <sub>DD</sub> - 1.0 | _      | <u> </u>        | ٧     |

| BDO LOW-level output voltage                  | V <sub>OL3</sub>     | I <sub>OL</sub> = 1.0 mA          | -                     |        | 1.0             | V     |

| AOUT LOW-level output voltage                 | V <sub>OL4</sub>     | I <sub>OL</sub> = 1.0 mA          | _                     | _      | 1.0             | V     |

| Parameter                            | Symbol          | Condition                         | Rating |     |     | Unit |

|--------------------------------------|-----------------|-----------------------------------|--------|-----|-----|------|

| raidilletei                          | Symbol          |                                   | min    | typ | max |      |

| DO HIGH-level output leakage current | I <sub>IH</sub> | $V_{OH} = V_{DD}$                 | -      | -   | 0.1 | μА   |

| DO LOW-level output leakage current  | I <sub>IL</sub> | V <sub>OL</sub> = V <sub>SS</sub> | -      | -   | 0.1 | μА   |

<sup>1.</sup>  $f_{FIN}$  = 20 MHz (100 mVrms), 11.16 MHz crystal between XIN and XOUT, all other inputs =  $V_{SS}$ , all outputs open.

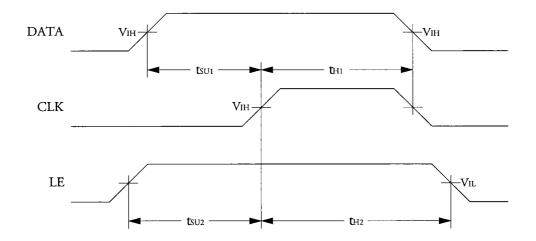

## Input timing characteristics

| Parameter       | Symbol           | Rating <sup>1</sup> | Unit |

|-----------------|------------------|---------------------|------|

| DATA setup time | t <sub>SU1</sub> | ≥ 12                | μs   |

| LE setup time   | t <sub>SU2</sub> | ≥ 12                | μs   |

| DATA hold time  | t <sub>H1</sub>  | ≥ 12                | μs   |

| LE hold time    | t <sub>H2</sub>  | ≥ 12                | μs   |

<sup>1. 11.16</sup> MHz crystal oscillator element. For other crystal oscillator frequencies, multiply the rating shown by (124/f<sub>X'tal</sub>).

## **FUNCTIONAL DESCRIPTION**

## **Input Data**

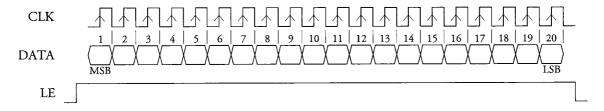

## **Data input timing**

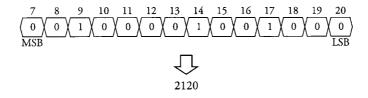

The 20-bit data is input on DATA with the MSB first. The data is input to the shift register on the rising edge of CLK. Accordingly, data changes should occur on the falling edge of CLK.

<sup>2. 11.16</sup> MHz crystal between XIN and XOUT, all other inputs =  $V_{SS}$ , all outputs open.

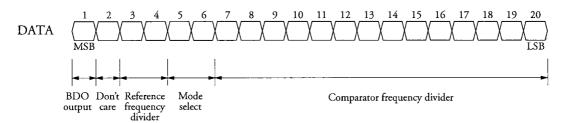

## **Data settings**

The comparator frequency, reference frequency and all other parameters can be set by the 20-bit input data. The 20-bit data has the following structure.

Bit 1 sets the BDO output. BDO is HIGH when this bit is 1. BDO is LOW when this bit is 0.

Bit 2 is not used and has no meaning. It can be set to any state.

Bits 3 and 4 select the reference frequency divider as shown in the following table.

| Bit 3 | Bit 4 | Comparator frequency <sup>1</sup> | Frequency<br>divider ratio |

|-------|-------|-----------------------------------|----------------------------|

| 0     | 0     | 9 kHz                             | 1240                       |

| 1     | 0     | 10 kHz                            | 1116                       |

| 0     | 1     | 1 kHz                             | 11160                      |

| 1     | 1     | 5 kHz                             | 2232                       |

<sup>1. 11.16</sup> MHz crystal oscillator

Bits 5 and 6 select the PLL operating mode as shown in the following table.

|                           | Bit 5 | Bit 6 | BDO                                                      | TBN  |

|---------------------------|-------|-------|----------------------------------------------------------|------|

| Normal mode               | 0     | 0     | Bit 1                                                    | 8 Hz |

| Standby mode <sup>1</sup> | 1     | 0     | Bit 1                                                    | 8 Hz |

| Test mode                 | 0     | 1     | This mode is for IC testing only and should not be used. |      |

| 163t HIUGE                | 1     | 1     |                                                          |      |

1. The feedback resistor is open circuit, so FIN goes HIGH and the N counter operation stops.

Bits 7 to 20 set the comparator frequency divider. Bit 7 is the MSB, and bit 20 is the LSB. An example is shown below.

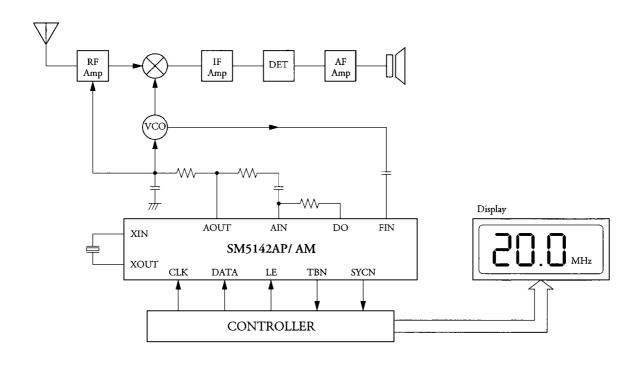

## TYPICAL APPLICATION

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no licence under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

## NIPPON PRECISION CIRCUITS INC.

3-9, Taihei 4-chome Sumida-ku, Tokyo 130, Japan Telephone: 03-5608-5571 Facsimile: 03-5608-5566

NC9414AE 1995.09

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com