### 查询SN65ALS180供应商

## 捷多邦,专业PCB打样**SN65ALS180**出SN75ALS180 DIFFERENTIAL DRIVER AND RECEIVER PAIRS

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

- Meet or Exceed the Requirements of TIA/EIA-422-B, TIA/EIA-485-A<sup>†</sup> and ITU Recommendation V.11

- High-Speed Advanced Low-Power Schottky Circuitry

- Designed for 25-MBaud Operation in Both Serial and Parallel Applications

- Low Skew Between Devices ... 6 ns Max

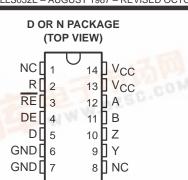

- Individual Driver and Receiver I/O Pins With Dual V<sub>CC</sub> and Dual GND

- Wide Positive and Negative Input/Output Bus Voltage Ranges

- Driver Output Capacity . . . ±60 mA

- Thermal Shutdown Protection

- Driver Positive- and Negative-Current Limiting

- Receiver Input Impedance . . . 12 kΩ Min

- Receiver Input Sensitivity . . . ±200 mV Max

- Receiver Input Hysteresis . . . 60 mV Typ

- Operate From a Single 5-V Supply

- Glitch-Free Power-Up and Power-Down

Protection

#### description

The SN65ALS180 and SN75ALS180 differential driver and receiver pairs are monolithic integrated circuits designed for bidirectional data communication on multipoint bus-transmission lines. They are designed for balanced transmission lines and meet TIA/EIA-422-B, TIA/EIA-485-A, and ITU Recommendation V.11.

The SN65ALS180 and SN75ALS180 combine a 3-state differential line driver and a differential input line receiver, both of which operate from a single 5-V power supply. The driver and receiver have active-high and active-low enables, respectively, that can be externally connected together to function as a direction control. The driver differential outputs and the receiver differential inputs are connected to separate terminals for greater flexibility and are designed to offer minimum loading to the bus when the driver is disabled or  $V_{CC} = 0$ .

These ports feature wide positive and negative common-mode voltage ranges, making the device suitable for party-line applications.

The SN65ALS180 is characterized for operation from -40°C to 85°C. The SN75ALS180 is characterized for operation from 0°C to 70°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> These devices meet or exceed the requirements of TIA/EIA-485-A, except for the Generator Contention Test (para. 3.4.2) and the Generator Current Limit (para. 3.4.3). The applied test voltage ranges are –6 V to 8 V for the SN75ALS180 and –4.5 V to 8 V for the SN65ALS180.

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

### **Function Tables**

| DRIVER |        |      |      |  |  |

|--------|--------|------|------|--|--|

| INPUT  | ENABLE | OUTI | PUTS |  |  |

| D      | DE     | Y    | Z    |  |  |

| Н      | Н      | Н    | L    |  |  |

| L      | Н      | L    | н    |  |  |

| Х      | L      | Z    | Z    |  |  |

#### RECEIVER

| DIFFERENTIAL INPUTS<br>A–B                              | EN <u>AB</u> LE<br>RE | OUTPUT<br>R |

|---------------------------------------------------------|-----------------------|-------------|

| $V_{ID} \ge 0.2 V$                                      | L                     | Н           |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < 0.2 \text{ V}$ | L                     | ?           |

| $V_{ID} \leq -0.2 V$                                    | L                     | L           |

| Х                                                       | н                     | Z           |

| Open                                                    | L                     | н           |

H = high level, L = low level, ? = indeterminate, X = irrelevant, Z = high impedance (off)

## logic symbol<sup>†</sup>

|         | 4 |   |            |                  |    | 1 | 9  |        |

|---------|---|---|------------|------------------|----|---|----|--------|

| DE      | 5 |   | EN1        | $\triangleright$ | 1⊽ |   | 10 | Y<br>- |

|         | 3 | N | EN2        | 1                | 1∇ |   | 12 | 2      |

| RE<br>R | 2 |   | EN2<br>▽ 2 | 7                | Ъ  | 4 | 11 | B      |

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

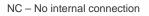

## logic diagram (positive logic)

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

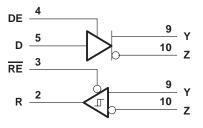

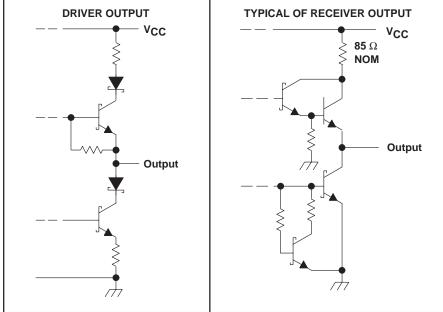

### schematics of inputs and outputs

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub> (see Note 1)                     |                |

|------------------------------------------------------------------|----------------|

| Voltage range at any bus terminal                                |                |

| Enable input voltage, V <sub>I</sub>                             |                |

| Package thermal impedance, $\theta_{JA}$ (see Note 2): D package |                |

| N package                                                        |                |

| Storage temperature range, T <sub>st</sub>                       | –65°C to 150°C |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds     |                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential I/O bus voltage, are with respect to network ground terminal.

2. The package thermal impedance is calculated in accordance with JESD 51, except for through-hole packages, which use a trace length of zero.

### recommended operating conditions

|                                                                                     |               | MIN                                           | NOM | MAX  | UNIT |

|-------------------------------------------------------------------------------------|---------------|-----------------------------------------------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                                                     |               | 4.75                                          | 5   | 5.25 | V    |

| Voltage at any bus terminal (separately or common mode), V <sub>I</sub> or $V_{IC}$ |               |                                               |     | 12   | V    |

| voltage at any bus terminal (separately of common mode), v[ of v[C                  |               |                                               |     | -7   | v    |

| High-level input voltage, V <sub>IH</sub>                                           | D, DE, and RE | 2                                             |     |      | V    |

| Low-level input voltage, VIL                                                        | D, DE, and RE |                                               |     | 0.8  | V    |

| Differential input voltage, VID (see Note 3)                                        |               |                                               |     | ±12  | V    |

| High-level output current, IOH                                                      | Driver        | 7<br>2<br>0.8<br>±12<br>60<br>-400<br>60<br>8 | mA  |      |      |

| nigh-level output current, IOH                                                      | Receiver      |                                               |     | -400 | μA   |

| Low-level output current, IOI                                                       | Driver        |                                               |     | 60   | mA   |

|                                                                                     | Receiver      |                                               |     | 8    | MA   |

| Operating free air temperature. Te                                                  | SN65ALS180    | -40                                           |     | 85   | °C   |

| Operating free-air temperature, T <sub>A</sub>                                      | SN75ALS180    | 0                                             |     | 70   | C    |

NOTE 3: Differential-input/output bus voltage is measured at the noninverting terminal, A/Y, with respect to the inverting terminal, B/Z.

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

## DRIVERS

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature range (unless otherwise noted)

| PARAMETER         |                                                                 | TEST CO                                            | ONDITIONS <sup>†</sup>                       | MIN               | түр‡ | MAX     | UNIT |  |

|-------------------|-----------------------------------------------------------------|----------------------------------------------------|----------------------------------------------|-------------------|------|---------|------|--|

| VIK               | Input clamp voltage                                             | Ij = -18 mA                                        |                                              |                   |      | -1.5    | V    |  |

| VO                | Output voltage                                                  | IO = 0                                             |                                              | 0                 |      | 6       | V    |  |

| VOD1              | Differential output voltage                                     | IO = 0                                             |                                              | 1.5               |      | 6       | V    |  |

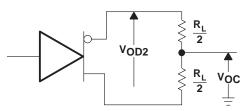

| VOD2              | Differential output voltage                                     | R <sub>L</sub> = 100 Ω,                            | See Figure 1                                 | 1/2 VOD1<br>or 2§ |      |         | V    |  |

|                   |                                                                 | R <sub>L</sub> = 54 Ω,                             | See Figure 1                                 | 1.5               | 2.5  | 5       |      |  |

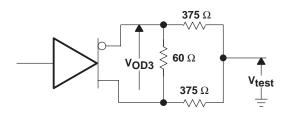

| V <sub>OD3</sub>  | Differential output voltage                                     | $V_{\text{test}} = -7 \text{ V to } 12 \text{ V},$ | See Figure 2                                 | 1.5               |      | 5       | V    |  |

| $\Delta  V_{OD} $ | Change in magnitude of differential output voltage <sup>¶</sup> |                                                    |                                              |                   |      | ±0.2    | V    |  |

| V <sub>OC</sub>   | Common-mode output voltage                                      | R <sub>L</sub> = 54 Ω or 100 Ω,                    | _ = 54 Ω or 100 Ω, See Figure 1              |                   |      | 3<br>–1 | V    |  |

| $\Delta  V_{OC} $ | Change in magnitude of common-mode output voltage¶              |                                                    |                                              |                   |      | ±0.2    | V    |  |

|                   | Output current                                                  | Output disabled,                                   | V <sub>O</sub> = 12 V                        |                   |      | 1       | mA   |  |

| 10                | Output current                                                  | See Note 4                                         | $V_{O} = -7 V$                               |                   |      | -0.8    | ША   |  |

| Iн                | High-level input current                                        | VI = 2.4 V                                         |                                              |                   |      | 20      | μΑ   |  |

| ۱ <sub>IL</sub>   | Low-level input current                                         | V <sub>I</sub> = 0.4 V                             |                                              |                   |      | -400    | μΑ   |  |

|                   |                                                                 | VO = -6 V                                          | SN75ALS180                                   |                   |      | -250    |      |  |

|                   |                                                                 | $V_{O} = -4 V$                                     | SN65ALS180                                   |                   |      | -250    |      |  |

| IOS               | Short-circuit output current#                                   | $V_{O} = 0$                                        | All                                          |                   |      | -150    | mA   |  |

|                   |                                                                 | VO = VCC                                           | All                                          |                   |      |         |      |  |

|                   |                                                                 | V <sub>O</sub> = 8 V                               | All                                          |                   |      |         |      |  |

| ICC               | Supply current                                                  | No load                                            | Driver outputs enabled,<br>Receiver disabled |                   | 25   | 30      | mA   |  |

| -                 |                                                                 |                                                    | Outputs disabled                             |                   | 19   | 26      |      |  |

<sup>†</sup> The power-off measurement in TIA/EIA-422-B applies to disabled outputs only and is not applied to combined inputs and outputs.

<sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

§ The minimum  $V_{OD2}$  with 100- $\Omega$  load is either 1/2  $V_{OD2}$  or 2 V, whichever is greater.

$\int \Delta |V_{OD}|$  and  $\Delta |V_{OC}|$  are the changes in magnitude of  $V_{OD}$  and  $V_{OC}$ , respectively, that occur when the input is changed from a high level to a low level.

<sup>#</sup> Duration of the short circuit should not exceed one second for this test.

NOTE 4: This applies for both power on and off; refer to TIA/EIA-485-A for exact conditions. The TIA/EIA-422-B limit does not apply for a combined driver and receiver terminal.

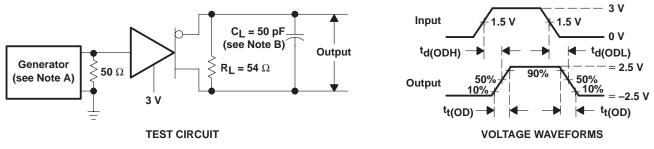

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature

| PARAMETER        |                                                           | TEST CONDITIONS         |                          |              | MIN | TYP‡ | MAX | UNIT |

|------------------|-----------------------------------------------------------|-------------------------|--------------------------|--------------|-----|------|-----|------|

| td(OD)           | Differential output delay time                            |                         |                          |              | 3   | 8    | 13  | ns   |

|                  | Pulse skew $( t_{d(ODH)} - t_{d(ODL)} )$                  | R <sub>L</sub> = 54 Ω,  | $C_{L} = 50 \text{ pF},$ | See Figure 3 |     | 1    | 6   | ns   |

| tt(OD)           | Differential output transition time                       |                         |                          |              | 3   | 8    | 13  | ns   |

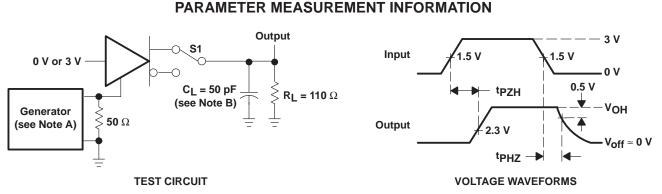

| <sup>t</sup> PZH | Output enable time to high level                          | R <sub>L</sub> = 110 Ω, | See Figure 4             |              |     | 23   | 50  | ns   |

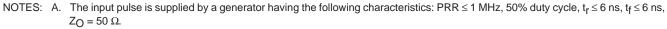

| tPZL             | Output enable time to low level                           | R <sub>L</sub> = 110 Ω, | See Figure 5             |              |     | 19   | 24  | ns   |

| <sup>t</sup> PHZ | Output disable time from high level                       | R <sub>L</sub> = 110 Ω, | See Figure 4             |              |     | 8    | 13  | ns   |

| tPLZ             | Output disable time from low level                        | R <sub>L</sub> = 110 Ω, | See Figure 5             |              |     | 8    | 13  | ns   |

|                  | I values are at $V_{00} = 5 V$ and $T_{4} = 25^{\circ}$ C |                         |                          |              |     |      |     |      |

<sup>‡</sup> All typical values are at V<sub>CC</sub> = 5 V and T<sub>A</sub> = 25°C.

SLLS052E – AUGUST 1987 – REVISED OCTOBER 1998

|                         | SYMBOL EQUIVALENTS                      |                                                    |  |  |  |  |  |  |

|-------------------------|-----------------------------------------|----------------------------------------------------|--|--|--|--|--|--|

| DATA-SHEET<br>PARAMETER | TIA/EIA-422-B                           | TIA/EIA-485-A                                      |  |  |  |  |  |  |

| VO                      | V <sub>oa</sub> , V <sub>ob</sub>       | V <sub>oa</sub> , V <sub>ob</sub>                  |  |  |  |  |  |  |

| VOD1                    | Vo                                      | Vo                                                 |  |  |  |  |  |  |

| IVOD2                   | V <sub>t</sub> (R <sub>L</sub> = 100 Ω) | V <sub>t</sub> (R <sub>L</sub> = 54 Ω)             |  |  |  |  |  |  |

| IVOD3                   |                                         | V <sub>t</sub><br>(test termination measurement 2) |  |  |  |  |  |  |

| V <sub>test</sub>       |                                         | V <sub>tst</sub>                                   |  |  |  |  |  |  |

| $\Delta  V_{OD} $       | $  V_t  -  \overline{V}_t  $            | $  \nabla_t  -  \overline{\nabla}_t  $             |  |  |  |  |  |  |

| V <sub>OC</sub>         | V <sub>os</sub>                         | V <sub>os</sub>                                    |  |  |  |  |  |  |

|                         | $ V_{OS} - \overline{V}_{OS} $          | $ V_{OS} - \overline{V}_{OS} $                     |  |  |  |  |  |  |

| los                     | I <sub>sa</sub>  ,  I <sub>sb</sub>     |                                                    |  |  |  |  |  |  |

| IO                      | I <sub>xa</sub>  ,  I <sub>xb</sub>     | l <sub>ia</sub> , l <sub>ib</sub>                  |  |  |  |  |  |  |

### RECEIVERS

electrical characteristics over recommended ranges of common-mode input voltage, supply voltage, and operating free-air temperature (unless otherwise noted)

|                  | PARAMETER                                                 | TE                          | ST CONDITIONS                                       | MIN   | TYP <sup>†</sup> | MAX  | UNIT |

|------------------|-----------------------------------------------------------|-----------------------------|-----------------------------------------------------|-------|------------------|------|------|

| V <sub>IT+</sub> | Positive-going input threshold voltage                    | V <sub>O</sub> = 2.7 V,     | I <sub>O</sub> = -0.4 mA                            |       |                  | 0.2  | V    |

| VIT-             | Negative-going input threshold voltage                    | V <sub>O</sub> = 0.5 V,     | I <sub>O</sub> = 8 mA                               | -0.2‡ |                  |      | V    |

| V <sub>hys</sub> | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT</sub> –) |                             |                                                     |       | 60               |      | mV   |

| VIK              | Enable-input clamp voltage                                | lj = -18 mA                 |                                                     |       |                  | -1.5 | V    |

| VOH              | High-level output voltage                                 | V <sub>ID</sub> = 200 mV,   | $I_{OH} = -400 \ \mu A$ , See Figure 6              | 2.7   |                  |      | V    |

| VOL              | Low-level output voltage                                  | $V_{ID} = -200 \text{ mV},$ | I <sub>OL</sub> = 8 mA, See Figure 6                |       |                  | 0.45 | V    |

| loz              | High-impedance-state output current                       | $V_{O}$ = 0.4 V to 2.4 V    |                                                     |       |                  | ±20  | μΑ   |

|                  |                                                           | Other input = 0 V,          | VI = 12 V                                           |       |                  | 1    | mA   |

| 1                | Line input current                                        | See Note 5                  | $V_{I} = -7 V$                                      |       |                  | -0.8 | ША   |

| IIН              | High-level enable-input current                           | V <sub>IH</sub> = 2.7 V     |                                                     |       |                  | 20   | μA   |

| ١ <sub>IL</sub>  | Low-level enable-input current                            | V <sub>IL</sub> = 0.4 V     |                                                     |       |                  | -100 | μΑ   |

| ri               | Input resistance                                          |                             |                                                     | 12    |                  |      | kΩ   |

| los              | Short-circuit output current                              | V <sub>ID</sub> = 200 mV,   | $V_{O} = 0$                                         | -15   |                  | -85  | mA   |

| ICC              | Supply current                                            | No load                     | Receiver outputs enabled,<br>Driver inputs disabled |       | 19               | 30   | mA   |

|                  |                                                           |                             | Outputs disabled                                    |       | 19               | 26   |      |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> The algebraic convention, in which the less positive (more negative) limit is designated minimum, is used in this data sheet for common-mode input voltage and threshold voltage levels only.

NOTE 5: This applies for both power on and power off. Refer to TIA/EIA-485-A for exact conditions.

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                                      | TEST COND                                          | ITIONS                  | MIN | TYP† | MAX | UNIT |

|------------------|----------------------------------------------------------------|----------------------------------------------------|-------------------------|-----|------|-----|------|

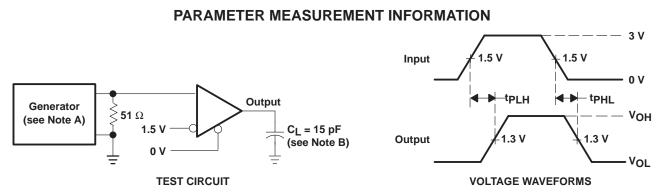

| <sup>t</sup> PLH | Propagation delay time, low- to high-level output              |                                                    |                         | 9   | 14   | 19  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high- to low-level output              | V <sub>ID</sub> = −1.5 V to 1.5 V,<br>See Figure 7 | C <sub>L</sub> = 15 pF, | 9   | 14   | 19  | ns   |

|                  | Skew ( t <sub>PHL</sub> – t <sub>PLH</sub>  )                  |                                                    |                         |     | 2    | 6   | ns   |

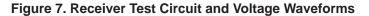

| <sup>t</sup> PZH | Output enable time to high level                               |                                                    | See Figure 8            |     | 7    | 14  | ns   |

| tPZL             | Output enable time to low level                                |                                                    |                         |     | 7    | 14  | ns   |

| <sup>t</sup> PHZ | Output disable time from high level                            | C <sub>L</sub> = 15 pF,                            |                         |     | 20   | 35  | ns   |

| <sup>t</sup> PLZ | Output disable time from low level                             |                                                    |                         |     | 8    | 17  | ns   |

| † All typic      | al values are at V <sub>CC</sub> = 5 V, T <sub>A</sub> = 25°C. |                                                    |                         |     |      |     |      |

PARAMETER MEASUREMENT INFORMATION

Figure 1. Driver  $V_{\mbox{OD}}$  and  $V_{\mbox{OC}}$

Figure 2. Driver VOD3

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>O</sub> = 50  $\Omega$ .

- B.  $C_{L}$  includes probe and jig capacitance.

### Figure 3. Driver Test Circuit and Voltage Waveforms

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

B. CL includes probe and jig capacitance.

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>O</sub> = 50  $\Omega$ .

- B. CL includes probe and jig capacitance.

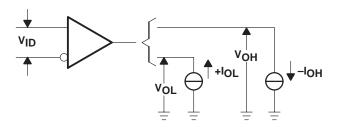

Figure 6. Receiver VOH and VOL

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>r</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>O</sub> = 50  $\Omega$ .

B. CL includes probe and jig capacitance.

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 50% duty cycle, t<sub>f</sub>  $\leq$  6 ns, t<sub>f</sub>  $\leq$  6 ns, Z<sub>O</sub> = 50  $\Omega$ .

B. CL includes probe and jig capacitance.

### Figure 8. Receiver Test Circuit and Voltage Waveforms

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

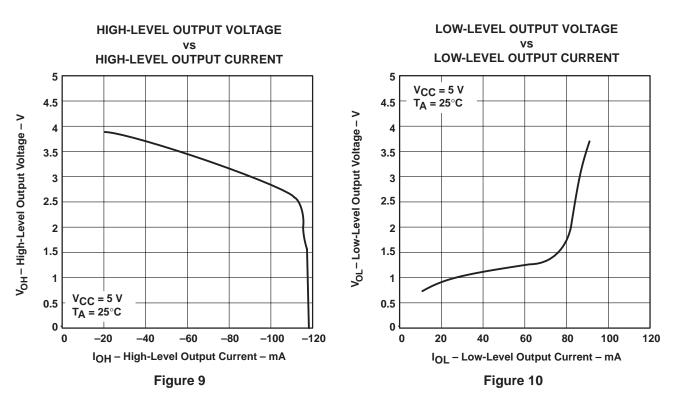

**TYPICAL CHARACTERISTICS – DRIVERS**

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

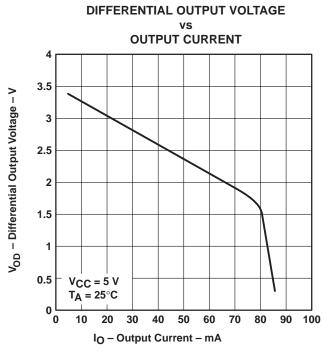

**TYPICAL CHARACTERISTICS – RECEIVERS**

SLLS052E - AUGUST 1987 - REVISED OCTOBER 1998

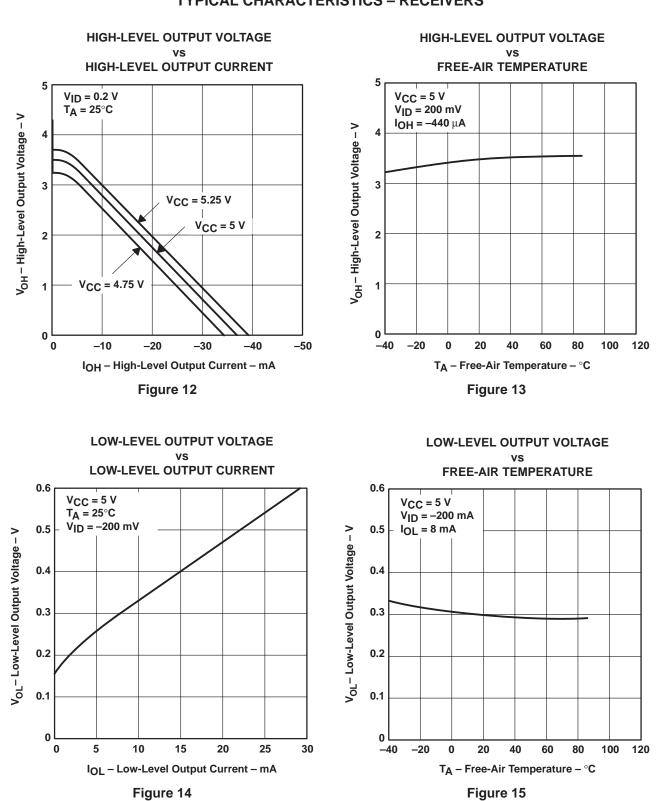

### **TYPICAL CHARACTERISTICS – RECEIVERS**

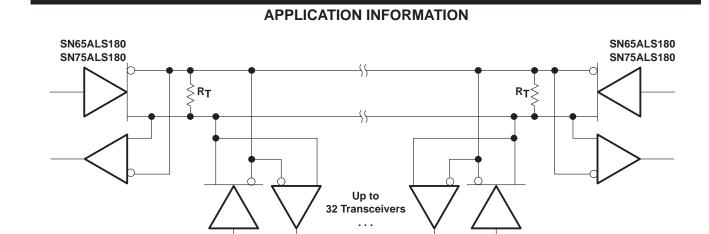

NOTE A: The line should be terminated at both ends in its characteristic impedance (R<sub>T</sub> = Z<sub>O</sub>). Stub lengths off the main line should be kept as short as possible.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated