www.ti.com

### HIGH-SPEED DIFFERENTIAL LINE TRANSCEIVER

#### **FEATURES**

- Low-Voltage Differential Driver and Receiver for Half-Duplex Operation

- Designed for Signaling Rates of 400 Mbit/s

- ESD Protection Exceeds 15 kV on Bus Pins

- Operates From a Single 3.3-V Supply

- Low-Voltage Differential Signaling With Typical Output Voltages of 350 mV and a 50- $\Omega$  Load

- Valid Output With as Little as 50 mV Input Voltage Difference

- Propagation Delay Times

- Driver: 1.7 ns TypReceiver: 3.7 ns Typ

- Power Dissipation at 200 MHz

- Driver: 50 mW TypicalReceiver: 60 mW Typical

- LVTTL Levels Are 5-V Tolerant

- Bus Pins Are High Impedance When Disabled or With V<sub>CC</sub> Less Than 1.5 V

- Open-Circuit Fail-Safe Receiver

- Surface-Mount Packaging

- D Package (SOIC)

- DGK Package (MSOP)

#### SN65LVDM176D (Marked as DM176 or LVM176) SN65LVDM176DGK (Marked as M76)

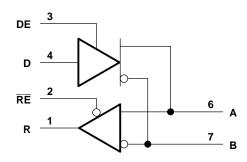

#### logic diagram (positive logic)

#### DESCRIPTION

The SN65LVDM176 is a differential line driver and receiver configured as a transceiver that uses low-voltage differential signaling (LVDS) to achieve signaling rates as high as 400 Mbit/s. These circuits are similar to TIA/EIA-644 standard compliant devices (SN65LVDS) counterparts except that the output current of the drivers is doubled. This modification provides a minimum differential output voltage magnitude of 247 mV into a 50- $\Omega$  load and allows double-terminated lines and half-duplex operation. The receivers detect a voltage difference of less than 50 mV with up to 1 V of ground potential difference between a transmitter and receiver.

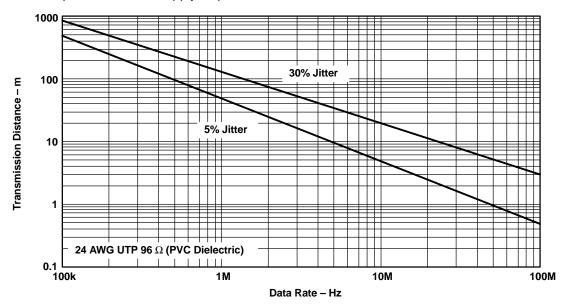

The intended application of this device and signaling technique is for half-duplex or multiplex baseband data transmission over controlled impedance media of approximately  $100-\Omega$  characteristic impedance. The transmission media may be printed-circuit board traces, backplanes, or cables. (Note: The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media, the noise coupling to the environment, and other application specific characteristics).

The SN65LVDM176 is characterized for operation from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **AVAILABLE OPTIONS**

|                | PACK                 | AGE                          |

|----------------|----------------------|------------------------------|

| T <sub>A</sub> | SMALL OUTLINE (D)(1) | MSOP<br>(DGK) <sup>(1)</sup> |

| -40°C to 85°C  | SN65LVDM176D         | SN65LVDM176DGK               |

(1) The D package is available taped and reeled. Add the suffix R to the device type(e.g., SN65LVDM176DR).

#### **FUNCTION TABLES**

#### DRIVER<sup>(1)</sup>

| INPUT ENABLE |    | OUTI | PUTS |

|--------------|----|------|------|

| D            | DE | Α    | В    |

| L            | Н  | L    | Н    |

| Н            | Н  | Н    | L    |

| Open         | Н  | L    | Н    |

| X            | L  | Z    | Z    |

(1) H = high level, L = low level, X = irrelevant, Z = high impedance

#### RECEIVER<sup>(1)</sup>

| DIFFERENTIAL INPUTS V <sub>ID</sub> = V <sub>A</sub> - V <sub>B</sub> | ENABLE<br>RE | OUTPUT<br>R |

|-----------------------------------------------------------------------|--------------|-------------|

| V <sub>ID</sub> ≥ 50 mV                                               | L            | Н           |

| 50 mV < V <sub>ID</sub> < 50 mV                                       | L            | ?           |

| V <sub>ID</sub> ≤ -50 mV                                              | L            | L           |

| Open                                                                  | L            | Н           |

| X                                                                     | Н            | Z           |

(1) H = high level, L = low level, X = irrelevant, Z = high impedance

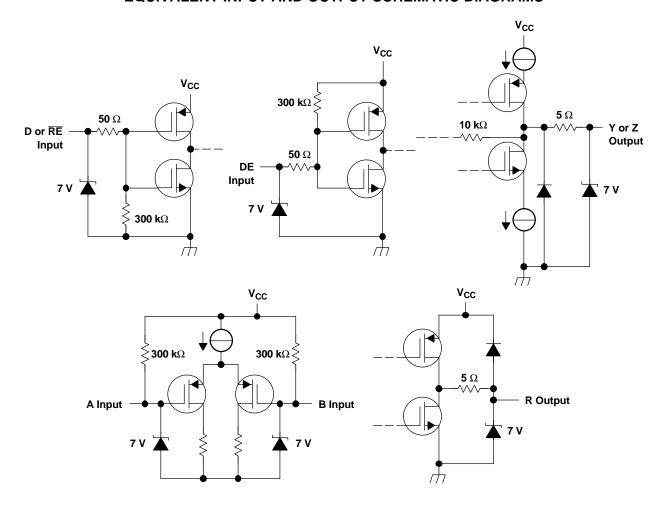

#### **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                          |                              | UNIT                         |

|------------------|------------------------------------------|------------------------------|------------------------------|

| $V_{CC}$         | Supply voltage <sup>(2)</sup>            |                              | –0.5 V to 4 V                |

|                  | Input voltage range                      | D, R, DE, RE                 | –0.5 V to 6 V                |

|                  | Input voltage range                      | A or B                       | –0.5 V to 4 V                |

|                  | Electrostatic discharge                  | A, B, and GND <sup>(3)</sup> | CLass 3, A:15 kV, B:600 V    |

|                  | Electrostatic discriarge                 | All terminals                | Class 3, A:7 kV, B:500 V     |

|                  | Continuous total power dissipation       |                              | See Dissipation Rating Table |

| T <sub>A</sub>   | Operating free-air temperature range     |                              | -40°C to 85°C                |

| T <sub>stg</sub> | Storage temperature range                |                              | -65°C to 150°C               |

|                  | Lead temperature 1,6 mm (1/16 inch) from | n case for 10 seconds        | 260°C                        |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltage values, except differential I/O bus voltage, are with respect to network ground terminal.

<sup>(3)</sup> Tested in accordance with MIL-STD-883C Method 3015.7.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_A \le 25^{\circ}C$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |  |  |

|---------|------------------------------------|------------------------------------------------|---------------------------------------|--|--|

| D       | 725 mW                             | 5.8 mW/°C                                      | 377 mW                                |  |  |

| DGK     | 424 mW                             | 3.4 mW/°C                                      | 220 mW                                |  |  |

#### **RECOMMENDED OPERATING CONDITIONS**

|                 |                                          | MIN                  | NOM | MAX                           | UNIT |

|-----------------|------------------------------------------|----------------------|-----|-------------------------------|------|

| V <sub>CC</sub> | Supply voltage                           | 3                    | 3.3 | 3.6                           | V    |

| V <sub>IH</sub> | High-level input voltage                 | 2                    |     |                               | V    |

| $V_{IL}$        | Low-level input voltage                  |                      |     | 8.0                           | V    |

| V <sub>ID</sub> | Magnitude of differential input voltage  | 0.1                  |     | 0.6                           | V    |

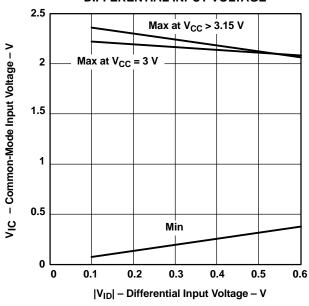

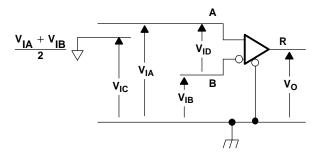

| V <sub>IC</sub> | Common-mode input voltage (see Figure 1) | $\frac{ V_{ID} }{2}$ |     | $\frac{ V_{ID} }{V_{CC}=0.8}$ | V    |

| T <sub>A</sub>  | Operating free-air temperature           | -40                  |     | 85                            | °C   |

# COMMON-MODE INPUT VOLTAGE vs DIFFERENTIAL INPUT VOLTAGE

Figure 1.

#### **DEVICE ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|     | PARAMETER TEST CONDITIONS      |                                                                         | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-----|--------------------------------|-------------------------------------------------------------------------|-----|--------------------|-----|------|

|     |                                | Driver and receiver enabled, no receiver load, driver $R_L = 50 \Omega$ |     | 10                 | 15  |      |

|     | I <sub>CC</sub> Supply current | Driver enabled, receiver disabled, $R_L = 50 \Omega$                    |     | 9                  | 15  | ^    |

| 'CC |                                | Driver disabled, receiver enabled, no load                              |     | 1.8                | 5   | mA   |

|     |                                | Disabled                                                                |     | 0.5                | 2   |      |

(1) All typical values are at 25°C and with a 3.3-V supply.

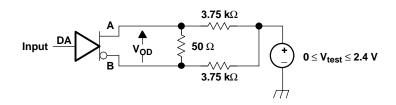

#### **DRIVER ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                                 | PARAMETER                                                      |          | TEST CONDITIONS                          | MIN       | TYP  | MAX       | UNIT |    |

|---------------------------------|----------------------------------------------------------------|----------|------------------------------------------|-----------|------|-----------|------|----|

| V <sub>OD</sub>                 | Differential output voltage magnitude                          |          | D FO O Coo Figure 2                      | 247       | 340  | 454       |      |    |

| $\Delta  V_{OD} $               | Change in differential output voltage magnitude betwee states  | en logic | $R_L$ = 50 Ω, See Figure 2 and Figure 3  | -50       |      | 50        | mV   |    |

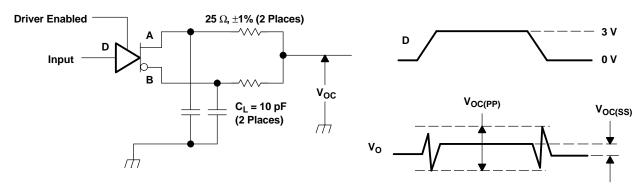

| V <sub>OC(SS)</sub>             | Steady-state common-mode output voltage                        |          |                                          | 1.125     |      | 1.37<br>5 | V    |    |

| $\Delta V_{OC(SS)}$             | Change in steady-state common-mode output voltage logic states | between  | See Figure 4                             | -50       |      | 50        | mV   |    |

| V <sub>OC(PP)</sub>             | Peak-to-peak common-mode output voltage                        |          |                                          |           | 50   | 150       | mV   |    |

|                                 | High-level input current <sup>(1)</sup>                        | DE       | - V <sub>IH</sub> = 5 V                  |           | 0.5  | 10        |      |    |

| I <sub>IH</sub>                 | nigh-level input current(*)                                    | D        | VIH = 2 V                                | VIH - 3 V |      | 2         | 20   | μΑ |

|                                 | Low level input ourrept(1)                                     | DE       | V 0.9.V                                  |           | -0.5 | -10       |      |    |

| I <sub>IL</sub>                 | Low-level input current <sup>(1)</sup>                         | D        | $V_{IL} = 0.8 \text{ V}$                 |           | 2    | 10        | μΑ   |    |

|                                 | Short-circuit output current <sup>(1)</sup>                    |          | V <sub>OA</sub> or V <sub>OB</sub> = 0 V |           |      | -10       | mA   |    |

| Short-circuit output current(1) |                                                                |          | $V_{OD} = 0 V$                           |           |      | -10       | IIIA |    |

| C <sub>I</sub>                  | Input capacitance                                              |          |                                          |           | 3    |           | pF   |    |

<sup>(1)</sup> The non-algebraic convention, where the more positive (least negative) limit is designated maximum, is used in this data sheet for this parameter.

#### RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                           | TEST CONDITIONS                | MIN  | TYP( MAX | UNIT |

|---------------------|-----------------------------------------------------|--------------------------------|------|----------|------|

| V <sub>IT+</sub>    | Positive-going differential input voltage threshold | See Figure 6                   |      | 50       | \/   |

| V <sub>IT</sub> _   | Negative-going differential input voltage threshold |                                | -50  |          | mV   |

| V <sub>OH</sub>     | High-level output voltage                           | $I_{OH} = -8 \text{ mA}$       | 2.4  |          | V    |

| $V_{OL}$            | Low-level output voltage                            | $I_{OL} = 8 \text{ mA}$        |      | 0.4      | V    |

|                     | locut current (A or D inputa)(2)                    | V <sub>I</sub> = 0 V           | -2   | -20      |      |

| ΙΙ                  | Input current (A or B inputs) <sup>(2)</sup>        | V <sub>I</sub> = 2.4 V         | -1.2 |          | μA   |

| I <sub>I(OFF)</sub> | Power-off input current (A or B inputs)             | V <sub>CC</sub> = 0 V or 1.8 V |      | 20       | μΑ   |

| I <sub>IH</sub>     | High-level input current (enables)                  | V <sub>IH</sub> = 5 V          |      | 10       | μΑ   |

| I <sub>IL</sub>     | Low-level input current (enables)                   | V <sub>IL</sub> = 0.8 V        |      | 10       | μA   |

| l <sub>OZ</sub>     | High-impedance output current <sup>(2)</sup>        | V <sub>O</sub> = 0 V or 5 V    |      | ±1       | μΑ   |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

<sup>(2)</sup> The non-algebraic convention, where the more positive (least negative) limit is designated maximum, is used in this data sheet for this parameter.

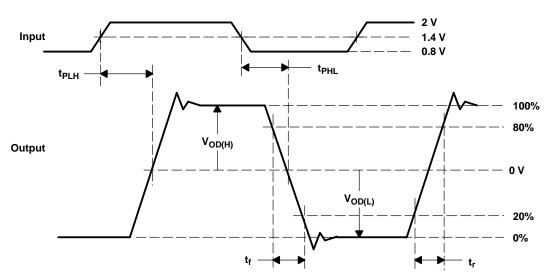

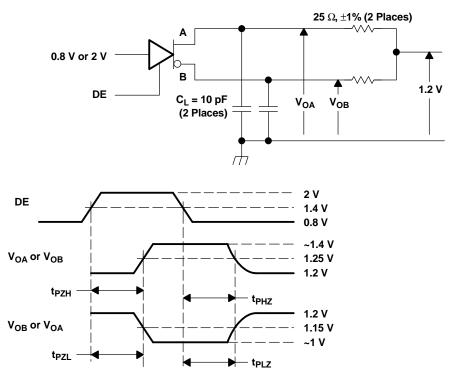

#### DRIVER SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                                   | TEST CONDITIONS                                     | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------|-----|--------------------|-----|------|

| t <sub>PLH</sub>        | Propagation delay time, low-to-high-level output            |                                                     | 0.5 | 1.7                | 2.7 | 20   |

| t <sub>PHL</sub>        | Propagation delay time, high-to-low-level output            |                                                     | 0.5 | 1.7                | 2.7 | ns   |

| t <sub>sk(p)</sub>      | Pulse skew ( t <sub>pHL</sub> - t <sub>pLH</sub>  )         | $R_L = 50 \Omega$ , $C_L = 10 pF$ ,<br>See Figure 3 |     | 0.2                |     | ns   |

| t <sub>r</sub>          | Differential output signal rise time                        | Coo riguro o                                        |     | 0.6                | 1   | 20   |

| t <sub>f</sub>          | Differential output signal fall time                        |                                                     |     | 0.6                | 1   | ns   |

| t <sub>sk(pp)</sub> (2) | Part-to-part skew                                           |                                                     |     |                    | 1   | ns   |

| t <sub>PZH</sub>        | Propagation delay time, high-impedance-to-high-level output |                                                     |     | 8                  | 12  |      |

| t <sub>PZL</sub>        | Propagation delay time, high-impedance-to-low-level output  | Coo Figure 5                                        |     | 7                  | 10  |      |

| t <sub>PHZ</sub>        | Propagation delay time, high-level-to-high-impedance output | See Figure 5                                        |     | 3                  | 10  | ns   |

| t <sub>PLZ</sub>        | Propagation delay time, low-level-to-high-impedance output  |                                                     |     | 4                  | 10  |      |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3 V supply.

#### RECEIVER SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                                   | TEST CONDITIONS                      | MIN | TYP(<br>1) | MAX | UNIT |

|-------------------------|-------------------------------------------------------------|--------------------------------------|-----|------------|-----|------|

| t <sub>PLH</sub>        | Propagation delay time, low-to-high-level output            |                                      | 2.3 | 3.7        | 4.5 |      |

| t <sub>PHL</sub>        | Propagation delay time, high-to-low-level output            |                                      | 2.3 | 3.7        | 4.5 | ns   |

| t <sub>sk(p)</sub>      | Pulse skew ( t <sub>pHL</sub> t <sub>pLH</sub>  )           | C <sub>L</sub> = 10 pF, See Figure 7 |     | 0.4        |     |      |

| t <sub>r</sub>          | Output signal rise time                                     |                                      |     | 0.8        | 1.5 | 20   |

| t <sub>f</sub>          | Output signal fall time                                     |                                      |     | 0.8        | 1.5 | ns   |

| t <sub>sk(pp)</sub> (2) | Part-to-part skew                                           |                                      |     |            | 1   | ns   |

| t <sub>PZH</sub>        | Propagation delay time, high-level-to-high-impedance output |                                      |     | 3          | 10  |      |

| t <sub>PZL</sub>        | Propagation delay time, low-level-to-low-impedance output   | Soo Figure 9                         |     | 3          | 10  | 20   |

| t <sub>PHZ</sub>        | Propagation delay time, high-impedance-to-high-level output | See Figure 8                         |     | 4          | 10  | ns   |

| t <sub>PLZ</sub>        | Propagation delay time, low-impedance-to-high-level output  |                                      |     | 6          | 10  |      |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

#### PARAMETER MEASUREMENT INFORMATION

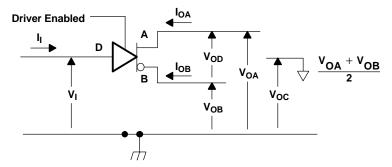

#### **DRIVER**

Figure 2. Driver Voltage and Current Definitions

<sup>(2)</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

<sup>(2)</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

#### PARAMETER MEASUREMENT INFORMATION (continued)

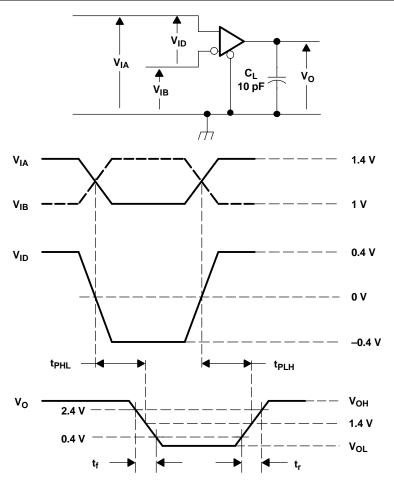

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10 ± 0.2 ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 3. Test Circuit, Timing, and Voltage Definitions for the Differential Output Signal

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width =  $500 \pm 10$  ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T. The measurement of  $V_{OC(PP)}$  is made on test equipment with a -3 dB bandwidth of at least 300 MHz.

Figure 4. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

#### PARAMETER MEASUREMENT INFORMATION (continued)

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width = 500  $\pm$  10 ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 5. Enable and Disable Time Circuit and Definitions

#### **RECEIVER**

Figure 6. Receiver Voltage Definitions

| APPLIED VOLTAGES<br>(V) |                 | RESULTING DIFFERENTIAL<br>INPUT VOLTAGE<br>(mV) | RESULTING COMMON-<br>MODE INPUT VOLTAGE<br>(V) |  |  |

|-------------------------|-----------------|-------------------------------------------------|------------------------------------------------|--|--|

| V <sub>IA</sub>         | V <sub>IB</sub> | V <sub>ID</sub>                                 | V <sub>IC</sub>                                |  |  |

| 1.225                   | 1.175           | 50                                              | 1.2                                            |  |  |

| 1.175                   | 1.225           | -50                                             | 1.2                                            |  |  |

| 2.41                    | 2.36            | 50                                              | 2.385                                          |  |  |

| 2.36                    | 2.41            | -50                                             | 2.385                                          |  |  |

| 0.05                    | 0               | 50                                              | 0.025                                          |  |  |

| 0                       | 0.05            | -50                                             | 0.025                                          |  |  |

| 1.5                     | 0.9             | 600                                             | 1.2                                            |  |  |

| 0.9                     | 1.5             | -600                                            | 1.2                                            |  |  |

| 2.4                     | 1.8             | 600                                             | 2.1                                            |  |  |

| 1.8                     | 2.4             | -600                                            | 2.1                                            |  |  |

| 0.6                     | 0               | 600                                             | 0.3                                            |  |  |

| 0                       | 0.6             | -600                                            | 0.3                                            |  |  |

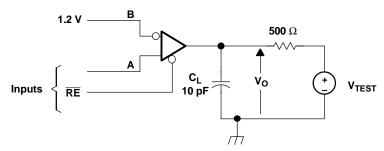

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10 ± 0.2 ns.  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 7. Timing Test Circuit and Waveforms

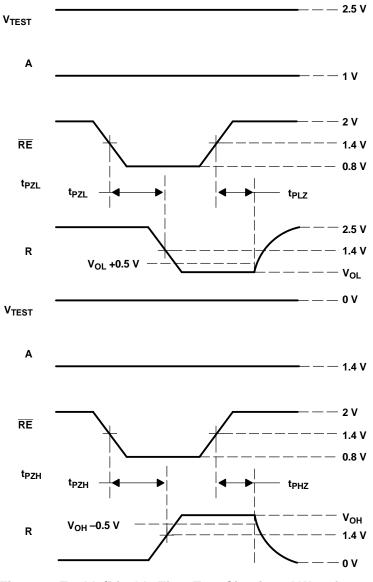

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width = 5000  $\pm$  10 ns.  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 8. Enable/Disable Time Test Circuit and Waveforms

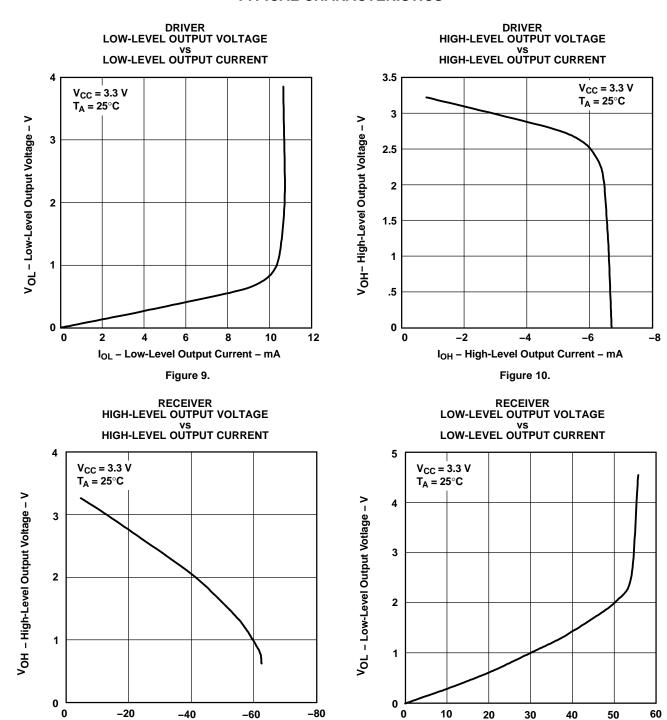

#### TYPICAL CHARACTERISTICS

I<sub>OL</sub> – Low-Level Output Current – mA

Figure 12.

I<sub>OH</sub> – High-Level Output Current – mA

Figure 11.

#### **TYPICAL CHARACTERISTICS (continued)**

Figure 13.

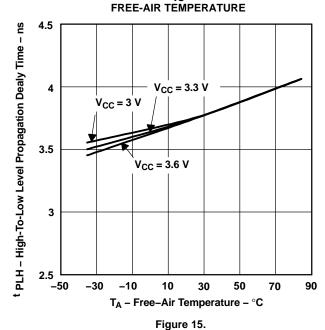

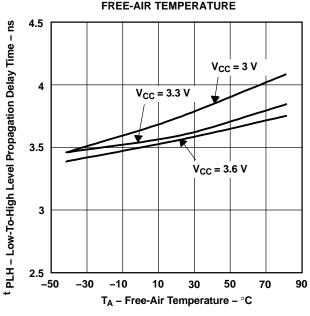

## RECEIVER HIGH-TO-LOW LEVEL PROPAGATION DELAY TIME vs

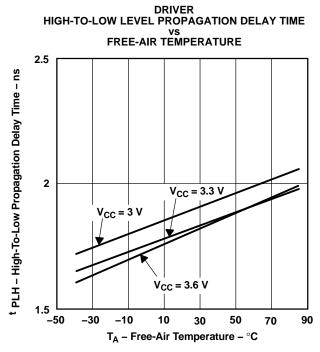

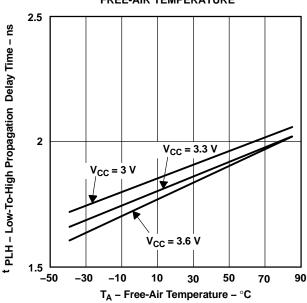

DRIVER

LOW-TO-HIGH LEVEL PROPAGATION DELAY TIME

vs

FREE-AIR TEMPERATURE

Figure 14.

#### RECEIVER LOW-TO-HIGH LEVEL PROPAGATION DELAY TIME vs FREE-AIR TEMPERATURE

Figure 16.

#### **APPLICATION INFORMATION**

The devices are generally used as building blocks for high-speed point-to-point data transmission. Ground differences are less than 1 V with a low common-mode output and balanced interface for very low noise emissions. Devices can interoperate with RS-422, PECL, and IEEE-P1596. Drivers/receivers maintain ECL speeds without the power and dual supply requirements.

Figure 17. Data Transmission Distance Versus Rate

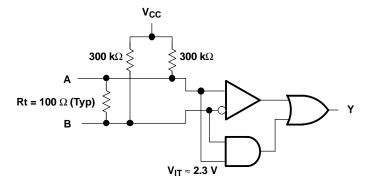

#### **FAIL SAFE**

One of the most common problems with differential signaling applications is how the system responds when no differential voltage is present on the signal pair. The LVDS receiver is like most differential line receivers, in that its output logic state can be indeterminate when the differential input voltage is between –50 mV and 50 mV and within its recommended input common-mode voltage range. TI's LVDS receiver is different in how it handles the open-input circuit situation, however.

Open-circuit means that there is little or no input current to the receiver from the data line itself. This could be when the driver is in a high-impedance state or the cable is disconnected. When this occurs, the LVDS receiver will pull each line of the signal pair to near  $V_{CC}$  through 300-k $\Omega$  resistors as shown in Figure 18. The fail-safe feature uses an AND gate with input voltage thresholds at about 2.3 V to detect this condition and force the output to a high-level regardless of the differential input voltage.

Figure 18. Open-Circuit Fail Safe of the LVDS Receiver

#### **APPLICATION INFORMATION (continued)**

It is only under these conditions that the output of the receiver will be valid with less than a 50-mV differential input voltage magnitude. The presence of the termination resistor, Rt, does not affect the fail-safe function as long as it is connected as shown in the figure. Other termination circuits may allow a dc current to ground that could defeat the pullup currents from the receiver and the fail-safe feature.

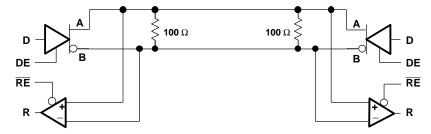

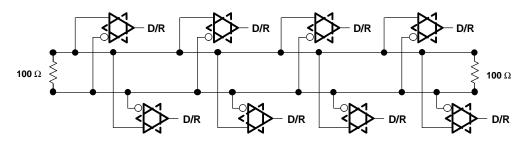

**Bidirectional Half-Duplex Applications**

**Multipoint Bus Applications**

Note A: Keep drivers and receivers as close to the LVDS bus side connector as possible.

Figure 19. Bidirectional Half-Duplex and Multipoint Bus Applications

ti.com 18-Jul-2006

#### PACKAGING INFORMATION

| Orderable Device  | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|-------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| SN65LVDM176D      | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DG4    | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DGK    | ACTIVE                | MSOP            | DGK                | 8    | 80             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DGKG4  | ACTIVE                | MSOP            | DGK                | 8    | 80             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DGKR   | ACTIVE                | MSOP            | DGK                | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DGKRG4 | ACTIVE                | MSOP            | DGK                | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DR     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDM176DRG4   | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

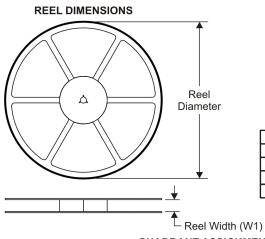

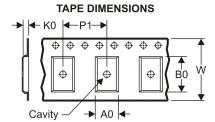

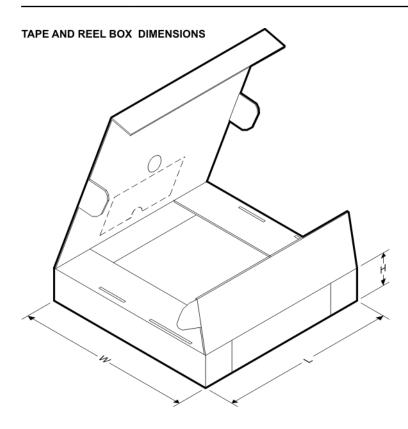

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

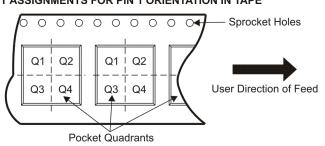

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| SN65LVDM176DGKR | MSOP            | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| SN65LVDM176DR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65LVDM176DGKR | MSOP         | DGK             | 8    | 2500 | 358.0       | 335.0      | 35.0        |

| SN65LVDM176DR   | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated