## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC™ FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

- 512 × 18-Bit Organization Array (SN74V215)

- 1024 × 18-Bit Organization Array (SN74V225)

- 2048 × 18-Bit Organization Array (SN74V235)

- 4096 × 18-Bit Organization Array (SN74V245)

- 7.5-ns Read/Write Cycle Time

- 3.3-V V<sub>CC</sub>, 5-V Input Tolerant

- First-Word or Standard Fall-Through Timing

- Single or Double Register-Buffered Empty and Full Flags

- Easily Expandable in Depth and Width

- Asynchronous or Coincident Read and Write Clocks

- Asynchronous or Synchronous Programmable Almost-Empty and Almost-Full Flags With Default Settings

- Half-Full Flag Capability

- Output Enable Puts Output Data Bus in High-Impedance State

- High-Performance Submicron CMOS

Technology

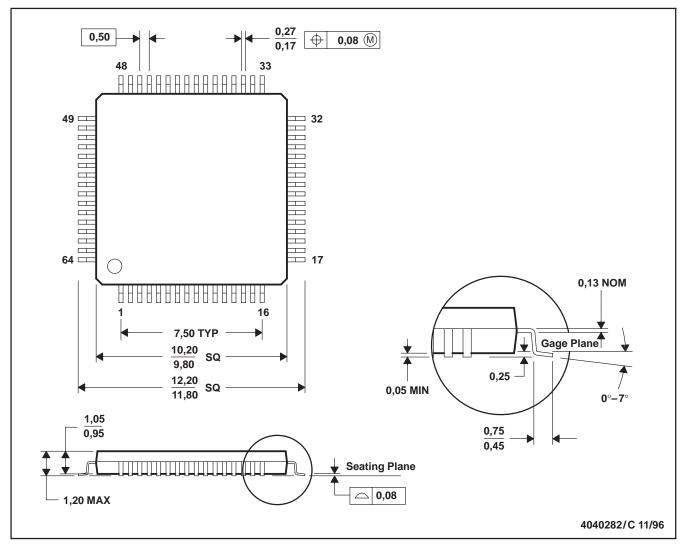

- Packaged in 64-Pin Thin Quad Flat Package

- DSP and Microprocessor Interface Control Logic

- Provide a DSP Glueless Interface to Texas Instruments TMS320<sup>™</sup> DSPs

#### description

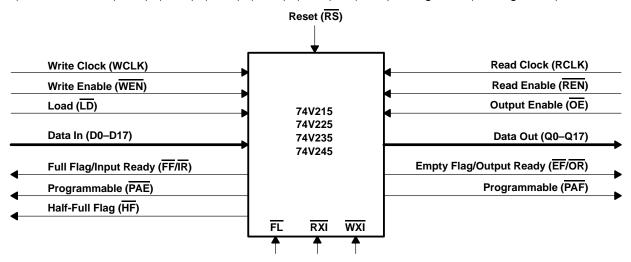

The SN74V215, SN74V225, SN74V235, and SN74V245 are very high-speed, low-power CMOS clocked first-in first-out (FIFO) memories. They support clock frequencies up to 133 MHz and have read-access times as fast as 5 ns. These DSP-Sync<sup>™</sup> FIFO memories feature read and write controls for use in applications such as DSP-to-processor communication, DSP-to-analog front end (AFE) buffering, network, video, and data communications.

These are synchronous FIFOs, which means each port employs a synchronous interface. All data transfers through a port are gated to the low-to-high transition of a continuous (free-running) port clock by enable signals. The continuous clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple interface between DSPs, microprocessors, and/or buses controlled by a synchronous interface. An output-enable ( $\overline{OE}$ ) input controls the 3-state output.

The synchronous FIFOs have two fixed flags, empty flag/output ready ( $\overline{EF}/\overline{OR}$ ) and full flag/input ready ( $\overline{FF}/\overline{IR}$ ), and two programmable flags, almost-empty ( $\overline{PAE}$ ) and almost-full ( $\overline{PAF}$ ). The offset loading of the programmable flags is controlled by a simple state machine, and is initiated by asserting the load pin ( $\overline{LD}$ ). A half-full flag ( $\overline{HF}$ ) is available when the FIFO is used in a single-device configuration.

Two timing modes of operation are possible with these devices: first-word fall-through (FWFT) mode and standard mode.

In FWFT mode, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. A read enable (REN) does not have to be asserted for accessing the first word.

In standard mode, the first word written to an empty FIFO does not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating  $\overline{\text{REN}}$  and enabling a rising RCLK edge, shifts the word from internal memory to the data output lines.

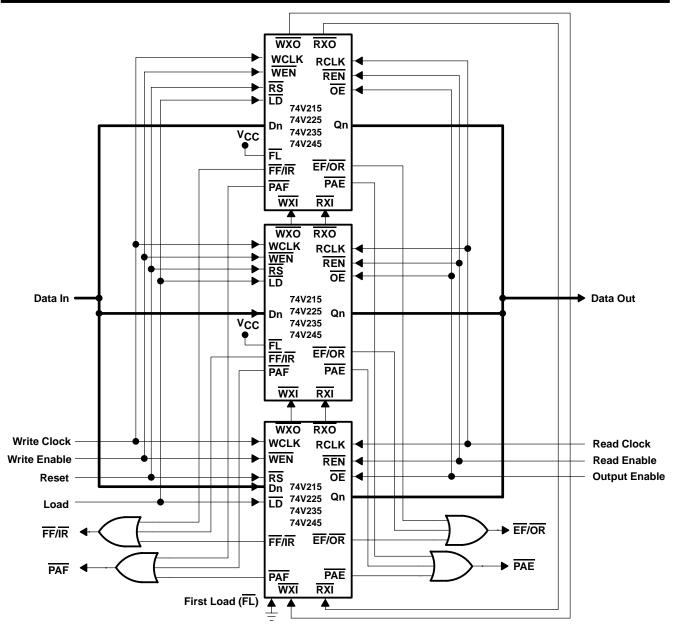

These devices are depth expandable, using a daisy-chain technique or FWFT mode. The  $\overline{XI}$  and  $\overline{XO}$  pins are used to expand the FIFOs. In depth-expansion configuration, first load ( $\overline{FL}$ ) is grounded on the first device and set to high for all other devices in the daisy chain.

The SN74V215, SN74V225, SN74V235, and SN74V245 are characterized for operation from 0°C to 70°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DSP-SYNC and TMS320 are trademarks of Texas Instruments.

Copyright © 2002, Texas Instruments Incorporated

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

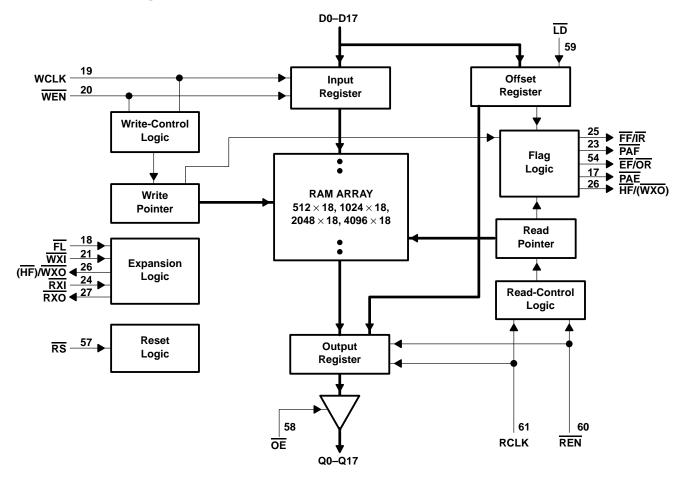

functional block diagram

# SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>TM</sup> FIRST-IN, FIRST-OUT MEMORIES SCAS636E – APRIL 2000 – REVISED SEPTEMBER 2002

## **Terminal Functions**

| TER    | MINAL                                                                        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.                                                                          | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D0D17  | 1–16, 63,<br>64                                                              | I   | Data inputs. Data inputs for an 18-bit bus.                                                                                                                                                                                                                                                                                                                                                                                                              |

| EF/OR  | 54                                                                           | о   | Memory-empty/valid-data-available flag. In the standard mode, the EF function is selected. EF indicates whether the FIFO memory is empty. In FWFT mode, the OR function is selected. OR indicates whether there is valid data available at the outputs.                                                                                                                                                                                                  |

| FF/IR  | 25                                                                           | 0   | Memory-full/space-available flag. In the standard mode, the FF function is selected. FF indicates whether the FIFO memory is full. In the FWFT mode, the IR function is selected. IR indicates whether there is space available for writing to the FIFO memory.                                                                                                                                                                                          |

| FL     | 18                                                                           | I   | Mode selection. In the single-device or width-expansion configuration, FL, together with WXI and RXI,<br>determines if the mode is standard mode or first-word fall-through (FWFT) mode, as well as whether the<br>PAE/PAF flags are synchronous or asynchronous (see Table 4). In the daisy-chain depth-expansion<br>configuration, FL is grounded on the first device (first-load device) and set to high for all other devices in<br>the daisy chain. |

| GND    | 30, 35, 40,<br>46, 51, 55,<br>62                                             |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LD     | 59                                                                           | I   | Read/write control. When LD is low, data on the inputs D0–D11 is written to the offset and depth registers on the low-to-high transition of the WCLK, when WEN is low. When LD is low, data on the outputs Q0–Q11 is read from the offset and depth registers on the low-to-high transition of RCLK when REN is low.                                                                                                                                     |

| OE     | 58                                                                           | I   | Output enable. When $\overline{OE}$ is low, the data output bus is active. If $\overline{OE}$ is high, the output data bus is in the high-impedance state.                                                                                                                                                                                                                                                                                               |

| PAE    | 17                                                                           | ο   | Programable almost-empty flag. When PAE is low, the FIFO is almost empty, based on the offset programmed into the FIFO. The default offset at reset is 63 from empty for SN74V215, and 127 from empty for SN74V225, SN74V235, and SN74V245.                                                                                                                                                                                                              |

| PAF    | 23                                                                           | 0   | Programable almost-full flag. When PAF is low, the FIFO is almost full, based on the offset programmed into the FIFO. The default offset at reset is 63 from full for SN74V215, and 127 from full for SN74V225, SN74V235, and SN74V245.                                                                                                                                                                                                                  |

| Q0–Q17 | 28, 29, 31,<br>32, 34,<br>36–39, 41,<br>42, 44, 45,<br>47, 48, 50,<br>52, 53 | ο   | Data outputs. Data outputs for an 18-bit bus.                                                                                                                                                                                                                                                                                                                                                                                                            |

| RCLK   | 61                                                                           | I   | Read clock. When $\overline{\text{REN}}$ is low, data is read from the FIFO on a low-to-high transition of RCLK, if the FIFO is not empty.                                                                                                                                                                                                                                                                                                               |

| REN    | 60                                                                           | I   | Read enable. When REN is low, data is read from the FIFO on every low-to-high transition of RCLK. When REN is high, the output register holds the previous data. Data is not read from the FIFO if EF is low.                                                                                                                                                                                                                                            |

| RS     | 57                                                                           | I   | Reset. When $\overline{RS}$ is set low, internal read and write pointers are set to the first location of the RAM array, $\overline{FF}$ and $\overline{PAF}$ go high, and $\overline{PAE}$ and $\overline{EF}$ go low. A reset is required before an initial write after power up.                                                                                                                                                                      |

| RXI    | 24                                                                           | I   | Read expansion. In the single-device or width-expansion configuration, RXI, together with FL and WXI, determines if the mode is standard mode or FWFT mode, as well as whether the PAE/PAF flags are synchronous or asynchronous (see Table 4). In the daisy-chain depth-expansion configuration, RXI is connected to RXO (read expansion out) of the previous device.                                                                                   |

| RXO    | 27                                                                           | 0   | Last-location-read flag. In the depth-expansion configuration, a pulse is sent from $\overline{\text{RXO}}$ to $\overline{\text{RXI}}$ of the next device when the last location in the FIFO is read.                                                                                                                                                                                                                                                    |

| VCC    | 22, 33, 43,<br>49, 56                                                        |     | Supply voltage. +3.3-V power-supply pins.                                                                                                                                                                                                                                                                                                                                                                                                                |

| WCLK   | 19                                                                           | I   | Write clock. When $\overline{\text{WEN}}$ is low, data is written into the FIFO on a low-to-high transition of WCLK if the FIFO is not full.                                                                                                                                                                                                                                                                                                             |

## **Terminal Functions (Continued)**

| TERMINAL |          | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME     | NO.      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| WEN      | 20       | I   | Write enable. When $\overline{\text{WEN}}$ is low, data is written into the FIFO on every low-to-high transition of WCLK. When $\overline{\text{WEN}}$ is high, the FIFO holds the previous data. Data is not written into the FIFO if $\overline{\text{FF}}$ is low.                                                                                                    |  |  |  |  |  |

| WXI      | WXI 21 I |     | Width expansion. In the single-device or width-expansion configuration, WXI, together with FL and RXI, determines if the mode is standard mode or FWFT mode, as well as whether the PAE/PAF flags are synchronous or asynchronous (see Table 4). In the daisy-chain depth-expansion configuration, WXI is connected to WXO (write expansion out) of the previous device. |  |  |  |  |  |

| WXO/HF   | 26       | ο   | Half-full flag. In the single-device or width-expansion configuration, the device is more than half full when $\overline{\text{HF}}$ is low. In the depth-expansion configuration, a pulse is sent from $\overline{\text{WXO}}$ to $\overline{\text{WXI}}$ of the next device when the last location in the FIFO is written.                                             |  |  |  |  |  |

## detailed description

## INPUTS:

## DATA IN (D0-D17)

Data inputs for 18-bit-wide data.

## CONTROLS:

## RESET (RS)

Reset is accomplished when  $\overline{\text{RS}}$  is taken low. During reset, both internal read and write pointers are set to the first location. A reset is required after power up before a write operation can take place. The half-full flag ( $\overline{\text{HF}}$ ) and programmable almost-full flag ( $\overline{\text{PAF}}$ ) is reset to high after t<sub>RSF</sub>. The programmable almost-empty flag ( $\overline{\text{PAE}}$ ) is reset to high. The empty flag ( $\overline{\text{EF}}$ ) resets to low in standard mode, but resets to high in FWFT mode. During reset, the output register is initialized to all zeros, and the offset registers are initialized to their default values.

#### WRITE CLOCK (WCLK)

A write cycle is initiated on the low-to-high transition of WCLK. Data setup and hold times must be met with respect to the low-to-high transition of WCLK.

The write and read clocks can be asynchronous or coincident.

## WRITE ENABLE (WEN)

When WEN is low, data can be loaded into the FIFO RAM array on the rising edge of every WCLK cycle if the device is not full. Data is stored in the RAM array sequentially and independently of any ongoing read operation.

When  $\overline{\text{WEN}}$  is high, no new data is written in the RAM array on each WCLK cycle.

To prevent data overflow in the standard mode, FF goes low, inhibiting further write operations. Upon completion of a valid read cycle, FF goes high, allowing a write to occur. The FF flag is updated on the rising edge of WCLK.

To prevent data overflow in the FWFT mode,  $\overline{IR}$  goes high, inhibiting further write operations. Upon completion of a valid read cycle,  $\overline{IR}$  goes low, allowing a write to occur. The  $\overline{IR}$  flag is updated on the rising edge of WCLK.

WEN is ignored when the FIFO is full in either FWFT or standard mode.

## READ CLOCK (RCLK)

Data can be read on the outputs on the low-to-high transition of RCLK when  $\overline{OE}$  is low.

The write and read clocks can be asynchronous or coincident.

SCAS636E – APRIL 2000 – REVISED SEPTEMBER 2

## detailed description (continued)

#### READ ENABLE (REN)

When REN is low, data is loaded from the RAM array into the output register on the rising edge of every RCLK cycle if the device is not empty.

When REN is high, the output register holds the previous data and no new data is loaded into the output register. Data outputs Q0–Qn maintain the previous data value.

In the standard mode, every word accessed at Qn, including the first word written to an empty FIFO, must be requested using  $\overline{\text{REN}}$ . When the last word has been read from the FIFO, the empty flag ( $\overline{\text{EF}}$ ) goes low, inhibiting further read operations. REN is ignored when the FIFO is empty. After a write is performed,  $\overline{\text{EF}}$  goes high, allowing a read to occur. The  $\overline{\text{EF}}$  flag is updated on the rising edge of RCLK.

In the FWFT mode, the first word written to an empty FIFO automatically goes to the outputs Qn, on the third valid low-to-high transition of RCLK + t<sub>SKEW</sub> after the first write. REN need not be asserted low. To access all other words, a read must be executed using REN. The RCLK low-to-high transition after the last word has been read from the FIFO, output ready (OR) goes high with a true read (RCLK with REN low), inhibiting further read operations. REN is ignored when the FIFO is empty.

## OUTPUT ENABLE (OE)

When  $\overline{OE}$  is low, the parallel output buffers transmit data from the output register. When  $\overline{OE}$  is high, the Q-output data bus is in the high-impedance state.

## $LOAD(\overline{LD})$

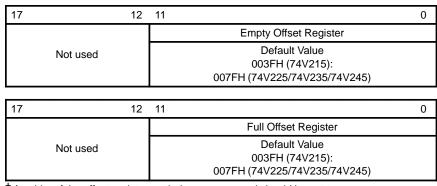

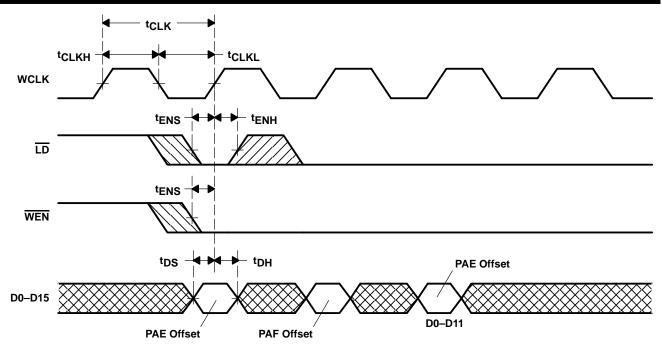

The SN74V215, SN74V225, SN74V235, and SN74V245 devices contain two 12-bit offset registers with data on the inputs, or read on the outputs. When  $\overline{\text{LD}}$  is low and  $\overline{\text{WEN}}$  is low, data on the inputs D0–D11 is written into the empty offset register on the first low-to-high transition of the write clock (WCLK). When  $\overline{\text{LD}}$  and  $\overline{\text{WEN}}$  are held low, data is written into the full offset register on the second low-to-high transition of WCLK (see Tables 1 and 2). The third transition of WCLK again writes to the empty-offset register.

However, writing to all offset registers need not occur at one time. One or two offset registers can be written and then, by bringing  $\overline{LD}$  high, the FIFO is returned to normal read/write operation. When  $\overline{LD}$  is low, and  $\overline{WEN}$  is low, the next offset register in sequence is written.

| LD | WEN | WCLK       | SELECTION <sup>†</sup>                                      |

|----|-----|------------|-------------------------------------------------------------|

| L  | L   | ↑          | Writing to offset registers:<br>Empty offset<br>Full offset |

| L  | Н   | $\uparrow$ | No operation                                                |

| Н  | L   | $\uparrow$ | Write into FIFO                                             |

| н  | Н   | $\uparrow$ | No operation                                                |

## Table 1. Writing to Offset Registers

<sup>†</sup> The same selection sequence applies to reading from the registers. REN is enabled and read is performed on the low-to-high transition of RCLK.

## detailed description (continued)

#### Table 2. Offset Register Location and Default Values<sup>†</sup>

<sup>†</sup> Any bits of the offset register not being programmed should be set to zero.

When LD is low and WEN is high, the WCLK input is disabled; then, a signal at this input can neither increment the write-offset-register pointer, nor execute a write.

The contents of the offset registers can be read on the output lines when LD is low and REN is low; then, data can be read on the low-to-high transition of RCLK. Reading the control registers employs a dedicated read-offset-register pointer. (The read and write pointers operate independently.) Offset register content can be read out in the standard mode only. It is inhibited in the FWFT mode.

A read from and a write to the offset registers should not be performed simultaneously.

## FIRST LOAD (FL)

For the single-device mode, see Table 5 for additional information. In the daisy-chain depth-expansion configuration,  $\overline{FL}$  is grounded to indicate it is the first device loaded and is set high for all other devices in the daisy chain (see *Operating Configurations* for further details).

## WRITE EXPANSION INPUT (WXI)

This is a dual-purpose pin. For single-device mode, see Table 5 for additional information.  $\overline{WXI}$  is connected to write expansion out ( $\overline{WXO}$ ) of the previous device in the daisy-chain depth-expansion mode.

## READ EXPANSION INPUT (RXI)

This is a dual-purpose pin. For single-device mode, see Table 5 for additional information.  $\overline{RXI}$  is connected to read expansion out ( $\overline{RXO}$ ) of the previous device in the daisy-chain depth-expansion mode.

## OUTPUTS:

## FULL FLAG/INPUT READY (FF/IR)

This is a dual-purpose pin. In FWFT mode, the input ready ( $\overline{IR}$ ) function is selected.  $\overline{IR}$  goes low when memory space is available for writing data. When there is no free space left,  $\overline{IR}$  goes high, inhibiting further write operations.

In standard mode, the  $\overline{FF}$  function is selected. When the FIFO is full,  $\overline{FF}$  goes low, inhibiting further write operations. When  $\overline{FF}$  is high, the FIFO is not full. If no reads are performed after a reset,  $\overline{FF}$  goes low after D writes to the FIFO. D = 512 for the SN74V215, 1024 for the SN74V225, 2048 for the SN74V235, and 4096 for the SN74V245.

$\overline{IR}$  goes high after D writes to the FIFO. D = 513 for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235, and 4097 for the SN74V245. The additional word in FWFT mode is due to the capacity of the memory plus output register.

FF/IR is synchronous and updated on the rising edge of WCLK.

## detailed description (continued)

## EMPTY FLAG/OUTPUT READY (EF/OR)

This is a dual-purpose pin. In FWFT mode, the  $\overline{OR}$  function is selected.  $\overline{OR}$  goes low at the same time the first word written to an empty FIFO appears valid on the outputs.  $\overline{OR}$  stays low after the RCLK low-to-high transition that shifts the last word from the FIFO memory to the outputs.  $\overline{OR}$  goes high only with a true read (RCLK with  $\overline{REN}$  low). The previous data stays at the outputs, indicating that the last word was read. Further data reads are inhibited until  $\overline{OR}$  goes low again.

In the standard mode, the  $\overline{EF}$  function is selected. When the FIFO is empty,  $\overline{EF}$  goes low, inhibiting further read operations. When  $\overline{EF}$  is high, the FIFO is not empty.

EF/OR is synchronous and updated on the rising edge of RCLK.

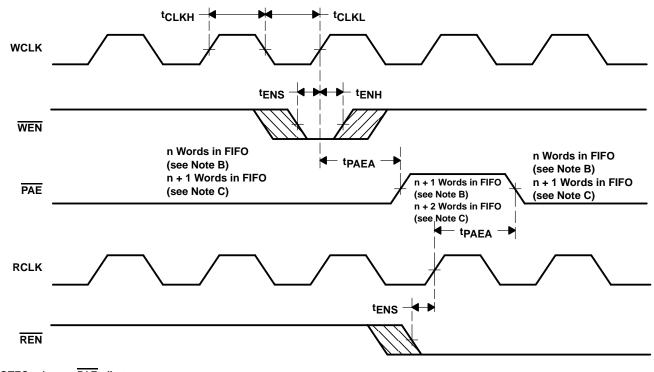

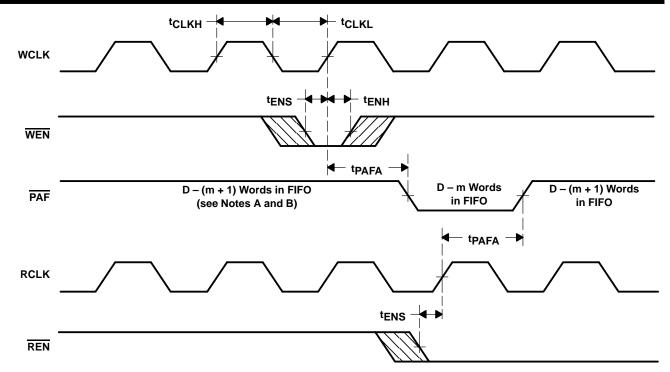

## PROGRAMMABLE ALMOST-FULL FLAG (PAF)

PAF goes low when the FIFO reaches the almost-full condition. In FWFT mode, if no reads are performed, PAF goes low after 513 – m for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235, and 4097 for the SN74V245. Default values for m are in Table 3 and Table 4.

In standard mode, if no reads are performed after reset ( $\overline{RS}$ ),  $\overline{PAF}$  goes low after (512 – m) writes for the SN74V215, (1024 – m) writes for the SN74V225, (2048 – m) writes for the SN74V235, and (4096 – m) writes for the SN74V245. The offset m is defined in the full offset register.

If asynchronous PAF configuration is selected, PAF is asserted low on the low-to-high transition of WCLK. PAF is reset to high on the low-to-high transition of RCLK. If synchronous PAF configuration is selected (see Table 5), PAF is updated on the rising edge of WCLK.

## PROGRAMMABLE ALMOST-EMPTY FLAG (PAE)

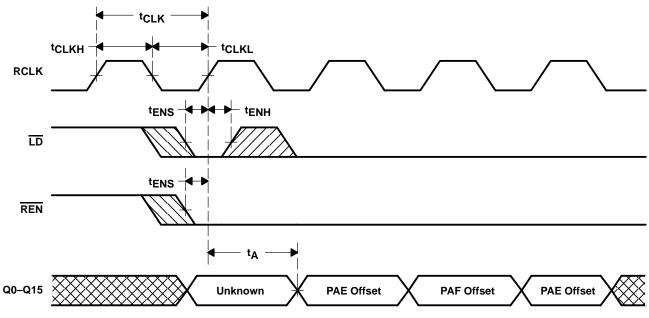

PAE goes low when the FIFO reaches the almost-empty condition. In FWFT mode,  $\overline{PAE}$  goes low when there are n + 1 words, or fewer, in the FIFO. In standard mode,  $\overline{PAE}$  goes low when there are n words or fewer in the FIFO. The offset n is defined as the empty offset. The default values for n are noted in Table 3 and Table 4.

If there is no empty offset specified, PAE is low when the device is 63 away from completely empty for SN74V215, and 127 away from completely empty for SN74V225, SN74V235, and SN74V245.

If asynchronous PAE configuration is selected, PAE is asserted low on the low-to-high transition of the read clock (RCLK). PAE is reset to high on the low-to-high transition of the write clock (WCLK). If synchronous PAE configuration is selected (see Table 5), PAE is updated on the rising edge of RCLK.

## WRITE EXPANSION OUT/HALF-FULL FLAG (WXO/HF)

This is a dual-purpose output. In the single-device and width-expansion mode, when write expansion in  $(\overline{WXI})$  and/or read expansion in  $(\overline{RXI})$  are grounded, this output acts as an indication of a half-full memory.

After one-half of the memory is filled, and at the low-to-high transition of the next write cycle, the half-full flag (HF) goes low and remains set until the difference between the write pointer and read pointer is less than or equal to one-half of the total memory of the device. HF is then reset to high by the low-to-high transition of the read clock (RCLK). HF is asynchronous.

In the daisy-chain depth-expansion mode,  $\overline{WXI}$  is connected to  $\overline{WXO}$  of the previous device. This output acts as a signal to the next device in the daisy chain by providing a pulse when the previous device writes to the last location of memory.

## READ EXPANSION OUT (RXO)

In the daisy-chain depth-expansion configuration, read expansion in  $(\overline{RXI})$  is connected to read expansion out  $(\overline{RXO})$  of the previous device. This output acts as a signal to the next device in the daisy chain by providing a pulse when the previous device reads from the last location of memory.

## detailed description (continued)

## DATA OUTPUTS (Q0-Q17)

Q0–Q17 are data outputs for 18-bit-wide data.

## functional description

### TIMING MODES:

## STANDARD vs FIRST-WORD FALL-THROUGH (FWFT) MODE

The SN74V215, SN74V225, SN74V235, and SN74V245 support two different timing modes. The selection of the mode of operation is determined during configuration at reset (RS). During an RS operation, the first load (FL), read expansion input (RXI), and write-expansion input (WXI) pins are used to select the timing mode as shown in the truth table (see Table 5). In standard mode, the first word written to an empty FIFO does not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating read enable (REN) and enabling a rising read clock (RCLK) edge, shifts the word from internal memory to the data output lines. In FWFT mode, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. A REN does not have to be asserted to access the first word.

Various signals, both input and output signals, operate differently, depending on which timing mode is in effect.

## FIRST-WORD FALL-THROUGH MODE (FWFT)

In this mode, status flags  $\overline{IR}$ ,  $\overline{PAF}$ ,  $\overline{HF}$ ,  $\overline{PAE}$ , and  $\overline{OR}$  operate in the manner outlined in Table 3. To write data into the FIFO,  $\overline{WEN}$  must be low. Data presented to the data-in lines is clocked into the FIFO on subsequent transitions of WCLK. After the first write is performed, the output ready ( $\overline{OR}$ ) flag goes low. Subsequent writes continue to fill the FIFO.  $\overline{PAE}$  goes high after n + 2 words have been loaded into the FIFO, where n is the empty offset value. The default setting for this value is stated in the footnote of Table 3. This parameter also is user programmable. See the *Programmable Flag Offset Loading* section.

If data continues to be written into the FIFO, and no read operations are taking place,  $\overline{\text{HF}}$  switches to low when the 258th (SN74V215), 514th (SN74V225), 1026th (SN74V235), and 2050th (SN74V245) word, respectively, is written into the FIFO. Continuing to write data into the FIFO causes  $\overline{\text{PAF}}$  to go low. Again, if no reads are performed,  $\overline{\text{PAF}}$  goes low after (513 – m) writes for the SN74V215, (1025 – m) writes for the SN74V225, (2049 – m) writes for the SN74V235, and (4097 – m) writes for the SN74V245, where m is the full offset value. The default setting for this value is stated in the footnote of Table 3.

When the FIFO is full, the input ready ( $\overline{IR}$ ) flag goes high, inhibiting further write operations. If no reads are performed after a reset,  $\overline{IR}$  goes high after D writes to the FIFO. D = 513 for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235, and 4097 for the SN74V245. The additional word in FWFT mode is due to the capacity of the memory plus output register.

If the FIFO is full, the first read operation causes the  $\overline{IR}$  flag to go low. Subsequent read operations cause  $\overline{PAF}$  and  $\overline{HF}$  to go high at the conditions described in Table 3. If further read operations occur without write operations,  $\overline{PAE}$  goes low when there are n + 1 words in the FIFO, where n is the empty offset value. If there is no empty offset specified,  $\overline{PAE}$  is low when the device is 64 away from empty for SN74V215, and 128 away from empty for SN74V225, SN74V235, and SN74V245. Continuing read operations cause the FIFO to be empty. When the last word has been read from the FIFO,  $\overline{OR}$  goes high, inhibiting further read operations. REN is ignored when the FIFO is empty.

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC<sup>TM</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

## functional description (continued)

|                         | NUMBER OF WORDS IN FIFO |                       |                         |    | PAF | HF |     |    |

|-------------------------|-------------------------|-----------------------|-------------------------|----|-----|----|-----|----|

| SN74V215                | SN74V225                | SN74V235              | SN74V245                | IR | PAF | HF | PAE | UR |

| 0                       | 0                       | 0                     | 0                       | L  | Н   | Н  | L   | Н  |

| 1 to (n+1) <sup>†</sup> | 1 to (n+1)†             | 1 to (n+1)†           | 1 to (n+1) <sup>†</sup> | L  | Н   | Н  | L   | L  |

| (n+2) to 257            | (n+2) to 513            | (n+2) to 1025         | (n+2) to 2049           | L  | Н   | Н  | Н   | L  |

| 258 to [513–(m+1)]‡     | 514 to [1025–(m+1)]‡    | 1026 to [2049–(m+1)]‡ | 2050 to [4097–(m+1)]‡   | L  | Н   | L  | Н   | L  |

| (513–m) to 512          | (1025–m) to 1024        | (2049–m) to 2048      | (4097–m) to 4096        | L  | L   | L  | Н   | L  |

| 513                     | 1025                    | 2049                  | 4097                    | Н  | L   | L  | Н   | L  |

#### Table 3. Status Flags for FWFT Mode

<sup>†</sup>n = Empty offset (SN74V215 n = 63; SN74V225, SN74V235, and SN74V245 n = 127)

<sup>‡</sup> m = Full offset (SN74V215 m = 63; SN74V225, SN74V235, and SN74V245 m = 127)

#### STANDARD MODE

In this mode, status flags  $\overline{FF}$ ,  $\overline{PAF}$ ,  $\overline{HF}$ ,  $\overline{PAE}$ , and  $\overline{EF}$  operate in the manner outlined in Table 4. To write data into the FIFO, write enable (WEN) must be low. Data presented to the data-in lines is clocked into the FIFO on subsequent transitions of the write clock (WCLK). After the first write is performed, the empty flag ( $\overline{EF}$ ) goes high. Subsequent writes continue to fill the FIFO. The programmable almost-empty flag ( $\overline{PAE}$ ) goes high after n + 1 words have been loaded into the FIFO, where n is the empty offset value. The default setting for this value is stated in the footnote of Table 4. This parameter also is user programmable. See the *Programmable Flag Offset Loading* section.

If data continues to be written into the FIFO, and no read operations are taking place, the half-full flag ( $\overline{\text{HF}}$ ) switches to low when the 257th (SN74V215), 513th (SN74V225), 1025th (SN74V235), and 2049th (SN74V245) word, is written into the FIFO. Continuing to write data into the FIFO causes the programmable almost-full flag ( $\overline{\text{PAF}}$ ) to go low. Again, if no reads are performed,  $\overline{\text{PAF}}$  goes low after (512 – m) writes for the SN74V215, (1024 – m) writes for the SN74V225, (2048 – m) writes for the SN74V235 and (4096 – m) writes for the SN74V245. Offset m is the full offset value. This parameter also is user programmable. See the *Programmable Flag Offset Loading* section. If there is no full offset specified,  $\overline{\text{PAF}}$  is low when the device is 63 away from full for SN74V215, and 127 away from full for the SN74V225, SN74V235, and SN74V245.

When the FIFO is full, the full flag ( $\overline{FF}$ ) goes low, inhibiting further write operations. If no reads are performed after a reset,  $\overline{FF}$  goes low after D writes to the FIFO. D = 512 for the SN74V215, 1024 for the SN74V225, 2048 for the SN74V235, and 4096 for the SN74V245.

If the FIFO is full, the first read operation causes  $\overline{FF}$  to go high. Subsequent read operations cause  $\overline{PAF}$  and the half-full flag ( $\overline{HF}$ ) to go high under the conditions described in Table 4. If further read operations occur, without write operations, the programmable almost-empty flag ( $\overline{PAE}$ ) goes low when there are n words in the FIFO, where n is the empty offset value. If there is no empty offset specified,  $\overline{PAE}$  is low when the device is 63 away from completely empty for SN74V215, and 127 away from completely empty for SN74V225, SN74V235, and SN74V245. Continuing read operations cause the FIFO to be empty. When the last word has been read from the FIFO,  $\overline{EF}$  goes low, inhibiting further read operations. REN is ignored when the FIFO is empty.

## functional description (continued)

|                     | NUMBER OF WORDS IN FIFO |                       |                       |    |     |    |     | 1  |

|---------------------|-------------------------|-----------------------|-----------------------|----|-----|----|-----|----|

| SN74V215            | SN74V225                | SN74V235              | SN74V245              | FF | PAF | HF | PAE | EF |

| 0                   | 0                       | 0                     | 0                     | Н  | Н   | Н  | L   | L  |

| 1 to n <sup>†</sup> | 1 to n†                 | 1 to n†               | 1 to n <sup>†</sup>   | Н  | Н   | Н  | L   | Н  |

| (n+1) to 256        | (n+1) to 512            | (n+1) to 1024         | (n+1) to 2048         | Н  | Н   | Н  | Н   | Н  |

| 257 to [512–(m+1)]‡ | 513 to [1025–(m+1)]‡    | 1025 to [2048–(m+1)]‡ | 2049 to [4096–(m+1)]‡ | Н  | Н   | L  | Н   | Н  |

| (512–m) to 511      | (1024–m) to 1023        | (2048–m) to 2047      | (4096–m) to 4095      | Н  | L   | L  | Н   | Н  |

| 512                 | 1024                    | 2048                  | 4096                  | L  | L   | L  | Н   | Н  |

## Table 4. Status Flags for Standard Mode

<sup>†</sup>n = Empty offset (SN74V215 n = 63; SN74V225, SN74V235, and SN74V245 n = 127)

<sup>‡</sup> m = Full offset (SN74V215 m = 63; SN74V225, SN74V235, and SN74V245 m = 127)

## PROGRAMMABLE FLAG LOADING

Full- and empty-flag offset values can be user programmable. The SN74V215, SN74V225, SN74V235, and SN74V245 have internal registers for these offsets. Default settings are stated in the footnotes of Table 3 and Table 4. Offset values are loaded into the FIFO using the data input lines D0–D11. To load the offset registers, the load ( $\overline{LD}$ ) pin and  $\overline{WEN}$  pin must be held low. Data present on D0–D11 is transferred to the empty offset register on the first low-to-high transition of WCLK. By continuing to hold the  $\overline{LD}$  and  $\overline{WEN}$  pins low, data present on D0–D11 is transferred into the full offset register on the next transition of the WCLK. The third transition again writes to the empty offset register. Writing to all offset registers does not have to occur at the same time. One or two offset registers can be written and, then, by bringing the  $\overline{LD}$  pin high, the FIFO is returned to normal read/write operation. When the  $\overline{LD}$  pin and  $\overline{WEN}$  again are set low, the next offset register in sequence is written.

The contents of the offset registers can be read on the data output lines Q0–Q11 when the  $\overline{\text{LD}}$  pin is set low, and  $\overline{\text{REN}}$  is set low. Data then can be read on the next low-to-high transition of RCLK. The first transition of RCLK presents the empty offset value to the data output lines. The next transition of RCLK presents the full offset value. Offset register content can be read in the standard mode only. It cannot be read in the FWFT mode.

## SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIMING SELECTION

The SN74V215, SN74V225, SN74V235, and SN74V245 can be configured during the configuration-at-reset cycle (see Table 5) with either asynchronous or synchronous timing for PAE and PAF flags.

If asynchronous PAE/PAF configuration is selected (see Table 5), the PAE is asserted low on the low-to-high transition of RCLK. PAE is reset to high on the low-to-high transition of WCLK. Similarly, the PAF is asserted low on the low-to-high transition of WCLK, and PAF is reset to high on the low-to-high transition of RCLK. For detailed timing diagrams, see Figure 9 for asynchronous PAE timing and Figure 10 for asynchronous PAF timing.

If synchronous PAE/PAF configuration is selected, PAE is asserted and updated on the rising edge of RCLK only, but not WCLK. Similarly, PAF is asserted and updated on the rising edge of WCLK only, but not RCLK. For detailed timing diagrams, see Figure 18 for synchronous PAE timing and Figure 19 for synchronous PAF timing.

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC<sup>TM</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

## functional description (continued)

| FL | RXI | WXI | EF/OR                                         | FF/IR                                        | PAE, PAF     | FIFO TIMING MODE |

|----|-----|-----|-----------------------------------------------|----------------------------------------------|--------------|------------------|

| 0  | 0   | 0   | Single register-buffered<br>empty flag        | Single register-buffered full flag           | Asynchronous | Standard         |

| 0  | 0   | 1   | Triple register-buffered<br>output-ready flag | Double register-buffered<br>input ready flag | Asynchronous | FWFT             |

| 0  | 1   | 0   | Double register-buffered<br>empty flag        | Double register-buffered<br>full flag        | Asynchronous | Standard         |

| 0† | 1   | 1   | Single register-buffered<br>empty flag        | Single register-buffered<br>full flag        | Asynchronous | Standard         |

| 1  | 0   | 0   | Single register-buffered<br>empty flag        | Single register-buffered<br>full flag        | Synchronous  | Standard         |

| 1  | 0   | 1   | Triple register-buffered<br>output-ready flag | Double register-buffered<br>input ready flag | Synchronous  | FWFT             |

| 1  | 1   | 0   | Double register-buffered<br>empty flag        | Double register-buffered<br>full flag        | Synchronous  | Standard         |

| 1‡ | 1   | 1   | Single register-buffered<br>empty flag        | Single register-buffered<br>full flag        | Asynchronous | Standard         |

Table 5. Truth Table for Configuration at Reset

<sup>†</sup> In daisy-chain <u>depth</u> expansion, FL is held low for the first-load device. The RXI and WXI inputs are driven by the corresponding RXO and WXO outputs of the preceding device.

<sup>‡</sup> In daisy-chain depth expansion, FL is held high for members of the expansion other than the first-load device. The RXI and WXI inputs are driven by the corresponding RXO and WXO outputs of the preceding device.

#### **REGISTER-BUFFERED FLAG OUTPUT SELECTION**

The SN74V215, SN74V225, SN74V235, and SN74V245 can be configured during the configuration-at-reset cycle (see Table 7) with single, double, or triple register-buffered flag output signals. The various combinations available are described in Table 6 and Table 7. In general, going from single to double or triple register-buffered flag outputs removes the possibility of metastable flag indications on boundary states (empty or full conditions). The tradeoff is the addition of clock-cycle delays for the respective flag to be asserted. Not all combinations of register-buffered flag outputs are supported. Register-buffered outputs apply to the empty flag and full flag only. Partial flags are not affected. Table 6 and Table 7 summarize the options available.

Table 6. Register-Buffered Flag Output Options, FWFT Mode

| OUTPUT READY |        | PARTIAL      | PROGRAMMING<br>AT RESET |   |     | FLAG TIMING<br>DIAGRAMS |

|--------------|--------|--------------|-------------------------|---|-----|-------------------------|

| (OR)         | (IR)   | FLAGS        | GS FL RXI WXI           |   | WXI | DIAGRAINS               |

| Triple       | Double | Asynchronous | 0                       | 0 | 1   | Figure 23               |

| Triple       | Double | Synchronous  | 1                       | 0 | 1   | Figure 16, Figure 17    |

| Table 7. Register-Buffered Flag Output Options, Standard Mode |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| EMPTY FLAG<br>(EF)     | FUL <u>L</u> FLAG<br>(FF) | PARTIAL<br>FLAGS | PROG | RESET | NG AT | FLAG TIMING<br>DIAGRAMS |

|------------------------|---------------------------|------------------|------|-------|-------|-------------------------|

| <b>BUFFERED OUTPUT</b> | <b>BUFFERED</b> OUTPUT    | TIMING MODE      | FL   | RXI   | WXI   | DIAGRAMS                |

| Single                 | Single                    | Asynchronous     | 0    | 0     | 0     | Figure 5, Figure 6      |

| Single                 | Single                    | Synchronous      | 1    | 0     | 0     | Figure 5, Figure 6      |

| Double                 | Double                    | Asynchronous     | 0    | 1     | 0     | Figure 20, Figure 22    |

| Double                 | Double                    | Synchronous      | 1    | 1     | 0     | Figure 20, Figure 22    |

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

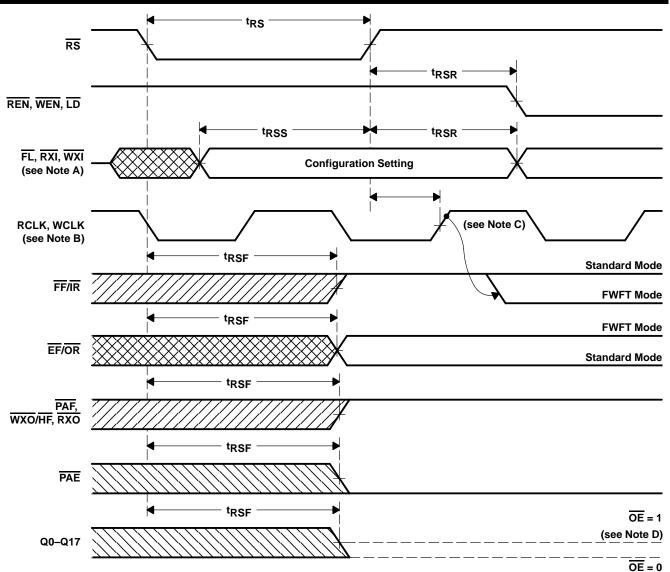

- NOTES: A. Single-device mode (FL, RXI, WXI) = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0). FL, RXI, WXI should be static (tied to V<sub>CC</sub> or GND).

- B. The clocks (RCLK, WCLK) can be free-running asynchronously or coincidentally.

- C. In FWFT mode, IR goes low based on the WCLK edge after reset.

- D. After reset, the outputs are low if  $\overline{OE} = 0$  and 3-state if  $\overline{OE} = 1$ .

#### Figure 1. Reset Timing

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNCTM FIRST-IN, FIRST-OUT MEMORIES

SCAS636E – APRIL 2000 – REVISED SEPTEMBER 2002

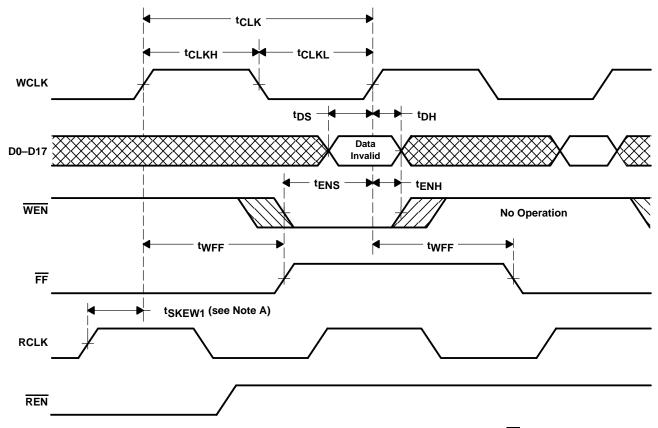

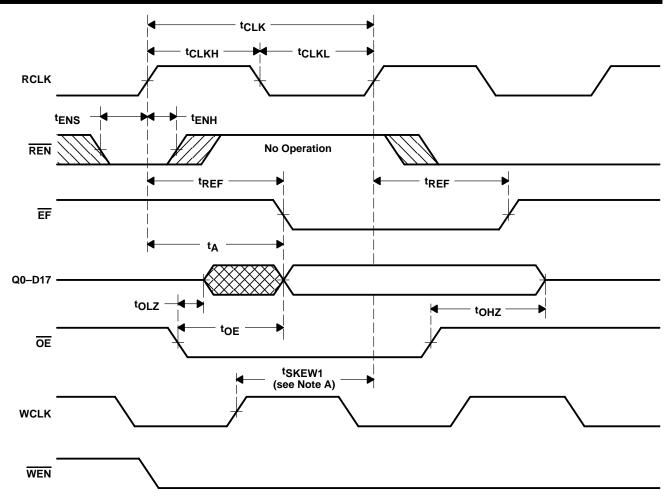

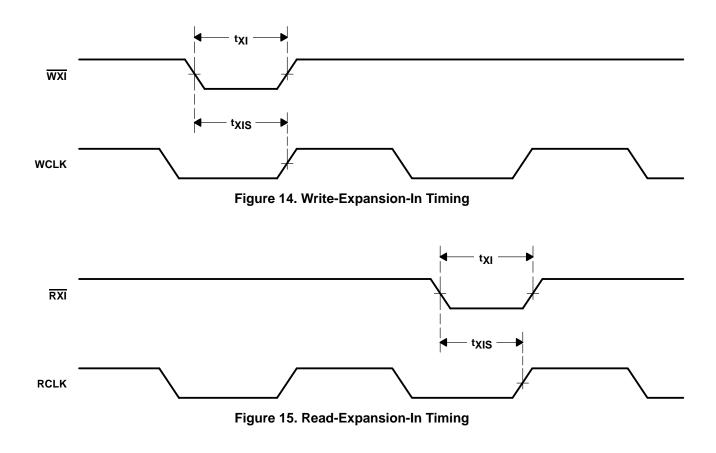

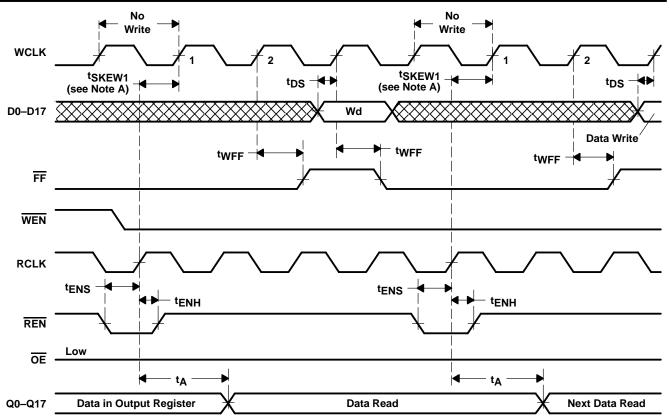

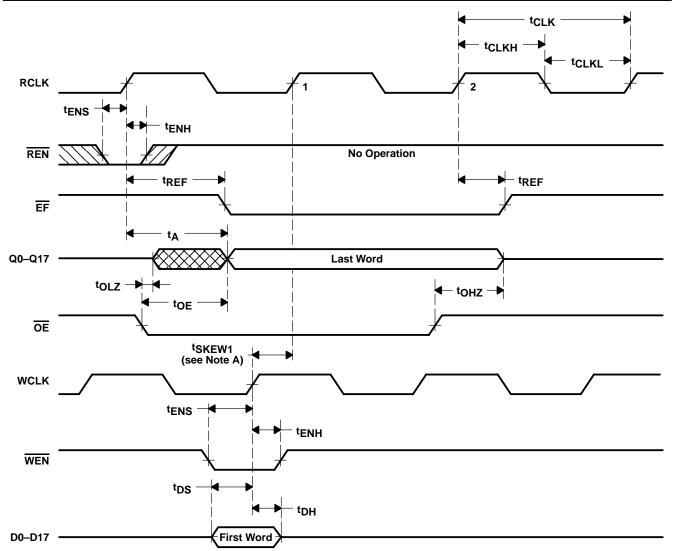

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that FF goes high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, FF might not change state until the next WCLK edge.

B. Select standard mode by setting (FL, RXI, WXI) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

## Figure 2. Write-Cycle Timing With Single Register-Buffered FF (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

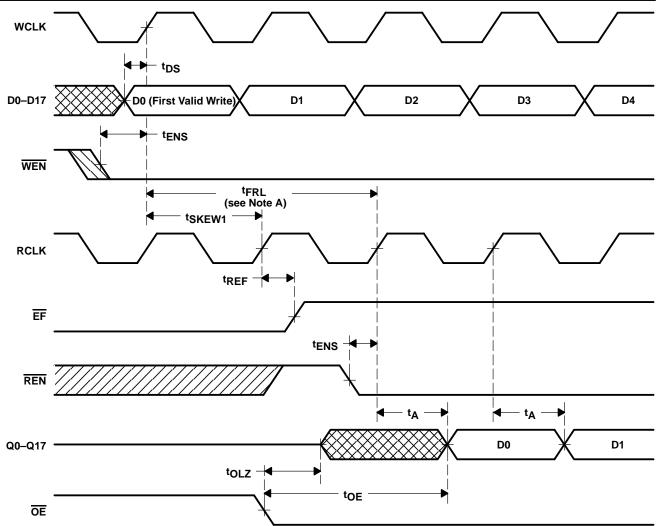

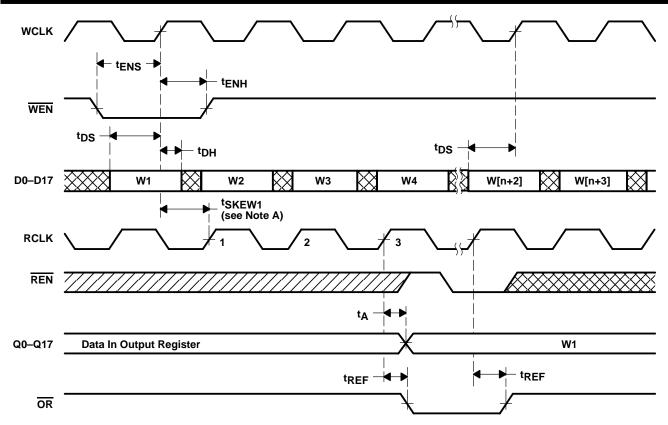

- NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge to ensure that EF goes high during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW1</sub>, EF might not change state until the next RCLK edge.

- B. Select standard mode by setting (FL, RXI, WXI) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

Figure 3. Read-Cycle Timing With Single Register-Buffered EF (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC^{\rm TM} FIRST-IN, FIRST-OUT MEMORIES

SCAS636E – APRIL 2000 – REVISED SEPTEMBER 2002

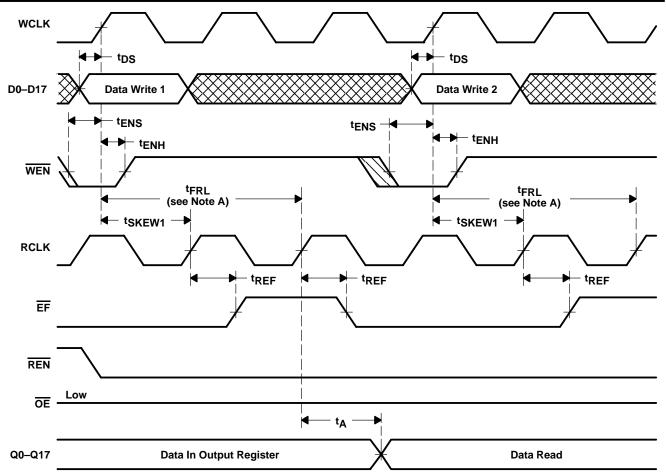

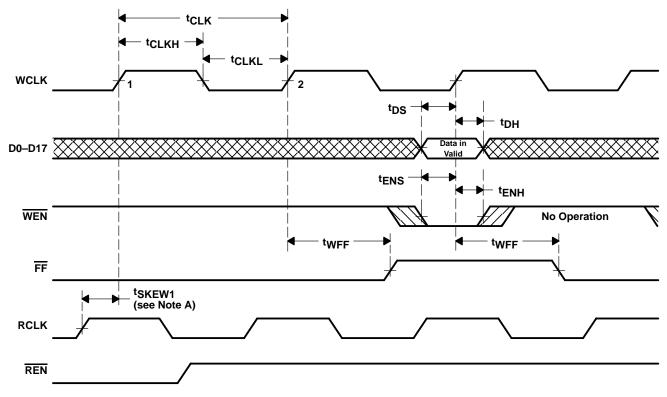

- NOTES: A. When t<sub>SKEW1</sub> is at the minimum specification, t<sub>FRL</sub> (maximum) = t<sub>CLK</sub> + t<sub>SKEW1</sub>. When t<sub>SKEW1</sub> is less than the minimum specification, t<sub>FRL</sub> (maximum) = either (2 × t<sub>CLK</sub>) + t<sub>SKEW1</sub> or t<sub>CLK</sub> + t<sub>SKEW1</sub>. The latency timing applies only at the empty boundary (EF is low).

- B. The first word always is available the cycle after EF goes high.

- C. Select standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

#### Figure 4. First-Data-Word Latency with Single Register-Buffered EF (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC™ FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

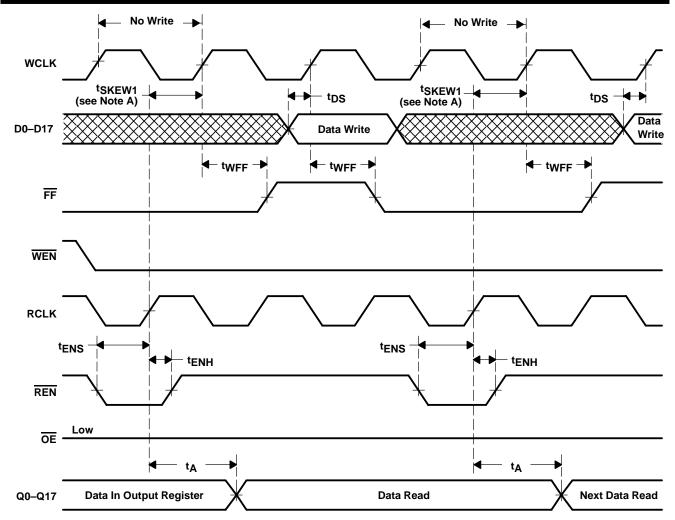

- NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that FF goes high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, FF might not change state until the next WCLK edge.

- B. Select standard mode by setting (FL, RXI, WXI) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

#### Figure 5. Single Register-Buffered Full-Flag Timing (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC^{TM} FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

- NOTES: A. When t<sub>SKEW1</sub> is at the minimum specification, t<sub>FRL</sub> (maximum) = t<sub>CLK</sub> + t<sub>SKEW1</sub>. When t<sub>SKEW1</sub> is less than the minimum specification, t<sub>FRL</sub> (maximum) = either (2 × t<sub>CLK</sub>) + t<sub>SKEW1</sub> or t<sub>CLK</sub> + t<sub>SKEW1</sub>. The latency timing applies only at the empty boundary (EF is low).

- B. Select standard mode by setting (FL, RXI, WXI) = (0,0,0), (0,1,1), (1,0,0) or (1,1,1) during reset.

#### Figure 6. Single Register-Buffered Empty Flag Timing (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

Figure 7. Write Programmable Registers (Standard and FWFT Modes)

Figure 8. Read Programmable Registers (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC^{\rm TM} FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

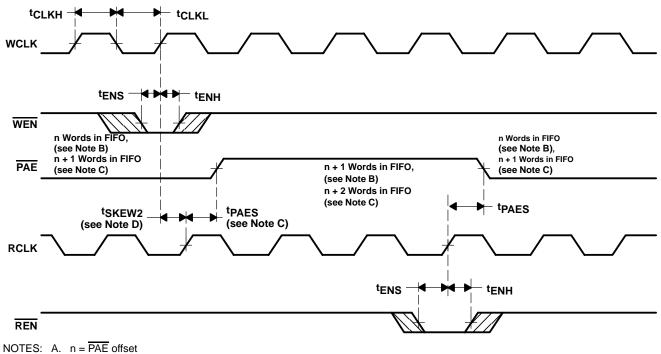

NOTES: A.  $n = \overline{PAE}$  offset

B. For standard mode

C. For FWFT mode

D. PAE is asserted low on RCLK transition and reset to high on WCLK transition.

E. Select the asynchronous modes by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,0), (0,0,1), (0,1,0), (0,1,1) or (1,1,1) during reset.

Figure 9. Asynchronous Programmable Almost-Empty-Flag Timing (Standard and FWFT Modes)

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

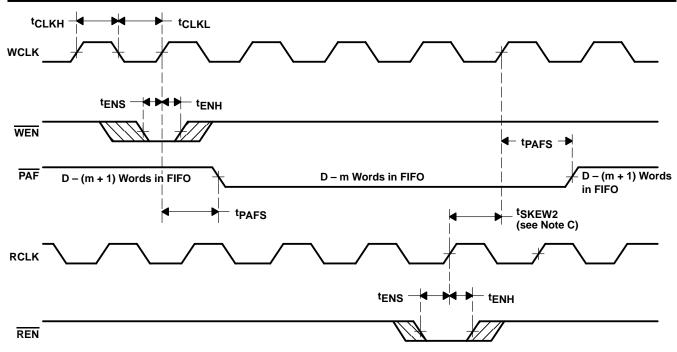

NOTES: A.  $m = \overline{PAF}$  offset

B. D = maximum FIFO depth

In FWFT mode: D = 513 for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235 and 4097 for the SN74V245 In standard mode: D = 512 for the SN74V215, 1024 for the SN74V225, 2048 for the SN74V235 and 4096 for the SN74V245 C. PAF is asserted to low on WCLK transition and reset to high on RCLK transition.

D. Select asynchronous modes by setting (FL, RXI, WXI) = (0,0,0), (0,0,1), (0,1,0), (0,1,1) or (1,1,1) during reset.

Figure 10. Asynchronous Programmable Almost-Full-Flag Timing (Standard and FWFT Modes)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC^{\rm TM} FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

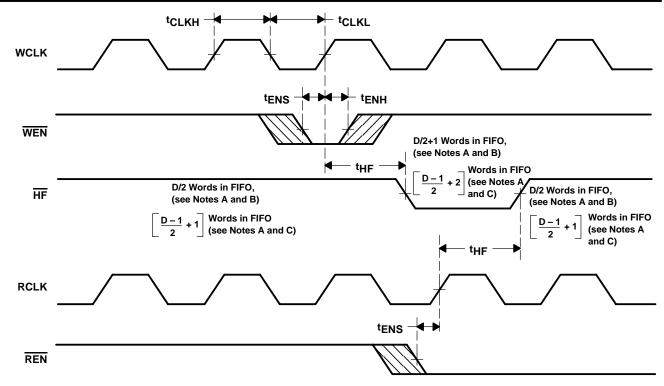

NOTES: A. D = maximum FIFO depth

In FWFT mode: D = 513 for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235 and 4097 for the SN74V245 In standard mode: D = 512 for the SN74V215, 1024 for the SN74V225, 2048 for the SN74V235 and 4096 for the SN74V245 B. For standard mode

- C. For FWFT mode

- D. Select single-device mode by setting (FL, RXI, WXI) = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0) during reset.

#### Figure 11. Half-Full-Flag Timing (Standard and FWFT Modes)

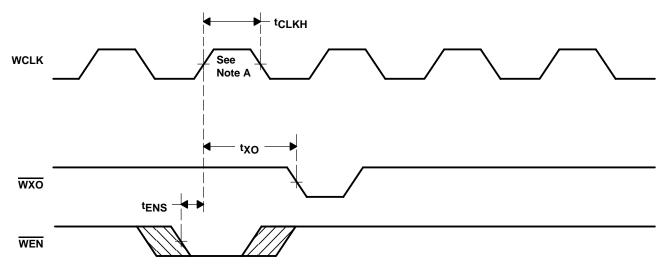

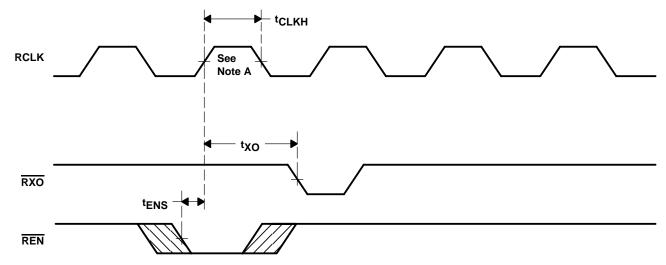

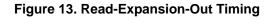

NOTE A: Write to last physical location.

## $\begin{array}{c} \text{SN74V215, SN74V225, SN74V235, SN74V245} \\ \text{512}\times18, 1024\times18, 2048\times18, 4096\times18 \\ \text{DSP-SYNC^{\tiny TM}} \text{ FIRST-IN, FIRST-OUT MEMORIES} \end{array}$

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

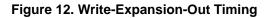

NOTE A: Read from last physical location.

ŝ

Т

IRS

FIRST-

7,8 ₩ ₩

48

$\boldsymbol{\infty}$

4096

r memories

×18, 1

ഗ

N74V225

N74V235,

**SN74V245**

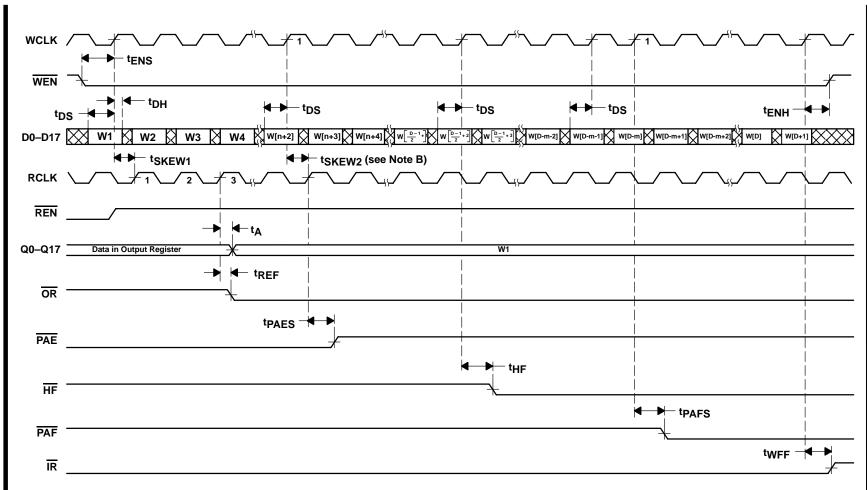

- NOTES: A. t SKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge for OR to go low after two RCLK cycles plus tREF. If the time between the rising edge of WLCK and the rising edge of RCLK is less than t SKEW1, the OR deassertion might be delayed one extra RCLK cycle.

- B. t<sub>SKEW2</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge for PAE to go high during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW2</sub>, the PAE deassertion might be delayed one extra RCLK cycle.

- C. LD is high, OE is low.

24

POST OFFICE

BOX 655303 • DALLAS, TEXAS 75265

TEXAS INSTRUMENTS

- D. n = PAE offset, m = PAF offset, D = maximum FIFO depth = 513 words for the SN74V215, 1025 words for the SN74V225, 2049 words for the SN74V235, and 4097 words for the SN74V245.

- E. Select synchronous FWFT mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (1,0,1) during reset.

Figure 16. Write Timing With Synchronous Programmable Flags (FWFT Mode)

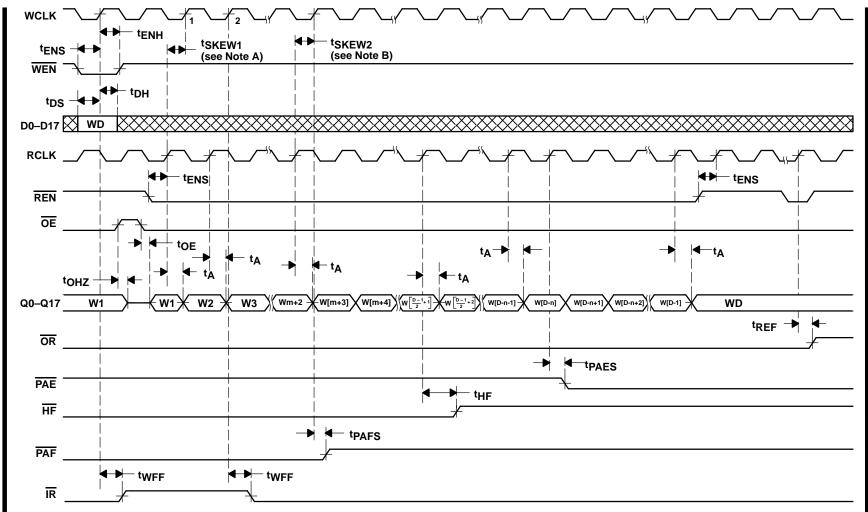

- NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that IR goes low after one WCLK plus t<sub>WFF</sub>. If the time between the rising edge of RLCK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, the IR assertion might be delayed an extra WCLK cycle.

- B. t<sub>SKEW2</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to go high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW2</sub>, the PAF deassertion time may be delayed an extra WCLK cycle.

- C. LD is high.

- D. n = PAE offset, m = PAF offset, D = maximum FIFO depth = 513 words for the SN74V215, 1025 words for the SN74V225, 2049 words for SN74V235, and 4097 words for SN74V245.

- E. Select synchronous FWFT mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (1,0,1) during reset.

Figure 17. Read Timing With Synchronous Programmable Flags (FWFT Mode)

DSP-S SN74V **YNCTM** СЛ FIRST-0 N74V225. 7 ω **IRST-OUT** 2048 SN74V235, X Θ  $\boldsymbol{\infty}$ MEMORIES 4096 **SN74V245**  $\boldsymbol{\omega}$

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

- B. For standard mode

- C. For FWFT mode

- D. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge for PAE to go high during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than tSKEW2, the PAE deassertion might be delayed one extra RCLK cycle.

- E. PAE is asserted and updated on the rising edge of RCLK only.

- F. Select synchronous modes by setting (FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during reset.

Figure 18. Synchronous Programmable Almost-Empty-Flag Timing (Standard and FWFT Modes)

## SN74V215, SN74V225, SN74V235, SN74V245 $512 \times 18$ , $1024 \times 18$ , $2048 \times 18$ , $4096 \times 18$ DSP-SYNC™ FIRST-IN. FÍRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

NOTES: A.  $m = \overline{PAF}$  offset

B. D = maximum FIFO depth

In FWFT mode: D = 513 for the SN74V215, 1025 for the SN74V225, 2049 for the SN74V235, and 4097 for the SN74V245. In standard mode: D = 512 for the SN74V215, 1024 for the SN74V225, 2048 for the <u>SN</u>74V235, and 4096 for the SN74V245.

C. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to go high during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than tSKEW2, the PAF deassertion time might be delayed an extra WCLK cycle.

- D. PAF is asserted and updated on the rising edge of WCLK only.

E. Select synchronous modes by setting (FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during reset.

Figure 19. Synchronous Programmable Almost-Full-Flag Timing (Standard and FWFT Modes)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC^{\rm TM} FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that FF goes high after one WCLK cycle plus t<sub>WFF</sub>. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, the FF deassertion time might be delayed an extra WCLK cycle.

B. LD is high.

C. Select double register-buffered standard mode by setting (FL, RXI, WXI) = (0,1,0) or (1,1,0) during reset.

Figure 20. Double Register-Buffered Full-Flag Timing (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E – APRIL 2000 – REVISED SEPTEMBER 2002

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to ensure that  $\overline{FF}$  goes high after one WCLK cycle plus t<sub>RFF</sub>. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, the  $\overline{FF}$  deassertion might be delayed an extra WCLK cycle.

B. LD is high.

C. Select double register-buffered standard mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,1,0) or (1,1,0) during reset.

Figure 21. Write-Cycle Timing With Double Register-Buffered FF (Standard Mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC<sup>TM</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

- NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge to ensure that  $\overline{\text{EF}}$  goes high after one RCLK cycle plus t<sub>REF</sub>. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW1</sub>, the  $\overline{\text{EF}}$  deassertion might be delayed an extra RCLK cycle.

- B. LD is high.

- C. Select double register-buffered standard mode by setting (FL, RXI, WXI) = (0,1,0) or (1,1,0) during reset.

## Figure 22. Read-Cycle Timing With Double Register-Buffered EF (Standard Timing)

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC™ FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

NOTES: A. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge for OR to go high during the current cycle. If the time between the rising edge of WLCK and the rising edge of RCLK is less than t<sub>SKEW1</sub>, the OR deassertion might be delayed one extra RCLK cycle.

B.  $\overline{\text{LD}}$  is high,  $\overline{\text{OE}}$  is low.

C. Select FWFT mode by setting ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$ ) = (0,0,1) or (1,0,1) during reset.

Figure 23. OR-Flag Timing and First Word Fall Through When FIFO is Empty (FWFT mode)

## SN74V215, SN74V225, SN74V235, SN74V245 512 $\times$ 18, 1024 $\times$ 18, 2048 $\times$ 18, 4096 $\times$ 18 DSP-SYNC<sup>TM</sup> FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

#### operating configurations

#### SINGLE-DEVICE CONFIGURATION

A single SN74V215, SN74V225, SN74V235, or SN74V245 can be used when the application requirements are for 512/1024/2048/4096 words or fewer, respectively. These FIFOs are in a single-device configuration when the first load ( $\overline{FL}$ ), write expansion in ( $\overline{WXI}$ ) and read expansion in ( $\overline{RXI}$ ) control inputs are configured as ( $\overline{FL}$ ,  $\overline{RXI}$ ,  $\overline{WXI}$  = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0) during reset (see Figure 24).

Figure 24. Block Diagram of Single 512 imes 18, 1024 imes 18, 2048 imes 18, or 4096 imes 18 Synchronous FIFO

## operating configurations (continued)

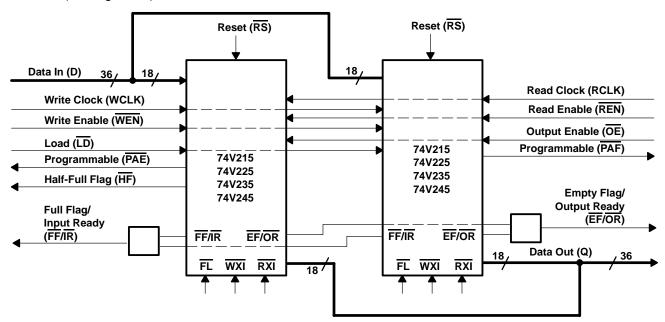

## WIDTH-EXPANSION CONFIGURATION

Word width may be increased simply by connecting together the control signals of multiple devices. Status flags can be detected from any one device. The exceptions are the empty flag/output ready and full flag/input ready. Because of variations in skew between RCLK and WCLK, it is possible for flag assertion and deassertion to vary by one cycle between FIFOs. To avoid problems, the user must create composite flags by gating the empty flags/output ready of every FIFO, and separately gating all full flags/input ready. Figure 25 demonstrates a 36-word width by using two SN74V215, SN74V225, SN74V235, or SN74V245 memories. Any word width can be attained by adding additional SN74V215, SN74V225, SN74V235, or SN74V245 memories. These FIFOs are in a single-device configuration when the first load (FL), write expansion in (WXI), and read expansion in (RXI) control inputs are configured as (FL, RXI, WXI = (0,0,0), (0,0,1), (0,1,0), (1,0,0), (1,0,1) or (1,1,0) during reset (see Figure 25).

NOTE A: Do not connect any output control signals directly together.

## Figure 25. Block Diagram of $512\times36,\,1024\times36,\,2048\times36,\,or\,4096\times36$ Synchronous FIFO Memory Used in a Width-Expansion Configuration

#### DEPTH-EXPANSION CONFIGURATION, DAISY-CHAIN TECHNIQUE (WITH PROGRAMMABLE FLAGS)

These devices can be adapted easily to applications requiring more than 512, 1024, 2048, or 4096 words of buffering. Figure 26 shows depth expansion using three SN74V215, SN74V225, SN74V235, or SN74V245 memories. Maximum depth is limited only by signal loading.

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC™ FIRST-IN, FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

NOTES: A. The first device must be designated by grounding the first load (FL) control input.

- B. All other devices must have  $\overline{FL}$  in the high state.

- C. The write expansion out (WXO) pin of each device must be tied to the write expansion in (WXI) pin of the next device.

- D. The read expansion out (RXO) pin of each device must be tied to the read expansion in (RXI) pin of the next device.

- E. All load (LD) pins are tied together.

- The half-full flag ( $\overline{HF}$ ) is not available in this depth-expansion configuration. F.

- G. EF, FF, PAE, and PAF are created with composite flags by ORing together every respective flag for monitoring. The composite PAE and PAF flags are not precise.

- H. In daisy-chain mode, the flag outputs are single-register buffered and the partial flags are in asynchronous timing mode.

Figure 26. Block Diagram of  $1536 \times 18$ ,  $3072 \times 18$ ,  $6144 \times 18$ ,  $12288 \times 18$ Synchronous FIFO Memory With Programmable Flags Used in Depth-Expansion Configuration

#### operating configurations (continued)

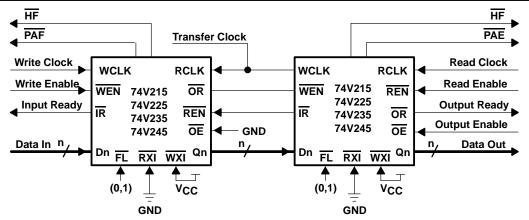

### **DEPTH-EXPANSION CONFIGURATION (FWFT MODE)**

In FWFT mode, the FIFOs can be connected in series (the data outputs of one FIFO connected to the data inputs of the next) with no external logic necessary. The resulting configuration provides a total depth equivalent to the sum of the depths associated with each single FIFO. NO TAG shows a depth expansion using two SN74V215, SN74V225, SN74V235, or SN74V245 memories.

Care should be taken to select FWFT mode during master reset for all FIFOs in the depth expansion configuration. The first word written to an empty configuration passes from one FIFO to the next (ripple down) until it finally appears at the outputs of the last FIFO in the chain. No read operation is necessary, but the RCLK of each FIFO must be free running. Each time the data word appears at the outputs of one FIFO, that device's OR line goes low, enabling a write to the next FIFO in line.

For an empty expansion configuration, the amount of time it takes for  $\overline{OR}$  of the last FIFO in the chain to go low (i.e., valid data to appear on the last FIFO's outputs) after a word has been written to the first FIFO is the sum of the delays for each individual FIFO:

$(N - 1) \times (4 \times transfer clock) + 3 \times T_{RCLK}$

Where: N is the number of FIFOs in the expansion and  $T_{RCLK}$  is the RCLK period. Extra cycles should be added for the possibility that the  $t_{SKEW1}$  specification is not met between WCLK and transfer clock, or RCLK and transfer clock, for the  $\overline{OR}$  flag.

The ripple-down delay is noticeable only for the first word written to an empty depth-expansion configuration. There is no delay evident for subsequent words written to the configuration.

The first free location created by reading from a full depth-expansion configuration bubbles up from the last FIFO to the previous one until finally it moves into the first FIFO of the chain. Each time a free location is created in one FIFO of the chain, that FIFO's IR line goes low, enabling the preceding FIFO to write a word to fill it.

For a full expansion configuration, the amount of time it takes for IR of the first FIFO in the chain to go low after a word has been read from the last FIFO is the sum of the delays for each individual FIFO:

$(N - 1) \times (3 \times transfer clock) + 2T_{WCLK}$

Where: N is the number of FIFOs in the expansion and  $T_{WCLK}$  is the WCLK period. Extra cycles should be added for the possibility that the  $t_{SKEW1}$  specification is not met between RCLK and transfer clock, or WCLK and transfer clock, for the IR flag.

The transfer clock line should be tied to either WCLK or RCLK, whichever is faster. Both these actions result in data moving, as quickly as possible, to the end of the chain and free locations to the beginning of the chain.

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>™</sup> FIRST-IN, FIRST-OUT MEMORIES SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

Figure 27. Block Diagram of 1024  $\times$  18, 2048  $\times$  18, 4096  $\times$  18, 8192  $\times$  18 Synchronous FIFO Memory With Programmable Flags Used in Depth-Expansion Configuration

## SN74V215, SN74V225, SN74V235, SN74V245 $512 \times 18$ , $1024 \times 18$ , $2048 \times 18$ , $4096 \times 18$ DSP-SYNC™ FIRST-IN. FIRST-OUT MEMORIES

SCAS636E - APRIL 2000 - REVISED SEPTEMBER 2002

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                         | 0.5 V to 5 V   |

|---------------------------------------------------------------|----------------|

| Continuous output current, $I_O (V_O = 0 \text{ to } V_{CC})$ | ±50 mA         |

| Storage temperature range, T <sub>stg</sub>                   | -55°C to 125°C |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions

|                |                                | MIN | TYP | MAX | UNIT |

|----------------|--------------------------------|-----|-----|-----|------|

| Vcc            | Supply voltage                 | 3.0 | 3.3 | 3.6 | V    |

| GND            | Supply voltage                 | 0   | 0   | 0   | V    |

| VIH            | High-level input voltage       | 2   |     | 5   | V    |

| VIL            | Low-level input voltage        |     |     | 0.8 | V    |

| т <sub>А</sub> | Operating free-air temperature | 0   |     | 70  | °C   |

#### electrical characteristics over recommended operating conditions (unless otherwise noted)

| PARAMETER        |                                   | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| VOH              | V <sub>CC</sub> = 3.0 V,          | $I_{OH} = -2 \text{ mA}$                                     | 2.4 |     |     | V    |

| VOL              | V <sub>CC</sub> = 3.0 V,          | I <sub>OL</sub> = 8 mA                                       |     |     | 0.4 | V    |

| lj               | V <sub>CC</sub> = 3.6 V,          | $V_I = V_{CC}$ to 0.4 V                                      |     |     | ±1  | μA   |

| loz              | V <sub>CC</sub> = 3.6 V,          | $\overline{OE} \ge V_{IH}$ , $V_O = V_{CC}$ to 0.4 V         |     |     | ±10 | μA   |

| ICC1             | $V_{CC} = 3.3 V,$                 | See Notes 1, 2, and 3                                        |     |     | 35  | mA   |

| I <sub>CC2</sub> | V <sub>CC</sub> = 3.6 V,          | See Notes 1 and 4                                            |     |     | 5   | mA   |

| C <sub>IN</sub>  | $V_I = 0, T_A = 25^{\circ}C,$     | f = 1 MHz                                                    |     | 10  |     | pF   |

| COUT             | $V_{O} = 0, T_{A} = 25^{\circ}C,$ | f = 1 MHz, Output deselected, ( $\overline{OE} \ge V_{IH}$ ) |     | 10  |     | pF   |

NOTES: 1. Tested with outputs disabled  $(I_{OUT} = 0)$

- 2. RCLK and WCLK switch at 20 MHz and data inputs switch at 10 MHz.

- 3. Typical I<sub>CC1</sub> = 2.04 + 0.88 × f<sub>S</sub> + 0.02 × C<sub>L</sub> × f<sub>S</sub> (in mA). These equations are valid under the following conditions:

V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C, f<sub>S</sub> = WCLK frequency = RCLK frequency (in MHz, using TTL levels), data switching at f<sub>S</sub>/2, C<sub>L</sub> = capacitive load (in pF).

4. All inputs =  $(V_{CC} - 0.2 V)$  or (GND + 0.2 V), except RCLK and WCLK, which switch at 20 MHz.

## SN74V215, SN74V225, SN74V235, SN74V245 512 × 18, 1024 × 18, 2048 × 18, 4096 × 18 DSP-SYNC<sup>TM</sup> FIRST-IN, FIRST-OUT MEMORIES SCAS636E – APRIL 2000 – REVISED SEPTEMBER 2002

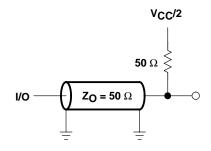

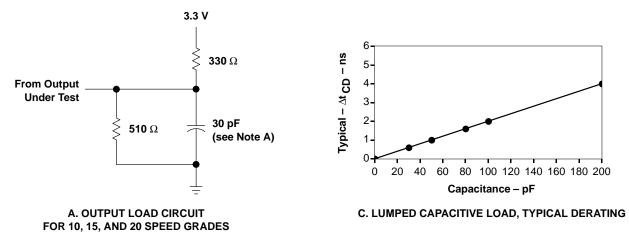

## timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figure 28 through Figure 23)

|                    |                                                                                 | '74V215-7<br>'74V225-7<br>'74V235-7<br>'74V235-7<br>'74V245-7 |      | <sup>?</sup> 74V215-10<br><sup>?</sup> 74V225-10<br><sup>?</sup> 74V235-10<br><sup>?</sup> 74V245-10 |     | '74V215-15<br>'74V225-15<br>'74V235-15<br>'74V245-15 |      | <sup>?</sup> 74V215-20<br><sup>?</sup> 74V225-20<br><sup>?</sup> 74V235-20<br><sup>?</sup> 74V245-20 |     | UNIT |

|--------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------|------|------------------------------------------------------------------------------------------------------|-----|------|

|                    |                                                                                 | MIN                                                           | MAX  | MIN                                                                                                  | MAX | MIN                                                  | MAX  | MIN                                                                                                  | MAX |      |

| fclock             | Clock cycle frequency                                                           |                                                               | 133  |                                                                                                      | 100 |                                                      | 66.7 |                                                                                                      | 50  | MHz  |

| t <sub>A</sub>     | Data access time                                                                | 2                                                             | 5    | 2                                                                                                    | 6.5 | 2                                                    | 10   | 2                                                                                                    | 12  | ns   |

| <sup>t</sup> CLK   | Clock cycle time                                                                | 7.5                                                           |      | 10                                                                                                   |     | 15                                                   |      | 20                                                                                                   |     | ns   |

| <sup>t</sup> CLKH  | Clock high time                                                                 | 3.5                                                           |      | 4.5                                                                                                  |     | 6                                                    |      | 8                                                                                                    |     | ns   |

| <sup>t</sup> CLKL  | Clock low time                                                                  | 3.5                                                           |      | 4.5                                                                                                  |     | 6                                                    |      | 8                                                                                                    |     | ns   |

| <sup>t</sup> DS    | Data setup time                                                                 | 2.5                                                           |      | 3                                                                                                    |     | 4                                                    |      | 5                                                                                                    |     | ns   |

| <sup>t</sup> DH    | Data hold time                                                                  | 0.5                                                           |      | 0.5                                                                                                  |     | 1                                                    |      | 1                                                                                                    |     | ns   |

| <sup>t</sup> ENS   | Enable setup time                                                               | 2.5                                                           |      | 3                                                                                                    |     | 4                                                    |      | 5                                                                                                    |     | ns   |