## SP574B/674B/1674B/774B

# 12-Bit Sampling A/D Converters

- Complete Monolithic 12-Bit A/D Converters with Sample-Hold, Reference, Clock and Tristate Outputs

- Full Nyquist Sampling at All Sample Rates

- Choice of Sampling Rates 40kHz, 66kHz, 100kHz or 125kHz

- Low Power Dissipation 110mW

- 12-Bit Linearity Over Temperature

- Commercial, Industrial and Military Temperature Ranges

- Next–Generation Replacement for 574A, 674A, 1674A, 774A Devices

## **DESCRIPTION...**

The SP574B/674B/1674B/774B (SPx74B) Series are complete 12-bit successive-approximation A/D converters integrated on a single die with tri-state output latches, an internal reference, clock and a sample-hold. The new "B-Series" features true Nyquist sampling while maintaining compatibility with prior versions. They are drop-in replacements for the older 574A/674A/1674A/774A type devices.

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to Digital Common                                       | 0 to +16.5V                        |

|-------------------------------------------------------------------------|------------------------------------|

| Analog Common to Digital Common                                         | ±1V                                |

| Control Inputs to Digital Common (CE, CS, A <sub>0</sub> , 12/8, R/C)   | 0.5V to V <sub>LOGIC</sub> +0.5V   |

| Analog Input Voltage Range                                              | ±FS ±30%                           |

| Analog Inputs to Analog Common<br>(REF IN, BIP OFF, 10V <sub>IN</sub> ) |                                    |

| 20V <sub>IN</sub> to Analog Common                                      | ±24V                               |

| REF OUT                                                                 | Indefinite short to common         |

|                                                                         | Momentary short to V <sub>cc</sub> |

| Power Dissipation                                                       | 1000mW                             |

| Lead Temperature, Soldering                                             |                                    |

| J/C                                                                     |                                    |

| MTBF-25°C Ground Base                                                   |                                    |

| MTBF-125°C Missile Launch                                               |                                    |

CAUTION:

ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

## **SPECIFICATIONS**

(Typical @ 25°C with  $V_{CC}$  = +15V,  $V_{EE}$  = 0V,  $V_{LOGIC}$  = +5V unless otherwise noted.)

| PARAMETER                                                                         | MIN.   | TYP.                   | MAX.                   | UNIT        | CONDITIONS                 |

|-----------------------------------------------------------------------------------|--------|------------------------|------------------------|-------------|----------------------------|

| RESOLUTION                                                                        |        |                        |                        |             |                            |

| All models                                                                        |        |                        | 12                     | Bits        |                            |

| ANALOG INPUTS                                                                     |        |                        |                        |             |                            |

| Input Ranges                                                                      |        |                        |                        |             |                            |

| Bipolar                                                                           |        | ±5, ±10                |                        | V           |                            |

| Unipolar                                                                          | 0 to   | +10, 0 to              | +20                    | V           |                            |

| Input Impedance                                                                   |        |                        |                        |             |                            |

| SP574B/SP674B                                                                     |        |                        |                        |             |                            |

| 10 Volt Input                                                                     | 3.75   |                        | 6.25                   | kΩ          |                            |

| 20 Volt Input                                                                     | 15     |                        | 25                     | kΩ          |                            |

| SP1674B/SP774B                                                                    |        |                        |                        |             |                            |

| 10 Volt Input                                                                     | 1.875  |                        | 3.125                  | kΩ          |                            |

| 20 Volt Input                                                                     | 7.45   |                        | 12.42                  | kΩ          |                            |

| Nyquist Frequency                                                                 |        |                        |                        |             |                            |

| SP574B                                                                            |        | 20                     |                        | kHz         |                            |

| SP674B                                                                            |        | 33                     |                        | kHz         |                            |

| SP1674B                                                                           |        | 50                     |                        | kHz         |                            |

| SP774B                                                                            |        | 62.5                   |                        | kHz         |                            |

| DIGITAL INPUTS                                                                    | _      |                        |                        |             |                            |

| Logic Inputs CE, $\overline{\text{CS}}$ R/ $\overline{\text{C}}$ , A <sub>O</sub> | , 12/8 |                        |                        |             |                            |

| Logic 1                                                                           | +2.4   |                        | +5.5                   | V           |                            |

| Logic 0                                                                           | -0.3   |                        | +0.8                   | V           |                            |

| Current                                                                           |        | ±0.1                   | ±50                    | μΑ          | -0.3V to +5.5V Input       |

|                                                                                   |        | _                      | ±5                     | μ <u>A</u>  | 0V to +5.5V Input          |

| Capacitance                                                                       |        | 5                      |                        | pF          |                            |

| 12/8 Control Input                                                                | Hard   | wire to V <sub>L</sub> | <sub>OGIC</sub> or DIG | ITAL COMMON |                            |

| DIGITAL OUTPUTS                                                                   |        |                        |                        |             |                            |

| Logic Outputs DB <sub>11</sub> –DB <sub>0</sub> , ST                              | S      |                        |                        |             |                            |

| Logic 1                                                                           | +2.4   |                        |                        | V           | $I_{SOURCE} \le 500 \mu A$ |

| Logic 0                                                                           |        |                        | +0.4                   | V           | I <sub>SINK</sub> ≤ 1.6mA  |

| Leakage (High Z State)                                                            |        |                        | ±40                    | μA          | Data bits only             |

| Capacitance                                                                       |        | 5                      |                        | pF          |                            |

| Parallel Data Output Codes                                                        |        | l<br>                  | !                      |             |                            |

| Unipolar                                                                          |        | tive true b            |                        |             |                            |

| Bipolar                                                                           | Positi | ve true of             | fset binary            |             |                            |

| INTERNAL REFERENCE                                                                |        |                        |                        |             |                            |

| Output Voltage                                                                    |        |                        | 10.00 ±0.1             | V           |                            |

| Output Current                                                                    |        | 2                      |                        | mA          | Note 1                     |

|                                                                                   |        |                        |                        |             |                            |

|                                                                                   |        |                        |                        |             |                            |

<sup>\*</sup>Inputs exceeding +30% or -30% of FS will cause erratic performance.

## **SPECIFICATIONS** (continued)

(Typical @ 25°C with  $V_{CC}$  = +15V,  $V_{EE}$  = 0V,  $V_{LOGIC}$  = +5V unless otherwise noted.)

| PARAMETER                    | MIN.   | TYP. | MAX.         | UNIT       | CONDITIONS                                                                                                               |

|------------------------------|--------|------|--------------|------------|--------------------------------------------------------------------------------------------------------------------------|

| CONVERSION TIME              |        |      |              |            |                                                                                                                          |

| SP574B                       |        |      |              |            |                                                                                                                          |

| 12–Bit Conversion            | 13     |      | 25           | μs         |                                                                                                                          |

| 8–Bit Conversion             | 10     |      | 19           | μs         |                                                                                                                          |

| SP674B<br>12–Bit Conversion  | 9      |      | 15           | μs         |                                                                                                                          |

| 8–Bit Conversion             | 6      |      | 11.2         | μs         |                                                                                                                          |

| SP1674B                      |        |      |              | ,          |                                                                                                                          |

| 12-Bit Conversion            | 5      |      | 10           | μs         |                                                                                                                          |

| 8-Bit Conversion             | 4      |      | 7.6          | μs         |                                                                                                                          |

| SP774B                       |        |      |              |            |                                                                                                                          |

| 12–Bit Conversion            | 4<br>3 |      | 8<br>6       | μs         |                                                                                                                          |

| 8–Bit Conversion  ACCURACY   | 3      |      | 0            | μs         |                                                                                                                          |

|                              |        |      |              |            |                                                                                                                          |

| Linearity Error –A, –J, –S   |        |      | ±1.0         | LSB        | @ 25°C and T to T                                                                                                        |

| -A, -3, -3<br>-В, -К, -Т     |        |      | ±0.5         | LSB        | <ul><li>@ 25°C and T<sub>MIN</sub> to T<sub>MAX</sub></li><li>@ 25°C and T<sub>MIN</sub> to T<sub>MAX</sub></li></ul>    |

| Differential Linearity Error |        |      | 0.0          |            | Note 2                                                                                                                   |

| -A, -J, -S                   | 11     |      |              | Bits       | @ 25°C                                                                                                                   |

|                              | 11     |      |              | Bits       | T <sub>MIN</sub> to T <sub>MAX</sub><br>@ 25°C                                                                           |

| –В, –К, –Т                   | 12     |      |              | Bits       | @ 25°C                                                                                                                   |

| Officet                      | 12     |      |              | Bits       | T <sub>MIN</sub> to T <sub>MAX</sub><br>Note 3                                                                           |

| Offset<br>Unipolar           |        | ±3   |              | LSB        | Note 3                                                                                                                   |

| Bipolar                      |        |      |              | LOD        |                                                                                                                          |

| -A, -J, -S                   |        | ±10  |              | LSB        |                                                                                                                          |

| −B, −K, −T                   |        | ±4   |              | LSB        |                                                                                                                          |

| Full Scale (Gain) Error      |        |      |              |            | % of full scale; $T_{MIN}$ to $T_{MAX}$                                                                                  |

|                              |        |      | ±0.3         | %FS        | Note 4                                                                                                                   |

| _A                           |        |      | ±0.6<br>±0.3 | %FS<br>%FS | No adjustment @ 25°C<br>With adjustment @ 25°C                                                                           |

| –В                           |        |      | ±0.3         | %FS        | No adjustment @ 25°C                                                                                                     |

|                              |        |      | ±0.15        | %FS        | With adjustment @ 25°C                                                                                                   |

| _J                           |        |      | ±0.5         | %FS        | No adjustment @ 25°C                                                                                                     |

|                              |        |      | ±0.22        | %FS        | With adjustment @ 25°C                                                                                                   |

| _K                           |        |      | ±0.4         | %FS        | No adjustment @ 25°C                                                                                                     |

| <b>-</b> S                   |        |      | ±0.12        | %FS<br>%FS | With adjustment @ 25°C                                                                                                   |

| _3                           |        |      | ±0.8<br>±0.5 | %FS        | No adjustment @ 25°C<br>With adjustment @ 25°C                                                                           |

| _T                           |        |      | ±0.6         | %FS        | No adjustment @ 25°C                                                                                                     |

|                              |        |      | ±0.25        | %FS        | With adjustment @ 25°C                                                                                                   |

| STABILITY                    |        |      |              |            | -                                                                                                                        |

| Unipolar Offset              |        |      |              |            |                                                                                                                          |

| _J                           |        |      | ±10          | ppm/°C     | $\begin{array}{c} T_{MIN} \text{ to } T_{MAX} \\ T_{MIN} \text{ to } T_{MAX} \\ T_{MIN} \text{ to } T_{MAX} \end{array}$ |

| -K, -A, -S                   |        |      | ±5           | ppm/°C     | I <sub>MIN</sub> to T <sub>MAX</sub>                                                                                     |

| –B, –T<br>Bipolar Offset     |        |      | ±2.5         | ppm/°C     | I MIN TO I MAX                                                                                                           |

| –J, –A, –S                   |        |      | ±10          | ppm/°C     | $\underline{T}_{MIN}$ to $\underline{T}_{MAX}$                                                                           |

| −K, −B, −T                   |        |      | ±5           | ppm/°C     | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                     |

| Gain (Scale Factor)          |        |      |              |            |                                                                                                                          |

| -J, -A, -S                   |        |      | ±50          | ppm/°C     | $\underline{T}_{MIN}$ to $\underline{T}_{MAX}$                                                                           |

| −K, −B, −T                   |        |      | ±25          | ppm/°C     | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                     |

|                              |        |      |              |            |                                                                                                                          |

|                              |        |      |              |            |                                                                                                                          |

|                              |        |      |              |            |                                                                                                                          |

|                              |        |      |              |            |                                                                                                                          |

|                              |        |      |              |            |                                                                                                                          |

## **SPECIFICATIONS** (continued)

(Typical @ 25°C with  $V_{CC}$  = +15V,  $V_{EE}$  = 0V,  $V_{LOGIC}$  = +5V unless otherwise noted.)

| PARAMETER                    | MIN.        | TYP. | MAX.             | UNIT | CONDITIONS |

|------------------------------|-------------|------|------------------|------|------------|

| POWER REQUIREMENTS           |             |      |                  |      |            |

| V <sub>LOGIC</sub>           | +4.5        |      | +5.5             | V    |            |

| I <sub>LOGIC</sub><br>SP574B |             | 1    | 3                | mA   |            |

| SP674B                       |             | 1    | 3                | mA   |            |

| SP1674B                      |             | 1    | 3<br>3<br>3<br>3 | mA   |            |

| SP774B                       |             | 1    | 3                | mA   |            |

| V <sub>CC</sub>              | +11.4       |      | +16.5            | V    |            |

| SP574B                       |             | 7    | 9                | mA   |            |

| SP674B                       |             | 7    | 9                | mA   |            |

| SP1674B                      |             | 10   | 12.5             | mA   |            |

| SP774B                       |             | 10   | 12.5             | mA   |            |

| POWER DISSIPATION            |             |      |                  |      |            |

| SP574B                       |             | 110  | 150              | mW   |            |

| SP674B                       |             | 110  | 150              | mW   |            |

| SP1674B                      |             | 155  | 200              | mW   |            |

| SP774B                       |             | 155  | 200              | mW   |            |

| ENVIRONMENTAL                |             |      |                  |      |            |

| Operating Temperature Rang   | е           |      |                  |      |            |

| –J, –K                       | 0           |      | +70              | °C   |            |

| –A, –B                       | -40         |      | +85              | °C   |            |

| -S, -T                       | <b>-</b> 55 |      | +125             | °C   |            |

| Storage Temperature Range    | 40          |      | . 0.5            | .~   |            |

| -J, -K                       | -40<br>65   |      | +85              | °C   |            |

| –A, –B, –S, −T               | -65         |      | +150             | °C   |            |

#### Notes:

- Available for external loads. External load should not change during conversion. When supplying an

external load and operating on a +12V supply, a buffer amplifier must be provided for the reference

output.

- 2. Minimum resolution for which no missing codes are guaranteed.

- 3. Externally adjustable to zero. See *Calibration* information.

- 4. Fixed  $50\Omega$  resistor between REF OUT and REF IN.

- 5. Specifications are identical for all models unless otherwise noted.

| TYPICAL AC DYNAMICS                |        |        |         |        |      |  |  |

|------------------------------------|--------|--------|---------|--------|------|--|--|

| Measurement/Model                  | SP574B | SP674B | SP1674B | SP774B | Unit |  |  |

| Test Conditions:                   |        |        |         |        |      |  |  |

| Sampling Rate                      | 40     | 67     | 100     | 125    | kHz  |  |  |

| Input Frequency (F <sub>IN</sub> ) | 19     | 31     | 49      | 61     | kHz  |  |  |

| SFDR                               | 90     | 85     | 80      | 77     | dB   |  |  |

| THD                                | -80    | -80    | -77     | -76    | dB   |  |  |

| SINAD                              | 72     | 72     | 71      | 71     | dB   |  |  |

| SNR                                | 72.5   | 72.5   | 72.5    | 72.5   | dB   |  |  |

#### Note:

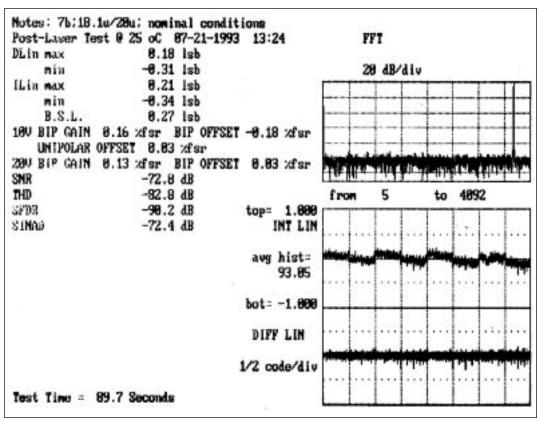

1. Refer to Figure 10, for typical FFT at Nyquist sampling rate.

#### PIN ASSIGNMENTS...

| PIN | FUNCTION          | PIN | FUNCTION               |

|-----|-------------------|-----|------------------------|

| 1   | $V_{LOGIC}$       | 28  | STS                    |

| 2   | 12/8              | 27  | DB <sub>11</sub> (MSB) |

| 3   | <del>CS</del>     | 26  | DB <sub>10</sub>       |

| 4   | A <sub>o</sub>    | 25  | $DB_9$                 |

| 5   | R/C               | 24  | DB <sub>8</sub>        |

| 6   | CE                | 23  | DB <sub>7</sub>        |

| 7   | V <sub>cc</sub>   | 22  | DB <sub>6</sub>        |

| 8   | REF OUT           | 21  | DB <sub>5</sub>        |

| 9   | ANA GND(AC)       | 20  | $DB_4$                 |

| 10  | REF IN            | 19  | DB <sub>3</sub>        |

| 11  | N/C*              | 18  | DB <sub>2</sub>        |

| 12  | BIP OFF           | 17  | DB <sub>1</sub>        |

| 13  | 10V <sub>IN</sub> | 16  | DB <sub>0</sub> (LSB)  |

| 14  | 20V <sub>IN</sub> | 15  | DIG. GND               |

\*This pin is not connected inside the device so it can be tied to -15V, ground, or left floating.

## FEATURES...

The **SPx74B Series** feature standard bipolar and unipolar input ranges of 10V and 20V. Input ranges are controlled by a bipolar offset pin and laser-trimmed for specified linearity, gain and offset accuracy. Power requirements are +5V and +12V to +15V with a maximum dissipation of 150mW at the specified voltages. Conversion times of  $8\mu s$ ,  $10\mu s$ ,  $15\mu s$  and  $25\mu s$  are available, as are units with 10, 25 or 50ppm/°C temperature coefficients for flexible matching to specific application requirements.

The **SPx74B Series** are available in nine product grades for each conversion time. The –J and –K models are specified over 0°C to + 70°C commercial temperature range; the –A and –B models are specified over the –40°C to +85°C industrial temperature range; the –S and –T models are specified over the –55°C to +125°C military temperature range. Package options include 28–pin CDIP, 28–pin plastic DIP (both narrow and wide), 28-pin PLCC and 28–pin SOIC.

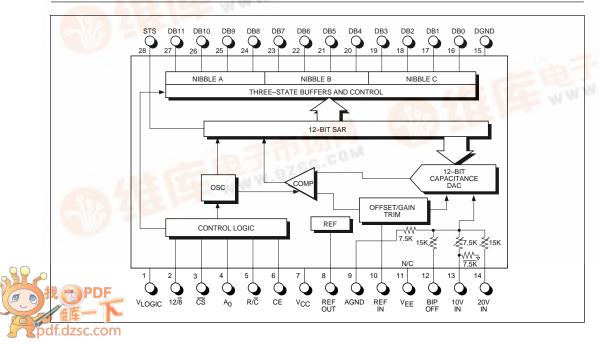

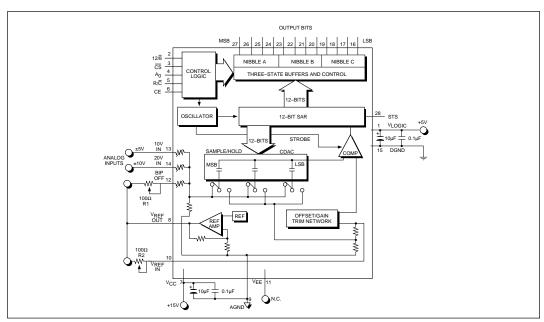

#### CIRCUIT OPERATION...

The **SPx74B** are complete monolithic capacitor DAC-based 12-bit analog-to-digital converters with integral voltage reference, comparator, successive—approximation register (SAR), sample—and—hold, clock, output buffers and control circuitry. The high level of integration of the **SPx74B Series** means they require few external components.

When the control section of the **SPx74B** initiates a conversion command, the clock is enabled and the successive–approximation register is reset to all zeros. Once the conversion cycle begins, it can not be stopped or restarted and data is not available from the output buffers. The SAR, timed by the clock, sequences through the conversion cycle and returns an end–of–convert flag to the control section of the ADC. The clock is then disabled by the control section, the output status goes low, and the control section is enabled to allow the data to be read by external command.

The internal **SPx74B** 12–bit CDAC is sequenced by the SAR starting from the MSB to the LSB at the beginning of the conversion cycle to provide an output voltage from the CDAC that is equal to the input signal voltage (which is divided by the input voltage divider network). The comparator determines whether the addition of each successively–weighted bit voltage causes the CDAC output voltage summation to be greater or less than the input voltage; if the sum is less, the bit is left on; if more, the bit is turned off. After testing all the bits, the SAR contains a 12–bit binary code which accurately represents the input signal to within  $\pm \frac{1}{2}$  LSB.

The internal reference provides the voltage reference to the CDAC with excellent stability over temperature and time. The reference is trimmed to  $10.00 \, \text{Volts} \pm 1\%$  and can supply up to  $2 \, \text{mA}$  to an external load in addition to that required to drive the reference input resistor ( $1 \, \text{mA}$ ) and offset resistor ( $1 \, \text{mA}$ ) when operating with  $\pm 15 \, \text{V}$  supplies. If the  $\mathbf{SPx74B}$  is used with  $\pm 12 \, \text{V}$  supplies, or if external current must be supplied over the full temperature range, an external buffer amplifier is recommended. Any external load on the  $\mathbf{SPx74B}$  reference must remain constant during conversion.

#### SAMPLE-AND-HOLD FUNCTION

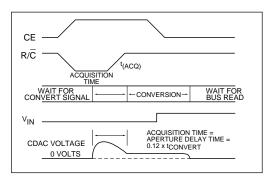

Although there is no sample–and–hold circuit in the classical sense, the sampling nature of the capacitive DAC makes the SPx74B appear to have a built–in sample–and–hold. The sample–and–hold function of the CDAC architecture is optimized to provide full Nyquist sampling at any maximum sampling rate. Because the S/H function is included in the ADC circuitry, the majority of the S/H specifications are included within the A/D specifications.

Note that some system architectures may use an external sample—and—hold. The built—in S/H function of the SPx74B will provide additional isolation. Once the internal sample is taken by the CDAC capacitance, the input of the **SPx74B** is disconnected from the input. This prevents transients occurring during conversion from being inflicted upon the attached buffer. All other 574/ 674-type circuits will cause a transient load current on the input which will upset the buffer output and may add error to the conversion itself. In addition, the isolation of the input after the acquisition time in the SPx74B allows you the opportunity to release the HOLD on an external sample and-hold and start it tracking the next sample. This will increase system throughput with your existing components.

When using an external S/H, the **SPx74B** acts as any other 574–type device because the internal S/H is transparent. The sample/hold function in the **SPx74B** is inherent to the capacitor DAC structure, and its timing characteristics are determined by the internally generated clock. However, for multiplexer operation, the internal S/H may eliminate the need for an external S/H. The operation of the S/H function is internal to the **SPx74B** and is

Figure 1. Sample-and-Hold Function

controlled through the normal  $R/\overline{C}$  control line (refer to Figure 1). When the  $R/\overline{C}$  line makes a negative transition, the SPx74B starts the timing of the sampling and conversion. The first two clock cycles are allocated to signal acquisition of the input by the CDAC (this time is defined as  $t_{ACO}$ ). Following these two cycles, the input sample is taken and held. The A/D conversion follows this cycle with the duration controlled by the internal clock cycle, which is determined by the specific product model. Note that because the sample is taken relative to the R/C transition,  $t_{ACO}$  is also the traditional "aperture delay" of this internal sample and hold. Since  $t_{ACO}$  is measured in clock cycles, its duration will vary with the internal clock frequency.

Offset, gain and linearity errors of the S/H circuit, as well as the effects of its droop rate, are included in the overall specs for the **SPx74B**.

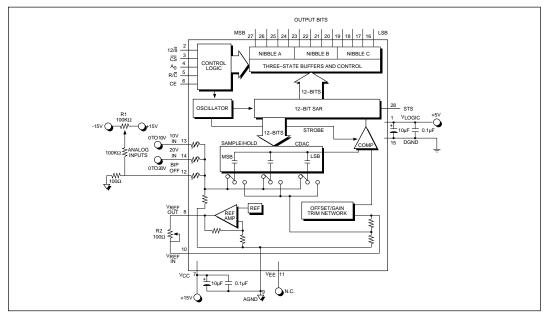

# USING THE SPX74B SERIES Typical Interface Circuit

The **SPx74B** is a complete A/D converter that is fully operational when powered up and issued a Start Convert Signal. Only a few external components are necessary. The **SPx74B Series** have four standard input ranges: 0V to +10V, 0V to +20V, ±5V and ±10V. *Figure 2* depicts a typical interface circuit for operating the **SPx74B** in a unipolar input mode. *Figure 3* depicts a typical interface circuit for operating the **SPx74B** in a bipolar input mode. Further information is given in the following sections on these connections, but first a few considerations concerning board layout to achieve the best operation.

For each application of this device, strict attention must be given to power supply decoupling, board layout (to reduce pickup between analog and digital sections), and grounding. Digital timing, calibration and the analog signal source must be considered for correct operation.

To achieve specified accuracy, a double–sided printed circuit board with a copper ground plane on the component side is recommended. Keep analog signal traces away from digital lines. It is best to lay the PC board out such that there is an analog section and a digital section with a single point ground connection between the two through an RF bead. If this is not possible, run analog

Figure 2. Unipolar Input Connections

signals between ground traces and cross digital lines at right angles only.

## **Grounding Considerations**

Any ground path from the analog and digital ground should be as low resistance as possible to accommodate the ground currents present with this device.

The analog ground current is approximately 6mA DC while the digital ground is 3mA DC. The analog and digital common pins should be tied together as close to the package as possible to guarantee best performance. The code–dependent currents flow through the  $V_{\rm LOGIC}$  and  $V_{\rm CC}$  terminals and not through the analog and digital common pins.

## **Power Supplies**

The supply voltages for the **SPx74B** must be kept as quiet as possible from noise pickup and also regulated from transients or drops. Because the part has 12–bit accuracy, voltage spikes on the supply lines can cause several LSB deviations on the output. Switching power supply noise can be a problem. Careful filtering and shielding should be employed to prevent the noise from being picked up by the converter.

Capacitor bypass pairs are needed from each supply pin to its respective ground to filter noise and counter the problems caused by the variations in supply current. A  $10\mu F$  tantalum and a  $0.1\mu F$  ceramic type in parallel between  $V_{LOGIC}$  (pin 1) and digital common (pin15), and  $V_{CC}$  (pin 7) and analog common (pin 9) is sufficient.  $V_{EE}$  is generated internally so pin 11 may be grounded or connected to a negative supply if the SPx74B is being used to upgrade an already existing design.

# CALIBRATION AND CONNECTION PROCEDURES

## Unipolar

The calibration procedure consists of adjusting the converter's most negative output to its ideal value for offset adjustment, and then adjusting the most positive output to its ideal value for gain adjustment.

Starting with offset adjustment and referring to *Figure 2*, the midpoint of the first LSB increment should be positioned at the origin to get an output code of all 0s. To do this, an input of  $+\frac{1}{2}$  LSB or +1.22mV for the 10V range and +2.44mV for the 20V range should be applied to the **SPx74B**. Adjust the offset potentiometer R<sub>1</sub> for code transition flickers between 0000 0000 0000 and 0000 0000 0001.

The gain adjustment should be done at positive full scale. The ideal input corresponding to the last code change is applied. This is  $1\frac{1}{2}LSB$  below the nominal full scale which is +9.9963V for the 10V range and +19.9927V for the 20V range. Adjust the gain potentiometer  $R_2$  for flicker between codes  $1111\ 1111\ 1110$  and  $1111\ 1111\ 1111$ . If calibration is not necessary for the intended application, replace  $R_2$  with a  $50\Omega$ , 1% metal film resistor and remove the network analog input to pin 13 for the 0V to 10V range or to pin 14 for the 0V to 20V range.

## **Bipolar**

The gain and offset errors listed in the specifications may be adjusted to zero using the potentiometers  $R_1$  and  $R_2$  (See *Figure 3*). If adjustment is not needed, either or both pots may be replaced by a  $50\Omega$ , 1% metal film resistor.

To calibrate, connect the analog input signal to pin 13 for a  $\pm 5$ V range or to pin 14 for a  $\pm 10$ V range. First apply a DC input voltage  $\frac{1}{2}$  LSB above negative full scale which is -4.9988V for the  $\pm 5$ V range or -9.9976V for the  $\pm 10$ V range. Adjust the offset potentiometer R<sub>1</sub> for flicker between output codes  $0000\,0000\,0000\,0000\,0000\,0000\,0001$ . Next, apply a DC input voltage  $1\frac{1}{2}$  LSB below positive full scale which is +4.9963V for the  $\pm 5$  range or

$\pm 9.9927$ V for the  $\pm 10$ V range. Adjust the gain potentiometer R<sub>2</sub> for flicker between codes 1111 1110 and 1111 1111 1111.

#### Alternative

The  $100\Omega$  potentiometer  $R_2$  provides gain adjust for 10V and 20V ranges. In some applications, a full scale of 10.24V (for and LSB of 2.5mV) or 20.48 (for an LSB of 5.0mV) is more convenient. For these, replace  $R_2$  by a  $50\Omega$ , 1% metal film resistor. Then to provide gain adjust for the 10.24 range, add a  $200\Omega$  potentiometer in series with pin 13. For the 20.48V range, add a  $1000\Omega$  potentiometer in series with pin 14.

#### **CONTROLLING THE SPx74B**

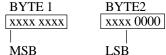

The **SPx74B** can be operated by most microprocessor systems due to the control input pins and on–chip logic. It may also be operated in the "stand–alone" mode and enabled by the  $R/\overline{C}$  input pin. Full microprocessor control consists of selecting an 8– or 12–bit conversion cycle, initiating the conversion, and reading the output data when ready. The output read has the options of choosing either 12–bits at once or 8–bits followed by 4–bits in a left–justified format. All five control inputs are TTL/CMOS compatible and include  $12/\overline{8}$ ,  $\overline{CS}$ ,  $A_0$ ,  $R/\overline{C}$  and CE. The use of these inputs in controlling the converter's operation is

Figure 3. Bipolar Input Connections

shown in *Table 1*, and the internal control logic is shown in a simplified schematic in *Figure 4*.

#### Conversion Start

A conversion may be initiated by a logic transition on any of the three inputs: CE,  $\overline{\text{CS}}$  R/ $\overline{\text{C}}$ , as shown in *Table* 1. The last of the three to reach the correct state starts the conversion, so one, two or all three may be dynamically controlled. The nominal delay from each is the same and all three may change state simultaneously. In order to assure that a particular input controls the start of conversion, the other two should be setup at least 50ns earlier. Refer to the convert mode timing specifications. The Convert Start timing diagram is shown in *Figure* 6.

The output signal STS is the status flag and goes high only when a conversion is in progress. While STS is high, the output buffers remain in a high impedance state so that data can not be read. Also, when STS is high, an additional Start Convert will not reset the converter or reinitiate a conversion. Note, if  $A_0$  changes state after a conversion begins, an additional Start Convert command will latch the new state of  $A_0$  and possibly cause a wrong cycle length for that conversion (8–versus 12–bits).

| CE      | cs | R/C | 12/8 | A <sub>o</sub> | OPERATION                                |

|---------|----|-----|------|----------------|------------------------------------------|

| 0       | х  | х   | х    | х              | None                                     |

| х       | 1  | х   | х    | х              | None                                     |

| <u></u> | 0  | 0   | х    | 0              | Initiate 12–Bit Conversion               |

| <u></u> | 0  | 0   | х    | 1              | Initiate 8–Bit Conversion                |

| 1       | Ł  | 0   | х    | 0              | Initiate 12–Bit Conversion               |

| 1       | Ł  | 0   | х    | 1              | Initiate 8–Bit Conversion                |

| 1       | 0  | Ŧ   | х    | 0              | Initiate 12–Bit Conversion               |

| 1       | 0  | ٦   | х    | 1              | Initiate 8–Bit Conversion                |

| 1       | 0  | 1   | 1    | х              | Enable 12–Bit Output                     |

| 1       | 0  | 1   | 0    | 0              | Enable 8 MSB's Only                      |

| 1       | 0  | 1   | 0    | 1              | Enable 4 LSB's plus 4<br>Trailing Zeroes |

Table 1. SPx74B Control Input Truth Table

#### Conversion Length

A conversion start transition latches the state of  $A_0$  as shown in *Figure 4* and *Table 1*. The latched state determines if the conversion stops with 8–bits ( $A_0$  high) or continues for 12–bits ( $A_0$  low). If all 12–bits are read following an 8–bit conversion, the three LSB's will be a logic "0" and DB<sub>3</sub> will be a logic "1".  $A_0$  is latched because it is also involved in enabling the output buffers as explained elsewhere. No other control inputs are latched.

## Stand-Alone Operation

The simplest interface is a control line connected to  $R/\overline{C}$ . The other controls must be tied to known states as follows: CE and  $12/\overline{8}$  are wired high,  $A_0$  and  $\overline{CS}$  are wired low. The output data arrives in words of 12–bits each. The limits on  $R/\overline{C}$  duty cycle are shown in *Figures 8* and 9. The duty cycle may be within and including the extremes shown in the specifications. In general, data may be read when  $R/\overline{C}$  is high unless STS is also high, indicating a conversion is in progress.

## **Reading Output Data**

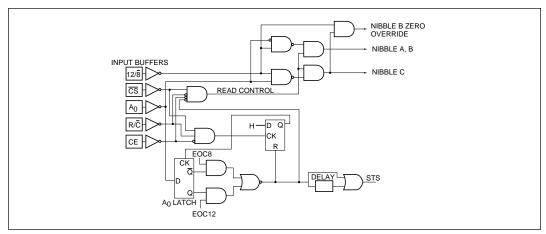

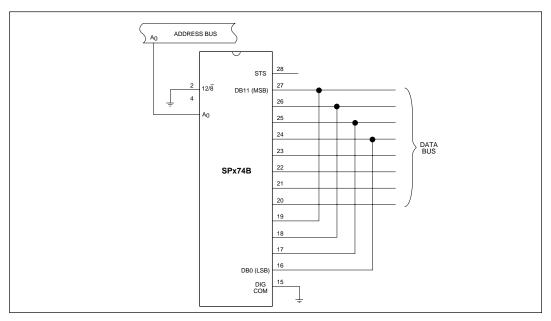

The output data buffers remain in a high impedance state until the following four conditions are met:  $R/\overline{C}$  is high, STS is low, CE is high and  $\overline{CS}$  is low. The data lines become active in response to these four conditions, and output data according to the conditions of the control lines  $12/\overline{8}$  and  $A_0$ . The timing diagram for this process is shown in *Figure 7*. When  $12/\overline{8}$  is high, all 12 data outputs become active simultaneously and the  $A_0$  input is ignored. The  $12/\overline{8}$  input is usually tied high or low; it is TTL/CMOS compatible. When  $12/\overline{8}$  is low, the output is separated into two 8-bit bytes as shown below:

This configuration makes it easy to connect to an 8—bit data bus as shown in Figure 5. The  $A_0$  control can be connected to the least significant bit of the address bus in order to store the output data into two consecutive memory locations. When  $A_0$  is pulled low, the 8 MSB's are enabled only. When  $A_0$  is high, the 8 MSB's are disabled, bits 4 through 7 are forced to a zero and the four LSB's are enabled. The two byte format is "left justified data" as shown above and can be considered to have a decimal point or binary to the left of byte 1.

A<sub>0</sub> may be toggled without damage to the converter at any time. Break-before-make action is guaranteed between the two data bytes. This assures that the outputs which are strapped together in *Figure 5* will never be enabled at the same time.

In *Figure 7*, it can be seen that a read operation usually begins after the conversion is complete and STS is low. If earlier access is needed, the read can begin no later than the addition of times  $t_{\rm DD}$  and  $t_{\rm HS}$  before STS goes low.

#### "NYQUIST" SAMPLING

Each of the **SPx74B** analog-to-digital converters has been designed to provide Nyquist sampling (highest input frequency is 1/2 of the sampling rate) data conversion with no degradation in DC performance. This is shown in Figure 10. Note that the Differential Linearity and Integral Linearity min/max values are well within the  $\pm$  1/2 LSB limits of a K-version Converter. Also, the Typical FFT at Nyquist rates shown on Figure 10 reflect the values listed in the Typical AC Dynamics table.

Figure 4. SPx74B Control Logic

Figure 5. Interfacing SPx74B to 8-Bit Interface Bus

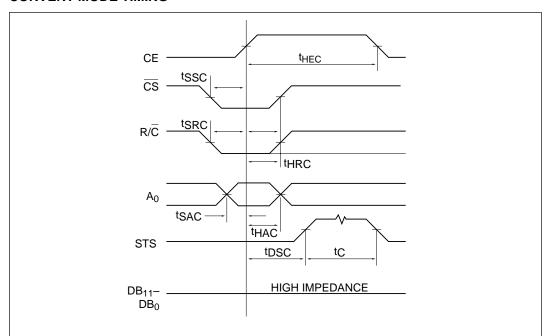

## **CONVERT MODE TIMING**

## **CHARACTERISTICS**

Typical @  $25^{\circ}$ C,  $V_{CC} = +15$ V or +10V,  $V_{LOGIC} = +5$ V,  $V_{EE} = 0$ V, unless otherwise specified.

| PARAMETER                                            | MIN. | TYP.          | MAX. | UNITS | CONDITIONS |

|------------------------------------------------------|------|---------------|------|-------|------------|

| t <sub>DSC</sub> STS Delay from CE                   |      |               | 200  | ns    |            |

| t <sub>HEC</sub> CE Pulse Width                      | 50   |               |      | ns    |            |

| t <sub>SSC</sub> CS to CE Setup                      | 50   |               |      | ns    |            |

| t <sub>HSC</sub> CS Low during CE High               | 50   |               |      | ns    |            |

| t <sub>SRC</sub> R/C to CE Setup                     | 50   |               |      | ns    |            |

| t <sub>HRC</sub> R/C Low during CE High              | 50   |               |      | ns    |            |

| t <sub>SAC</sub> A <sub>0</sub> to CE Setup          | 0    |               |      | ns    |            |

| t <sub>HAC</sub> A <sub>0</sub> Valid during CE High | 50   |               |      | ns    |            |

| t <sub>C</sub> Conversion Time <sup>1, 3, 4</sup>    | See  | specification | ons  |       |            |

## NOTES:

- Parameters guaranteed by design and sample tested. Parameters 100% tested @ 25°C on special orders. 1.

- 2.

- 3. 100% tested.

- $\rm T_{\rm min}$  to  $\rm T_{\rm max}$ 4.

Figure 6. Convert Mode Timing

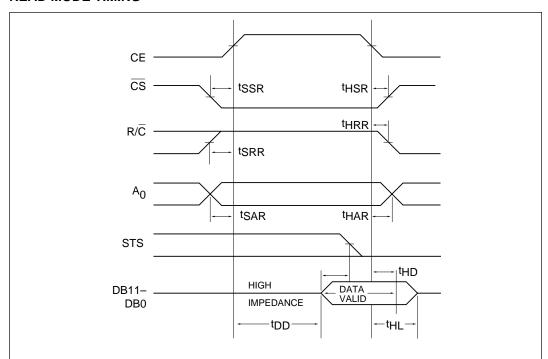

## **READ MODE TIMING**

## **CHARACTERISTICS**

Typical @  $25^{\circ}$ C,  $V_{cc} = +15$ V or +12V,  $V_{LOGIC} = +5$ V,  $V_{EE} = 0$ V, unless otherwise specified.

|                  | PARAMETER                            | MIN. | TYP. | MAX. | UNITS | CONDITIONS |

|------------------|--------------------------------------|------|------|------|-------|------------|

| t <sub>DD</sub>  | Access Time From CE <sup>2</sup>     |      |      | 150  | ns    |            |

| t <sub>HD</sub>  | Data Valid After CE Low <sup>2</sup> | 25   |      |      | ns    |            |

| t <sub>HL</sub>  | Output Float Delay <sup>2</sup>      |      |      | 150  | ns    |            |

| tssr             | CS to CE Setup                       | 50   | 0    |      | ns    |            |

| t <sub>SRR</sub> | R/C to CE Setup                      | 0    | 0    |      | ns    |            |

| t <sub>SAR</sub> | A <sub>0</sub> to CE Setup           | 50   |      |      | ns    |            |

| t <sub>HSR</sub> | CS Valid After CE Low                | 0    | 0    |      | ns    |            |

| tHRR             | R/C High After CE Low                | 0    | 50   |      | ns    |            |

| t <sub>HAR</sub> | A <sub>0</sub> Valid After CE Low    | 50   |      |      | ns    |            |

| t <sub>HS</sub>  | STS Delay After Data Valid           | 300  |      | 1000 | ns    |            |

## NOTES:

- Parameters guaranteed by design and sample tested. Parameters 100% tested @ 25°C on special orders. 1.

- 2.

Figure 7. Read Mode Timing

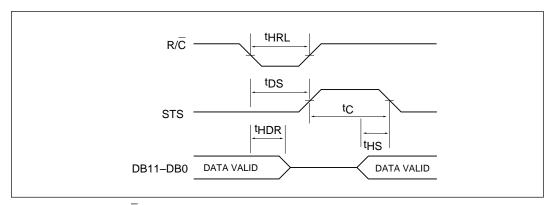

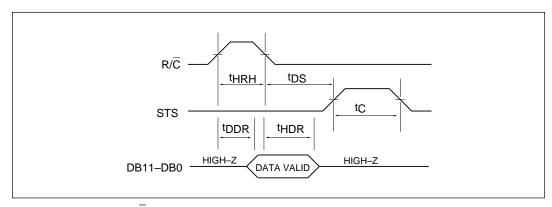

## STAND-ALONE MODE TIMING CHARACTERISTICS

Typical @  $25^{\circ}$ C,  $V_{CC}$ = +15V or +12V,  $V_{LOGIC}$  = +5V,  $V_{EE}$  =0V, unless otherwise specified.

| PARAMETER                                               | MIN. | TYP. | MAX. | UNITS | CONDITIONS |

|---------------------------------------------------------|------|------|------|-------|------------|

| t <sub>HRL</sub> Low R/C Pulse Width <sup>2</sup>       | 50   |      |      | ns    |            |

| t <sub>DS</sub> STS Delay from R/C <sup>2</sup>         |      |      | 200  | ns    |            |

| t <sub>HDR</sub> Data Valid After R/C Low <sup>2</sup>  |      | 25   |      | ns    |            |

| t <sub>HS</sub> STS Delay After Data Valid <sup>2</sup> | 300  |      | 1000 | ns    |            |

| t <sub>HRH</sub> High R/C Pulse Width                   | 150  |      |      | ns    |            |

| t <sub>DDR</sub> Data Access Time                       |      |      | 150  | ns    |            |

## NOTES:

- Parameters guaranteed by design and sample tested. Parameters 100% tested @ 25°C on special orders. 1.

- 2.

Figure 8. Low Pulse for  $R/\overline{C}$  — Outputs Enabled After Conversion

Figure 9. High Pulse For  $R/\overline{C}$  — Outputs Enabled While R/C is High, Otherwise High Impedance

Figure 10. Typical FFT at Nyquist Sampling Rates

| lodel      | Monotonicity | Linearity | Gain TC  | Temperature Range                                | Package Types |

|------------|--------------|-----------|----------|--------------------------------------------------|---------------|

| 5us Conve  | rsion Time   |           |          |                                                  |               |

| P574BJ     | 11 Bits      | ±1.0 LSB  | 50ppm/°C | 0°C to +70°C                                     | L, N, P, S    |

| P574BK     |              | +0.5 LSB  | 25ppm/°C | 0°C to +70°C                                     | I N P S       |

| P574BA     | 11 Bits      | ±1.0 LSB  | 50ppm/°C | -40°C to +85°C<br>-40°C to +85°C                 | L, N, P, S    |

| P574BB     | 12 Bits      | ±0.5 LSB  | 25ppm/°C | 40°C to +85°C                                    | L, N, P, S    |

| P574BS     | 11 Bits      | ±1.0 LSB  | 50ppm/°C | 55°C to +125°C                                   |               |

| P574BT     | 12 Bits      | ±0.5 LSB  | 25ppm/°C | 55°C to +125°C<br>-55°C to +125°C                | C             |

| 5us Conve  | rsion Time   |           |          |                                                  |               |

| P674BJ     | 11 Bits      | ±1.0 LSB  | 50ppm/°C | 0°C to +70°C                                     | L. N. P. S    |

| P674BK     | 12 Bits      | +0.5 LSB  | 25ppm/°C | 0°C to +70°C                                     | L. N. P. S    |

| P674BA     | 11 Bits      | ±1.0 LSB  | 50ppm/°C | -40°C to +85°C<br>-40°C to +85°C                 | L. N. P. S    |

| P674BB     | 12 Bits      | ±0.5 LSB  | 25ppm/°C | 40°C to +85°C                                    | L. N. P. S    |

| P674BS     | 11 Bits      | ±1.0 LSB  | 50ppm/°C | 55°C to +125°C                                   |               |

| P674BT     | 12 Bits      | ±0.5 LSB  | 25ppm/°C | 55°C to +125°C<br>-55°C to +125°C                | C             |

| Ous Conve  | rsion Time   |           |          |                                                  |               |

| D167/B I   | 11 Rite      | +1.0 LSB  | 50nnm/°C | 0°C to +70°C                                     | INPS          |

| P1674BK    |              | +0.5 LSB  | 25ppm/°C | 0°C to +70°C                                     | INPS          |

| P1674BA    | 11 Bits      | +1.0 LSB  | 50ppm/°C | -40°C to +85°C                                   | INPS          |

| P1674BR    | 12 Rits      | +0.5 LSB  | 25nnm/°C | -40°C to +85°C                                   | I N P S       |

| P1674BS    | 11 Bits      | +1.0 LSB  | 50ppm/°C | -55°C to +125°C                                  |               |

| P1674BT    | 12 Bits      | ±0.5 LSB  | 25ppm/°C | 0°C to +70°C                                     |               |

| us Convers |              |           |          |                                                  |               |

| P774B.I    | 11 Rits      | +1.0.LSB  | 50nnm/°C | 0°C to +70°C                                     | INPS          |

| P774BK     | 12 Rits      | +0.5 LSB  | 25nnm/°C | 0°C to +70°C                                     | I N P S       |

| P774BA     | 11 Rits      | +1 0 LSB  | 50nnm/°C | 0°C to +70°C<br>-40°C to +85°C<br>-40°C to +85°C | I N P S       |

| P774BB     | 12 Rits      | +0.5 LSB  | 25nnm/°C | -40°C to +85°C                                   | I N P         |

| P774BS     | 11 Rite      | +1 0 I SB | 50ppm/°C | 55°C to +125°C                                   | ۱۹, ۲, ۲      |

| P774BT     |              | ±0.5 LSB  | 25ppm/°C |                                                  |               |

|            |              |           |          |                                                  |               |

SIGNAL PROCESSING EXCELLENCE

#### Sipex Corporation

Headquarters and Sales Office 22 Linnell Circle

Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

#### Sales Office

233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600