This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

# **SP8643A**

350MHz ÷ 10/11

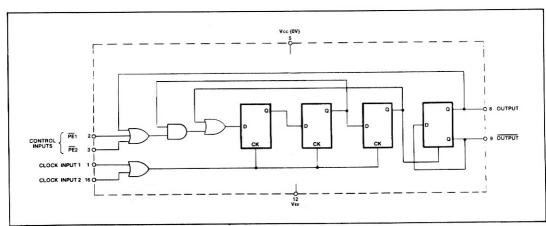

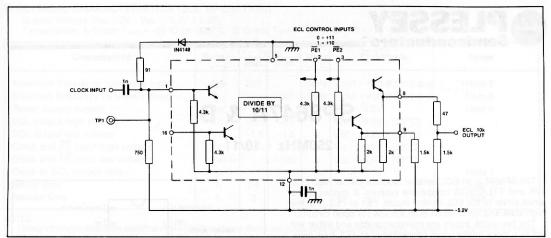

The SP8643 is an ECL variable modulus divider, with ECL 10K compatible outputs. It divides by 10 when either of the ECL control inputs, PE1 or PE2, is in the high state and by 11 when both are low (or open circuit).

The two clock inputs are interchangeable and either will act as a clock inhibit when connected to an ECL high level. Normally, one input is left open circuit and the other is AC coupled, with externally-applied bias.

## **FEATURES**

- ECL Compatible Inputs/Outputs

- AC Coupled Input (External Bias)

## QUICK REFERENCE DATA

- Supply Voltage: -5.2V

- Power Consumption: 260mW

- Temperature Range: -55°C to +125°C

### 16 CLOCK INPUT 2 CLOCK INPUT 1 CONTROL INPUT 1 15 NC CONTROL INPUT 2 14 NC 13 NC NC [ Vcc (OV) 12 VEE 11 DO NOT CONNECT NC [ 10 NC NC [ 9 OUTPUT OUTPUT **DG16**

Fig.1 Pin connections - top view

## **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage            | -8V             |

|---------------------------|-----------------|

| Output current            | 20mA            |

| Storage temperature range | -55°C to +150°C |

| Max. junction temperature | +175°C          |

| Max. clock I/P voltage    | 2.5V p-p        |

Fig.2 Functional diagram

### **ELECTRICAL CHARACTERISTICS**

Supply Voltage: Vcc = 0V VEE = -5.2V ± 0.25V

Temperature: Tamb = -55°C to +125°C

| Characteristic                     | Symbol           | Value |       | Units  | Conditions                     | Notes  |

|------------------------------------|------------------|-------|-------|--------|--------------------------------|--------|

| Characteristic                     | Symbol           | Min.  | Max.  | Office | Office Conditions              | Holes  |

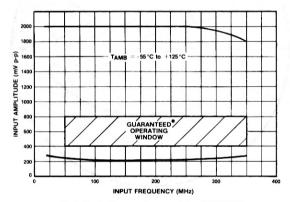

| Maximum frequency (sinewave input) | f <sub>max</sub> | 350   |       | MHz    | Input = 400-800mV p-p          |        |

| Minimum frequency (sinewave input) | fmin             |       | 50    | MHz    | Input = 400-800mV p-p          |        |

| Power supply current               | IEE              |       | 65    | mA     | VEE = -5.2V                    |        |

| ECL output high voltage            | Vон              | -0.85 | -0.7  | V      | V <sub>EE</sub> = -5.2V (25°C) |        |

| ECL output low voltage             | Vol              | -1.8  | -1.5  | V      | VEE = -5.2V (25°C)             | . 27   |

| PE input high voltage              | VINH             | -0.93 |       | V      | VEE = -5.2V (25°C)             |        |

| PE input low voltage               | VINL             |       | -1.62 | V      | VEE = -5.2V (25°C)             |        |

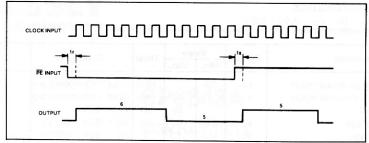

| Clock to ECL output delay          | t <sub>p</sub>   |       | 6     | ns     |                                | Note 6 |

| Set-up time                        | ts               | 2.5   |       | ns     | - 190 v (p- 10 v)              | Note 6 |

| Release time                       | tr               | 3     |       | ns     |                                | Note 6 |

#### NOTES

- 1. Unless otherwise stated, the electrical characteristics shown above are guaranteed over specified supply, frequency and temperature range.

- 2. The temperature coefficient of VoH = +1.63mV/°C, VoL = +0.94mV/°C and of VIN = +1.22mV/°C but these are not tested.

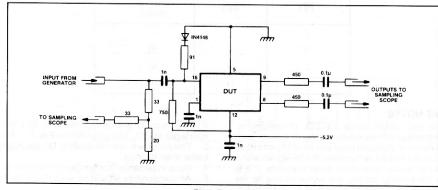

- 3. The test configuration for dynamic testing is shown in Fig.6.

- The set up time t<sub>s</sub> is defined as minimum time that can elapse between L → H transition of control input and the next L → H clock pulse transition to ensure that +10 is obtained.

- The release time tris defined as the minimum time that can elapse between H → L transition of the control input and the next L→ H clock pulse transition to ensure that the ÷11 mode is obtained.

- Guaranteed but not tested.

\*Tested as specified in table of Electrical Characteristics

Fig.3 Typical input characteristic of SP8643A

# TRUTH TABLE FOR CONTROL INPUTS

| PE1 | PE2 | Division<br>Ratio |  |

|-----|-----|-------------------|--|

| L   | L   | 11                |  |

| н   | L   | 10                |  |

| L   | н   | 10                |  |

| н   | н   | 10                |  |

## **OPERATING NOTES**

- 1. The clock and control inputs are ECL III compatible. There is an internal pulldown resistor to VEE of 4.3k on each input and therefore any unused input can be left open circuit when not in use but should be bypassed for RF signals with a 1nF capacitor to ensure maximum noise immunity. If it is desirable to capacitively couple the signal source to the clock input then an external bias is required as shown in Fig. 6. The external bias voltage should be -1.3 V at  $25\,^{\circ}\mathrm{C}$ .

- 2. The outputs are compatible with ECL II but can be interfaced to ECL 10K as shown in Fig. 7.

- 3. The circuit will operate down to  $\overrightarrow{DC}$  but slew rate must be better than  $100V/\mu s$ .

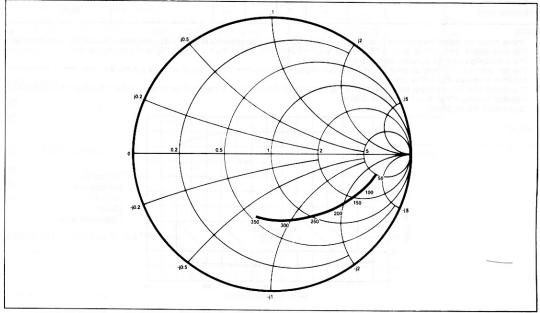

- 4. Input impedance is a function of frequency. See Fig. 5.

- 5. All components should be suitable for the frequency in use.

Fig.4 Timing diagram

Fig.5 Typical input impedance. Test conditions: supply voltage -5.2V, ambient temperature 25°C, frequencies in MHz, impedances normalised to 50 ohms.

Fig.6 Test circuit

Fig.7 Typical application using ECL outputs. NB Voltage at TP1 should be -1.3V at 25°C

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com