# *SPT5420*

# 13-BIT, OCTAL D/A CONVERTER

# TECHNICAL DATA

JUNE 26, 2001

# **FEATURES**

- 13-bit resolution

- Pin compatible with AD7839

- Eight DACs in one package

- · Buffered voltage outputs

- Wide output voltage swing V<sub>DD</sub>-2.5 V to V<sub>SS</sub>+2.5 V

- 15 µs settling time to ±0.5 LSB

- Double-buffered digital inputs

- Microprocessor and TTL/CMOS compatible

**APPLICATIONS**

- Automatic test equipment

- Instrumentation

- Process control

# **GENERAL DESCRIPTION**

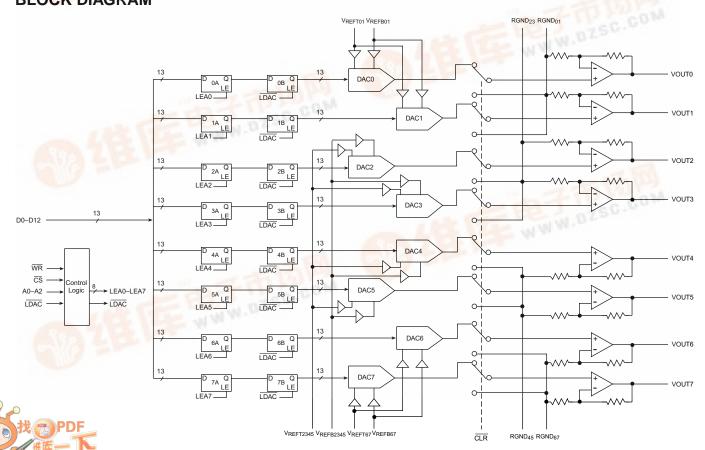

The SPT5420 contains eight 13-bit digital-to-analog CMOS converters designed primarily for automatic test equipment applications. It uses novel circuit topology to convert the 13-bit digital inputs into output voltages which are proportionate to the applied reference voltages. Each

DAC's full-scale output voltage and output voltage offset are adjustable with analog inputs (RGND, VREFB, VREFT).

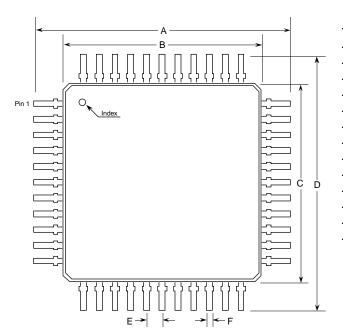

The SPT5420 operates over an industrial temperature range of -40 °C to +85 °C and is available in a 10 x 10 mm, 44-lead metric quad flat pack (MQFP) plastic package.

# **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

####

# **ELECTRICAL SPECIFICATIONS**

$T_{A} = T_{MIN} \text{ to } T_{MAX}, V_{CC} = +5.0 \text{ V}, V_{DD} = +11.5 \text{ V}, V_{SS} = -8.0 \text{ V}, V_{REFB} = -1.5 \text{ V}, V_{REFB} = -1.5 \text{ V}, V_{RL} = +10 \text{ k}\Omega, C_{L} = 50 \text{ pF, unless otherwise specified.}$

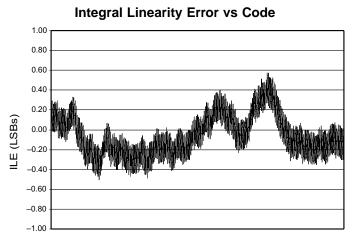

| PARAMETERS                                                                                                                         | TEST<br>CONDITIONS | TEST<br>LEVEL              | MIN                                     | SPT5420<br>TYP | MAX                               | UNITS                          |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------|-----------------------------------------|----------------|-----------------------------------|--------------------------------|

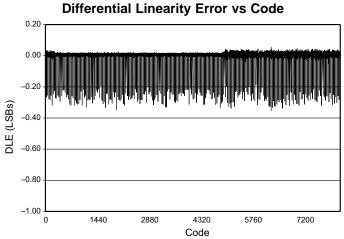

| Accuracy Resolution Integral Linearity Error (ILE) Differential Linearity Error (DLE) Zero-Scale Error Full Scale Error Gain Error |                    | VI<br>VI<br>VI<br>VI<br>VI | 13<br>-2.0<br>-1.0<br>-25<br>-25<br>-25 | ±0.5<br>±0.3   | +2.0<br>+1.0<br>+25<br>+25<br>+25 | Bits<br>LSB<br>LSB<br>mV<br>mV |

| Reference Inputs Input Current VREFT <sup>1</sup> VREFB <sup>2</sup>                                                               |                    | IV<br>VI<br>VI             | 0<br>-5.0                               | +3.5<br>-1.5   | ±100<br>+5.0<br>0                 | nA<br>V<br>V                   |

| RGND Inputs DC Input Impedance Input Range                                                                                         |                    | V<br>IV                    | -2.0                                    | 60             | 2.0                               | kΩ<br>V                        |

| Output Characteristics Output Swing <sup>3,4</sup> Short Circuit Current Resistive Load DC Output Impedance                        |                    | VI<br>IV<br>VI<br>IV       | 5                                       | +7/–3          | 15<br>1.0                         | V<br>mA<br>kΩ<br>Ω             |

| Digital Inputs Logic 1 Voltage Logic 0 Voltage Maximum Input Current Input Capacitance                                             |                    | VI<br>VI<br>VI<br>V        | 2.4<br>-10                              | 10             | 0.8<br>10                         | V<br>V<br>μΑ/pin<br>pF         |

### Notes:

4.

$$V_{OUT} = 2 X (V_{REFB} + [V_{REFT} - V_{REFB}] X \frac{INPUT CODE}{8192}) - V_{RGND}$$

<sup>1.</sup>  $V_{REFT}$  < 8 V + ( $V_{SS}$  x 0.5); e.g., if  $V_{SS}$  = -8 V, then  $V_{REFT}$  < 4 V

<sup>2.</sup>  $V_{REFB}$  >  $(V_{DD}$  x 0.5) - 9.5 V; e.g., if  $V_{DD}$  = 11 V, then  $V_{REFB}$  > -4 V

<sup>3.</sup>  $V_{SS} + 2.5 \text{ V} \le V_{OUT} \le V_{SS} + 16.0 \text{ V}$  for  $18.5 \text{ V} \le V_{DD} - V_{SS} \le 20.0 \text{ V}$  $V_{SS} + 2.5 \text{ V} \le V_{OUT} \le V_{DD} - 2.5 \text{ V}$  for  $V_{DD} - V_{SS} \le 18.5 \text{ V}$

### **ELECTRICAL SPECIFICATIONS**

$T_A = T_{MIN} \text{ to } T_{MAX}, V_{CC} = +5.0 \text{ V}, V_{DD} = +11.5 \text{ V}, V_{SS} = -8.0 \text{ V}, V_{REFT} = 3.5 \text{ V}, V_{REFB} = -1.5 \text{ V}, R_L = +10 \text{ k}\Omega, C_L = 50 \text{ pF, unless otherwise specified.}$

| PARAMETERS                                                                                                                                                                                                                                                                         | TEST<br>CONDITIONS                                                                                       | TEST<br>LEVEL                    | MIN                | SPT5420<br>TYP                        | MAX                             | UNITS                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|---------------------------------------|---------------------------------|------------------------------------------|

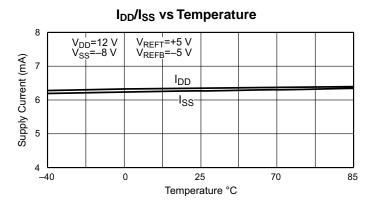

| Power Requirements  V <sub>CC</sub> Supply Voltage (Digital)  V <sub>DD</sub> Supply Voltage (Analog)1,2  V <sub>SS</sub> Supply Voltage (Analog)1,2  I <sub>CC</sub> Supply Current  I <sub>DD</sub> Supply Current  I <sub>SS</sub> Supply Current  Power Supply Rejection Ratio | Outputs Unloaded<br>Outputs Unloaded<br>ΔV <sub>DD</sub> / ΔFull Scale<br>ΔV <sub>SS</sub> / ΔFull Scale | IV<br>VI<br>VI<br>VI<br>VI<br>IV | 4.75<br>5<br>–12.5 | 5<br>11.5<br>-8<br>5<br>5<br>80<br>80 | 5.25<br>12.5<br>-5<br>0.5<br>10 | V<br>V<br>V<br>mA<br>mA<br>dB<br>dB      |

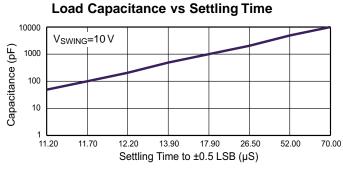

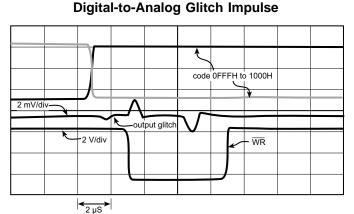

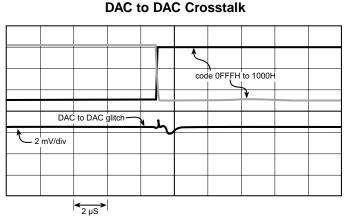

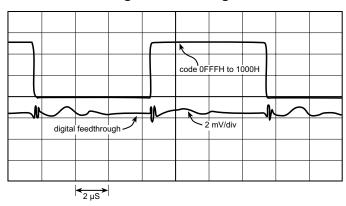

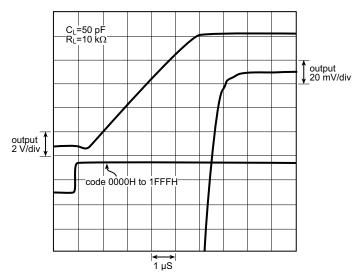

| Dynamic Performance Output Settling Time³ (Full Scale Change to ±0.5 LSB) Slew Rate Glitch Impulse Channel to Channel Isolation DAC to DAC Crosstalk Digital Crosstalk Digital Feedthrough                                                                                         | C <sub>L</sub> ≤ 220 pF                                                                                  | IV<br>V<br>V<br>V<br>V           |                    | 2.0<br>35<br>100<br>40<br>1<br>1      | 15                              | μs<br>V/μs<br>nV-s<br>dB<br>nV-s<br>nV-s |

| Timing Characteristics<br>(See page 4)                                                                                                                                                                                                                                             |                                                                                                          | IV                               |                    |                                       |                                 |                                          |

- 1. Supplies should provide 2.5 V headroom above and below max output swing.

- 2.  $V_{DD} V_{SS} \le 20 \text{ V}$

- 3. Output can drive 10,000 pF without oscillation, but with settling time degradation.

### **DEFINITION OF SELECTED TERMINOLOGY**

### **Channel-to-Channel Isolation**

Channel-to-Channel isolation refers to the proportion of input signal from one DAC's reference input that appears at the output of the other DAC. It is expressed in dBs.

### **DAC-to-DAC Crosstalk**

DAC-to-DAC crosstalk is defined as the glitch impulse that appears at one DAC's output due to both the digital change and subsequent analog output change at any other DAC. It is specified in nV-s.

### **Digital Crosstalk**

The glitch impulse transferred to one DAC's output due to a change in digital input code of any other DAC. It is specified in nV-s.

### **Digital Feedthrough**

Digital feedthrough is the noise at a DAC's output caused by changes to D0-D12 while WR is high.

| TEST LEVEL CODES                                                                                                                                                                                                                         | LEVEL   | TEST PROCEDURE                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|

| All electrical characteristics are subject to the following conditions:                                                                                                                                                                  | I<br>II | 100% production tested at the specified temperature. 100% production tested at $T_A = +25$ °C, and sample tested at the |

| All parameters having min/max specifications are guaranteed. The Test Level column indi-                                                                                                                                                 | III     | specified temperatures.  QA sample tested only at the specified temperatures.                                           |

| cates the specific device testing actually per-<br>formed during production and Quality Assur-<br>ance inspection. Any blank section in the data<br>column indicates that the specification is not<br>tested at the specified condition. | IV      | Parameter is guaranteed (but not tested) by design and characterization data.                                           |

|                                                                                                                                                                                                                                          | V       | Parameter is a typical value for information purposes only.                                                             |

|                                                                                                                                                                                                                                          | VI      | 100% production tested at $T_A$ = +25 °C. Parameter is guaranteed over specified temperature range.                     |

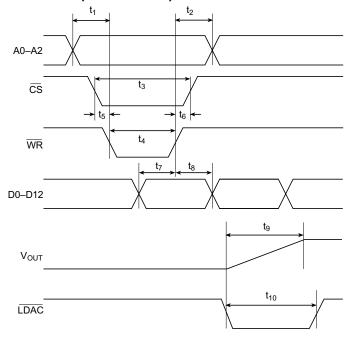

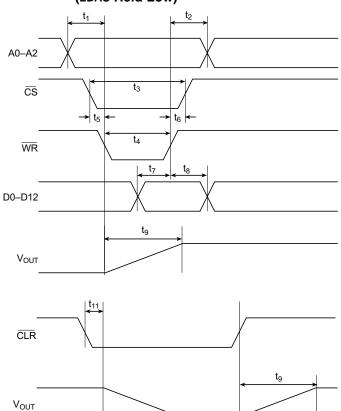

# **TIMING CHARACTERISTICS**

Figure 1a – Timing Diagram: Latched Mode (LDAC Strobed)

Figure 1b – Timing Diagram: Transparent Mode (LDAC Held Low)

| PARAMETER                  | SYMBOL          | MIN | TYP | MAX | UNIT |

|----------------------------|-----------------|-----|-----|-----|------|

| Address Valid to WR Setup  | t <sub>1</sub>  | 20  |     |     | ns   |

| Address Valid to WR Hold   | t <sub>2</sub>  | 0   |     |     | ns   |

| CS Pulse Width Low         | t <sub>3</sub>  | 50  |     |     | ns   |

| WR Pulse Width Low         | t <sub>4</sub>  | 50  |     |     | ns   |

| CS to WR Setup             | t <sub>5</sub>  | 0   |     |     | ns   |

| WR to CS Hold              | t <sub>6</sub>  | 0   |     |     | ns   |

| Data Setup                 | t <sub>7</sub>  | 25  |     |     | ns   |

| Data Hold                  | t <sub>8</sub>  | 0   |     |     | ns   |

| Settling Time <sup>1</sup> | t <sub>9</sub>  |     |     | 15  | us   |

| LDAC Pulse Width Low       | t <sub>10</sub> | 50  |     |     | ns   |

| CLR Pulse Activation       | t <sub>11</sub> |     |     | 300 | ns   |

| HOTEO                      | •               |     |     |     |      |

NOTES:

All digital input rise and fall times are measured from 10% to 90% of +5 V.  $t_{\text{r}} = t_{\text{f}} = 5 \ \text{ns}.$

1.  $R_L = 10 \text{ k}\Omega$

$C_L \leq 220 \ pF$

# VOLTAGE REFERENCES AND ANALOG GROUND INPUTS

Three  $V_{REFTXX}$  and three  $V_{REFBXX}$  inputs set the output range of the three corresponding groups of DACs (0 and 1; 2 through 5; 6 and 7). Four RGND<sub>XX</sub> inputs set the output offset voltage of the four corresponding groups of DACs (0 and 1; 2 and 3; 4 and 5; 6 and 7). The formula for output swing and offset is presented in the "Analog Outputs" section below.

### DAC ADDRESSING AND LATCHING

Each DAC has an input latch which receives data from the data bus, and a DAC latch which receives data from the input latch. The analog output of each DAC corresponds to the data in its DAC latch. One of the eight input latches is addressed by the address lines A(2:0) according to Table I. While CS and WR are low, the addressed input latch is transparent and the seven other input latches are latched. Bringing CS or WR high latches data into the addressed input latch. While LDAC is low, all eight DAC latches are transparent. Bringing LDAC high latches data into the DAC latches. While CS, WR and LDAC are low, both latches are transparent and input data is transferred directly to the selected DAC. While CLR is low, all DAC outputs are set to their corresponding RGND<sub>XX</sub>. Bringing  $\overline{CLR}$ high returns each DAC's output to the voltage corresponding to the data in each DAC latch.

Table II summarizes this information, and figures 1a and 1b should be referenced for timing limitations.

### POWER SUPPLY SEQUENCING

The sequence in which  $V_{DD}$ ,  $V_{SS}$  and  $V_{CC}$  come up is not critical. The reference inputs,  $V_{REFTXX}$  and  $V_{REFBXX}$ , must come on only after  $V_{DD}$  and  $V_{SS}$  have been established. However, they may be turned on prior to  $V_{CC}$ . The digital inputs must be driven only after  $V_{DD}$ ,  $V_{SS}$  and  $V_{CC}$  have been established. Reverse the power-on sequence for power-down.

# ANALOG OUTPUTS VS DIGITAL INPUT CODE

The output voltage range is equal to twice the difference between  $V_{\text{REFTXX}}$  and  $V_{\text{REFBXX}}$ . The output voltage is given by:

$$V_{OUT} = 2 \text{ X } (V_{REFB} + [V_{REFT} - V_{REFB}] \text{ X } \frac{INPUT CODE}{8192}) - V_{RGND}$$

$$CODE = 0 - 8191$$

Table I - DAC Addressing

| A2 | <b>A</b> 1 | Α0 | Addressed Input<br>Latch DAC# |  |

|----|------------|----|-------------------------------|--|

| 0  | 0          | 0  | 0                             |  |

| 0  | 0          | 1  | 1                             |  |

| 0  | 1          | 0  | 2                             |  |

| 0  | 1          | 1  | 3                             |  |

| 1  | 0          | 0  | 4                             |  |

| 1  | 0          | 1  | 5                             |  |

| 1  | 1          | 0  | 6                             |  |

| 1  | 1          | 1  | 7                             |  |

|    |            |    |                               |  |

Table II - Control Logic Table

| WR | CS | LDAC | CLR | Input Latch   | DAC Latch            |

|----|----|------|-----|---------------|----------------------|

| 0  | 0  | Х    | 1   | transparent1  | Х                    |

| 1  | Х  | Х    | 1   | latched       | Х                    |

| Х  | 1  | Х    | 1   | latched       | Х                    |

| Х  | Х  | 0    | 1   | Х             | transparent          |

| Х  | Х  | 1    | 1   | Х             | latched              |

| Х  | Х  | Х    | 0   | DAC outputs a | t RGND <sub>XX</sub> |

#### Note

6/26/01

Only the input latch addressed by A(2:0) is transparent.

The other input latches are latched.

# TYPICAL PERFORMANCE CHARACTERISTICS

2880

4320 Code 5760

7200

1440

6/26/01

# TYPICAL PERFORMANCE CHARACTERISTICS

# **Digital Feedthrough**

# Slew and Settling Time

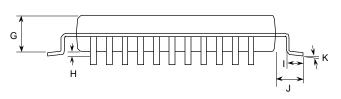

# **PACKAGE OUTLINE**

# 44-Lead MQFP

|        | INC        | HES    | MILLI | METERS |

|--------|------------|--------|-------|--------|

| SYMBOL | MIN        | MAX    | MIN   | MAX    |

| Α      | 0.5098     | 0.5295 | 12.95 | 13.45  |

| В      | 0.3917     | 0.3957 | 9.95  | 10.05  |

| С      | 0.3917     | 0.3957 | 9.95  | 10.05  |

| D      | 0.5098     | 0.5295 | 12.95 | 13.45  |

| E      | 0.0311     | 0.0319 | 0.79  | 0.81   |

| F      | 0.0118     | 0.0177 | 0.30  | 0.45   |

| G      | 0.0768     | 0.0827 | 1.95  | 2.10   |

| Н      | 0.0039     | 0.0098 | 0.10  | 0.25   |

| I      | 0.0287     | 0.0406 | 0.73  | 1.03   |

| J      | 0.0630 REF |        | 1.60  | REF    |

| K      | 0°         | 7°     | 0°    | 7°     |

6/26/01

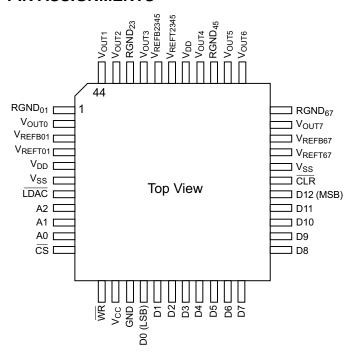

### **PIN ASSIGNMENTS**

### PIN FUNCTIONS

| Name    | Function                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL | CONTROL PINS                                                                                                                                                                                                                             |

| CS      | Chip Select (Active Low)                                                                                                                                                                                                                 |

| WR      | Level Triggered Write Input (Active Low). Used in conjunction with $\overline{\text{CS}}$ to write data to the SPT5420 input data latches. Data is latched into selected input data latch on the rising edge of $\overline{\text{WR}}$ . |

| CLR                   | (Active Low) Analog Clear. Sets the output voltages to RGND. (Each RGND is common to a DAC pair.) CLR does not reset the digital latches. When CLR is brought back high, the DAC outputs revert back to their original outputs as determined by the data in their DAC latches. |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDAC                  | When this logic input is taken low, the contents of<br>the input latches are transferred to their respective<br>DAC latches. (Active Low) Data is latched on<br>rising edge.                                                                                                   |

| A0 – A2               | Addresses DAC0 to DAC7 for loading the eight input latches.                                                                                                                                                                                                                    |

| D0 – D12              | Digital Inputs (D0 = LSB)                                                                                                                                                                                                                                                      |

| ANALOG                | PINS                                                                                                                                                                                                                                                                           |

| V <sub>REFT01</sub>   | Top Reference Voltage for DACs 0 and 1                                                                                                                                                                                                                                         |

| V <sub>REFT2345</sub> | Top Reference Voltage for DACs 2, 3, 4 and 5                                                                                                                                                                                                                                   |

| V <sub>REFT67</sub>   | Top Reference Voltage for DACs 6 and 7                                                                                                                                                                                                                                         |

| V <sub>REFB01</sub>   | Bottom Reference Voltage for DACs 0 and 1                                                                                                                                                                                                                                      |

| $V_{REFB2345}$        | Bottom Reference Voltage for DACs 2, 3, 4 and 5                                                                                                                                                                                                                                |

| V <sub>REFB67</sub>   | Bottom Reference Voltage for DACs 6 and 7                                                                                                                                                                                                                                      |

| RGND <sub>01</sub>    | Reference Ground for Output Amplifiers 0 and 1                                                                                                                                                                                                                                 |

| RGND <sub>23</sub>    | Reference Ground for Output Amplifiers 2 and 3                                                                                                                                                                                                                                 |

| RGND <sub>45</sub>    | Reference Ground for Output Amplifiers 4 and 5                                                                                                                                                                                                                                 |

| RGND <sub>67</sub>    | Reference Ground for Output Amplifiers 6 and 7                                                                                                                                                                                                                                 |

| V <sub>OUT0-7</sub>   | Output Voltage Pins for DAC0 – DAC7                                                                                                                                                                                                                                            |

| POWER S               | UPPLY PINS                                                                                                                                                                                                                                                                     |

| $V_{CC}$              | Digital +5 V Supply                                                                                                                                                                                                                                                            |

| $V_{DD}$              | Analog +11.5 V Supply (Nominal)                                                                                                                                                                                                                                                |

| V <sub>SS</sub>       | Analog –8 V Supply (Nominal)                                                                                                                                                                                                                                                   |

| GND                   | Ground                                                                                                                                                                                                                                                                         |

# ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE  |

|-------------|-------------------|----------|

| SPT5420SIM  | –40 to +85 °C     | 44L MQFP |

### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com © Copyright 2002 Fairchild Semiconductor Corporation