# HIGH SPEED CMOS 64K-BIT STATIC RAM

# DESCRIPTION

The SRM2264L1012 is an 8,192 words x 8 bits asynchronous, static, random access memory on a monolithic CMOS chip. Its very low standby power requirement makes it ideal for applications requiring non-volatile storage with back-up batteries. The asynchronous and static nature of the memory requires no external clock or refreshing circuit. Both the input and output ports are TTL compatible; and the three-state output allows easy expansion of memory capacity.

# FEATURES

| Fast access time   | SRM2264L | .10 100ns (Max)  |

|--------------------|----------|------------------|

| Low supply current |          | 12 120ns (Max)   |

|                    |          | 47mA (Typ) 100ns |

|                    |          | 45mA (Typ) 120ns |

- Completely static ......

No clock required

- TTL compatible inputs and outputs

查询SRM2264L供应商

- 3-state output with wired-OR capability

- Non-volatile storage with back-up batteries

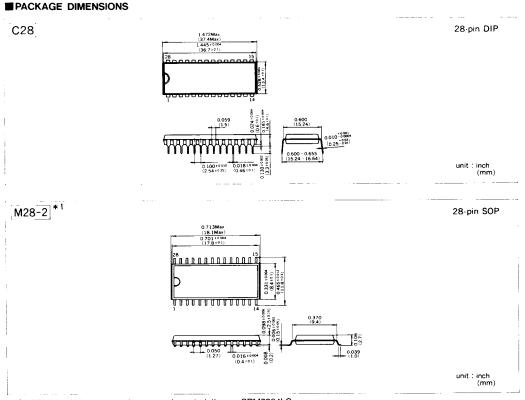

- Package ...... SRM2264LC10/12 28-pin DIP(plastic)

SRM2264LC10/12 28-pin DIP(plastic) SRM2264LM10/12 28-pin SOP (plastic)

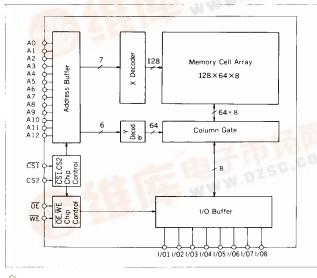

# BLOCK DIAGRAM

# PIN CONFIGURATION

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

|--------------------------------------------------------|--|

|--------------------------------------------------------|--|

#### PIN DESCRIPTION

| A0 to A12 | Address Input     |

|-----------|-------------------|

| WE        | Write Enable      |

| ŌE        | Output Enable     |

| CS1, CS2  | Chip Select       |

| I/01 to 8 | Data I/O          |

| VDD       | Power Supply(+5V) |

| Vss       | Power Supply( OV) |

| NC        | No connection     |

|           |                   |

# SRM2264L10/12

| ABSOLUTE MAXIMUM RATINGS       |        |                      | (Vss=0V |

|--------------------------------|--------|----------------------|---------|

| Parameter                      | Symbol | Ratings              | Unit    |

| Supply voltage                 | VDD    | -0.5 to 7.0          | V       |

| Input voltage *                | VI     | -0.5 to 7.0          | v       |

| Input/Output voltage*          | Vi⁄o   | -0.5 to VDD+O.3      | V       |

| Power dissipation              | PD     | 1.0                  | w       |

| Operating temperature          | Topr   | 0 to 70              | °C      |

| Storage temperature            | Tstg   | -65 to 150           | °C      |

| Soldering temperature and time | Tsol   | 260°C, 10s (at lead) | _       |

# RECOMMENDED DC OPERATING CONDITIONS

\* VI, VI/O (Min) = -1.0V when pulse width is 50 ns  $(Vss = 0V, Ta = 0 \text{ to } 70^{\circ}C)$

| ILCOMMENDED DC O |        |        |     |           | $0^{\circ}$ , $1^{\circ} = 0^{\circ} 0^{\circ} 0^{\circ} 0^{\circ}$ |

|------------------|--------|--------|-----|-----------|---------------------------------------------------------------------|

| Parameter        | Symbol | Min    | Тур | Max       | Unit                                                                |

| Supply Veltero   | VDD    | 4.5    | 5.0 | 5.5       | V                                                                   |

| Supply Voltage   | Vss    | 0      | 0   | 0         | V                                                                   |

| Input Voltage    | ViH    | 2.2    | 3.5 | VDD + 0.3 | V                                                                   |

| input voltage    | VIL    | -0.3 * | _   | 0.8       | v                                                                   |

# ELECTRICAL CHARACTERISTICS

\* If pulse width is less than 50 ns, it is -1.0V

| DC Electrical Characteristics |        |                               |     | $(V_{DD} = 5V \pm 10\%, V_{SS} = 0V, T_{a} = 0 \text{ to } 70^{\circ}\text{C}$ |     |     |         |     |      |

|-------------------------------|--------|-------------------------------|-----|--------------------------------------------------------------------------------|-----|-----|---------|-----|------|

| Parameter                     | Symbol | Conditions                    | SR  | M2264L                                                                         | 10  | SRM | 12264L1 | 2   | Unit |

|                               |        |                               | Min | Typ*                                                                           | Max | Min | Тур*    | Max |      |

| Input leakage current         | ILI    | Vi = 0 to VDD                 | -1  | -                                                                              | 1   | -1  |         | 1   | μΑ   |

| Standby supply current        | IDDS   | CS1-VIH or CS2-VIL            | _   | 0.5                                                                            | 1.0 |     | 0.5     | 1.0 | mA   |

|                               | IDDS1  | CS1=CS2>VDD -0.2V or CS2≤0.2V | —   | 0.5                                                                            | 20  | _   | 0.5     | 20  | μΑ   |

| Average operating current     | IDDA   | V=VIL,VIH II/O=0mA toyc=Min   |     | 47                                                                             | 82  | —   | 45      | 80  | mA   |

| Operating supply current      | lddo   |                               | -   | 35                                                                             | 60  | _   | 35      | 60  | mA   |

| Output leakage                | ILO    | CS1=VIH or CS2=VIL or WE=VIL  | -1  | _                                                                              | 1   | -1  |         | 1   | μΑ   |

| -                             |        | or OE=VIH, VVO=0 to VDD       |     |                                                                                |     |     |         |     |      |

| High level output voltage     | Vон    | IOH=-1.0mA                    | 2.4 | VDD-0.1                                                                        | -   | 2.4 | VDD-0.1 |     | V    |

| Low level output voltage      | VOL    | loL=4.0mA                     | —   | 0.2                                                                            | 0.4 | —   | 0.2     | 0.4 | V    |

# Terminal Capacitance

(f = 1MHz, Ta = 25°C) Parameter Symbol Conditions Min Max Unit Тур VADD = OV Address Capacitance CADD 5 -----3 рF Input Capacitance Сі  $V_{i} = 0V$ 5 6 рF \_\_\_\_ I/O Capacitance Cvo Vi/o = 0V 6 7 рF \_\_\_\_

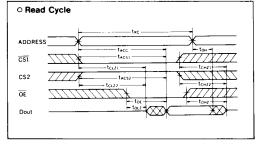

# AC Electrical Characteristics O Read Cycle

$(VDD = 5V \pm 10\%, Vss = 0V, Ta = 0 \text{ to } 70^{\circ}\text{C})$

|                          |        |            | (100 = 01 ± 10%, 100 = 01; 14 = 0 10 10 0) |     |          |      |    |  |

|--------------------------|--------|------------|--------------------------------------------|-----|----------|------|----|--|

| Parameter                | Symbol | Conditions | SRM2264L10                                 |     | SRM2264L | Unit |    |  |

| T didificion             |        |            | Min                                        | Max | Min      | Max  |    |  |

| Read cycle time          | tRC    |            | 100                                        | _   | 120      | —    | ns |  |

| Address access time      | tACC   |            |                                            | 100 |          | 120  | ns |  |

| CS1 access time          | tACS1  | *1         |                                            | 100 |          | 120  | ns |  |

| CS2 access time          | tACS2  |            |                                            | 100 |          | 120  | ns |  |

| OE access time           | tOE    |            | —                                          | 50  | _        | 60   | ns |  |

| CS1 output set time      | tCLZ1  |            | 10                                         |     | 10       |      | ns |  |

| CS1 output floating time | tCHZ1  |            |                                            | 35  |          | 40   | ns |  |

| CS2 output set time      | tCLZ2  | *2         | 10                                         |     | 10       |      | ns |  |

| CS2 output floating time | tCHZ2  |            |                                            | 35  | _        | 40   | ns |  |

| OE output set time       | tolz   |            | 5                                          | —   | 5        | —    | ns |  |

| OE output floating time  | tonz   |            | _                                          | 35  | —        | 40   | ns |  |

| Output hold time         | tOH    | *1         | 10                                         | —   | 10       | —    | ns |  |

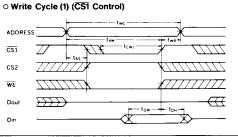

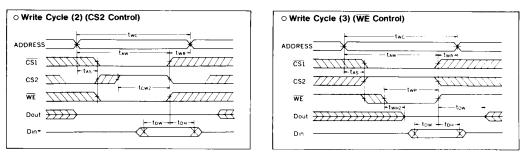

# **O Write Cycle**

|                       |        |            | SRM22 | 264L10 | SRM2 | 264L12 |      |

|-----------------------|--------|------------|-------|--------|------|--------|------|

| Parameter             | Symbol | Conditions | Min   | Max    | Min  | Max    | Unit |

| Write cycle time      | twc    |            | 100   |        | 120  | —      | ns   |

| Chip select time 1    | tcw1   |            | 80    |        | 85   |        | ns   |

| Chip select time 2    | tCW2   |            | 80    |        | 85   | —      | ns   |

| Address enable time   | taw    |            | 80    |        | 85   |        | ns   |

| Address setup time    | tas    | *1         | 0     | —      | 0    | —      | ns   |

| Write pulse width     | twp    |            | 60    |        | 70   |        | ns   |

| Address hold time     | twn    |            | 0     | -      | 0    | —      | ns   |

| Input data setup time | tow    |            | 50    | - 1    | 50   | _      | ns   |

| Input data hold time  | ton    |            | 0     |        | 0    | _      | ns   |

| WE output floating    | twHz   | *3         |       | 35     |      | 40     | ns   |

| WE output setup time  | tow    | 3          | 5     |        | 5    | _      | ns   |

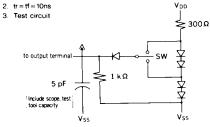

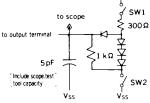

### \* 1 Test Conditions

- 1. Input pulse level : 0.8V to 2.4V

- 2. tr = tf = 10ns

- 3. Input and output timing reference levels : 1.5V

- 4. Output load ITTL + CL = 100pF

#### \* 3 Test Conditions

- 1. Input pulse level : 0.8V to 2.4V

- 2. tr = tf = 10ns

Test : tow,twnz Hi-Z . "H" and "H" . Hi-Z SW is Voo side Test : tow,twnz Hi-Z .\* "L" and "L" .+ Hi-Z SW is Vss side

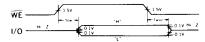

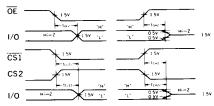

Output turnon turnoff time

#### Timing Chart

#### \* 2 Test Conditions

- 1. Input pulse level : 0.8V to 2.4V

- 2. tr = tf = 10ns

VDD

Test : tcHz1, tcHz2, toHz Both SW1 and SW2 are close Test : toL21, toL22, toL2 Hi-Z---"H" SW1 is open, SW2 is close. Test: tci.zi, tci.zz, toi.z Hi-Z→"L" SW1 is close, SW2 is open.

Note : 1. During read cycle time, WE is to be "H" level.

- 2. During write cycle time that is controlled by CS1 or CS2, Output Buffer is in high impedance state whether OE level is "H" or "L".

- 3. During write cycle time that is controlled by WE, Output Buffer is high impedance state if OE is "H" level.

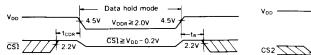

#### DATA RETENTION CHARACTERISTIC WITH LOW VOLTAGE POWER SUPPLY

$(Ta = 0 to 70^{\circ}C)$

| Parameter                     | Symbol         | Conditions                                                                 | Min               | Тур | Max | Unit |

|-------------------------------|----------------|----------------------------------------------------------------------------|-------------------|-----|-----|------|

| Data retention supply voltage | VDDR           |                                                                            | 2.0               | _   | 5.5 | v    |

| Data retention current        | DDR            | $\frac{V_{DD} = 3V}{CS1 = CS2 \ge V_{DD} - 0.2V \text{ or } CS2 \ge 0.2V}$ | _                 | -   | 10  | μA   |

| Chip select data hold time    | tCDR           |                                                                            | 0                 |     |     | ns   |

| Operation recovery time       | t <sub>R</sub> |                                                                            | t <sub>RC</sub> * |     |     | ns   |

\*t<sub>RC</sub> = Read cycle time

# Data retention timing (CS1 Control)

# Data retention timing (CS2 Control)

#### **FUNCTIONS**

#### Truth Table

| CS1 | CS2 | OE | WE | A0 to A12 | DATA I/O    | Mode           | IDD         |

|-----|-----|----|----|-----------|-------------|----------------|-------------|

| н   | х   | -  | —  |           | Hi-Z        | Unselected     | IDDS, IDDS1 |

| _   | L   |    | _  | _         | Hi-Z        | Unselected     | IDDS, IDDS1 |

| L   | н   | х  | L  | Stable    | Input data  | Write          | IDDO        |

| L   | н   | L  | н  | Stable    | Output data | Read           | IDDO        |

| L   | н   | н  | н  | Stable    | Hi-Z        | Output disable | IDDO        |

X:"H" or "L", --: "H", "L" or "Hi-Z"

# Reading data

Data is able to be read when the address is setted while holding  $\overline{CS1} = "L"$ , CS2 = "H",  $\overline{OE} = "L"$  and  $\overline{WE} = "H"$ . Since Data I/O terminals are in high impedance state when  $\overline{OE} = "H"$ , the data bus line can be used for any other objective, then access time apparently is able to be cut down.

## Writing data

There are the following four ways of writing data into the memory.

- (1) Hold CS2 ="H", WE="L" set addresses and give "L" pulse to CS1.

- (2) Hold CS1="L". WE ="L", set addresses and give "H" pulse to CS2.

- (3) Hold  $\overline{CS1}$  = "L", CS2 = "H", set addresses and give "L" pulse to  $\overline{WE}$ .

- (4) After setting addresses, give "L" pulse to CS1, WE and give "H" pulse to CS2.

Anyway, data on the Data I/O terminals are latched up into the SRM2264L $\frac{90}{10}$  at the end of the period that  $\overline{CS1}$ , WE are "L" level, and CS2 is "H" level. As Data I/O terminals are in high impedance state when any of  $\overline{CS1}$ ,  $\overline{OE}$  = "H", or CS2 = "L", the contention on the data bus can be avoided.

### Standby mode

When CS1 is "H" or CS2 is "L" level, the SRM2264L90/10/12 is in the standby mode which has retaining date operation. In this case Data I/O terminals are Hi-Z, and all inputs of addresses, WE and data can be any "H" or "L". When CS1 and CS2 level are in the range over VDD-0.2V, or CS2 level is in the range under 0.2V, in the SRM2264L10/12 there is almost no current flow except through the high resistance parts of the memory.

\*1 SRM2264LM90/10/12 has the same characteristics as SRM2264LC90/10/12.

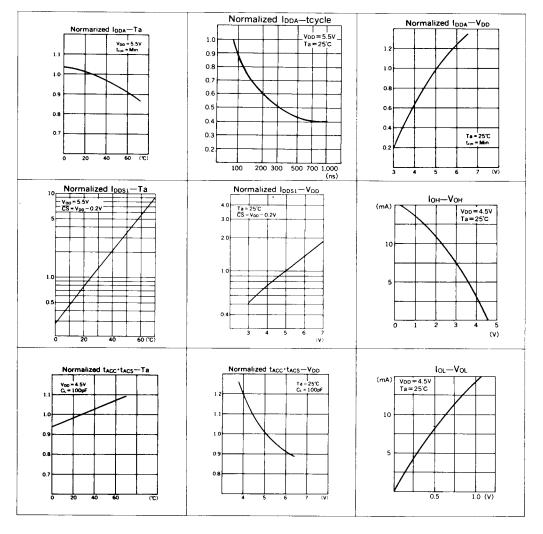

# **CHARACTERISTICS CURVES**

A-20

-----