ST3854

# **ELECTRONIC HOOK SWITCH DEVICE**

- TIP AND RING SWITCHES FOR TERMINAL CONNECTED TO A TELEPHONE LINE

- HANDSFREE / ON HOOK DIALING KEY CONTROL

- HANDSET SWITCH CONTROL

- RINGER INTERFACE AND RECTIFIER RIN-GER BRIDGE

- PULSE DIALING INTERFACE

- AUTOMATIC LINE SEIZURE THROUGH MI-CROCONTROLLER CONTROL

- LINE INHIBITION THROUGH MICROCON-TROLLER CONTROL

- FRENCH DC LINE CURRENT REGULATION:

- OFF HOOK MODE (60mA Max.)

- PULSE DIALING (75mA Max.)

- FRENCH INCOMING CALL CURRENT CONTROL

- IN DC CURRENT REGULATION MODE,

VOLTAGE INFORMATION FOR THE SPEECH

CIRCUIT FOR Tx AND Rx GAIN CONTROL

- POWER DISSIPATION LIMITATION FOR OVER-VOLTAGE SURGES

- LINE CURRENT PRESENCE INFORMATION

- LOW VOLTAGE SWITCHES REQUESTED FOR EHKS KEY AND HKS SWITCH

The possible use of low voltage switches, 5 volts, for HKS switch and EHKS key, allows reliable functionality in critical environment condition like humidity atmosphere saturation.

The Electronic Hook Switch device allows to make a high voltage line interface for any terminal connected on a telephone line with few discrete components (Rectifier bridge, R/C ring network and protections) and allows to pass the French requirements by added only two resistors and two capacitors more.

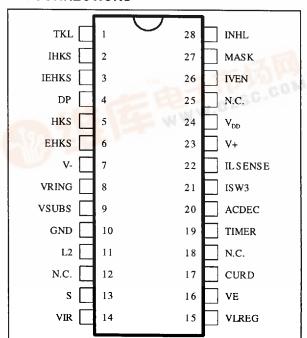

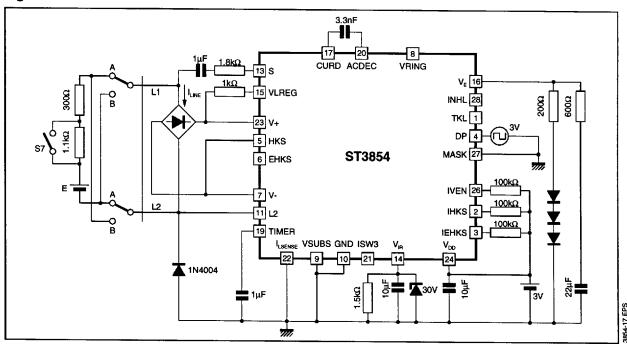

## **PIN CONNECTIONS**

## **DESCRIPTION**

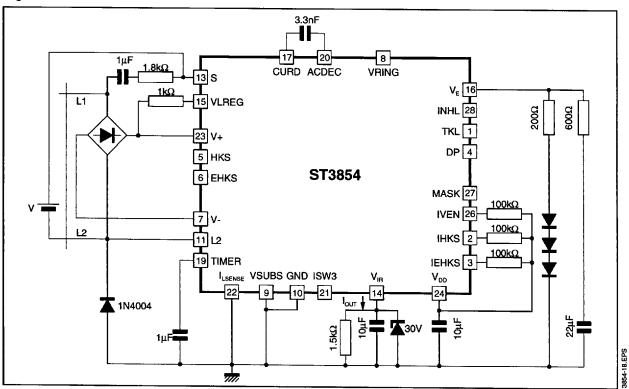

The Electronic Hook Switch device integrates the high voltage stage, which is directly connected on a telephone line, of a terminal like, corded telephone set with handsfree or On Hook Dialing, cordless phone, answering machine or fax.

It integrates all the different DC line French regula-

The high voltage switches, N-channel/D-Mos and P-channel/Drain extension Mos, are integrated in a mixed 250 Volts technology.

The ringer interface allows to use a common ground between speech, dialing and ringing features.

54-01.EP

zsc.com

# ST3854

# **PIN LIST**

| Pin N° | Symbol               | Function                                                                                                                                                                                                                            |  |  |  |  |  |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1      | TKL                  | Input logic signal to "take the line" in Electronic hook switch mode or for cordless and answering machine.  TKL = "1"; line closed  TKL = "0"; line released.  Note: In inhibit the line feature, this pin should be at level "1". |  |  |  |  |  |

| 2      | IHKS                 | Open drain output logic signal following the status of mechanical hook-switch, Pin 5.                                                                                                                                               |  |  |  |  |  |

| 3      | IEHKS                | Open drain output logic signal following the status of EHKS key , Pin 6.                                                                                                                                                            |  |  |  |  |  |

| 4      | DP                   | Input logic signal for pulse dialing and flash modes.  DP = "1"; line closed.  DP = "0"; line is open and timer and overvoltage protection circuits are resetted.                                                                   |  |  |  |  |  |

| 5      | HKS                  | Mechanical hook switch input                                                                                                                                                                                                        |  |  |  |  |  |

| 6      | EHK                  | Key input for electronic hook switch feature                                                                                                                                                                                        |  |  |  |  |  |

| 7      | V-                   | Connected to the negative polarity of the external rectifier bridge                                                                                                                                                                 |  |  |  |  |  |

| 8      | VRING                | Ring frequency information for frequency analysis and Inhibit the line feature                                                                                                                                                      |  |  |  |  |  |

| 9      | VSUBS                | Substrat                                                                                                                                                                                                                            |  |  |  |  |  |

| 10     | GND                  | Ground, negative common reference point                                                                                                                                                                                             |  |  |  |  |  |

| 11     | L2                   | Output connection with the line L2 terminal                                                                                                                                                                                         |  |  |  |  |  |

| 12     | N.C.                 | This pin should be left open, (internally connected)                                                                                                                                                                                |  |  |  |  |  |

| 13     | S                    | Output connection to the ring R/C network                                                                                                                                                                                           |  |  |  |  |  |

| 14     | V <sub>IR</sub>      | Positive ringer supply voltage                                                                                                                                                                                                      |  |  |  |  |  |

| 15     | VLREG                | To external 1k resistor for line current regulation purpose (French characteristic.)                                                                                                                                                |  |  |  |  |  |

| 16     | VE                   | Positive power supply for speech circuit                                                                                                                                                                                            |  |  |  |  |  |

| 17     | CURD                 | To external AC decoupling capacitor for AC shunt in DC current regulation mode                                                                                                                                                      |  |  |  |  |  |

| 18     | N.C.                 |                                                                                                                                                                                                                                     |  |  |  |  |  |

| 19     | TIMER                | To external capacitor, for current limiting duration during Off-Hook transient with AC ring signal. (French requirement). This capacitor is also used for AC shunt in DC current regulation mode.                                   |  |  |  |  |  |

| 20     | ACDEC                | To external AC decoupling capacitor for AC shunt in DC current regulation mode                                                                                                                                                      |  |  |  |  |  |

| 21     | ISW3                 | Current information flowing in SW3 switch to obtain AGC speech linearity during DC current regulation                                                                                                                               |  |  |  |  |  |

| 22     | I <sub>L SENSE</sub> | Resistor threshold to overvoltage protection circuit                                                                                                                                                                                |  |  |  |  |  |

| 23     | V+                   | Positive path of external rectifier bridge                                                                                                                                                                                          |  |  |  |  |  |

| 24     | V <sub>DD</sub>      | Internal logic positive supply                                                                                                                                                                                                      |  |  |  |  |  |

| 25     | N.C                  |                                                                                                                                                                                                                                     |  |  |  |  |  |

| 26     | IVEN                 | Line current presence information output logic                                                                                                                                                                                      |  |  |  |  |  |

| 27     | MASK                 | Input logic for DC current regulation control in pulse dialing mode.  MASK="1", I <sub>L Max.</sub> < 55mA  MASK= "0", I <sub>L Max.</sub> < 75mA                                                                                   |  |  |  |  |  |

| 28     | INHL                 | Inhibition of any line connection command through HKS and EHKS pins.  Note: In inhibit the line feature, the TKL Pin should also be at level "1".                                                                                   |  |  |  |  |  |

854-01.1BL

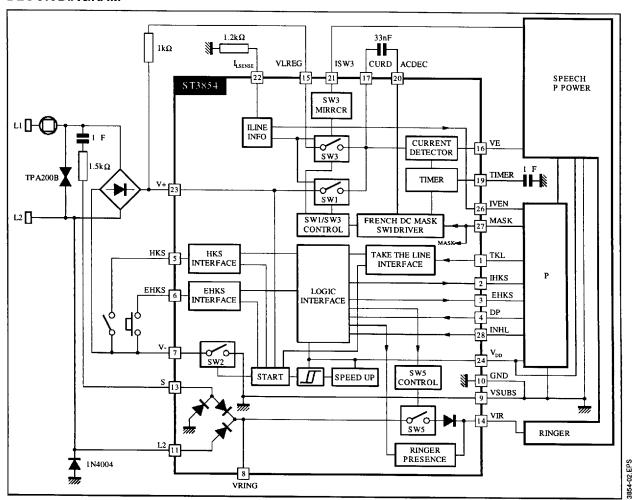

## **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Parameter                        | Value     | Unit |

|--------------------|----------------------------------|-----------|------|

| $V_{lmax}$         | Peak voltage between Pins 23 & 7 | 250       | V    |

| V <sub>emax</sub>  | Peak voltage between Pins 16 & 9 | 20        | V    |

| $V_{max}$          | Peak voltage between Pins 14 & 9 | 70        | V    |

| V <sub>DDmax</sub> | Peak voltage between Pins 24 & 9 | 6         | V    |

| Ismax              | Current in Speech mode           | 150       | mA   |

| P <sub>max</sub>   | Maximum Power                    | 0.7       | W    |

| T <sub>oper</sub>  | Operating Temperature            | -25, +55  | °C   |

| T <sub>stg</sub>   | Storage Temperature              | -55, +150 | °C   |

| Tj                 | Junction Temperature             | -25, 125  | °C   |

## THERMAL RESISTANCE

| Symbol                | Parameter                           |      | Value | Unit |

|-----------------------|-------------------------------------|------|-------|------|

| R <sub>th (j-a)</sub> | Thermal Resistance Junction-Ambient | Max. | 90    | °C/W |

# **ELECTRICAL CHARACTERISTICS** (Tamb = 25°C, V<sub>DD</sub> = 3V if not otherwise specified)

| Symbol           | Parameter                                               | Test Conditions                                                                                                                                     | Min.       | Тур.              | Мах.              | Unit                     |

|------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|-------------------|--------------------------|

| VL1              | Minimum Operating Current                               | Test 1, I <sub>L</sub> = 5mA                                                                                                                        |            | 3                 | 4                 | ٧                        |

| RSWI1/2          | Ron of Switches SW1 & SW2                               | Test 1, I <sub>L</sub> = 20mA                                                                                                                       |            | 35                | 45                | Ω                        |

| RSWI3            | Ron of Switch SW3                                       | Test 1, V <sub>L1/L2</sub> = 54V                                                                                                                    |            | 220               | 350               | Ω                        |

| RSWI5            | Ron of Switch SW5                                       | Test 3, $V_S = 1$<br>$V_S = 20V$<br>$V_S = 30V$                                                                                                     | OV         | 560<br>460<br>430 | 700<br>600<br>550 | Ω<br>Ω<br>Ω              |

| ILEAK            | Leakage Current (on-hook)                               | Test 1, $V_{L1/L2} = 104V$<br>$V_{L1/L2} = 250V$                                                                                                    | = 54V      | 1<br>1.5<br>2     | 5<br>10<br>15     | μΑ<br>μΑ<br>μΑ           |

| IBIAS            | Current Consumption (off-hook)                          | Test 1, I <sub>L</sub> = 20mA                                                                                                                       |            | 0.5               | 0.7               | mΑ                       |

| IV <sub>DD</sub> | Bias Current on V <sub>DD</sub>                         | Test 1, $I_L = 20$ mA, $V_{DD} = 3V$                                                                                                                |            | 270               | 400               | μΑ                       |

| $V_{DD}$         | V <sub>DD</sub> Supply (*)                              | After speed up mode                                                                                                                                 | 2.75       |                   | 5.5               | ٧                        |

| VSUT             | V <sub>DD</sub> Speed-up Threshold                      | Speed up OFF<br>Speed up ON                                                                                                                         |            | 2.9<br>2.6        | *                 | <b>&gt;</b> >            |

| I <sub>REG</sub> | Line Regulation Current                                 | Test 1, $V_{L1/L2} = 54V$ , $R_L = 300\Omega$                                                                                                       |            | 45                | 55                | mA                       |

| ISTART           | Start-up Line Current                                   | Test 1, V <sub>L1/L2</sub> = 54V                                                                                                                    |            | 110               | 150               | mA                       |

| Imask            | Line Current in mask mode & in pulse make period        | Test 2, V <sub>L1/L2</sub> = 54V                                                                                                                    |            | 64                | 75                | mA                       |

| lopl             | Line Current in mask mode & in pulse break period       | Test 2, V <sub>L1/L2</sub> = 104V                                                                                                                   |            | 300               | 350               | μА                       |

| RIsw3            | SW3 Switch Current Ratio                                | Test 1, V <sub>L1/L2</sub> = 54V                                                                                                                    |            | 2000              |                   |                          |

| Ітім             | Timer Pin Bias Current                                  | Test 1, V <sub>L1/L2</sub> = 54V                                                                                                                    |            | 10                |                   | μА                       |

| Rsoff            | R between Pin 5 or Pin 6 and Pin 7 to stay in On-Hook   | Test 1, V <sub>L1/L2</sub> = 54V                                                                                                                    | 100        |                   |                   | kΩ                       |

| Rson             | R between Pin 5 or Pin 6 and Pin 7 to maintain Off-Hook | Test 1, V <sub>L1/L2</sub> = 54V                                                                                                                    |            |                   | 10                | kΩ                       |

| Isens            | Overvoltage Threshold                                   |                                                                                                                                                     |            | 0.6               |                   | V                        |

| ACatt            | AC Attenuation, 20 Log V <sub>L</sub> /V <sub>E</sub>   | Test 1, V <sub>AC</sub> = 1.4V <sub>RMS</sub> ,<br>f = 1kHz, V <sub>L1/L2</sub> = 54V<br>I <sub>L</sub> = I <sub>REG</sub><br>I <sub>L</sub> = 20mA |            | 0.5<br>0.5        | 1 1               | dB<br>dB                 |

| ACdist           | AC Distortion                                           | Test 1, V <sub>AC</sub> =1.4V <sub>RMS</sub> ,<br>f = 1kHz, V <sub>L1/L2</sub> = 54V<br>I <sub>L</sub> = I <sub>REG</sub><br>I <sub>L</sub> = 20mA  |            | 0,6<br>0.5        | 1 1               | %<br>%                   |

| V <sub>IH1</sub> | DP, MASK, INHL Input Voltage                            | Test 1, V <sub>DD</sub> = 3V, High level = "1"                                                                                                      | 2.4        |                   |                   | V                        |

| V <sub>IH2</sub> | TKL Input Voltage                                       | Test 1, High level = "1"  Remote command (master) (**)  Remote command (slave), V <sub>DD</sub> = 3V                                                | 4<br>2.4   |                   | V <sub>DD</sub>   | V                        |

| ITKLm<br>ITKLs   | TKL Input Current                                       | Remote command (master), V <sub>DD</sub> = 5V<br>Remote command (slave), V <sub>DD</sub> = 3V                                                       | 200<br>150 | 80                |                   | μ <b>Α</b><br>μ <b>Α</b> |

| VIL              | TKL, DP, MASK, INHL Input Voltage                       | Test 1, V <sub>DD</sub> = 3V, Low level = "0"                                                                                                       |            |                   | 0.3               | ٧                        |

| V <sub>OH</sub>  | IHKS, IEHKS, IVEN Output voltage                        | Test 1, V <sub>DD</sub> = 3V, High level = "1"                                                                                                      | 2.7        |                   |                   | V                        |

| V <sub>OL</sub>  | IHKS, IEHKS, IVEN Output voltage                        | Test 1, V <sub>DD</sub> = 3V, High level = "0"                                                                                                      |            |                   | 0.45              | ٧                        |

$<sup>^{\</sup>star}$   $\,$  The values of V\_DDmin and VSUT (Speed up ON) are correlated.

54-04.TBL

<sup>\*\*</sup> The command TKL is defined as "Master", if the line is seized through this pin and as "Slave", is the line has been previously seized by EHKS key and use to maintain the line closed.

#### **FUNCTIONAL DESCRIPTION**

#### **Switches**

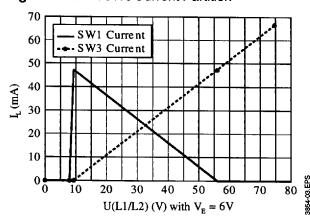

- SW1, SW2 and SW3 isolate the speech and dialing part in On-Hook mode, these 3 switches are open in On-Hook mode and are closed in Off-Hook mode. These switches are closed if HKS or EHKS input Pin is connected to V-, or if TKL input Pin is at logic level "1".

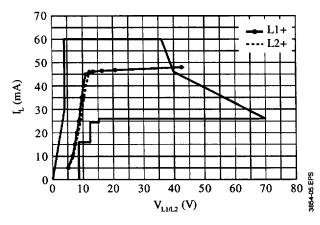

- In Off-Hook mode, the line current goes in the switch SW1 since the current value reaches the threshold of the current detector connected between CURD Pin and VE Pin, when this threshold is reached, and the voltage across L1/L2 wires increases the current increases progressively in the switch SW3 and the 1K resistor connected between V+ Pin and VLREG Pin and decreases in the switch SW1. The current threshold is internally fixed at 47mAtypical, if neccessary, this one can be increased by connecting an external resistor between CURD Pin and VE Pin.

- SW5 is closed in On-Hook mode to connect the ring part, in Off-Hook mode this switch is opened and the ringer part is disconnected.

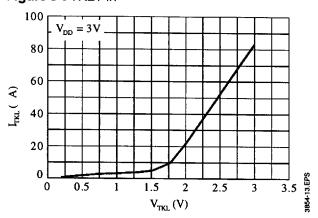

Figure 1: SW1/SW3 Current Partition

## **Logic Control**

The EHKS device is controlled by a microcontroller through:

- Output Pins IHKS and IEHKS which give the status how the line has been taken.

- Output Pin IVEN which gives the status of the presence of a line current.

- Input Pin TKL to maintain the line closed when it has been previously taken through EHKS key

- Input Pin DP to generate the Pulse dialing and the Flash signalization.

- Input Pin MASK to control the line current during Pulse dialing and Flash signalization

- Input INHL which forbids to close the line through HKS switch and EHKS Key, if INHL and TKL Pins are simultaneously at logic level "1". This feature can be used in an answering machine.

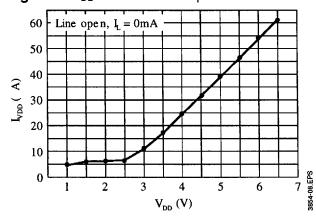

- The V<sub>DD</sub> supplies all the logic control, a speed up mode charges V<sub>DD</sub> capacitor to 2.9V, at start up and each time that the V<sub>DD</sub> supply goes below 2.6V.

#### **Timer**

A timer feature allows the line current to go upper 90mA and lower 150mA, at the start up, to realize the incoming call detection requested by French requirements. The time duration (Tstart) of this upper current limitation is fixed by the capacitor, Ctimer, connected on TIMER Pin.

Tstart =  $0.12 \times 10^6 \times Ctimer$

## Ringer Interface

Three diodes of the ringer bridge are integrated. In Inhibit the line mode, INHL and TKL Pins simultaneously at logic level "1", the switch SW5 is opened and the presence of a ringing signal can be detected on Pin VRING where the ring frequency is not filtered.

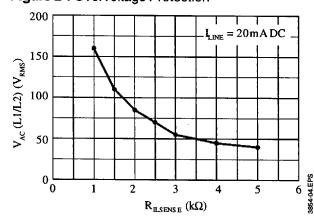

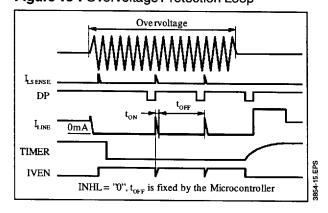

### **Overvoltage Protection**

An overvoltage protection is integrated to open the line when the voltage across the line wires L1 & L2 is too high. The voltage threshold where the line is open is fixed by the external resistor connected on ILSENSE Pin. The overvoltage protection circuit is reseted if the DP pin goes to logic level "0".

Figure 2: Overvoltage Protection

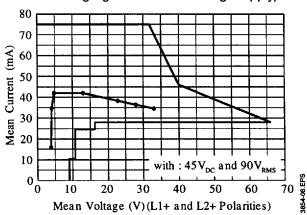

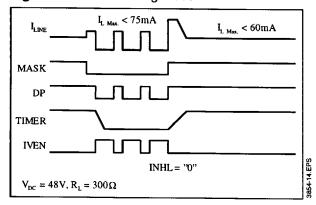

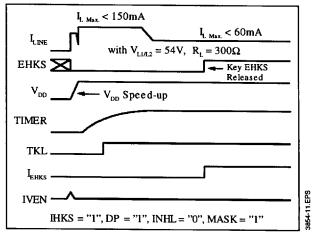

Figure 3: French DC Mask

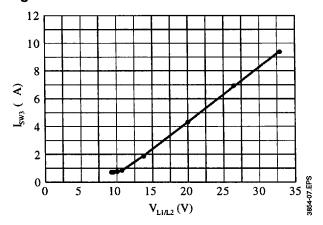

Figure 5: ISW3 Current Information

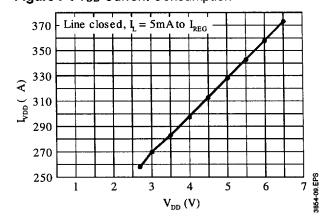

Figure 6: VDD Current Consumption

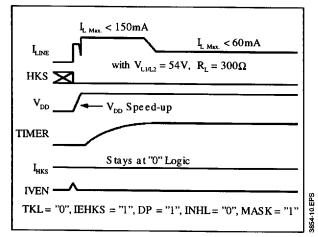

Figure 4: French Incoming Call (Off-Hook with AC ring signal and DC exchange supply)

Figure 7: V<sub>DD</sub> Current Consumption

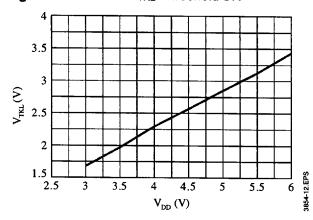

Figure 8: TKL Pin - VTKL Threshold ON

Figure 10: Off-Hook with mechanical hook switch

Figure 12: Pulse Dialing Mode

Figure 9: TKL Pin

Figure 11: Off-Hook with EHKS kev

Figure 13: Overvoltage Protection Loop

The ratio  $\frac{t_{\text{ON}}}{t_{\text{ON}}+t_{\text{OFF}}}$  influences the power dissipated in the ST3854 device.

To limit the power dissipated in the ST3854, toFF should be higher than 200ms.

Note: If during toff, VDD voltage decreases lower than the speed up threshold, the internal latch is reseted, same action than DP pin.

## **TESTS**

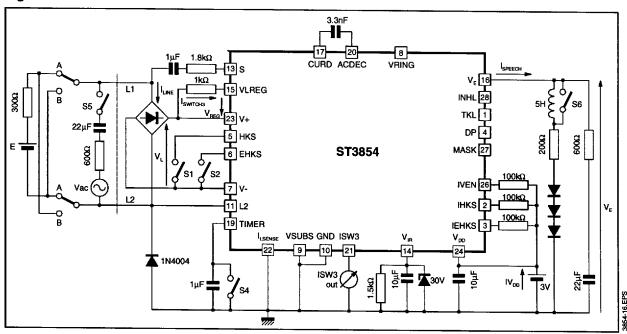

Figure 14: Test 1

$$R_{SWI1/2} = \frac{V_L - V_E}{I_{SPEECH}} \;, \;\; R_{SWI3} = \frac{V_{15} - V_E}{I_{SWITCH3}} \;, \;\; I_{BIAS} = I_{LINE} - I_{SPEECH} \;, \;\; R_{ISW3} = \frac{I_{SWITCH3}}{I_{SW3OUT}} \;.$$

Ітім is measured in S4 switch.

IREG and ISTART are Iline values which depend of the switch configuration.

All the parameters are measured in both polarities (S3 in A & B positions)

| Parameters                                                 | S1     | S2     | S4         | <b>S</b> 5 | S6<br>Opened |  |

|------------------------------------------------------------|--------|--------|------------|------------|--------------|--|

| R <sub>SWI1/2</sub> / I <sub>BIAS</sub> / IV <sub>DD</sub> | Closed | Opened | Closed     | Opened     |              |  |

| VE1 / VL1 / RSWI3 / IREG RISW3 / VDD / Vsut                | Closed | Opened | Opened     | Opened     | Opened       |  |

| REG                                                        | Opened | Closed | Opened     | Opened     | Opened       |  |

| I <sub>LEAK</sub> / R <sub>SOFF</sub> / R <sub>SON</sub>   | Opened | Opened | Opened     | Opened     | Opened       |  |

| ISTART                                                     | Closed | Opened | Closed     | Opened     | Closed       |  |

| Ітім                                                       | Closed | Opened | Closed (*) | Opened     | Opened       |  |

| ACatt / ACdist                                             | Closed | Opened | Opened     | Closed     | Opened       |  |

## **TESTS** (continued)

Figure 15: Test 2

Imask: S7 closed, lopl: S7 opened

Figure 16: Test 3

$$R_{SWI5} = \frac{V - V_{IR}}{I_{OUT}}$$

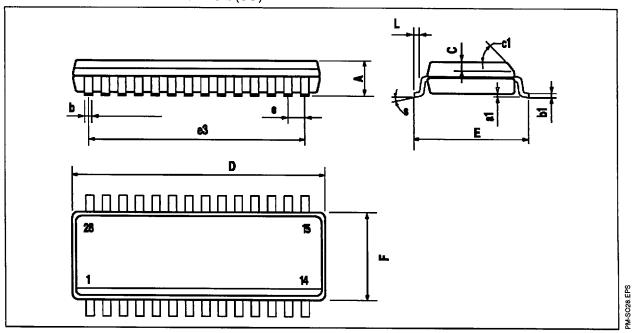

#### PACKAGE MECHANICAL DATA

28 PINS - PLASTIC MICROPACAKGE (SO)

| Dimensions   | Millimeters |       |       | Inches |       |       |  |

|--------------|-------------|-------|-------|--------|-------|-------|--|

| Dilliensions | Min.        | Тур.  | Max.  | Min.   | Тур.  | Max.  |  |

| Α            |             |       | 2.65  |        |       | 0.104 |  |

| a1           | 0.1         |       | 0.3   | 0.004  |       | 0.012 |  |

| b            | 0.35        |       | 0.49  | 0.014  |       | 0.019 |  |

| b1           | 0.23        |       | 0.32  | 0.009  |       | 0.013 |  |

| С            | ,=          | 0.5   |       |        | 0.020 |       |  |

| c1           |             |       | 45° ( | Тур.)  |       | I     |  |

| D            | 17.7        |       | 18.1  | 0.697  |       | 0.713 |  |

| E            | 10          |       | 10.65 | 0.394  |       | 0.419 |  |

| е            |             | 1.27  |       |        | 0.050 |       |  |

| e3           |             | 16.51 |       |        | 0.65  |       |  |

| F            | 7.4         |       | 7.6   | 0.291  |       | 0.299 |  |

| L            | 0.4         |       | 1.27  | 0.016  | 1-1   | 0.050 |  |

| S            | 8° (Max.)   |       |       |        |       |       |  |

ESD - The SGS-THOMSON Internal Quality Standards set a large of 2kV that each pin of the device should withstand in a series of test based on the Human Body Model (MIL STD 883 Method 3015): with C = 100 pF,  $R = 1500 \Omega$  and performing 3 pulses for each pin versus  $V_{CC}$  and GND.

Device characterization showed that, in front of the SGS-THOMSON Internally Quality Standards, all pins of ST3854 withstand at least 750V. The above points are not expected to represent a practical limit for the correct device utilization nor for its reliability in the field. Nonetheless they must be mentionned in connection with the applicability of the different SURE 6 requirements to ST3854.

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1996 SGS-THOMSON Microelectronics - All Rights Reserved

## SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.