# STARMAN<sup>TM</sup> CHANNEL DECODER

#### FRONT\_END INTERFACE:

- IF input carrier frequency: f = 1.84 MHz

- Single internal 6 bit A/D converter

- QPSK demodulation

- Input symbol frequency: Fs = 1.84 Msymbols/s

- Digital Nyquist root filter:

roll-off value of 0.4

- Digital carrier loop:

- on-chip quadrature demodulator and tracking loop

- lock detector

- C/N indicator

- Digital timing recovery:

- internal timing error evaluation, filter and correction

- Digital AGC:

- internal signal power estimation and filter

- output control signal for AGC (1 bit PWM)

# FORWARD ERROR CORRECTION:

- Inner decoder:

- Viterbi soft decoder for convolutional codes, constraint length M=7, Rate 1/2

- Deinterleaver block

- Outer decoder:

- Reed-Solomon decoder for 32 parity bytes; correction of up to 16 byte errors

- Block lengths: 255

- Energy dispersal descrambler

# BACK\_END INTERFACE:

- Broadcast Channel selection

- Audio Service Component selection to MPEG decoder

- Service Component selection

#### CONTROL:

I<sup>2</sup>C serial Bus control interface

#### **DECRYPTION:**

WES scheme supported

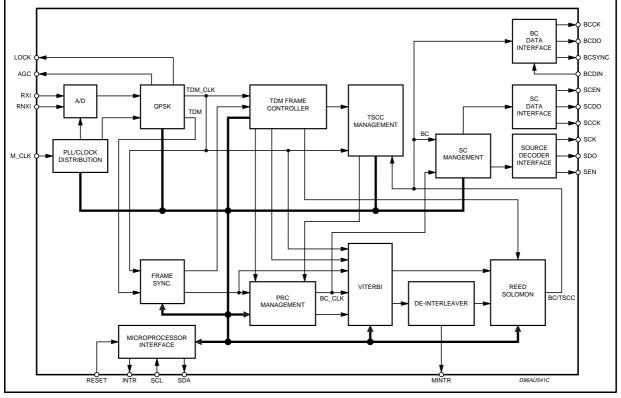

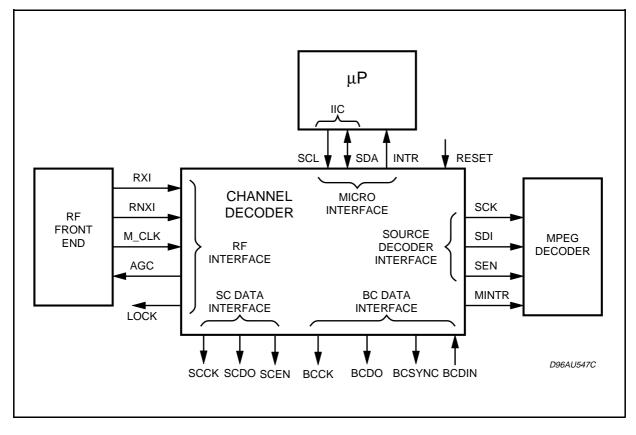

# DESCRIPTION

Designed for World Space satellites digital audio receivers, the STA002 Digital Receiver Front-end integrates all the blocks needed to demodulate incoming digital satellite audio signals from the tuner: analog to digital converter, QPSK demodulator, signal power estimator, automatic gain control, Viterbi decoder, deinterleaver, Reed-Solomon decoder and energy dispersal descrabler. Its advanced error correction functions guarantees a low error rate even with small low gain receiver antennas.

Additional functions include the selection of broadcast channel, service components and audio components for source decoding:

- The MPEG Audio bitstream is provided at the serial audio output port.

- The Broadcast Channel is provided to the serial data output port.

- The Service Component is provided at the SC output interface.

World Space encryption scheme is supported for pay programs and paging.

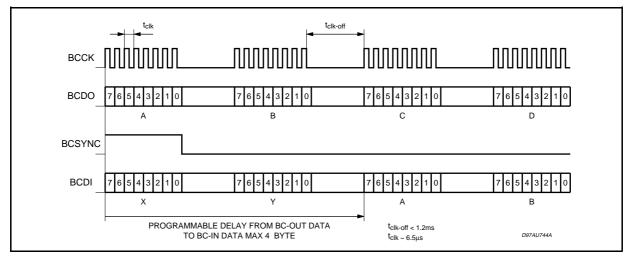

# Fig. 1: Channel Decoder Block Diagram

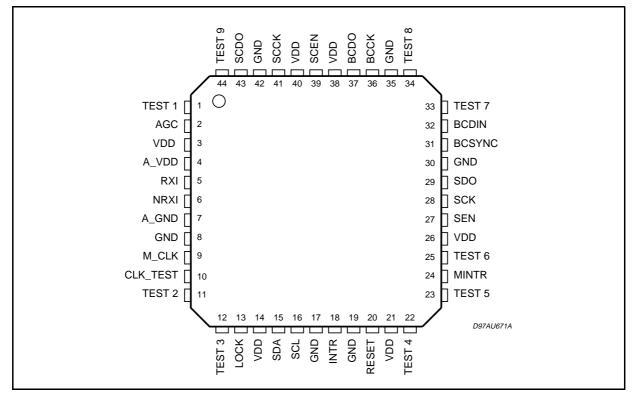

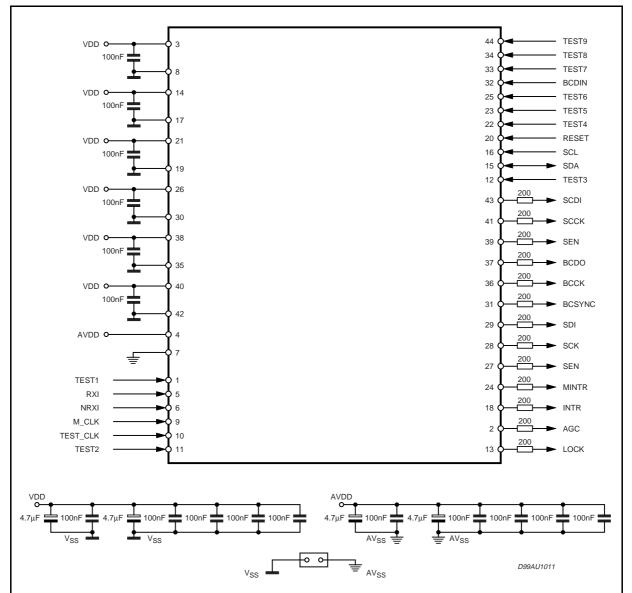

Fig. 2: Pin Connection

5

# **PIN DESCRIPTION**

| Туре                     | Pin Name           | Туре          | Function                       | PAD Description                      |

|--------------------------|--------------------|---------------|--------------------------------|--------------------------------------|

| 1, 11, 12                | TEST (1:3)         | Ι             | Test Pin                       | CMOS Input Pad Buffer with Pull-Down |

| 22                       | 23, 25, 33, 34, 44 | TEST<br>(4:9) | 1                              | Test Pin                             |

| 2                        | AGC                | 0             | AGC Output                     | CMOS 2mA Output Driver               |

| 3, 14, 21,<br>26, 38, 40 | VDD                |               | Positive Supply Voltage        |                                      |

| 4                        | A_VDD              |               | Analog Positive Supply Voltage |                                      |

| 5                        | RXI                | I             | IF Signal Input                | Analog Pad Buffer                    |

| 6                        | NRXI               | 1             | IF Signal Input                | Analog Pad Buffer                    |

| 7                        | A_GND              |               | Analog Ground                  |                                      |

| 9                        | M_CLK              | Ι             | Master Clock                   | Analog Pad Buffer with Comparator    |

| 10                       | CLK_TEST           |               | Not Connected                  | CMOS Input Pad Buffer                |

| 13                       | LOCK               | 0             | Carrrier Lock Indicator        | CMOS 2mA Output Driver               |

| 15                       | SDA                | I/O           | Data + ACK                     | CMOS Schmitt Trigger Bdir Pad Bufer  |

| 16                       | SCL                | Ι             | Serial Clock                   | CMOS Input Pad Schmitt Triggered     |

| 8, 17, 19,<br>30, 35, 42 | GND                |               | Negative Supply Voltage        |                                      |

| 18                       | INTR               | 0             | Interrupt                      | CMOS 2mA Output Driver               |

| 20                       | RESET              | I             | Master Reset                   | CMOS Input Pad Buffer with Pull-Up   |

| 24                       | MINTR              | 0             | MPEG Interrupt                 | CMOS 2mA Output Driver               |

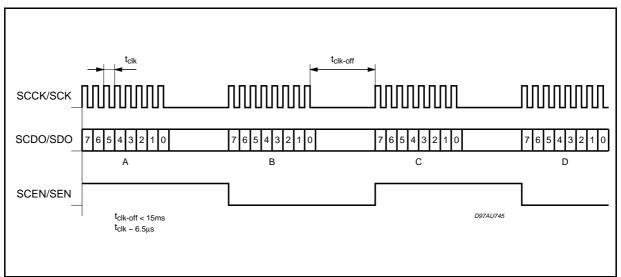

| 27                       | SEN                | 0             | MPEG Enable                    | CMOS 2mA Output Driver               |

| 28                       | SCK                | 0             | MPEG Clock                     | CMOS 2mA Output Driver               |

| 29                       | SDO                | 0             | MPEG Bit Output                | CMOS 2mA Output Driver               |

| 31                       | BCSYNC             | 0             | Broadcast Channel Sync         | CMOS 2mA Output Driver               |

| 32                       | BCDIN              | Ι             | Broadcast Channel Data Input   | CMOS Input Pad Buffer                |

| 36                       | BCCK               | 0             | Broadcast Channel Clock        | CMOS 2mA Output Driver               |

| 37                       | BCDO               | 0             | Broadcast Channel Data Output  | CMOS 2mA Output Driver               |

| 39                       | SCEN               | 0             | Service Component Enable       | CMOS 2mA Output Driver               |

| 41                       | SCCK               | 0             | Service Component Clock        | CMOS 2mA Output Driver               |

| 43                       | SCDO               | 0             | Service Component Data Output  | CMOS 2mA Output Driver               |

Note: pin 1, 11, 12 and 22 must be connected to ground in functional mode.

# THERMAL DATA

| Symbol                | Parameter                              | Value | Unit |

|-----------------------|----------------------------------------|-------|------|

| R <sub>th j-amb</sub> | Thermal resistance Junction to Ambient | 85    | °C/W |

# ABSOLUTE MAXIMUM RATINGS

| Symbol            | Parameter              | Value                        | Unit |

|-------------------|------------------------|------------------------------|------|

| V <sub>DD</sub>   | Power Supply           | -0.3 to 4                    | V    |

| Vi                | Voltage on Input pins  | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Vo                | Voltage on output pins | -0.3 to V <sub>DD</sub> +0.3 | V    |

| T <sub>stg</sub>  | Storage Temperature    | -40 to +150                  | °C   |

| T <sub>oper</sub> | Operative ambient temp | -20 to +85                   | °C   |

#### **ELECTRICAL CHARACTERISTICS:** VDD = $3.3V \pm 0.3V$ ; Tamb = 0 to 70°C; Rg = $50\Omega$ unless otherwise specified

# **DC OPERATING CONDITIONS**

| Symbol          | Parameter                      | Value        |

|-----------------|--------------------------------|--------------|

| V <sub>DD</sub> | Power Supply Voltage           | 2.7 to 3.6V  |

| Tj              | Operating Junction Temperature | -20 to 125°C |

#### **GENERAL INTERFACE ELECTRICAL CHARACTERISTICS**

| Symbol           | Parameter                                          | Test Condition | Min. | Тур. | Max. | Unit | Note |

|------------------|----------------------------------------------------|----------------|------|------|------|------|------|

| ۱ <sub>۱۲</sub>  | Low Level Input Current<br>Without pull-up device  | $V_i = 0V$     | -10  |      | 10   | μA   | 1    |

| I <sub>IH</sub>  | High Level Input Current<br>Without pull-up device | $V_i = V_{DD}$ | -10  |      | 10   | μA   | 1    |

| V <sub>esd</sub> | Electrostatic Protection                           | Leakage < 1µA  | 2000 |      |      | V    | 2    |

Note 1: The leakage currents are generally very small, < 1nA. The value given here is a maximum that can occur after an electrostatic stress on the pin. Note 2: Human Body Model.

#### **DC ELECTRICAL CHARACTERISTICS**

| Symbol          | Parameter                 | Test Condition        | Min.                 | Тур. | Max.            | Unit | Note |

|-----------------|---------------------------|-----------------------|----------------------|------|-----------------|------|------|

| VIL             | Low Level Input Voltage   |                       |                      |      | $0.2^{*}V_{DD}$ | V    |      |

| VIH             | High Level Input Voltage  |                       | 0.8*V <sub>DD</sub>  |      |                 | V    |      |

| V <sub>ol</sub> | Low Level Output Voltage  | I <sub>ol</sub> = Xma |                      |      | 0.4V            | V    | 1, 2 |

| V <sub>oh</sub> | High Level Output Voltage |                       | 0.85*V <sub>DD</sub> |      |                 | V    | 1, 2 |

|                 |                           |                       |                      |      |                 |      |      |

Note 1: Takes into account 200mV voltage drop in both supply lines.

Note 2: X is the source/sink current under worst case conditions and is reflected in the name of the I/O cell according to the drive capability.

# PULL\_UP & PULL\_DOWN CHARACTERISTICS

| Symbol          | Parameter                          | Test Condition                   | Min. | Тур. | Max. | Unit | Note |

|-----------------|------------------------------------|----------------------------------|------|------|------|------|------|

| I <sub>pu</sub> | Pull-up current                    | $V_i = 0V$                       | -25  | -66  | -125 | μA   | 1    |

| I <sub>pu</sub> | Pull-up current                    | V <sub>i</sub> = Vdd             | 25   | 66   | 125  | μΑ   | 1    |

| R <sub>pu</sub> | Equivalent Pull-up<br>Resistance   | $V_i = 0V$                       |      | 50   |      | kΩ   |      |

| R <sub>pu</sub> | Equivalent Pull-down<br>Resistance | V <sub>i</sub> = V <sub>DD</sub> |      | 50   |      | kΩ   |      |

Note 1: Min. condition:  $V_{DD} = 2.7V$ ,  $125^{\circ}C$  Min process Max. condition:  $V_{DD} = 3.6V$ ,  $-20^{\circ}C$  Max.

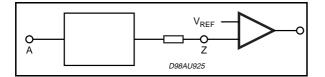

#### M\_CLK Electrical Characteristics (Pin number 9)

| Symbol           | Parameter                | Min.                 | Тур.                 | Max.                 | Unit |

|------------------|--------------------------|----------------------|----------------------|----------------------|------|

| Vil              | Low Level Input Voltage  |                      |                      | V <sub>DD</sub> -1.7 | V    |

| Vih              | High Level Input Voltage | V <sub>DD</sub> -0.9 |                      |                      | V    |

| V <sub>ref</sub> | Input Reference Voltage  |                      | V <sub>DD</sub> -1.3 |                      | V    |

#### POWER DISSIPATION

| Symbol | Parameter                                   | Test Condition     | Min. | Тур. | Max. | Unit | Note |

|--------|---------------------------------------------|--------------------|------|------|------|------|------|

| PD     | Power Dissipation<br>@ V <sub>DD</sub> = 3V | M_CLK = 39,0269MHz |      |      | 80   | mW   |      |

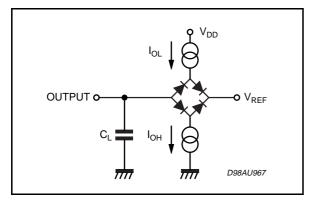

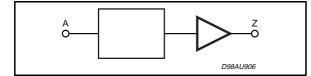

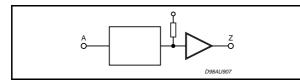

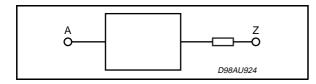

Figure 4. Test Load Circuit

# **Test Load**

| Output        | IOL   | Юн    | C∟    | VREF |

|---------------|-------|-------|-------|------|

| SDA           | 5mA   |       | 100pF | 3.6V |

| Other Outputs | 100μΑ | 100μΑ | 100pF | 1.5V |

|               |       |       |       |      |

#### FUNCTIONAL DESCRIPTION

The STA002 integrates all the functions needed to demodulate the signal coming from the RF FE; with reference to the block diagram (Fig 1), STA002 includes the following functions:

#### Microprocessor interface

Data transmission from microcontroller to the device takes place through the 2 wires (SDA and SCL) I2C bus interface. STA002 acts always as a slave in all its communications.

#### Interface to the Front-end

This block receives from the RF front-end the QPSK modulated signal, centered at 1.84 MHz (2nd IF frequency). This signal is over sampled using the Master Clock and converted to digital on 6 bits in 2's complement format. The same frequency is also used to provide the clock signal for the QPSK demodulator block.

#### QPSK

This block is composed by:

- AGC1

- quadrature demodulator

- carrier recovery

- timing recovery

- frequency sweep generator

- AGC2

- lock indicator

- carrier to noise estimator

To assure flexibility and to cover different working conditions most of the parameters of each function can be programmed through the I2C interface.

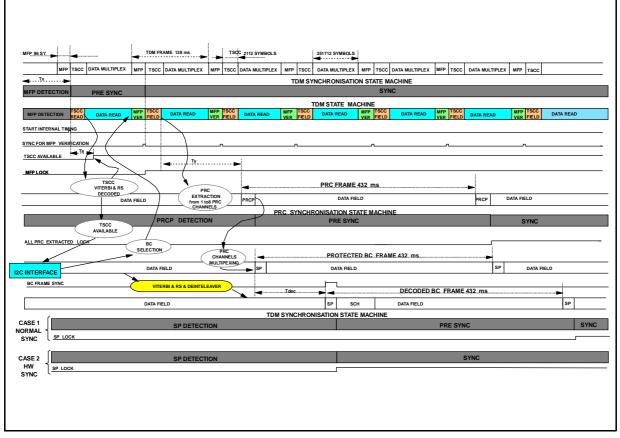

#### **TDM Demultiplexer**

The TDM frame is divided into 3 fields.

The first is the Master Frame Preamble (MFP) which contains the synchronisation word. The second, the Time Slot Control Channel (TSCC), contains information about the organization of the Prime Rate Channel data which follows. The third, is the data field; it contains 96 Prime Rate Channels of 16 Kbit/s each; up to 8 Prime Rate Channels are grouped into one Broadcast Channel.

The TDM demultiplexer executes the extraction and decoding of one Broadcast Channel from the TDM stream, according to the instructions coming from the microcontroller. The decoding flow is the following:

#### - TDM synchronization

The master frame synchronization block receives

the demodulated symbol stream from the QPSK demodulator and performs the alignment detecting the Master Frame Preamble.

The known syncronization word is also used to correct the phase ambiguity intrinsic in QPSK demodulation.

#### - TSCC extraction

The information of the Prime Rate Channels to Broadcast Channels allocation are contained in the TSCC field which is synchronised with the MFP.

In this stage all the information related to the TSCC are extracted and made available for the microcontroller via the I2C interface.

- PRC extraction and BC recovery

This block, after the Broadcast Channel (BC) selection, performs the extraction and synchronisation of the Prime Rate Channels (PRC) belonging to the selected BC.

The extracted PRCs are aligned and grouped into one BC data stream.

- FEC decoder

The extracted BC is decoded using a concatenated Forward Error Correction approach.

The FEC circuitry utilizes three error correction stages: a rate 1/2 Viterbi decoder, a 255x4 bytes convolutional deinterleaver and a 255/223 Reed Solomon decoder.

The RS input blocks are 255 bytes long with 32 parity bytes.

Up to 16 errored bytes can be fixed in each RS block.

#### **BC** demultiplexer

Every BC contains up to 8 Service Components; the Service Control Header (SCH) field contains all the information related to the organization of the Service Components. This stage provides the extraction of the SCH from the BC.

The SCH is available through I2C bus to the microcontroller for the selection of the desired Audio Service Component, which is then supplied directly to the MPEG Source decoder via the audio Service Component Interface.

#### **DEVICE OPERATION**

#### 1. I<sup>2</sup>C BUS SPECIFICATION

The STA002 supports the I2C protocol. This protocol defines any device that sends data on to the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the others as the slave. The master will always initiate the transfer and will provide the serial clock

for synchronisation. The STA002 is always a slave device in all its communications.

#### **1.1 COMMUNICATION PROTOCOL**

#### 1.1.0 Data transition or change

Data changes on the SDA line must only occur when the SCL clock is low. SDA transitions while the clock is high are used to identify START or STOP condition.

#### 1.1.1 Start condition

START is identified by a high to low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must precede any command for data transfer.

#### 1.1.2 Stop condition

STOP is identified by low to high transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A STOP condition terminates communications between STA002 and the bus master.

#### 1.1.3 Acknowledge bit

An acknowledge bit is used to indicate a successful data transfer. The bus transmitter, either master or slave, will release the SDA bus after sending 8 bits of data.

During the 9th clock pulse the receiver pulls the SDA bus low to acknowledge the receipt of 8 bits of data.

Some registers do not give acknowledge when the data is not available.

#### 1.1.4 Data input

During the data input the STA002 samples the SDA signal on the rising edge of the clock SCL. For correct device operation the SDA signal has to be stable during the rising edge of the clock and the data can change only when the SCL line is low.

#### **1.2 DEVICE ADDRESSING**

To start communication between the master and the STA002, the master must initiate with a start condition. Following this the master sends onto the SDA line 8 bits (MSB first) corresponding to the device select address and read or write mode.

The 7 most significant bits are the device address identifier, corresponding to the I2C bus definition. For the STA002 these are fixed as 1101010.

The 8th bit (LSB) is the read or write operation bit

(RW; set to 1 in read mode and to 0 in write mode). After a START condition the STA002 identifies on the bus the device address and if matching it will acknowledges the identification on SDA bus during the 9th bit time.

The following 2 bytes after the device identification byte are the internal space address.

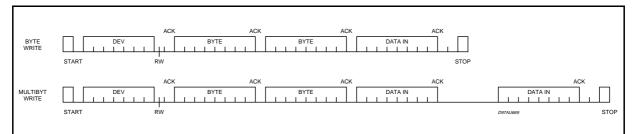

#### 1.3 WRITE OPERATION (see fig. 5)

Following a START condition the master sends a device select code with the RW bit set to 0.

The STA002 gives the acknowledge and waits for the 2 bytes of internal address. The least significant 10 bits of the 2 bytes address provides access to any of the internal registers. The most significant bit means incremental mode (1 = autoincremental, 0 = no) and the other bits are set to zero.

After the receiption of each of the internal bytes address the STA002 again responds with an ac-knowledge.

#### 1.3.1 Byte write

In the byte write mode the master sends one data byte and this is acknowledged by STA002. The master then terminates the transfer by generating a STOP condition.

#### 1.3.2 Multibyte write

The multibyte write mode can start from any internal address. The master sends the data and each one is acknowledged by the STA002. The transfer is terminated by the master generating a STOP condition.

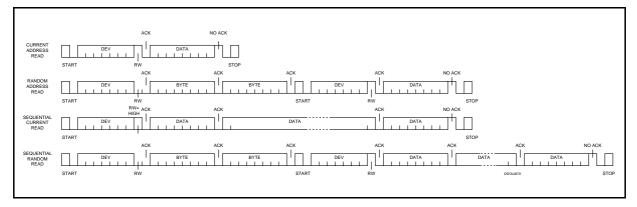

#### 1.4 READ OPERATION (see Fig. 6)

#### 1.4.1 Current byte address read

The STA002 has an internal byte address counter. Each time a byte is written or read, this counter, according to the autoincremental bit setting, is incremented or not.

For the current byte address read mode, following a START condition the master sends the device address with the RW bit set to 1. The STA002 acknowledges this and outputs the byte addressed by the internal byte address counter.

The counter is then incremented or not depending on the autoincremental bit. The master does not acknowledge the received byte, but terminates the transfer with a STOP condition.

#### 1.4.2 Random byte address read

A dummy write is performed to load the byte address into the internal address register.

#### Fig. 5: Write Mode Sequence

#### Fig. 6: Read Mode Sequence

This is followed by another START condition from the master and the device address repeated with the RW bit set to 1. The STA002 acknowledges this and outputs the byte addressed by the internal byte address counter.

The master does not acknowledge the received byte, but terminates the transfer with a STOP condition.

1.4.3 Sequential address read

This mode can be initiated with either a current address read or a random address read. However in this case the master does acknowledge the data byte output and the STA002 continues to output the next byte in sequence.

To terminate the stream of bytes the master does not acknowledge the last received byte, but terminates the transfer with a STOP condition.

The output data stream is from consecutive byte addresses, with the internal byte address counter automatically incremented after each byte output.

#### 1.5 REGISTER MAP (8 BIT REGISTER)

| FUNCTION      | START   | ADDRESS    | END A   | DDRESS     |

|---------------|---------|------------|---------|------------|

|               | HEX_COD | BIN        | HEX_COD | BIN        |

| SCH           | 000H    | 000000000  | 03FH    | 0000111111 |

| RFU           | 040H    | 0000111111 | 07FH    | 0001111111 |

| QPSK          | 080H    | 001000000  | 09FH    | 0010011111 |

| RFU           | 0A0H    | 0010100000 | 0FFH    | 0011111111 |

| SCH_MEM       | 100H    | 010000000  | 1EBH    | 0111101011 |

| RFU           | 1ECH    | 0111101100 | 1FFH    | 0111111111 |

| TDM_MULTIPLEX | 200H    | 100000000  | 23FH    | 1000111111 |

| RFU           | 240H    | 1001000000 | 2FFH    | 1011111111 |

| TSCC_MEM      | 300H    | 110000000  | 3C1H    | 1111000001 |

| RFU           | 3C2H    | 1111000010 | 3FFH    | 1111111111 |

1.5.1 Register address List (by function)

#### 1.5.2 SCH Registers

| HEX_COD | DEC_COD | REGISTER NAME              | ТҮРЕ | RESET<br>VALUE |

|---------|---------|----------------------------|------|----------------|

| 000H    | 0       | BRI_REG & NSC_REG (note 1) | R    |                |

| 001H    | 1       | EC_REG (note 1)            | R    |                |

| 002H    | 2       | AFCI 1_REG (note 1)        | R    |                |

| 003H    | 3       | AFCI 2_REG (note 1)        | R    |                |

| 004H    | 4       | SOF_SF_REG (note 1)        | R    |                |

| 005H    | 5       | ADF1_REG (7:0) (note 1)    | R    |                |

| 006H    | 6       | ADF1_REG (15:8) (note 1)   | R    |                |

| 007H    | 7       | ADF2_REG (7:0) (note 1)    | R    |                |

| 008H    | 8       | ADF2_REG (15:8) (note 1)   | R    |                |

| 009H    | 9       | ADF2_REG (23:16) (note 1)  | R    |                |

| 00AH    | 10      | ADF2_REG (31:24) (note 1)  | R    |                |

| 00BH    | 11      | ADF2_REG (39:32) (note 1)  | R    |                |

| 00CH    | 12      | ADF2_REG (47:40) (note 1)  | R    |                |

| 00DH    | 13      | ADF2_REG (55:48) (note 1)  | R    |                |

| 00EH    | 14      | ADF2_REG (63:56) (note 1)  | R    |                |

| 00FH    | 15      | SEL_SC_REG                 | R/W  | 98H            |

| 010H    | 16      | IW_REG (7:0) (note 2)      | W    | 41H            |

| 011H    | 17      | IW_REG (15:8) (note 2)     | W    | 42H            |

| 012H    | 18      | IW_REG (23:16) (note 2)    | W    | 43H            |

| 013H    | 19      | IW_REG (31:24) (note 2)    | W    | 44H            |

| 014H    | 20      | IW_REG(39:32) (note 2)     | W    | 45H            |

| 015H    | 21      | IW_REG (47:40) (note 2)    | W    | 46H            |

| 016H    | 22      | IW_REG (55:48) (note 2)    | W    | 47H            |

| 017H    | 23      | IW_REG (63:56) (note 2)    | W    | 48H            |

| 018H    | 24      | EM_REG                     | R/W  | 00H            |

| 019H    | 25      | PIWE_REG (7:0) (note 2)    | R/W  | 00H            |

| 01AH    | 26      | PIWE_REG (15:8) (note 2)   | R/W  | 00H            |

| 01BH    | 27      | BCIN_DELAY_REG             | R/W  | 00H            |

| 01CH    | 28      | BC_ALARM_REG               | R/W  | 20H            |

| 01DH    | 29      | TEST_PURPOSE               | R/W  |                |

| 01EH    | 30      | RFU                        |      |                |

| 01FH    | 31      | RFU                        |      |                |

| 020H    | 32      | TEST PURPOSE               | R/W  |                |

| 021H    | 33      | TEST PURPOSE               | R/W  |                |

| 022H    | 34      | TEST PURPOSE               | R/W  |                |

| 023H    | 35      | TEST PURPOSE               | R/W  |                |

| 024H    | 36      | TEST PURPOSE               | R/W  |                |

| 025H    | 37      | TEST PURPOSE               | R/W  |                |

| 026H    | 38      | TEST PURPOSE               | R/W  |                |

| 027H    | 39      | TEST PURPOSE               | R/W  |                |

| 028H    | 40      | TEST PURPOSE               | R/W  |                |

| 029H    | 41      | TEST PURPOSE               | R/W  |                |

Note 1: no acknowledge when data is not available Note 2: when updated all bytes must be written

57

# 1.5.2 SCH Registers

| HEX_COD | DEC_COD | REGISTER NAME           | TYPE | RESET<br>VALUE |

|---------|---------|-------------------------|------|----------------|

| 02AH    | 42      | TEST PURPOSE            | R/W  |                |

| 02BH    | 43      | TEST PURPOSE            | R/W  |                |

| 02CH    | 44      | TEST PURPOSE            | R/W  |                |

| 02DH    | 45      | TEST PURPOSE            | R/W  |                |

| 02EH    | 46      | TEST PURPOSE            | R/W  |                |

| 02FH    | 47      | TEST PURPOSE            | R/W  |                |

| 030H    | 48      | TEST PURPOSE            | R/W  |                |

| 031H    | 49      | TEST PURPOSE            | R/W  |                |

| 032H    | 50      | TEST PURPOSE            | R/W  |                |

| 033H    | 51      | TEST PURPOSE            | R/W  |                |

| 034H    | 52      | TEST PURPOSE            | R/W  |                |

| 035H    | 53      | TEST PURPOSE            | R/W  |                |

| 036H    | 54      | TEST PURPOSE            | R/W  |                |

| 037H    | 55      | TEST PURPOSE            | R/W  |                |

| 038H    | 56      | PIW_RAM (7:0) (note1)   | W    | 00H            |

| 039H    | 57      | PIW_RAM (15:8) (note1)  | W    | 00H            |

| 03AH    | 58      | PIW_RAM (23:16) (note1) | W    | 00H            |

| 03BH    | 59      | PIW_RAM (31:24) (note1) | W    | 00H            |

| 03CH    | 60      | PIW_RAM (39:32) (note1) | W    | 00H            |

| 03DH    | 61      | PIW_RAM (47:40) (note1) | W    | 00H            |

| 03EH    | 62      | PIW_RAM (55:48) (note1) | W    | 00H            |

| 03FH    | 63      | PIW_RAM (63:56) (note1) | W    | 00H            |

Note 1: when updated all bytes must be written

# 1.5.3 QPSK Registers

| HEX_COD | DEC_COD | REGISTER NAME       | ТҮРЕ | RESET<br>VALUE |  |

|---------|---------|---------------------|------|----------------|--|

| 080H    | 128     | QPSK_CONTROL1       | R/W  | 10H            |  |

| 081H    | 129     | QPSK_CONTROL2       | R/W  | 90H            |  |

| 082H    | 130     | AGC1 _REF1 (note 1) | R/W  | 06H            |  |

| 083H    | 131     | AGC1 _REF2 (note 1) | R/W  | 01H            |  |

| 084H    | 132     | AGC1_BETA           | R/W  | 00H            |  |

| 085H    | 133     | AGC1_INTG           | R/W  | 7FH            |  |

| 086H    | 134     | AGC2_REF            | R/W  | 16H            |  |

| 087H    | 135     | AGC2 _BETA          | R/W  | 00H            |  |

| 088H    | 136     | AGC2_INTG           | R/W  | 23H            |  |

| 089H    | 137     | CN_CNT              | R/W  | FFH            |  |

| 08AH    | 138     | SYMFREQ1 (note 1)   | R/W  | D3H            |  |

| 08BH    | 139     | SYMFREQ2 (note 1)   | R/W  | 11H            |  |

| 08CH    | 140     | SYMFREQ3 (note 1)   | R/W  | 0CH            |  |

| 08DH    | 141     | TIMFLTPAR           | R/W  | 48H            |  |

| 08EH    | 142     | TIMINTG             | R/W  | 00H            |  |

| 08FH    | 143     | CARFLTPAR           | R/W  | 57H            |  |

| 090H    | 144     | IFFREQ1 (note 1)    | R/W  | 37H            |  |

| 091H    | 145     | IFFREQ2 (note 1)    | R/W  | 1DH            |  |

| 092H    | 146     | IFFREQ3 (note 1)    | R/W  | C1H            |  |

| 093H    | 147     | IFFREQ4 (note 1)    | R/W  | 00H            |  |

| 094H    | 148     | CARINTG             | R/W  | 00H            |  |

| 095H    | 149     | RAMPCTRL            | R/W  | 01H            |  |

| 096H    | 150     | CARFREQ1            | R    |                |  |

| 097H    | 151     | CARFREQ2            | R    |                |  |

| 098H    | 152     | CARFREQ3            | R    |                |  |

| 099H    | 153     | FLAG                | R    |                |  |

| 09AH    | 154     | RFU                 |      |                |  |

| 09BH    | 155     | RFU                 |      |                |  |

| 09CH    | 156     | RFU                 |      |                |  |

| 09DH    | 157     | RFU                 |      |                |  |

| 09EH    | 158     | RFU                 |      |                |  |

| 09FH    | 159     | RFU                 |      |                |  |

Note 1: when updated all bytes must be written

57

# 1.5.4 SCH\_MEM Registers

| HEX_COD | DEC_COD | REGISTER NAME         | ТҮРЕ | RESET<br>VALUE |

|---------|---------|-----------------------|------|----------------|

| 100H    | 256     | SC1_LENGHT & SC1_TYPE | R    |                |

| 101H    | 257     | SC1_EC & SC1_PT       | R    |                |

| 102H    | 258     | SC1_PT                | R    |                |

| 103H    | 259     | LANGUAGE 1            | R    |                |

| 104H    | 260     | SC2_LENGHT & SC2_TYPE | R    |                |

| 105H    | 261     | SC2_EC & SC2_PT       | R    |                |

| 106H    | 262     | SC2_PT                | R    |                |

| 107H    | 263     | LANGUAGE 2            | R    |                |

| 108H    | 264     | SC3_LENGHT & SC3_TYPE | R    |                |

| 109H    | 265     | SC3_EC & SC3_PT       | R    |                |

| 10AH    | 266     | SC3_PT                | R    |                |

| 10BH    | 267     | LANGUAGE 3            | R    |                |

| 10CH    | 268     | SC4_LENGHT & SC4_TYPE | R    |                |

| 10DH    | 269     | SC4_EC & SC4_PT       | R    |                |

| 10EH    | 270     | SC4_PT                | R    |                |

| 10FH    | 271     | LANGUAGE 4            | R    |                |

| 110H    | 272     | SC5_LENGHT & SC5_TYPE | R    |                |

| 111H    | 273     | SC5_EC & SC5_PT       | R    |                |

| 112H    | 274     | SC5_PT                | R    |                |

| 113H    | 275     | LANGUAGE 5            | R    |                |

| 114H    | 276     | SC6_LENGHT & SC6_TYPE | R    |                |

| 115H    | 277     | SC6_EC & SC6_PT       | R    |                |

| 116H    | 278     | SC6_PT                | R    |                |

| 117H    | 279     | LANGUAGE 6            | R    |                |

| 118H    | 280     | SC7_LENGHT & SC7_TYPE | R    |                |

| 119H    | 281     | SC7_EC & SC7_PT       | R    |                |

| 11AH    | 282     | SC7_PT                | R    |                |

| 11BH    | 283     | LANGUAGE 7            | R    |                |

| 11CH    | 284     | SC8_LENGHT & SC8_TYPE | R    |                |

| 11DH    | 285     | SC8_EC & SC8_PT       | R    |                |

| 11EH    | 286     | SC8_PT                | R    |                |

| 11FH    | 287     | LANGUAGE8             | R    |                |

| 120H    | 288     | DYNAMIC LABEL         | R    |                |

| 121H    | 289     | DYNAMIC LABEL         | R    |                |

| 122H    | 290     | DYNAMIC LABEL         | R    |                |

| 123H    | 291     | DYNAMIC LABEL         | R    |                |

| 124H    | 292     | DYNAMIC LABEL         | R    |                |

| 12711   | 232     |                       |      |                |

| 1E7H    | 487     | DYNAMIC LABEL         | R    |                |

| 1E8H    | 488     | DYNAMIC LABEL         | R    |                |

| 1E9H    | 489     | DYNAMIC LABEL         | R    |                |

| 1EAH    | 490     | DYNAMIC LABEL         | R    |                |

| 1EBH    | 491     | DYNAMIC LABEL         | R    |                |

Note: no acknowledge when data is not available for all the SCH\_MEM registers

# 1.5.5 TDM\_MULTIPLEX Registers

| HEX_COD | DEC_COD | REGISTER NAME         | ТҮРЕ | RESET<br>VALUE |  |

|---------|---------|-----------------------|------|----------------|--|

| 200H    | 512     | TDM_TRSH 1            | R/W  | 4BH            |  |

| 201H    | 513     | TDM_TRSH 2            | R/W  | 43H            |  |

| 202H    | 514     | PRC_TRSH 1            | R/W  | 2AH            |  |

| 203H    | 515     | PRC_TRSH 2            | R/W  | 23H            |  |

| 204H    | 516     | VITERBI_ERROR_CONTROL | R/W  | 00H            |  |

| 205H    | 517     | SP_TRSH 2             | R/W  | 13H            |  |

| 206H    | 518     | PRC_MAXDELAY          | R/W  | 06H            |  |

| 207H    | 519     | TDM_ALARM             | R/W  | 00H            |  |

| 208H    | 520     | PRC_ALARM             | R/W  | 00H            |  |

| 209H    | 521     | BC_SEL 1 (note)       | R/W  | 01H            |  |

| 20AH    | 522     | BC_SEL2 (note)        | R/W  | 00H            |  |

| 20BH    | 523     | CONTROL               | R/W  | 00H            |  |

| 20CH    | 524     | INT_MASK              | R/W  | 00H            |  |

| 20DH    | 525     | ERROR_ REG            | R/W  | 00H            |  |

| 20EH    | 526     | STATUS REG            | R    |                |  |

| 20FH    | 527     | PRC_ACTIVE_REG        | R    |                |  |

| 210H    | 528     | PRC_LOCK_REG          | R    |                |  |

| 211H    | 529     | PRC_DELAY_REG         | R    |                |  |

| 212H    | 530     | RS_ERROR_CONTROL      | R/W  | 00H            |  |

| 213H    | 531     | VIT_ERROR1            | R/W  |                |  |

| 214H    | 532     | VIT_ERROR2            | R/W  |                |  |

| 215H    | 533     | RS_BYTE_ERROR1        | R/W  |                |  |

| 216H    | 534     | RS_BYTE_ERROR2        | R/W  |                |  |

| 217H    | 535     | RS_BLOCK_ERROR        | R/W  |                |  |

| 218H    | 536     | TEST_PURPOSE          | R/W  |                |  |

| 219H    | 537     | TEST_PURPOSE          | R/W  |                |  |

| 21AH    | 538     | TEST_PURPOSE          | R/W  |                |  |

| 21BH    | 539     | TEST_PURPOSE          | R/W  |                |  |

| 21CH    | 540     | TEST_PURPOSE          | R/W  |                |  |

| 21DH    | 541     | TEST_PURPOSE          | R/W  |                |  |

| 21EH    | 542     | PLL_INT_REG           | R/W  | 00H            |  |

| 21FH    | 543     | TEST_PURPOSE          | R/W  |                |  |

| 220H    | 544     | RESERVED              | R/W  | 07H            |  |

| 221H    | 545     | RESERVED              | R/W  | 1CH            |  |

| 222H    | 546     | RESERVED              | R/W  | 4AH            |  |

| 223H    | 547     | RESERVED              | R/W  | 03H            |  |

| 224H    | 548     | RESERVED              | R/W  | 18H            |  |

| 225H    | 548     | RESERVED              | R/W  | 25H            |  |

| 226H    | 550     | RESERVED              | R/W  | 2EH            |  |

| 227H    | 551     | RESERVED              | R/W  | 3EH            |  |

| 228H    | 552     | RESERVED              | R/W  | 18H            |  |

| 229H    | 553     | RESERVED              | R/W  | 0DH            |  |

| 22AH    | 554     | RESERVED              | R/W  | 18H            |  |

| 22BH    | 555     | RESERVED              | R/W  | 12H            |  |

| 22CH    | 556     | RESERVED              | R/W  | 0AH            |  |

| 22DH    | 557     | RESERVED              | R/W  | 0CH            |  |

Note: when updated all bytes must be written

57

| HEX_COD | DEC_COD | REGISTER NAME | TYPE | RESET<br>VALUE |

|---------|---------|---------------|------|----------------|

| 22EH    | 558     | RESERVED      | R    | 0EH            |

| 22FH    | 559     | RESERVED      | R    | 12H            |

| 230H    | 560     | RESERVED      | R    | 32H            |

| 231H    | 561     | RESERVED      | R    | 0CH            |

| 232H    | 562     | RESERVED      | R    | 1CH            |

| 233H    | 563     | RESERVED      | R    | 2FH            |

| 234H    | 564     | RESERVED      | R    | 0AH            |

| 235H    | 565     | RESERVED      | R    | 0BH            |

| 236H    | 566     | RESERVED      | R    | 2AH            |

| 237H    | 567     | RESERVED      | R    | 09H            |

| 23CH    | 568     | TEST_PURPOSE  | R    | 09H            |

| 23DH    | 569     | TEST_PURPOSE  | R    | 09H            |

| 237EH   | 570     | TEST_PURPOSE  | R    | 09H            |

# 1.5.5 TDM\_MULTIPLEX Registers (continued)

# 1.5.6 TSCC\_MEM Registers

| HEX_COD | DEC_COD | REGISTER NAME  | TYPE | RESET<br>VALUE |

|---------|---------|----------------|------|----------------|

| 300H    | 768     | TSCW 1 (7:0)   | R    |                |

| 301H    | 769     | TSCW 1 (15:8)  | R    |                |

| 302H    | 770     | TSCW 2 (7:0)   | R    |                |

| 303H    | 771     | TSCW 2 (15:8)  | R    |                |

| 304H    | 772     | TSCW 3 (7:0)   | R    |                |

| 305H    | 773     | TSCW 3 (15:8)  | R    |                |

| 306H    | 774     | TSCW 4 (7:0)   | R    |                |

| 307H    | 775     | TSCW 4 (15:8)  | R    |                |

|         |         |                |      |                |

| 3BCH    | 956     | TSCW 95 (7:0)  | R    |                |

| 3BDH    | 957     | TSCW 95 (15:8) | R    |                |

| 3BEH    | 958     | TSCW 96 (7:0)  | R    |                |

| 3BFH    | 959     | TSCW 96 (15:8) | R    |                |

| 3C0H    | 960     | TSCW ID (7:0)  | R    |                |

| 3C1H    | 961     | TSCW ID (15:8) | R    |                |

#### 2. IF INTERFACE

The Master Clock (M\_CLK) is the source of all the STA002 internal timings.

$M\_CLK$  is internally divided to drive the A/D converter and to provide the clock signal for the QPSK block.

The IF input signal, centered at 1.84MHz, is oversampled at a frequency  $F_{ck}$  of M\_CLK/4 or M\_CLK/2 according to STA002 presettings.

#### 2.1 PLL

This fully integrated PLL includes the phase/frequency detector, the charge pump, the filter and

#### the VCO.

The PLL output frequency  $F_{\text{Ck}}$  can be selected via  $I^2C$  interface according to the PLL\_INT\_REG.

Reg. name: PLL\_INT\_REG Internal address: 21E H Reset Value : 00H Type: R/W

| MSB | LSB |

|-----|-----|

|-----|-----|

| X X D5 D4 D3 D2 D1 D0 | Х | Х | b4 | b3 | b2 | b1 | b0 |

|-----------------------|---|---|----|----|----|----|----|

Description: PLL and INTR pin control register

| b1 | b0     | PLL output clock (ADC input)                                                           |

|----|--------|----------------------------------------------------------------------------------------|

| 0  | 0      | M_CLK (pin 9)                                                                          |

| 0  | 1      | 2XM_CLK (pin9)                                                                         |

| 1  | 0      | Test purpose                                                                           |

| 1  | 1      | Test purpose                                                                           |

| b5 | b4     | INTR pin control                                                                       |

| 0  | 0      | Normal function (from ERROR_REG)                                                       |

|    | 0      |                                                                                        |

| Ő  | 1      | BC_LOCK signal on INTR pin                                                             |

| -  | 1<br>0 | BC_LOCK signal on INTR pin<br>MFP_LOCK signal on INTR pin<br>PRCP_ALL_LOCK on INTR pin |

b3, b2: Test purpose

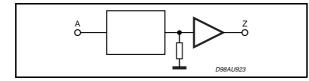

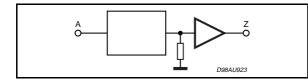

#### 2.2 A/D CONVERTER

This block performs the analog to digital conversion of the incoming IF input signal.

The ADC has a resolution of 6 bit and is based on the so called Half Flash architecture to reduce both area and power consumption.

The sampling rate depends on the M\_CLK (Master Clock) frequency and on the PLL presetting.

#### 3. QPSK DEMODULATOR

3.1 QUADRATURE DEMODULATOR

The final base-band demodulation is performed in this block.

The samples of the IF input signal are multiplied by the sine and cosine functions to get the two inphase (I) and quadrature (Q) components of the QPSK signal. The phase ambiguity inherent in QPSK is solved in the frame synchronisation part.

A programmable bit allows to multiply by -1 the quadrature component in order to accomodate QPSK modulation with another convention of rotation sense (this is equivalent to a permutation of I and Q components).

The sine and cosine functions are generated by an NCO using a phase accumulator and a lookup table.

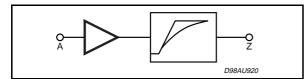

#### 3.2. INTERPOLATOR NYQUIST FILTER

The I and Q components are filtered by a digital Nyquist root filter with the following features:

Separate I and Q stream, Fck/Fsym samples per symbols;

Raised root cosine shape with roll-off factor of 40%;

Separate I and Q output stream, 1 sample per symbol.

This filter performs both the Nyquist filter function (matched with the one in the transmission side) and the interpolation function to compute the optimum output sample.

#### 3.3. TIMING RECOVERY

The timing loop is completely implemented digitally and comprises the timing detector working at symbol rate, a loop filter, the timing NCO and the Nyquist/interpolator filters.

The loop is controlled by two parameters, alpha\_tmg and beta\_tmg contained in the TIMFLTPAR register.

#### 3.3.1 Timing loop registers

Timing loop filter parameter register (TIMFLTPAR)

Internal address: 8D H Reset Value: 48H

#### ....

| MSB       |    |    |    |    |      |      | LSB |

|-----------|----|----|----|----|------|------|-----|

| b7        | b6 | b5 | b4 | b3 | b2   | b1   | b0  |

| alpha_tmg |    |    |    |    | beta | _tmg |     |

Timing frequency registers (TIMINTG) Internal address: 8E H Reset Value: 0AH

| MSB           |    |    |    |    |    |    | LSB |

|---------------|----|----|----|----|----|----|-----|

| b7            | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

| signed number |    |    |    |    |    |    |     |

The value of this register, when the system is locked, is an image of the frequency offset.

Timing NCO frequency setting (SYMFREQ) Internal address: 8C H 8B H 8A H Reset Value : 0CH 11H D3H

| MSB      |     |     |     |     |     |     | LSB |

|----------|-----|-----|-----|-----|-----|-----|-----|

| b23      | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

| SYMEREO3 |     |     |     |     |     |     |     |

SYMFREQ3

|          | MSB |     |     |     |     |     |    | LSB |

|----------|-----|-----|-----|-----|-----|-----|----|-----|

|          | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8  |

| SYMFREQ2 |     |     |     |     |     |     |    |     |

| MSB      |    |    |    |    |    |    | LSB |

|----------|----|----|----|----|----|----|-----|

| b7       | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

| SYMFREQ1 |    |    |    |    |    |    |     |

This register is divided into three bytes. The LSB byte is named SYMFREQ1, the MSB is named SYMFREQ3.

The 22 bits value to be written into this register is given by:

$$SYMFREQ = INT\left(\frac{F_{sym}}{F_{ck}} 2^{22}\right)$$

for example if

M\_CLK = 39,02687179MHz, Fck = M\_CLK/4

SYMFREQ = 790995 = (C11D3)HEX which is the Reset Value.

#### 3.3.2 Loop equations

This timing loop is a second order one. The natural frequency and the damping factor may be calculated by the following formulas:

$$f_{n} = \frac{\sqrt{K_{0} K_{D} \beta \cdot m}}{2\pi}$$

where  $\beta$  is programmed by the timing register beta\_tmg:

$b = 2^{beta\_tmg-14} \cdot Fsym (Fsym = 1.84MHz)$

where m is the reference value of the AGC2 loop (see AGC2\_REF register), KD is the timing detector gain and Ko is the constant of the timing NCO:

$$K_0 = \frac{2\pi}{2^{22}} F_{Ck}$$

The damping factor is:

$$\xi = \frac{\alpha}{2} \sqrt{\frac{K_{o} K_{D} \cdot m}{\beta}}$$

where  $\alpha$  is programmed by the timing register alpha\_tmg:

$$\alpha = 2^{alpha_tmg}$$

beta\_tmg can only take value from 0 to 15; if beta\_tmg is 0 the loop reduces to a first order one.

Alpha\_tmg can take any value from 0 to 7. If both alpha\_tmg and beta\_tmg are 0 then the timing loop is open.

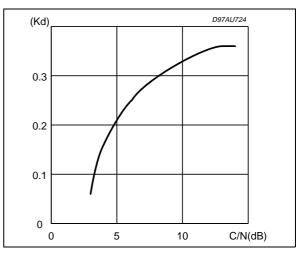

The timing phase detector gain  $K_D$  depends on the signal to noise ratio and is given in the following figure:

(see par. 3.8 for the C/N definition)

K<sub>D</sub> = 0.356 for a noise free input signal.

The natural frequency and the damping factor can be rewritten as:

#### **Phase Detector Gain**

$$f_n = 2.064 \ \sqrt{F_{CK}} \ \sqrt{m \cdot K_D \cdot 2^{beta\_tmg}}$$

$$\xi = 0.0577 \sqrt{F_{CK}} \sqrt{\frac{m \cdot K_D}{2^{beta\_tmg}}} \cdot 2^{alpha\_tmg}$$

Table 1 gives the natural frequency and the damping factor for the nominal amplitude m=22, KD = 0.356 and M\_CLK = 39.02687179MHz.

In high noise conditions the value of KD may be reduced up to 25% of its nominal (noise free) value; it is recommended to start with a damping factor, calculated without noise, greater than the usual value of 0.7.

#### 3.4. CARRIER RECOVERY

Also the carrier recovery is completely implemented digitally and comprises a phase and frequency detector, a loop filter, a NCO and a sine/cosine look-up table.

The carrier NCO is the local oscillator for the input quadrature demodulator.

3.4.1 Carrier loop registers

Carrier loop filter parameter register (CARFLTPAR)

Internal address: 8F H Reset Value: 57H

MSB

| MOB |       |       |    |    |      |      | LOD |

|-----|-------|-------|----|----|------|------|-----|

| b7  | b6    | b5    | b4 | b3 | b2   | b1   | b0  |

|     | alpha | a_car |    |    | beta | _car |     |

I SB

TABLE 1. Timing loop parameters (m= 22; K<sub>D</sub> = 0.356; M\_CLK = 39.02687179MHz)

| beta_tmg  | 0  | 1    | 2    | 3    | 4    | 5        | 6    | 7    | 8    | 9    | 10   |

|-----------|----|------|------|------|------|----------|------|------|------|------|------|

| fn(Hz)    | NA | 25   | 36   | 51   | 72   | 102      | 144  | 204  | 288  | 408  | 577  |

| alpha_tmg |    |      |      |      | Dan  | nping fa | ctor |      |      |      |      |

| 0         | NA | NA   | NA   | NA   | NA   | NA       | NA   | NA   | NA   | NA   | NA   |

| 1         | NA | 0.71 | 0.50 | 0.36 | 0.25 | 0.18     | 0.13 | 0.09 | 0.06 | 0.04 | 0.03 |

| 2         | NA | 1.42 | 1.01 | 0.71 | 0.50 | 0.36     | 0.25 | 0.18 | 0.13 | 0.09 | 0.06 |

| 3         | NA | 2.85 | 2.01 | 1.42 | 1.01 | 0.71     | 0.50 | 0.36 | 0.25 | 0.18 | 0.13 |

| 4         | NA | 5.70 | 4.03 | 2.85 | 2.01 | 1.42     | 1.01 | 0.71 | 0.50 | 0.36 | 0.25 |

| 5         | NA | 11.4 | 8.06 | 5.70 | 4.03 | 2.85     | 2.01 | 1.42 | 1.01 | 0.71 | 0.50 |

| 6         | NA | 22.8 | 16.1 | 11.4 | 8.06 | 5.70     | 4.03 | 2.85 | 2.01 | 1.42 | 1.01 |

| 7         | NA | 45.6 | 32.2 | 22.8 | 16.1 | 11.4     | 8.06 | 5.70 | 4.02 | 2.85 | 2.01 |

Carrier frequency registers (CARINTG) Internal address: 94 H Reset Value: 00H

| MSB           |    |    |    |    |    |    | LSB |  |  |  |

|---------------|----|----|----|----|----|----|-----|--|--|--|

| b7            | b6 | b5 | b4 | b3 | b2 | b1 | b0  |  |  |  |

| signed number |    |    |    |    |    |    |     |  |  |  |

This register is formed by the 8 integrator MSBs of the carrier loop filter.

The value of this register, when the system is locked, is an image of the frequency offset. It may be read or written at any time by the micro. When written the integrator LSBs are reset.

Carrier NCO frequency setting register (IFFREQ) Internal address: 93 H 92 H 91 H 90 H Reset Value : 00H C1H 1DH 37H

| MSB     |     |     |     |     |     |     | LSB |  |

|---------|-----|-----|-----|-----|-----|-----|-----|--|

| b31     | b30 | b29 | b28 | b27 | b26 | b25 | b24 |  |

| IFFREQ4 |     |     |     |     |     |     |     |  |

| MSB     |     |     |     |     |     |     | LSB |  |

|---------|-----|-----|-----|-----|-----|-----|-----|--|

| b23     | b22 | b21 | b20 | b19 | b18 | b17 | b16 |  |

| IFFREQ3 |     |     |     |     |     |     |     |  |

| MSB     |     |     |     |     |     |    | LSB |  |

|---------|-----|-----|-----|-----|-----|----|-----|--|

| b15     | b14 | b13 | b12 | b11 | b10 | b9 | b8  |  |

| IFFREQ2 |     |     |     |     |     |    |     |  |

| MSB     |    |    |    |    |    |    | LSB |  |

|---------|----|----|----|----|----|----|-----|--|

| b7      | b6 | b5 | b4 | b3 | b2 | b1 | b0  |  |

| IFFREQ1 |    |    |    |    |    |    |     |  |

This register is divided into four bytes.

The LSB byte is named IFFREQ1, the MSB is named IFFREQ4.

The 26 bits value to be written into this register is given by:

$$\mathsf{IFFREQ} = \mathsf{INT}\left(\frac{\mathsf{IF}}{\mathsf{F}_{\mathsf{ck}}} 2^{26}\right)$$

For example if  $M_CLK = 39.02687179MHz$ , Fck =  $M_CLK/4$

IFFREQ = 12655927 = (C11D37)HEX

which is the Reset Value.

Actual Carrier Frequency Register (CARFREQ) Internal address: 96 H, 97 H, 98 H

|            | MSB |     |     |     |     |     |     | LSB |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

|            | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

| CAR FREQ 3 |     |     |     |     |     |     |     |     |

|            | MSB |     |     |     |     |     |    | LSB |

|------------|-----|-----|-----|-----|-----|-----|----|-----|

|            | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8  |

| CAR FREQ 2 |     |     |     |     |     |     |    |     |

| MSB        |    |    |    |    |    |    | LSB |  |

|------------|----|----|----|----|----|----|-----|--|

| b7         | b6 | b5 | b4 | b3 | b2 | b1 | b0  |  |

| CAR FREQ 1 |    |    |    |    |    |    |     |  |

This register contains the actual carrier frequency value when the system is locked.

It is divided into 3 registers: CARFREQ3, down to 1 (CARFREQ3 is the MSB).

This register may be read at any time and it is useful to store the value of the recovered carrier. If the system unlocks (due, to a lack of signal etc.) the carrier NCO could be initialized with this value to speed-up the tracking process.

#### 3.4.2 Loop parameters

Like the timing loop the carrier loop is a second

TABLE 2. Carrier loop parameters (m = 22; K<sub>D</sub> = 1.26; M\_CLK = 39.02687179MHz)

| beta_car  | 0            | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| fn(KHz)   | NA           | 0.38         | 0.54         | 0.77         | 1.09         | 1.54         | 2.17         | 3.07         | 4.35         | 6.15         | 8.69         |

| alpha_car |              |              |              |              | Dan          | nping fa     | ctor         |              |              |              |              |

|           | ) NA<br>NA   | NA<br>0.67   | NA<br>0.47   | NA<br>0.34   | NA<br>0.24   | NA<br>0.17   | NA<br>0.12   | NA<br>0.08   | NA<br>0.06   | NA<br>0.04   | NA<br>0.03   |

|           | 2 NA         | 1.34         | 0.47         | 0.34         | 0.24<br>0.47 | 0.17         | 0.12         | 0.08         | 0.08         | 0.04         | 0.03         |

|           | 3 NA<br>I NA | 2.69<br>5.37 | 1.90<br>3.80 | 1.34<br>2.69 | 0.95<br>1.90 | 0.67<br>1.34 | 0.47<br>0.95 | 0.34<br>0.67 | 0.24<br>0.47 | 0.17<br>0.34 | 0.12<br>0.24 |

|           | 5 NA         | 10.7         | 7.60         | 5.37         | 3.80         | 2.69         | 1.90         | 1.34         | 0.95         | 0.67         | 0.47         |

order system controlled by two parameters, alpha-car and beta-car, contained in the CARFLTPAR register.

The natural frequency and the damping factor are given in the following formulas:

$$f_n = \sqrt{\frac{m K_0 K_D \beta}{2\pi}}$$

where  $\beta$  is programmed by the carrier register beta\_car:

$$\beta = 2^{beta\_car-4} \cdot Fsym (Fsym = 1.84MHz)$$

m is the reference value of the AGC2 loop (see AGC2\_REF register), KD is the phase detector gain and Ko is the constant of the carrier NCO:

$$K_0 = \frac{2\pi}{2^{26}} F_{CK}$$

The damping factor is

$$\xi = \frac{\alpha}{2} \sqrt{\frac{\mathsf{mK}_{\mathsf{O}} \mathsf{K}_{\mathsf{D}}}{\mathsf{B}}}$$

where  $\alpha$  is programmed by the carrier register alpha\_car:

$$\alpha = 2^{alpha_car+6}$$

beta\_car can only take value from 0 to 15; if beta\_car is 0 the loop becames a first order one.

alpha\_car can take any value from 0 to 9. If both alpha\_car and beta\_car are 0 then the loop is open.

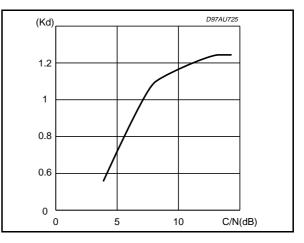

KD depends on the signal to noise ratio and is given in the figure in next column.

(see par. 3.8 for C/N definition)

KD = 1.26 for a noise free input signal.

The natural frequency and the damping factor can be rewritten as:

$$f_n = 16.515 \; \sqrt{F_{CK}} \; \sqrt{\; m \cdot K_D \cdot 2^{\; beta\_car}}$$

#### **Phase Detector Gain**

$$\xi = 0.0289 \sqrt{F_{CK}} 2^{alpha}_{car} \sqrt{\frac{m \cdot K_{D}}{2^{beta}_{car}}}$$

Table 2 gives the natural frequency and the damping factor for the nominal amplitude m = 22, KD = 1.26 and M\_CLK = 39.02687179MHz.

In presence of noise the value of KD may be reduced of up to 60%; it is recommended to start with a damping factor, without noise, greater than the usual value of 0.7.

### 3.4.3 Phase and frequency detector parameter

The carrier phase error is calculated by the following formula :  $\varepsilon = I \operatorname{sgn}(Q) - Q \operatorname{sgn}(I)$ .

This value is computed (at symbol rate) if the actual I and Q components are greater than a programmed threshold otherwise the previous value is mantained. In this way the detector outputs a DC value proportional to the frequency offset between the incoming signal and the local oscillator.

The threshold value may be programmed by the PFDTHR parameter inside the QPSK\_CON-TROL2 register:

# QPSK\_CONTROL2 Register Internal address: 81 H Reset Value: 90H

| MSB |     |     |    |    |     |    | LSB |

|-----|-----|-----|----|----|-----|----|-----|

| b7  | b6  | b5  | b4 | b3 | b2  | b1 | b0  |

|     | PFD | THR |    | CN | THR | S  | N   |

The threshold value depends on the signal level at the Nyquist filter output. A good value for this parameter is given by: PFDTHR = 0.4 AGC2REF where AGC2REF is the reference value for the AGC2 loop.

#### 3.4.4 Internal ramp parameter

In presence of a frequency offset greater than the pull-in range of the carrier loop or in presence of low signal to noise ratio the tracking performance of the loop itself may became rather slow. To help the loop in tracking this frequency offset an internal ramp can be activated by I<sup>2</sup>C bus.

This ramp can be switched on or off by setting the SWON parameter 1 or 0 respectively. When SWON=0 the output value of the ramp is null. The sweep rate can be calculated by the following formula:

$$\frac{dF}{dt} = \frac{2^{swstep}}{stepper+1} \frac{F_{ck}^2}{2^{26}}$$

where swstep can only take 0 and 1 values and stepper can be programmed in a range from 0 to 15.

| MSB     |                                         |    |    |    |    |    | LSB |  |

|---------|-----------------------------------------|----|----|----|----|----|-----|--|

| Х       | Х                                       | b5 | b4 | b3 | b2 | b1 | b0  |  |

| b5 : S  | 5 : SWON; 1 = 2 ramp on; 0 = 2 ramp off |    |    |    |    |    |     |  |

| b4 : S  | WSTEP                                   |    |    |    |    |    |     |  |

| b3 - b( | b3 - b0 : STEPPER                       |    |    |    |    |    |     |  |

Ramp control register (RAMPCTRL) Internal address: 95 H Reset Value: 01H

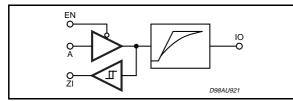

### 3.5. AGC1

3.5.1 AGC1 control

To avoid a degradation of the signal to noise ratio a constant IF level is necessary at the channel decoder input.

The AGC1 outputs a signal to control the Variable Gain Amplifier in the RF Front-End in order to mantain a fixed level at the ADC input.

The input signal power (computed after the A/D conversion) is compared to a programmable

The result is converted into a pulse width modulation signal to drive the AGC output pin; it may be filtered by a simple RC filter to control the gain command of a variable gain amplifier before the A to D conversion.

The 8 integrator MSB's (AGC1\_ INTG register) may be read or written at any time by the micro; when written, the LSB's are reset.

The integrator value is the level of the AGC output, after low pass filtering; it gives an image of the input signal power. The sign of the loop can be controlled by the AGC1CHS control bit in the QPSK\_CONTROL1 register in order to adapt the loop to a positive or negative slope of the variable gain amplifier.

#### 3.5.2 Registers

AGC1 reference level register (AGC1\_REF) Internal address: 83 H 82H

Reset Value : 01H 06H

| MSB |   |   |   |   |   |    | LSB |

|-----|---|---|---|---|---|----|-----|

| Х   | Х | Х | Х | Х | Х | b9 | b8  |

|     |   |   |   |   |   |    | -   |

AGC1\_REF2

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

AGC1\_REF1

This register is divided into two bytes. The LSB byte is named AGC1\_REF1, the MSB is named AGC1\_REF2.

The reset value of this register (262) maintains the peak signal input level equal to the half range of the ADC.

AGC1 integrator gain register (AGC1\_BETA) Internal address: 84 H Reset Value: 00H

| MSB  |     |   |   |   |    |    | LSB |

|------|-----|---|---|---|----|----|-----|

| Х    | Х   | Х | Х | Х | b2 | b1 | b0  |

| AGC1 | BET | 4 |   |   |    |    |     |

The AGC1 loop gain  $\beta_{AGC1}$  is given by:

$$b_{AGC1} = 2^{AGC1\_BETA}$$

The parameter AGC1\_BETA can only take values from 0 to 5. When AGC1\_BETA is set to "111" the loop gain is null. This condition is useful to open the AGC1 loop.

AGC1 integrator value register (AGC1\_INTG) Internal address: 85 H Reset Value: 00H

| MSB           |    |    |    |    |    |    | LSB |

|---------------|----|----|----|----|----|----|-----|

| b7            | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

| signed number |    |    |    |    |    |    |     |

To open the AGC1 loop this register must be reset and the AGC1\_BETA parameter must be "111".

### 3.6. AGC2

3.6.1 AGC2 control

The AGC2 loop is used at the output of the Nyquist / interpolator filter for power optimization in the signal bandwith.

The modulus of the complex signal at the output of the Nyquist filter is compared to a programmable threshold and then scaled by the AGC2\_BETA coefficient and integrated.

The integrated error drives two multiplier at the output of both the Nyquist filters in order to mantain constant the level signal at the demodulator output.

3.6.2 Register

AGC2 reference level register (AGC2\_REF)

Internal address: 86 H

Reset Value : 16 H

| MSE | 3 |    |    |    |    |    | LSB |

|-----|---|----|----|----|----|----|-----|

| Х   | Х | b5 | b4 | b3 | b2 | b1 | b0  |

AGC2\_REF

The value written in this register corresponds to the modulud of the output complex signal (I,Q).

AGC2 integrator gain register (AGC2\_BETA) Internal address: 87 H

Reset Value: 00H

#### MSB

| I | Х    | Х    | Х | Х | Х | b2 | b1 | b0 |

|---|------|------|---|---|---|----|----|----|

|   | AGC2 | BETA | 4 |   |   |    |    |    |

LSB

The AGC2 loop gain  $\beta_{AGC2}$  can be controlled by this register:

$\beta$ AGC2 = 2<sup>AGC2\_BETA</sup>

The parameter AGC2\_BETA can take values from 0 to 6. When AGC2\_BETA is set to "111" the loop gain is null and the AGC2 amplifier gain keeps the last value.

AGC2 integrator value register (AGC2\_INTG) Internal address: 88 H Reset Value: 00H

| MSB |    |    |        |        |    |    | LSB |

|-----|----|----|--------|--------|----|----|-----|

| b7  | b6 | b5 | b4     | b3     | b2 | b1 | b0  |

|     |    | ;  | signed | numbei | r  |    |     |

To open the AGC2 loop this register must be reset and the AGC2\_BETA parameter must be "111".

The AGC2 reference level value impacts the value of the following functions:

- Carrier to Noise indicator;

- The carrier loop;

- The timing loop

### 3.7. LOCK INDICATOR

This 1 bit carrier lock flag may be read at any time.

This flag is available at the chip output and can be also read by the micro in the FLAG register

A low logic level at the Lock Indicator means that a QPSK signal is found. The lock indicator flag controls, internally, the ramp block. The sweep function is disable whenever a lock condition is detected.

#### 3.8. CARRIER TO NOISE INDICATOR

A register is used to estimate the carrier to noise level C/N in a range from 4 to 17dB.

Remark: in the WorldStar system the correspondence between C/N, Eb/No (Energy per net-bit to noise ratio) and Eb/No|<sub>QPSK</sub> (Energy per channelbit to noise ratio) are the following:

$$C/N = Eb/No|_{QPSK} + 3dB = Eb/No - 0.6dB$$

The C/N indicator may be used to optimize the antenna pointing or to give an idea of the RF sigal quality. This is based on the measure of the scattering of the QPSK constellation: a 10 bit counter is incremented when the scattering is exceeding a certain value. After a programmable time interval the 8MSB of the counter are loaded in the corresponding I<sup>2</sup>C-bus register.

The register value strongly depends on the AGC2\_REF parameter.

#### 3.8.1 C/N Register (CNCNT)

This register contains a value proportional to the signal to noise ratio at the Nyquist filter output (Eb/No|QPSK).

57

| C/N(dB) | Eb/No QPSK | CNTHR = 8 |     |      | C  | CNTHR = 12 |     |    | CNTHR = 16 |     |  |

|---------|------------|-----------|-----|------|----|------------|-----|----|------------|-----|--|

| m = A   | AGC2_REF   | 16        | 22  | 26   | 16 | 22         | 26  | 16 | 22         | 26  |  |

| 3       | 0          | 161       | 121 | 101  | NA | 177        | 151 | NA | NA         | 193 |  |

| 4       | 1          | 155       | 112 | 93   | NA | 173        | 145 | NA | NA         | 192 |  |

| 5       | 2          | 148       | 102 | 84   | NA | 168        | 138 | NA | NA         | 190 |  |

| 6       | 3          | 140       | 91  | 73   | NA | 161        | 130 | NA | NA         | 186 |  |

| 7       | 4          | 132       | 79  | 61   | NA | 155        | 120 | NA | NA         | 184 |  |

| 8       | 5          | 122       | 68  | 50   | NA | 148        | 110 | NA | NA         | 180 |  |

| 9       | 6          | 113       | 55  | 38   | NA | 141        | 100 | NA | NA         | 177 |  |

| 10      | 7          | 105       | 46  | 28   | NA | 134        | 89  | NA | NA         | 174 |  |

| 11      | 8          | 92        | 33  | 20   | NA | 125        | 79  | NA | NA         | 170 |  |

| 12      | 9          | 84        | 26  | 13   | NA | 118        | 67  | NA | NA         | 165 |  |

| 13      | 10         | 71        | 20  | 8    | NA | 112        | 57  | NA | NA         | 161 |  |

| 14      | 11         | 65        | 14  | 6    | NA | 103        | 51  | NA | NA         | 158 |  |

| 15      | 12         | 58        | 9   | 3.2  | NA | 93         | 40  | NA | NA         | 154 |  |

| 16      | 13         | 49        | 5   | 1.6  | NA | 84         | 32  | NA | NA         | 149 |  |

| 17      | 14         | 42        | 3.4 | 0.9  | NA | 77         | 27  | NA | NA         | 144 |  |

| 18      | 15         | 34        | 2.4 | 0.5  | NA | 70         | 23  | NA | NA         | 141 |  |

| 19      | 16         | 32        | 1.5 | 0.25 | NA | 66         | 19  | NA | NA         | 137 |  |

| 20      | 17         | 30        | 0.9 | 0.07 | NA | 61         | 13  | NA | NA         | 131 |  |

TABLE 3. Correspondence between C/N and the CNCNT register contents.

The value are the average of 1000 readings of the CNCNT register.

The relation between C/N and the required value (CNCNT) is given in the table 3 for three AGC2 reference levels. A value of 255 means overflow.

#### 3.8.2 Control Register

There are two parameters to control the C/N esti-mator circuit CNTHR and SN located in the QPSK\_CONTROL 2 register. The CNTHR parameter (2 bits) sets the threshold

value under which the circuit is activated.

The SN parameter (2bits) sets the measure time internal.

Both there two parameters are given in the following tables:

| CNTHR | THRESHOLD |

|-------|-----------|

| 00    | 8         |

| 01    | 12        |

| 10    | 16        |

| 11    | NA        |

| SN | TIME INTERVAL IN SYMBOLS |

|----|--------------------------|

| 00 | 1024                     |

| 01 | 4096                     |

| 10 | 16384                    |

| 11 | 65536                    |

A suitable value of the threshold and time interval must be chosen to have a good level of confidence of the C/N estimate.

To increase the measure accuracy is advisable to average several values.

Before starting the measure the CNCNT register must be reset and can be read after the selected time internal.

A flag bit (CNFLAG) is set to 1 to indicate that a value is available in the CNCNT register.

#### **3.9 CONTROL REGISTERS**

QPSK\_CONTROL1 register Internal address: 80 H Reset Value: 10H

| MSB |      |    |    |    |   |   | LSB |

|-----|------|----|----|----|---|---|-----|

| Х   | b6   | b5 | b4 | b3 | Х | Х | Х   |

|     | 0040 |    |    |    |   |   |     |

b6: AGC1CHS

b5 : CAR CHS

b4 :TIMCHS

b3:QCHP

AGC1CHS changes the polarity of the AGC signal at output pin.

CARCHS and TIMCHS change the sign of the carrier tracking loop and symbol tracking loop respectively.

QCHS inverts the sign of the Q component.

**QPSK CONTROL2 register**

Internal address: 81 H

Reset Value: 90H

#### **MSB** LSB b7 b5 b6 b4 b3 b2 b1 b0 CNTHR PFDTHR SN

This register controls the Phase and frequency detector threshold (see par. 3.4.3) and the C/N indicator (see 3.8.2)

FLAG REGISTER

#### internal address: 99 H

| LOCK     | CNFLAG |  |  |  |  |  |  |  |  |  |

|----------|--------|--|--|--|--|--|--|--|--|--|

| reserved |        |  |  |  |  |  |  |  |  |  |

This is a read only register when the LOCK bit is 0 then the carrier is locked. When the CNFLAG bit is 1 then the C/N estimation is available.

#### 4. TDM DEMULTIPLEXING

4.1 TDM\_MULTIPLEX REGISTERS.

Reg name: TDM\_TRSH1 Internal address: 200 H Type: R/W Reset Value: 4BH

| MSB |    |    |    |    |    |    | LSB |  |

|-----|----|----|----|----|----|----|-----|--|

| Х   | b6 | b5 | b4 | b3 | b2 | b1 | b0  |  |

Description: Master frame preamble recognition - Synchronization threshold level.

Definition of the minimum number of TDM preamble bits to be recognized before enabling the frame synchronization.

Reg name: TDM\_TRSH2 Internal address: 201 H Type: R/W Reset Value: 43H

Table 4: TDM FSM active states

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| Х   | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

Description: Master frame preamble recognition - Warning flag threshold level.

Definition of the minimum number of TDM preamble bits to be recognized before setting an alarm condition.

Reg name: TDM\_ALARM

Internal address: 207 H Type: R/W Reset Value: 00H

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

Description: TDM finite state machine control register (see Table 4).

Reg name: PRC\_TRSH1 Internal address: 202 H Type: R/W Reset Value: 2AH

| MSB |   |    |    |    |    |    | LSB |

|-----|---|----|----|----|----|----|-----|

| Х   | Х | b5 | b4 | b3 | b2 | b1 | b0  |

Description: Prime rate channel preamble recognition - Synchronization threshold level.

Definition of the minimum number of PRC preamble bits to be recognized before enabling PRC synchronization.

47/

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | TDM FSM active states                                              |  |  |  |  |

|----|----|----|----|----|----|----|----|--------------------------------------------------------------------|--|--|--|--|

| Х  | Х  | Х  | Х  | Х  | 0  | 0  | 0  | mfp_detection, mfp_presync, mfp_sync,alarm 1 (1 cycle)             |  |  |  |  |

| Х  | Х  | Х  | Х  | Х  | 0  | 0  | 1  | mfp_detection, mfp_presync, mfp_sync,alarm 1 (2 cycle)             |  |  |  |  |

| Х  | Х  | Х  | Х  | Х  | 0  | 0  | 0  | mfp_detection, mfp_presync, mfp_sync,alarm 1 (3 cycle)             |  |  |  |  |

| Х  | Х  | Х  | Х  | Х  | 0  | 0  | 1  | mfp_detection, mfp_presync, mfp_sync,alarm 1 (4 cycle)             |  |  |  |  |

| 0  | 0  | 0  | 0  | 0  | 1  | Х  | Х  | mfp_detection, mfp_presync, mfp_sync, alarm 1, alarm 2 (1 cycles)  |  |  |  |  |

| 0  | 0  | 0  | 0  | 1  | 1  | Х  | Х  | mfp_detection, mfp_presync, mfp_sync, alarm 1, alarm 2 (2 cycles)  |  |  |  |  |

| -  | -  | -  | •  | -  | 1  | Х  | Х  | mfp_detection, mfp_presync, mfp_sync, alarm 1, alarm 2 (n cycles)  |  |  |  |  |

| 1  | 1  | 1  | 1  | 1  | 1  | Х  | Х  | mfp_detection, mfp_presync, mfp_sync, alarm 1, alarm 2 (32 cycles) |  |  |  |  |

Reg name: PRC\_TRSH2 Internal address: 203 H Type: R/W Reset Value: 23H

| MSB |   |    |    |    |    |    | LSB |

|-----|---|----|----|----|----|----|-----|

| Х   | Х | b5 | b4 | b3 | b2 | b1 | b0  |

Description: Prime rate channel preamble recognition - Warning flag threshold level.

It defines the minimum number of PRC preamble bits to be recognized before setting an alarm condition.

Reg name: PRC\_ALARM Internal address: 208 H Type: R/W

Reset Value: 00H

| MSB |    |    |    |   |   |    | LSB |  |

|-----|----|----|----|---|---|----|-----|--|

| b7  | b6 | b5 | b4 | Х | Х | b1 | b0  |  |

Description: PRC finite state machine control register (see table 5).

Reg name: PRC\_ACTIVE\_REG Internal address: 20F H Type: R

Table 5: PRC\_ALARM

671

| MSB |    |    |    |    |    |    | LSB |  |

|-----|----|----|----|----|----|----|-----|--|

| h7  | b6 | b5 | h4 | b3 | h2 | b1 | b0  |  |

Description: It gives the list of active PRC within one selected BC.

b0 to b7 indicates PRC0 to PRC7 respectively.

Reg name: PRC\_LOCK\_REG Internal address: 210 H Type: R

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

| _   |    |    |    |    |    |    |     |

Description: Lock status of each PRC

b0 to b7 indicates the lock status of PRC0 to PRC7 respectively.

Reg name: PRC\_DELAY\_REG

Internal address: 211 H

Type: R

| MSB |   |   |   |    |    |    | LSB |  |

|-----|---|---|---|----|----|----|-----|--|

| Х   | Х | Х | Х | b3 | b2 | b1 | b0  |  |

Description: PRC maximum number of delay symbols

It detects the maximum number of delay symbols among the PRC within the same BC.

| b7 | b6 | b5 | b4 | b1 | b0 | PRC FSM active states                                         |

|----|----|----|----|----|----|---------------------------------------------------------------|

| Х  | Х  | Х  | Х  | 0  | 0  | prcp_detection, prcp_presync, prcp_sync                       |

| Х  | Х  | Х  | Х  | 0  | 1  | prcp_detection, prcp_presync, prcp_sync, alarm 1              |

| 0  | 0  | 0  | 0  | 1  | 0  | sp_detection, sp_presync, sp_sync, alarm2                     |

| 0  | 0  | 0  | 1  | 1  | 0  | sp_detection, sp_presync, sp_sync, alarm2 (1 cycle)           |

| 0  | 0  | 1  | 0  | 1  | 0  | sp_detection, sp_presync, sp_sync, alarm2 (2 cycles)          |

| 0  | 0  | 1  | 1  | 1  | 0  | sp_detection, sp_presync, sp_sync, alarm2 (3 cycles)          |

| -  | -  | -  | -  | 1  | 0  | sp_detection, sp_presync, sp_sync, alarm2 (n cycles)          |

| 1  | 1  | 1  | 1  | 1  | 0  | sp_detection, sp_presync, sp_sync, alarm2 (16 cycles)         |

| 0  | 0  | 0  | 0  | 1  | 1  | sp_detection, sp_presync, sp_sync, alarm1, alarm2             |

| 0  | 0  | 0  | 1  | 1  | 1  | sp_detection, sp_presync, sp_sync, alarm1, alarm2 (1 cycle)   |

| 0  | 0  | 1  | 0  | 1  | 1  | sp_detection, sp_presync, sp_sync, alarm1, alarm2 (2 cycles)  |

| 0  | 0  | 1  | 1  | 1  | 1  | sp_detection, sp_presync, sp_sync, alarm1, alarm2 (3 cycles)  |

| -  | -  | -  | -  | 1  | 1  | sp_detection, sp_presync, sp_sync, alarm1, alarm2 (n cycles)  |

| 1  | 1  | 1  | 1  | 1  | 1  | sp_detection, sp_presync, sp_sync, alarm1, alarm2 (16 cycles) |

Reg name: PRC\_MAXDELAY Internal address: 206 H Type: R/W Reset Value:06H

| MSB |   |   |   |   |    |    | LSB |

|-----|---|---|---|---|----|----|-----|

| Х   | Х | Х | Х | Х | b2 | b1 | b0  |

Description: Maximum accepted number of delay symbols among the prime rate channels belonging to the same broadcast channel.

Reg name: SP\_TRSH2

Internal address: 205 H

Type: R/W

Reset Value: 13H

| MSB |   |   |    |    |    |    | LSB |

|-----|---|---|----|----|----|----|-----|

| Х   | Х | Х | b4 | b3 | b2 | b1 | b0  |

Description: Service control header preamble recognition - Warning flag threshold level.

Definition of the minimum number of SCH preamble bits to be recognized before enabling SCH synchronization

Reg name: BC\_SEL1, BC\_SEL2 Internal address: 209 H , 20AH Type: R/W Reset Value: 01H, 00H

BC\_SEL1 (LSB)

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

### BC\_SEL2 (MSB)

| MSB |     |     |     |     |     |    | LSB |

|-----|-----|-----|-----|-----|-----|----|-----|

| b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8  |

Description: Broadcast channel selection

b10 ....b0: BC number selection

b11: Test purpose

b15 ... b12 : Test purpose (must be set at 0 in functional mode)

#### 4.2 INTERRUPT/STATUS REGISTERS

Reg name: CONTROL Internal address: 20BH Type: R/W Reset Value: 00H

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

Description: Control register

b0 : Software reset on

b1 : Software reset enable

b2 : Set TDM out of frame

b3 : ERROR\_REG reset on read enable

b4 : Set PRC out of frame

b5 : Set BC out of frame

b6, b7: Test purpose

Reg name: INT\_MASK Internal address: 20CH Type: R/W

Reset Value: 00H

| MSB |    |    |    |    |    |    | LSB |  |