# XMRADIO<sup>®</sup> SDARS CHANNEL DECODER

### FRONT END INTERFACE

- TWO INTERNAL 10 BIT A/D CONVERTERS

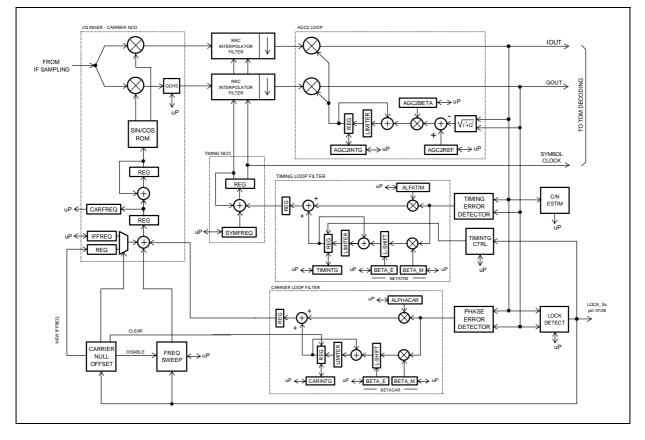

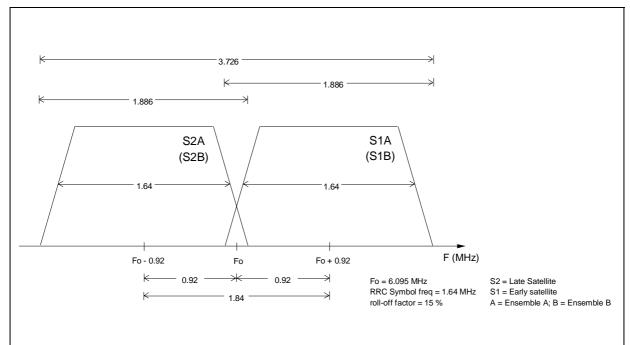

- TWO QPSK DEMODULATORS FOR SATELLITE BRANCH

- ONE MULTICARRIER DEMODULATOR FOR TERRESTRIAL BRANCH

- SATELLITE SYMBOL FREQUENCY: 1.64 MBAUD

- TERRESTRIAL SYMBOL FREQUENCY: 2.99 MBAUD

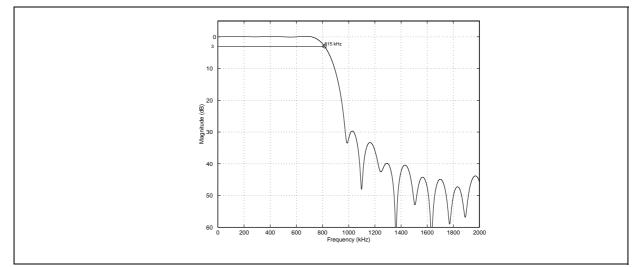

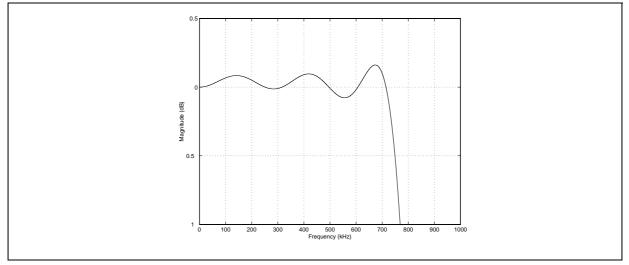

- DIGITAL ROOT RAISED COSINE NYQUIST FILTER: 15% ROLL-OFF

- FFT LENGTH: 768 SUB-CARRIERS

- FULL DIGITAL CARRIER AND FREQUENCY RECOVERY AND TRACKING LOOPS

- FREQUENCY INVERSION COMPENSATION FOR HIGH-SIDE/LOW-SIDE MIXER INJECTION

- LOCK DETECTORS, C/N INDICATOR, ON CHIP BER ESTIMATORS

- TWO DIGITAL AGCs: INTERNAL SIGNAL POWER ESTIMATION AND FILTERING

- 1 BIT PDM AGCs CONTROL SIGNAL OUTPUTS

#### TDM DECODING AND MANAGEMENT

- SATELLITE AND TERRESTRIAL FRAME SYNCHRONIZATION

- SATELLITE PHASE AMBIGUITY RESOLUTION

- TDM DEMULTIPLEXING

- PRIME RATE CHANNEL (PRC)

- DEMULTIPLEXING

- EXTERNAL MEMORY CONTROLLING

#### FORWARD ERROR CORRECTION

- VITERBI DECODER: K=7, R=1/3

- SATELLITE DEPUNCTURING: RATE 3/4

- TERRESTRIAL DEPUNCTURING: RATE 3/5

- CONVOLUTIONAL TIME DEINTERLEAVER OVER 4.7 SEC

- BLOCK DEINTERLEAVER OVER 2 RS BLOCKS

- REED-SOLOMON DECODER: (255,223). UP TO 16 BYTES CORRECTION CAPABILITY.

THIS DEVICE CAN BE SOLD ONLY TO CUSTOMERS THAT HAVE SIGNED A LICENSE AGREEMENT WITH XM SATELLITE RADIO.

- ENERGY DISPERSAL DESCRAMBLER

- SAT-SAT AND TERR-SAT DIVERSITY COMBINING

#### BACK END INTERFACE

- TWO PAYLOAD CHANNEL BITSTREAM INTERFACES

- PAYLOAD CHANNEL SELECTION LOGIC

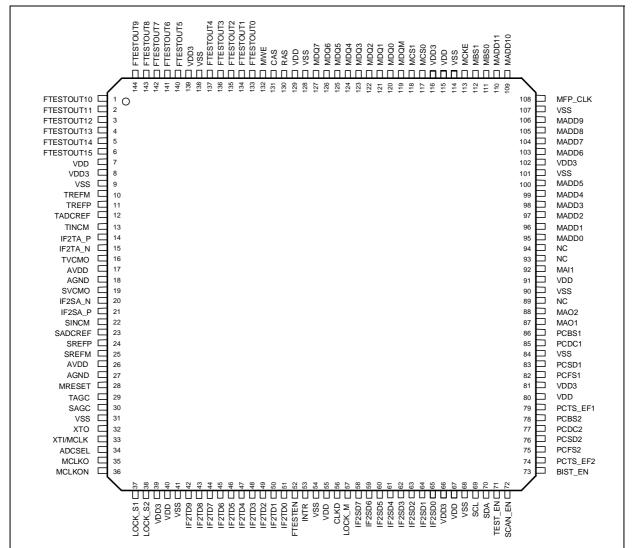

- DESIGNED TO WORK WITH THE STA450A SERVICE AND SOURCE DECODER

#### LOW POWER TECHNOLOGY

- 1.8V, 0.18μm TECHNOLOGY

- 3.3V CAPABLE I/Os

#### CONTROL

- IIC-BUS SLAVE CONTROL INTERFACE

- DEVICE ADDRESS: 1101010

#### DESCRIPTION

The SDARS is a satellite transmission system based on two geostationary satellites on the East and West coasts of the Continental United States (CONUS). In the urban areas, where the line of sight reception of the satellites is difficult or not possible, the service is covered by terrestrial repeaters adopting a MultiCarrier Modulation scheme.

Designed for digital radio receivers compatible with the XMRadio SDARS System, the STA400A Channel Decoder integrates all the functions to demodu-

late and decode the incoming satellite and terrestrial signals after the RF Front-End down-convertions: Analogto-Digital conversions, satellite and terrestrial demodulations, AGCs, frame synchronization and demultiplexing, Viterbi decoding, time and spatial diversity combining, Reed-Solomon decoding and deinterleaving, Prime Rate Channel (PRC) demultiplexing, Payload Channel (PC) selection.

At the end of the demodulation and decoding processes a configurable serial data stream is made available to STA450A, the Service/Source Decoder, via the PC BitStream interface.

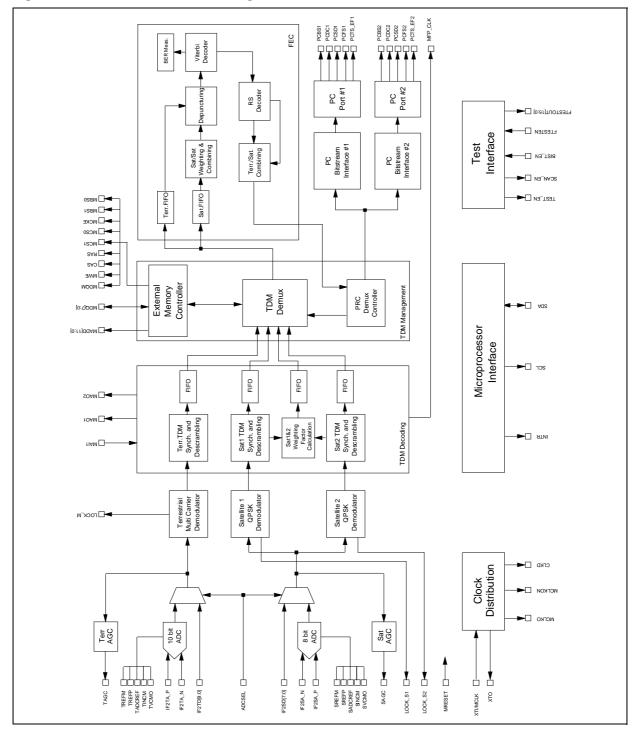

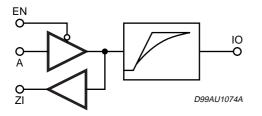

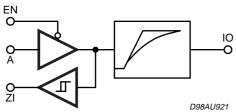

Figure 1. Channel Decoder Block Diagram

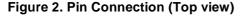

# **PIN DESCRIPTION**

| Pin N°                                                  | Pin Name        | Туре | Function                            | PAD Description   |

|---------------------------------------------------------|-----------------|------|-------------------------------------|-------------------|

| [1:6]                                                   | FTESTOUT[10:15] | 0    | Configurable Functional Test Output | 2mA Output Driver |

| 7,40,55,<br>67,80,91,<br>115,129,                       | VDD             | PWR  | 1.8V Positive Supply Voltage        |                   |

| 8,39,66,<br>81,102,<br>116,139                          | VDD3            | PWR  | 3.3V Positive Supply Voltage        |                   |

| 9,31,41,<br>54,68,84,<br>90,101,107<br>,114,128,<br>138 | VSS             | GND  | Digital Ground                      |                   |

# PIN DESCRIPTION (Continued)

| Pin N° | Pin Name | Туре               | Function                                                                                         | PAD Description        |

|--------|----------|--------------------|--------------------------------------------------------------------------------------------------|------------------------|

| 10     | TREFM    | Analog<br>Vref     | Terr. ADC Reference Negative Voltage.<br>Bottom of the reference ladder (driven or<br>filtered). | Analog Pad Buffer (1)  |

| 11     | TREFP    | Analog<br>Vref     | Terr. ADC Reference Positive Voltage. Top of the reference ladder (driven or filtered).          | Analog Pad Buffer (1)  |

| 12     | TADCREF  | Analog<br>Terminal | Terr. ADC Reference Adjust (external resistor to determine Ipol)                                 | Analog Pad Buffer (1)  |

| 13     | TINCM    | Analog<br>Output   | Terr. ADC Internal Common-Mode output for bypassing                                              | Analog Pad Buffer (1)  |

| 14     | IF2TA_P  | Analog<br>Input    | Terr. 2nd IF Differential Input - Positive                                                       | Analog Pad Buffer (1)  |

| 15     | IF2TA_N  | Analog<br>Input    | Terr. 2nd IF Differential Input - Negative                                                       | Analog Pad Buffer (1)  |

| 16     | TVCMO    | Analog<br>Terminal | Terr. ADC Internal Common Mode (filtered)                                                        | Analog Pad Buffer (1)  |

| 17,26  | AVDD     | PWR                | Analog Positive Supply Voltage (1.8V)                                                            |                        |

| 18,27  | AGND     | GND                | Analog Ground                                                                                    |                        |

| 19     | SVCMO    | Analog<br>Terminal | Sat. ADC Internal Common Mode<br>(filtered)                                                      | Analog Pad Buffer (1)  |

| 20     | IF2SA_N  | Analog<br>Input    | Sat. 2nd IF Differential Input - Negative                                                        | Analog Pad Buffer (1)  |

| 21     | IF2SA_P  | Analog<br>Input    | Sat. 2nd IF Differential Input - Positive                                                        | Analog Pad Buffer (1)  |

| 22     | SINCM    | Analog<br>Output   | Sat. ADC Internal Common-Mode output for bypassing                                               | Analog Pad Buffer (1)  |

| 23     | SADCREF  | Analog<br>Terminal | Sat. ADC Reference Adjust (external resistor to determine Ipol)                                  | Analog Pad Buffer (1)  |

| 24     | SREFP    | Analog<br>Vref     | Sat. ADC Reference Positive Voltage. Top of the reference ladder (driven or filtered).           | Analog Pad Buffer (1)  |

| 25     | SREFM    | Analog<br>Vref     | Sat. ADC Reference Negative Voltage.<br>Bottom of the reference ladder (driven or<br>filtered).  | Analog Pad Buffer (1)  |

| 28     | MRESET   | I                  | Master Reset                                                                                     | Schmitt Trigger Buffer |

| 29     | TAGC     | 0                  | Terr. AGC Control Signal                                                                         | 2mA Output Driver      |

| 30     | SAGC     | 0                  | Sat. AGC Control Signal                                                                          | 2mA Output Driver      |

| 32     | ХТО      | 0                  | XTAL Output                                                                                      | Oscillator Buffer      |

| 33     | XTI/MCLK | I                  | XTAL Input or Master Clock Input                                                                 | Analog Pad Buffer (2)  |

| 34     | ADCSEL   | I                  | Selection between Internal or External ADC<br>0=Internal                                         | Buffer with Pull-Down  |

# PIN DESCRIPTION (Continued)

| InternationalInternational TestDrive52FTESTENIFunctional TestEnable (1=enable)Buffer with Pull-Down53INTROInterrupt2mA Output Driver56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver58IF2SD[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. Higl<br>Drive69SCLIIIC-bus Serial ClockSchmitt Trigger Buffe70SDAI/OIIC-bus Serial DataSchmitt Trigger Buffe<br>Buffer with Pull-Down71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel Serial Data 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver78PCS1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver78PCS1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver78PCS1O </th <th>Pin N°</th> <th>Pin Name</th> <th>Туре</th> <th>Function</th> <th>PAD Description</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin N°   | Pin Name   | Туре | Function                                 | PAD Description                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|------|------------------------------------------|---------------------------------------------|

| 37LOCK_S1OSatellite Dem1 Lock Indicator2mA Output Driver38LOCK_S2OSatellite Dem2 Lock Indicator2mA Output Driver[42:51]IF2TD[9:0]ITerr. 2nd IF Digital InputInput Pad Buffer. High52FTESTENIFunctional Test Enable (1=enable)Buffer with Pull-Down53INTROInterrupt2mA Output Driver56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver57IS25[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. High<br>Drive69SCLIIIIC-bus Serial ClockSchmitt Trigger Buffer70SDAI/OIC-bus Serial DataSchmitt Trigger Buffer71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bitt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel PRC Frame Sync 22mA Output Driver77PCDC2OPayload Channel PRC Frame Sync 12mA Output Driver78PCSS1OPayload Channel PRC Frame Sync 12mA Output Driver78PCSD1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35       | MCLKO      | 0    | Master Clock Output                      | 4mA Output Driver                           |

| 38LOCK_S2OSatellite Dem2 Lock Indicator2mA Output Driver[42:51]IF2TD[9:0]ITerr. 2nd IF Digital InputInput Pad Buffer. High<br>Drive.52FTESTENIFunctional Test Enable (1=enable)Buffer with Pull-Down53INTROInterrupt2mA Output Driver56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver58IF2SD[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. High<br>Drive69SCLIIIC-bus Serial ClockSchmitt Trigger Buffer70SDAI/OIC-bus Serial DataSchmitt Trigger Buffer71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel PRC Frame Sync 22mA Output Driver77PCDC2OPayload Channel PRC Frame Sync 12mA Output Driver78PCS1OPayload Channel PRC Frame Sync 12mA Output Driver78PCS2OPayload Channel PRC Frame Sync 12mA Output Driver78PCS1OPayload Channel PRC Frame Sync 12mA Output Driver78PCS1O <td>36</td> <td>MCLKON</td> <td>0</td> <td>Inverted Master Clock Output</td> <td>4mA Output Driver</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36       | MCLKON     | 0    | Inverted Master Clock Output             | 4mA Output Driver                           |

| [42:51]IF2TD[9:0]ITerr. 2nd IF Digital InputInput Pad Buffer. High<br>Drive.52FTESTENIFunctional Test Enable (1=enable)Buffer with Pull-Down53INTROInterrupt2mA Output Driver56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver69SCLIIIC-bus Serial ClockSchmitt Trigger Buffe70SDAI/OIIC-bus Serial DataSchmitt Trigger Buffe71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel Serial Data 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Serial Data 22mA Output Driver78PCS1OPayload Channel Serial Data 22mA Output Driver78PCS2OPayload Channel Serial Data 12mA Output Driver78PCS1OPayload Channel Serial Data 12mA Output Driver79PCTS_EF1OPayload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37       | LOCK_S1    | 0    | Satellite Dem1 Lock Indicator            | 2mA Output Driver                           |

| InternationalInternational TestDrive52FTESTENIFunctional TestEnable (1=enable)Buffer with Pull-Down53INTROInterrupt2mA Output Driver56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver58IF2SD[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. Higl<br>Drive69SCLIIIC-bus Serial ClockSchmitt Trigger Buffe70SDAI/OIIC-bus Serial DataSchmitt Trigger Buffe<br>Buffer with Pull-Down71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel Serial Data 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver78PCS1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver78PCS1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver78PCS1O </td <td>38</td> <td>LOCK_S2</td> <td>0</td> <td>Satellite Dem2 Lock Indicator</td> <td>2mA Output Driver</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38       | LOCK_S2    | 0    | Satellite Dem2 Lock Indicator            | 2mA Output Driver                           |

| 53INTROInterrupt2mA Output Driver56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver[58:65]IF2SD[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. High<br>Drive69SCLIIIC-bus Serial ClockSchmitt Trigger Buffer70SDAI/OIIC-bus Serial DataSchmitt Trigger BiDir<br>Buffer. 4mA Driver71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Serial Data 12mA Output Driver78PCBS2OPayload Channel Scc Sync1/ ErrorFlag 12mA Output Driver78PCSD1OPayload Channel PRC Frame Sync12mA Output Driver78PCS1OPayload Channel PRC Frame Sync12mA Output Driver78PCS1OPayload Channel Serial Data 12mA Output Driver79PCTS_E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [42:51]  | IF2TD[9:0] | I    | Terr. 2nd IF Digital Input               | Input Pad Buffer. High<br>Drive.            |

| 56CLKDODivided Master Clock2mA Output Driver57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver[58:65]IF2SD[7:0]1Sat. 2nd IF Digital InputInput Pad Buffer. Higl<br>Drive69SCL1IIC-bus Serial ClockSchmitt Trigger Biblir<br>Buffer. 4mA Driver70SDAI/OIIC-bus Serial DataSchmitt Trigger Biblir<br>Buffer. 4mA Driver71TEST_EN1ATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_EN1Scan Enable (1=Enabled)Buffer with Pull-Down73BIST_EN1RAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel Serial Data 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Serial Data 22mA Output Driver78PCBS2OPayload Channel Data Clock 22mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ErrorFlag 12mA Output Driver83PCD1OPayload Channel PRC Frame Sync12mA Output Driver86PCBS1OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52       | FTESTEN    | I    | Functional Test Enable (1=enable)        | Buffer with Pull-Down                       |

| 57LOCK_MOTerrestrial Demodulator Lock Indicator2mA Output Driver[58:65]IF2SD[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. Higl<br>Drive69SCLIIC-bus Serial ClockSchmitt Trigger Buffe70SDAI/OIIC-bus Serial DataSchmitt Trigger BiDir<br>Buffer. 4mA Driver71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 22mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel PRC Frame Sync 12mA Output Driver78PCBS1OPayload Channel PRC Frame Sync12mA Output Driver84PCS01OPayload Channel PRC Frame Sync12mA Output Driver85PCDC1OPayload Channel PRC Frame Sync12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver88MAO2OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver89.93.94NCOMobile Adapter Output #12mA Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53       | INTR       | 0    | Interrupt                                | 2mA Output Driver                           |

| [58:65]IF2SD[7:0]ISat. 2nd IF Digital InputInput Pad Buffer. High<br>Drive69SCLIIIC-bus Serial ClockSchmitt Trigger Buffe70SDAI/OIIC-bus Serial DataSchmitt Trigger BiDir<br>Buffer. 4mA Driver71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel PRC Frame Sync 22mA Output Driver75PCFS2OPayload Channel Serial Data 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Serial Data 22mA Output Driver78PCBS2OPayload Channel Serial Data 12mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver83PCD1OPayload Channel Serial Data 12mA Output Driver84PCS51OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Serial Data 12mA Output Driver88MAO2OPayload Channel Serial Data 12mA Output Driver89,93,94NCInNot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56       | CLKD       | 0    | Divided Master Clock                     | 2mA Output Driver                           |

| AndAndAndDrive69SCLIIIC-bus Serial ClockSchmitt Trigger Buffe70SDAI/OIIC-bus Serial DataSchmitt Trigger BiDir<br>Buffer. 4mA Driver71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel PRC Frame Sync 22mA Output Driver75PCFS2OPayload Channel Serial Data 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver79PCTS_EF1OPayload Channel RC Frame Sync12mA Output Driver83PCD1OPayload Channel Serial Data 12mA Output Driver85PCD1OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Serial Data 12mA Output Driver88MAO2OMobile Adapter Output #12mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57       | LOCK_M     | 0    | Terrestrial Demodulator Lock Indicator   | 2mA Output Driver                           |

| TotalDataDataData70SDAI/OIIC-bus Serial DataSchmitt Trigger BiDir<br>Buffer. 4mA Driver71TEST_ENIATPG Test Enable (1=Enabled)Buffer with Pull-Down72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 2<br>(432 msec)2mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Data Clock 22mA Output Driver77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Serial Data 12mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2ONot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [58:65]  | IF2SD[7:0] | I    | Sat. 2nd IF Digital Input                | Input Pad Buffer. High<br>Drive             |

| Image: Second and the second and th | 69       | SCL        | I    | IIC-bus Serial Clock                     | Schmitt Trigger Buffer                      |

| 72SCAN_ENIScan Enable (1=Enabled)Buffer with Pull-Down73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 2<br>(432 msec)2mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel PRC Frame Sync12mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver85PCDC1OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87NAO1OMobile Adapter Output #12mA Output Driver89,93,94NCNCNot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70       | SDA        | I/O  | IIC-bus Serial Data                      | Schmitt Trigger BiDir<br>Buffer. 4mA Driver |

| 73BIST_ENIRAM Bilt In Self Test Enable (1=Enabled)Buffer with Pull-Down74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 2<br>(432 msec)2mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver78PCBS2OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Data Clock 12mA Output Driver87MAO1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver88MAO2OMobile Adapter Output #12mA Output Driver89,93,94NCNot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71       | TEST_EN    | I    | ATPG Test Enable (1=Enabled)             | Buffer with Pull-Down                       |

| 74PCTS_EF2OPayload Channel TSCC Sync2/ErrorFlag 2<br>(432 msec)2mA Output Driver75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Serial Data 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag12mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Data Clock 12mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2ONot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72       | SCAN_EN    | I    | Scan Enable (1=Enabled)                  | Buffer with Pull-Down                       |

| (432 msec)(432 msec)75PCFS2OPayload Channel PRC Frame Sync 22mA Output Driver76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag1<br>(432 msec)2mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver86PCBS1OPayload Channel Data Clock 12mA Output Driver87MAO1OPayload Channel Data Clock 12mA Output Driver88MAO2OMobile Adapter Output #22mA Output Driver89,93,94NCImage: Not Connected.Image: Not Connected.Image: Not Connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73       | BIST_EN    | I    | RAM Bilt In Self Test Enable (1=Enabled) | Buffer with Pull-Down                       |

| 76PCSD2OPayload Channel Serial Data 22mA Output Driver77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag1<br>(432 msec)2mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2OMobile Adapter Output #22mA Output Driver89,93,94NCImage: Not Connected.Image: Not Connected.Image: Not Connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74       | PCTS_EF2   | 0    |                                          | 2mA Output Driver                           |

| 77PCDC2OPayload Channel Data Clock 22mA Output Driver78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag1<br>(432 msec)2mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver89,93,94NCImage: Mathematic Mat                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75       | PCFS2      | 0    | Payload Channel PRC Frame Sync 2         | 2mA Output Driver                           |

| 78PCBS2OPayload Channel Byte Sync2 (RS Symbol)2mA Output Driver79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag1<br>(432 msec)2mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2ONot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76       | PCSD2      | 0    | Payload Channel Serial Data 2            | 2mA Output Driver                           |

| 79PCTS_EF1OPayload Channel TSCC Sync1/ ErrorFlag1<br>(432 msec)2mA Output Driver82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2ONot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77       | PCDC2      | 0    | Payload Channel Data Clock 2             | 2mA Output Driver                           |

| 82PCFS1OPayload Channel PRC Frame Sync12mA Output Driver83PCSD1OPayload Channel Serial Data 12mA Output Driver85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2ONot Connected.2mA Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78       | PCBS2      | 0    | Payload Channel Byte Sync2 (RS Symbol)   | 2mA Output Driver                           |

| 83PCSD1OPayload Channel Serial Data 12mA Output Driver85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2OMobile Adapter Output #22mA Output Driver89,93,94NCImage: Not Connected.Image: Not Connected.Image: Not Connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79       | PCTS_EF1   | 0    |                                          | 2mA Output Driver                           |

| 85PCDC1OPayload Channel Data Clock 12mA Output Driver86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2OMobile Adapter Output #22mA Output Driver89,93,94NCImage: Not Connected.Image: Not Connected.Image: Not Connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82       | PCFS1      | 0    | Payload Channel PRC Frame Sync1          | 2mA Output Driver                           |

| 86PCBS1OPayload Channel Byte Sync1 (RS Symbol)2mA Output Driver87MAO1OMobile Adapter Output #12mA Output Driver88MAO2OMobile Adapter Output #22mA Output Driver89,93,94NCImage: Not Connected.Image: Not Connected.Image: Not Connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83       | PCSD1      | 0    | Payload Channel Serial Data 1            | 2mA Output Driver                           |

| 87MAO1OMobile Adapter Output #12mA Output Driver88MAO2OMobile Adapter Output #22mA Output Driver89,93,94NCNot Connected.Image: Connected connecte                                                                                                                                        | 85       | PCDC1      | 0    | Payload Channel Data Clock 1             | 2mA Output Driver                           |

| 88     MAO2     O     Mobile Adapter Output #2     2mA Output Driver       89,93,94     NC     Not Connected.     Image: Content of the second se                                                                                       | 86       | PCBS1      | 0    | Payload Channel Byte Sync1 (RS Symbol)   | 2mA Output Driver                           |

| 89,93,94         NC         Not Connected.         Image: Connected connecte                                   | 87       | MAO1       | 0    | Mobile Adapter Output #1                 | 2mA Output Driver                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88       | MAO2       | 0    | Mobile Adapter Output #2                 | 2mA Output Driver                           |

| 92 MAI1 I Mobile Adapter Input Buffer with Pull-Dowr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 89,93,94 | NC         |      | Not Connected.                           |                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92       | MAI1       | I    | Mobile Adapter Input                     | Buffer with Pull-Down                       |

# PIN DESCRIPTION (Continued)

| Pin N°    | Pin Name      | Туре | Function                              | PAD Description             |

|-----------|---------------|------|---------------------------------------|-----------------------------|

| [95:100]  | MADD[0:5]     | 0    | External Memory Address               | 2mA Output Driver           |

| [103:106] | MADD[6:9]     | 0    | External Memory Address               | 2mA Output Driver           |

| 108       | MFP_CLK       | 0    | TDM Master Frame Clock                | 2mA Output Driver           |

| [109:110] | MADD[10:11]   | 0    | External Memory Address               | 2mA Output Driver           |

| [111:112] | MBS[0:1]      | 0    | External Memory Block Selection       | 2mA Output Driver           |

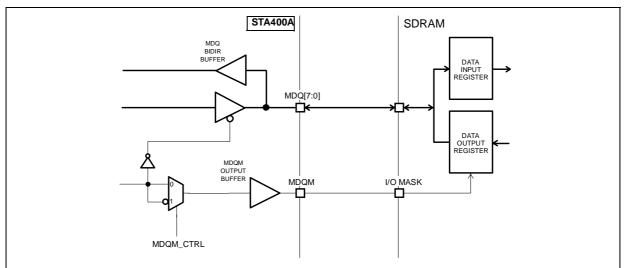

| 113       | MCKE          | 0    | External Memory Clock Enable          | 2mA Output Driver           |

| [117:118] | MCS[0:1]      | 0    | External Memory Chip Select           | 2mA Output Driver           |

| 119       | MDQM          | 0    | External Memory Data Mask             | 2mA Output Driver           |

| [120:127] | MDQ[0:7]      | I/O  | External Memory Data Input Output     | BiDir Buffer. 2mA<br>Driver |

| 130       | RAS           | 0    | External Memory Row Address Strobe    | 2mA Output Driver           |

| 131       | CAS           | 0    | External Memory Column Address Strobe | 2mA Output Driver           |

| 132       | MWE           | 0    | External Memory Write Enable          | 2mA Output Driver           |

| [133:137] | FTESTOUT[0:4] | 0    | Configurable Functional Test Output   | 2mA Output Driver           |

| [140:144] | FTESTOUT[5:9] | 0    | Configurable Functional Test Output   | 2mA Output Driver           |

Direct connection to core

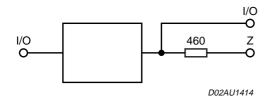

Connected to the internal oscillator buffer via 460 Ohm series resistor

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                      | Value                | Unit |

|-------------------|--------------------------------|----------------------|------|

| $V_{DD,} AV_{DD}$ | 1.8V Power supply Voltage      | -0.5 to 2.5          | V    |

| V <sub>DD3</sub>  | 3.3V Power Supply Voltage      | -0.5 to 4            | V    |

| Vi                | Voltage on input pin           | -0.5 to (Vdd3 + 0.5) | V    |

| Vo                | Voltage on output pin          | -0.5 to (Vdd3 + 0.5) | V    |

| V <sub>ia</sub>   | Voltage on analog input pin    | -0.8 to (AVdd + 0.8) | V    |

| V <sub>oa</sub>   | Voltage on analog output pin   | -0.8 to (AVdd + 0.8) | V    |

| T <sub>stg</sub>  | Storage Temperature            | -55 to +150          | °C   |

| Toper             | Operative Ambient Temperature  | -40 to +85           | °C   |

| Тj                | Operative Junction Temperature | -40 to +125          | °C   |

# THERMAL DATA

| Symbol             | Parameter                                             | Value | Unit |

|--------------------|-------------------------------------------------------|-------|------|

| R <sub>j-amb</sub> | Thermal Resistence junction to ambient <sup>(1)</sup> | 40    | ⁰C/W |

Notes: 1. according to JEDEC specification on a 4 layers board

# **DC ELECTRICAL CHARACTERISTCS:** (T<sub>amb</sub> = -40 to +85°C, V<sub>DD</sub> = AV<sub>DD</sub> = 1.65 to 1.95V, V<sub>DD3</sub> = 3.0 to 3.6V unless otherwise specified).

| Symbol                | Parameter                                      | Conditions                                                                                                                                                                                        | Min  | Тур | Max  | Unit |

|-----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>DD</sub>       | 1.8V Supply Voltage                            |                                                                                                                                                                                                   | 1.65 | 1.8 | 1.95 | V    |

| $V_{DD3}$             | 3.3V Supply Voltage                            |                                                                                                                                                                                                   | 3.0  | 3.3 | 3.6  | V    |

| $AV_{DD}$             | 1.8V Analog Supply Voltage                     |                                                                                                                                                                                                   | 1.65 | 1.8 | 1.95 | V    |

| I <sub>DD</sub>       | V <sub>DD</sub> Power Supply Current           | MCLK = 23.92MHz; sat1, sat2<br>& terr arms active;<br>V <sub>DD</sub> =1.95V                                                                                                                      |      | 130 | 160  | mA   |

| I <sub>DD3</sub>      | V <sub>DD3</sub> Power Supply Current          | MCLK = 23.92MHz; sat1, sat2<br>& terr arms active; V <sub>DD3</sub> =3.6V                                                                                                                         |      | 45  | 90   | mA   |

| I <sub>AVDDsat</sub>  | AV <sub>Ddsat</sub> Power Supply Current       | $\label{eq:mclk} \begin{array}{l} \mbox{MCLK} = 23.92\mbox{MHz}; \\ \mbox{V}_{\rm IN} = 0.75\mbox{Vpp}; \mbox{f}_{\rm IN} = 6.095\mbox{MHz}; \\ \mbox{AV}_{\rm Ddsat} = 1.95\mbox{V} \end{array}$ |      | 16  | 20   | mA   |

| I <sub>AVDDterr</sub> | AV <sub>Ddterr</sub> Power Supply Current      | MCLK = 23.92MHz;<br>V <sub>IN</sub> =0.75Vpp; f <sub>IN</sub> =2.99MHz;<br>AV <sub>Ddterr</sub> =1.95V                                                                                            |      | 16  | 20   | mA   |

| Pd                    | Power Dissipation                              | MCLK = 23.92MHz;<br>V <sub>DD</sub> = 1.8V; V <sub>DD3</sub> = 3.3V                                                                                                                               |      | 350 |      | mW   |

| l <sub>il</sub>       | Low level input leakage current 1)             | Vi = 0V                                                                                                                                                                                           |      |     | 1    | μΑ   |

| l <sub>ih</sub>       | High level input leakage current 1)            | Vi = V <sub>DD3</sub>                                                                                                                                                                             |      |     | 1    | μΑ   |

| loz                   | Tristare output leakage current 2)             | Vo = 0V or V <sub>DD3</sub>                                                                                                                                                                       |      |     | 1    | μA   |

| I <sub>pd</sub>       | Pull-down current                              | Vi = V <sub>DD3</sub>                                                                                                                                                                             | 30   |     | 110  | μA   |

| R <sub>pu</sub>       | Equivalent pull-up resistance 7)               | Vi = 0V                                                                                                                                                                                           |      | 50  |      | KΩ   |

| R <sub>pd</sub>       | Equivalent pull-down resistance 7)             | Vi = V <sub>DD3</sub>                                                                                                                                                                             |      | 50  |      | kΩ   |

| V <sub>il</sub>       | Low level input voltage                        |                                                                                                                                                                                                   |      |     | 0.8  | V    |

| Vih                   | High level input voltage                       |                                                                                                                                                                                                   | 2    |     |      | V    |

| V <sub>ilhyst</sub>   | Low level threshold input falling              |                                                                                                                                                                                                   | 0.8  |     | 1.35 | V    |

| V <sub>ihhyst</sub>   | High level threshold input rising              |                                                                                                                                                                                                   | 1.3  |     | 2    | V    |

| V <sub>hyst</sub>     | Schmitt trigger hysteresis <sup>3)</sup>       |                                                                                                                                                                                                   | 0.3  |     | 0.8  | V    |

| Vol                   | Low level output voltage 4,5)                  | lol = XmA                                                                                                                                                                                         |      |     | 0.2  | V    |

| Voh                   | High level output voltage <sup>4,5)</sup>      | loh = XmA                                                                                                                                                                                         | 2.8  |     |      | V    |

| Cin                   | Input capacitance 3)                           |                                                                                                                                                                                                   |      |     | 1.2  | pF   |

| Cout                  | Output Capacitance 3)                          |                                                                                                                                                                                                   |      |     | 1.9  | pF   |

| Cio                   | I/O (bi-directional) capacitance <sup>3)</sup> |                                                                                                                                                                                                   |      |     | 2.1  | pF   |

| Ilatchup              | I/O Latch-up current                           |                                                                                                                                                                                                   | 200  |     |      | mA   |

| V <sub>ESD</sub>      | Electrostatic Protection <sup>6)</sup>         | Leakage<1µA                                                                                                                                                                                       | 4000 |     |      | V    |

Note 1: Performed on all the input pins excluded the pull-down ones Note 2: Performed on the I/O pins in tristate mode

Note 2: Performed on the I/O pins in instate mode Note 3: Guaranteed by Design Note 4: take into account 200mV voltage drop in supply lines and Input/Output levels for frequency > 20MHz. Note 5. X is the source/sink current under worst case conditions (X = 2 to 4 mA) Note 6: Human body Model Note 7. Guaranteed by Ipd measurements

# ADC ELECTRICAL CHARACTERISTCS: ( $T_{amb}$ = -40 to +85°C, $V_{DD}$ =1.8V, $AV_{DD}$ = 1.65 to 1.95V, $V_{DD3}$ = 3.3V unless otherwise specified

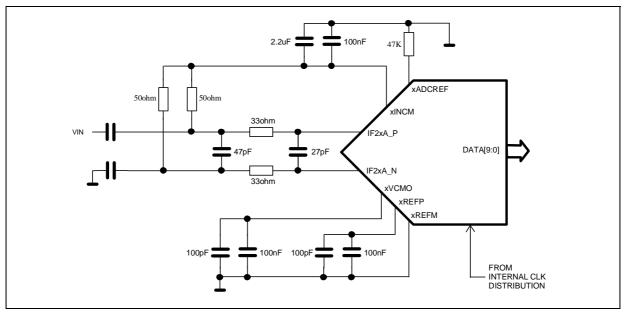

# ADC Analog Input

| Symbol                         | Parameter                       | Conditions | Min   | Тур  | Max   | Unit |

|--------------------------------|---------------------------------|------------|-------|------|-------|------|

| IF2xA_P,<br>IF2xA_N            | Voltage Range                   |            |       | 0.75 |       | Vpp  |

| XINCM                          | Internal Common Mode            |            | 0.375 |      | 0.625 | V    |

| R <sub>in</sub> <sup>(1)</sup> | Input Resistance 2)             | @75MHz     |       | 35   |       | kΩ   |

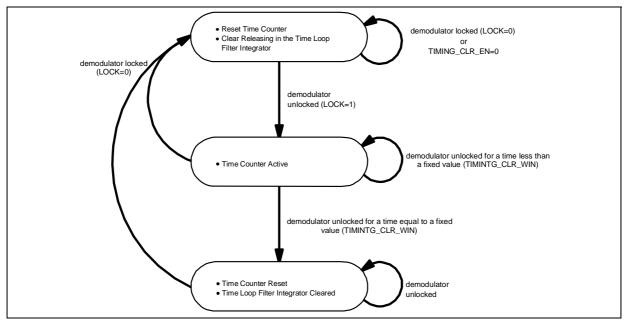

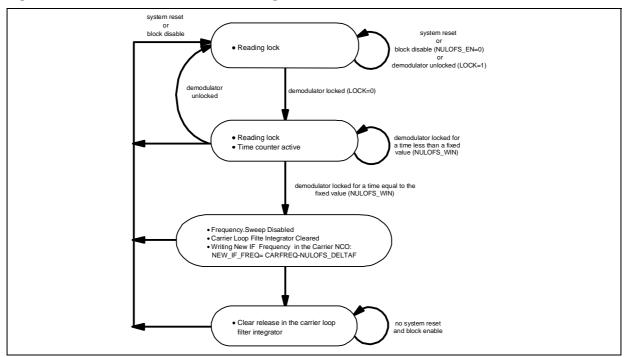

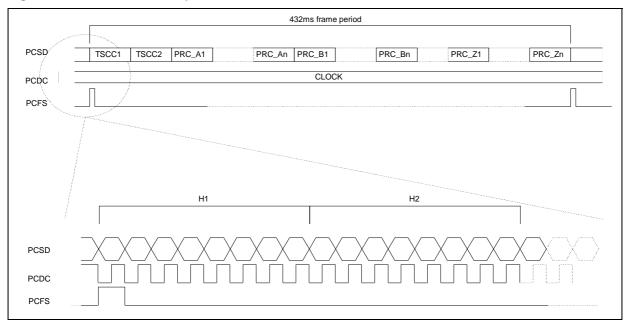

| C <sub>in</sub>                | Input Capacitance <sup>2)</sup> |            |       | 800  |       | fF   |