## STM6717/6718/6719/6720 STM6777/6778/6779/6780

Dual/triple ultra-low voltage supervisors with push-button reset (with delay option)

#### **Features**

- Primary supply (V<sub>CC1</sub>) monitor. Fixed (factory-programmed) reset thresholds: 4.63V to 1.58V

- Secondary supply (V<sub>CC2</sub>) monitor (STM6717/18/19/20/77/78).

- Fixed (factory-programmed) reset thresholds: 3.08V to 0.79V

- Tertiary supply monitor (using externally adjustable rstin):

- 0.626V internal reference

- $\overline{RST}$  outputs (push-pull or open drain); state guaranteed IF  $V_{CC1}$  OR  $V_{CC2} \ge 0.8V$

- Reset delay time (t<sub>rec</sub>) on power-up: 210ms(typ)

- Manual reset input (MR)

- Optional delayed manual reset input (MRC) with external capacitor (STM6777/78/79/80)

- Low supply current 11µA (typ), V<sub>CC1</sub> =V<sub>CC2</sub>=3.6V

- Operating temperature: -40°C to 85°C (industrial grade)

#### Table 1. Device options

| Part    | Moni             | tored vol        | tages | Manual reset | Delayed  | Reset out | tput (RST)              |         |  |

|---------|------------------|------------------|-------|--------------|----------|-----------|-------------------------|---------|--|

| number  | V <sub>CC1</sub> | V <sub>CC2</sub> | RSTIN | input (MR)   | MRnin    |           | Active-low (open drain) | Package |  |

| STM6717 | ~                | ~                |       | ~            |          |           | ~                       | WY      |  |

| STM6718 | <b>/</b>         | ~                |       | ~            |          | ~         |                         | WY      |  |

| STM6719 | ~                | ~                | ~     | ~            |          |           | ~                       | WB      |  |

| STM6720 | <b>/</b>         | ~                | ~     | ~            |          | ~         |                         | WB      |  |

| STM6777 | <b>V</b>         | ~                |       | ~            | V        |           | ~                       | WB      |  |

| STM6778 | ~                | ~                |       | ~            | <b>V</b> | ~         |                         | WB      |  |

| STM6779 | <b>V</b>         |                  | ~     | ~            | V        |           | ~                       | WB      |  |

| STM6780 | <b>V</b>         |                  | ~     | ~            | V        | ~         |                         | WB      |  |

## **Contents**

| Summary description                                           | 5    |

|---------------------------------------------------------------|------|

| Pin Descriptions                                              | 7    |

| Active-Low, Push-pull Reset Output (RST) - STM6718/20/78/80   | 7    |

| Active-Low, Open Drain Reset Output (RST) - STM6717/19/77/79  | 7    |

| Push-Button Reset Input (MR)                                  |      |

| Manual Reset Delay Input (MRC) - STM6777/78/79/80)            | 8    |

| Primary Supply Voltage Monitoring Input (V <sub>CC1</sub> )   | 8    |

| Secondary Supply Voltage Monitoring Input (V <sub>CC2</sub> ) | 8    |

| Adjustable Reset Comparator Input (RSTIN; STM6719/20/79/80)   | 8    |

| Operation                                                     | . 10 |

| Applications Information                                      | . 10 |

| ypical operating characteristics                              | . 11 |

| Maximum rating                                                | . 17 |

| OC and AC parameters                                          | . 18 |

| Package mechanical data                                       | . 22 |

| Part numbering                                                | . 25 |

| Sevision history                                              | 26   |

## List of tables

| Table 1.  | Device options                                                    | 1  |

|-----------|-------------------------------------------------------------------|----|

| Table 2.  | Signal names                                                      | 6  |

| Table 3.  | Pin functions                                                     | 8  |

| Table 4.  | Absolute maximum ratings                                          | 17 |

| Table 5.  | Operating and AC measurement conditions                           | 18 |

| Table 6.  | DC and AC characteristics                                         | 19 |

| Table 7.  | t <sub>MLMH</sub> Minimum pulse width                             | 21 |

| Table 8.  | SOT23-5 – 5-lead small outline transistor package mechanical data | 23 |

| Table 9.  | SOT23-6 – 6-lead small outline transistor package mechanical data | 24 |

| Table 10. | Ordering information scheme                                       | 25 |

| Table 11. | Document revision history                                         | 26 |

# **List of figures**

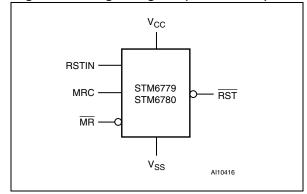

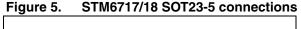

| Figure 1.  | Logic diagram (STM6717/18)                                                         | 6  |

|------------|------------------------------------------------------------------------------------|----|

| Figure 2.  | Logic diagram (STM6777/78)                                                         | 6  |

| Figure 3.  | Logic diagram (STM6719/20)                                                         | 6  |

| Figure 4.  | Logic diagram (STM6779/80)                                                         | 6  |

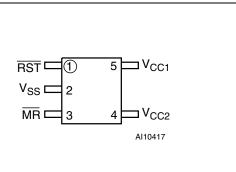

| Figure 5.  | STM6717/18 SOT23-5 connections                                                     | 7  |

| Figure 6.  | STM6777/78 SOT23-6 connections                                                     | 7  |

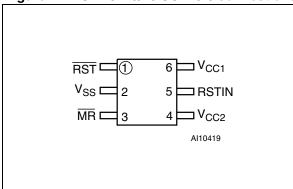

| Figure 7.  | STM6719/20 SOT23-6 connections                                                     | 7  |

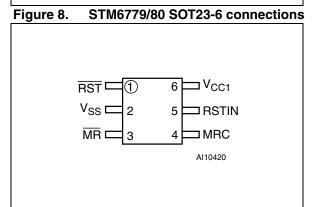

| Figure 8.  | STM6779/80 SOT23-6 connections                                                     | 7  |

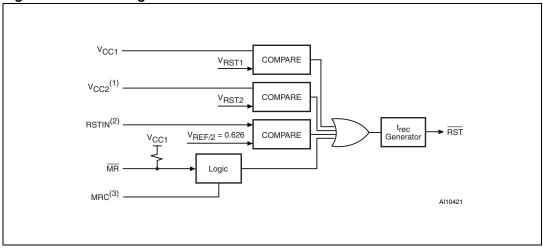

| Figure 9.  | Block diagram                                                                      | 9  |

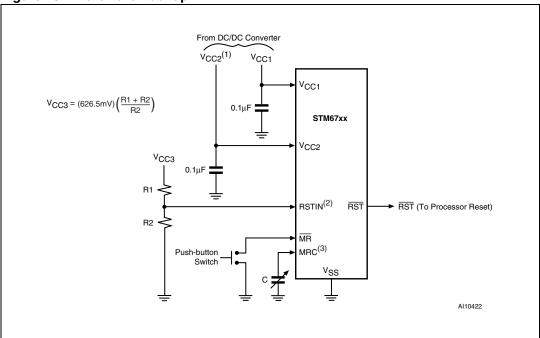

| Figure 10. | Hardware hookup                                                                    | 9  |

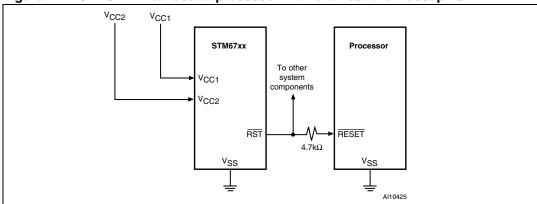

| Figure 11. | STM67xx interface to processor with bi-directional reset pins                      | 10 |

| Figure 12. | Ensuring RST valid to V <sub>CC</sub> = 0 (active-low, push-pull outputs)          | 10 |

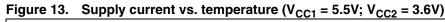

| Figure 13. | Supply current vs. temperature (V <sub>CC1</sub> = 5.5V; V <sub>CC2</sub> = 3.6V)  | 11 |

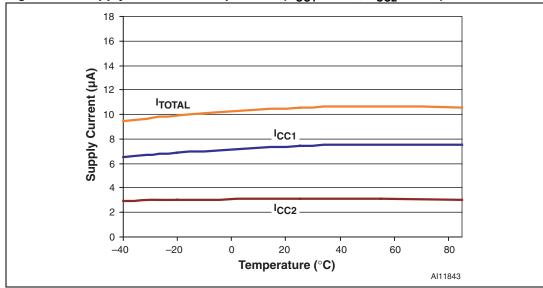

| Figure 14. | Supply current vs. temperature (V <sub>CC1</sub> = 3.6V; V <sub>CC2</sub> = 2.75V) | 11 |

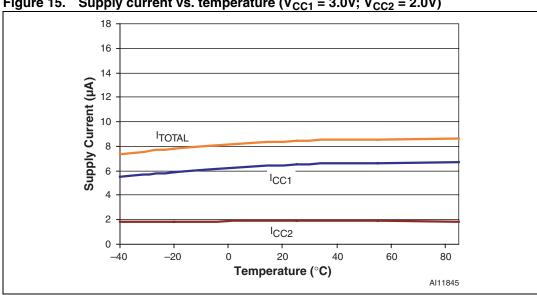

| Figure 15. | Supply current vs. temperature (V <sub>CC1</sub> = 3.0V; V <sub>CC2</sub> = 2.0V)  |    |

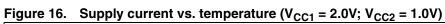

| Figure 16. | Supply current vs. temperature (V <sub>CC1</sub> = 2.0V; V <sub>CC2</sub> = 1.0V)  |    |

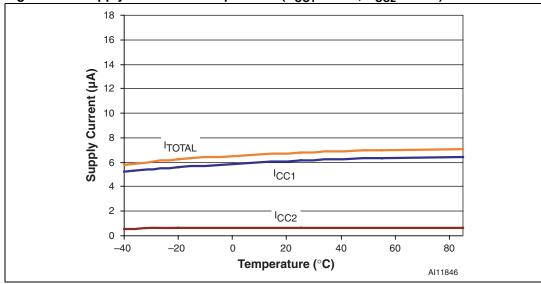

| Figure 17. | Normalized V <sub>CC</sub> reset time-out period vs. temperature                   |    |

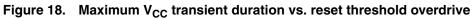

| Figure 18. | Maximum V <sub>CC</sub> transient duration vs. reset threshold overdrive           | 13 |

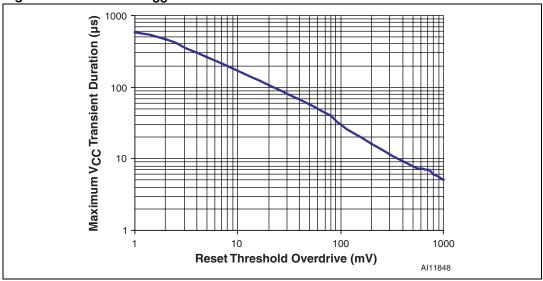

| Figure 19. | Normalized V <sub>RST1</sub> threshold vs. temperature                             |    |

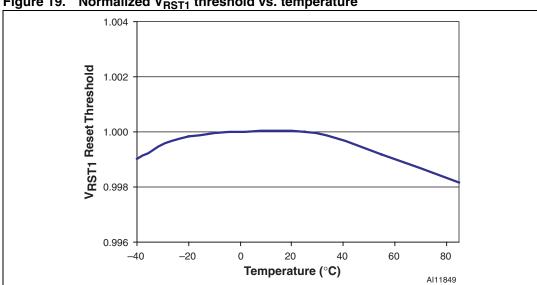

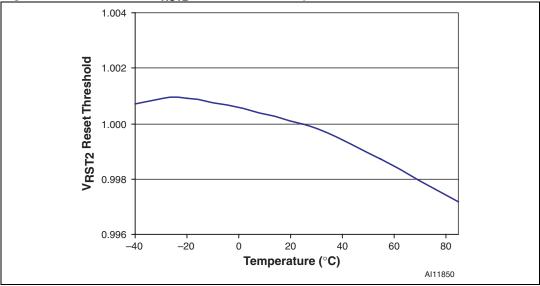

| Figure 20. | Normalized V <sub>RST2</sub> threshold vs. temperature                             |    |

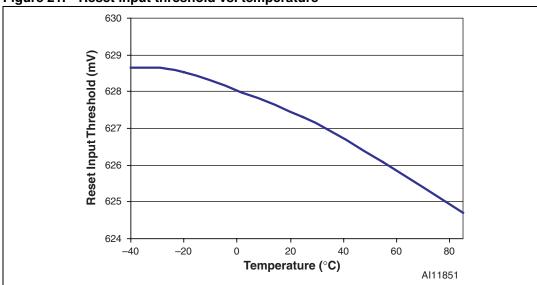

| Figure 21. | Reset input threshold vs. temperature                                              |    |

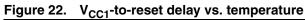

| Figure 22. | V <sub>CC1</sub> -to-reset delay vs. temperature                                   |    |

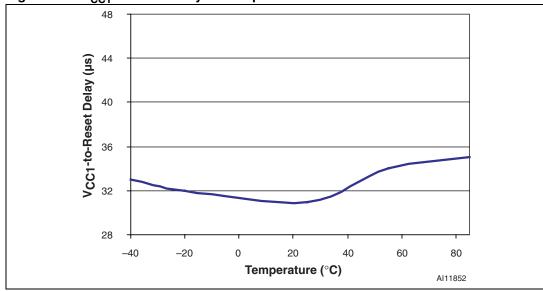

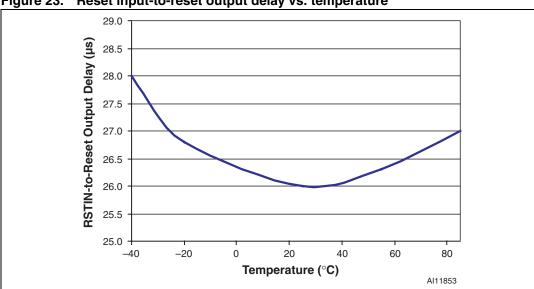

| Figure 23. | Reset input-to-reset output delay vs. temperature                                  |    |

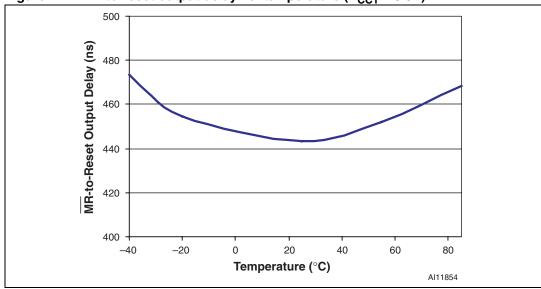

| Figure 24. | MR-to-reset output delay vs. temperature $(V_{CC1} = 3.6V)$                        |    |

| Figure 25. | AC Testing Input/Output Waveforms                                                  |    |

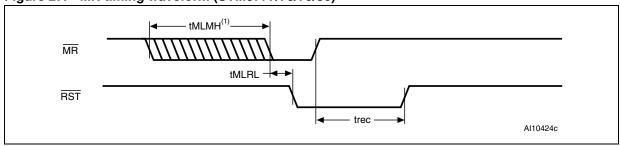

| Figure 26. | MR timing waveform (STM6717/18/19/20)                                              |    |

| Figure 27. | MR timing waveform (STM6777/78/79/80)                                              |    |

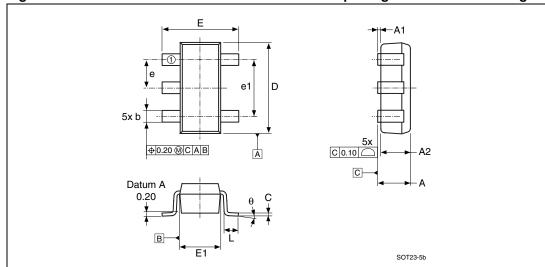

| Figure 28. | SOT23-5 – 5-lead small outline transistor package mechanical drawing               | 22 |

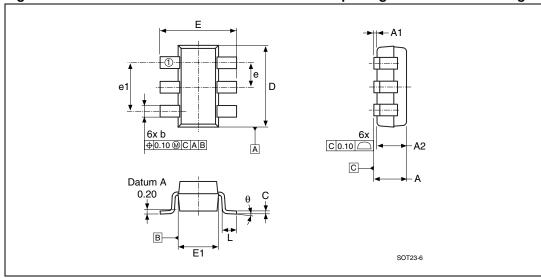

| Figure 29  | SOT23-6 – 6-lead small outline transistor package mechanical drawing               | 23 |

## **Summary description**

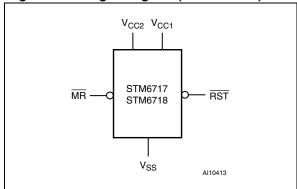

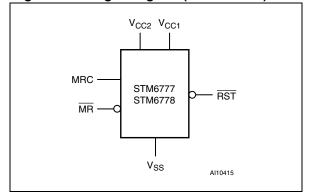

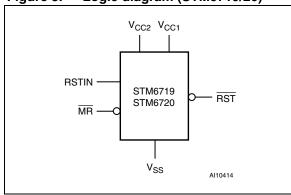

The STM6717/18/19/20 and STM6777/78/79/80 Supervisors are a family of low voltage/low supply current processor (Micro or DSP) Supervisors, designed to monitor two (or three) system power supply voltages. They are targeted at applications such as Set-Top Boxes (STBs), portable, battery-powered systems, networking, and communication systems.

All device options have a push-button-type manual reset input  $(\overline{MR})$ . The STM6777/78/79/80 also includes an option which enables the user to delay the start of the Manual Reset process from 6µs (MRC pin left open) or more with external capacitor. The delay is implemented by connecting the appropriately sized capacitor between the MRC pin and  $V_{SS}$  (typical 4s delay with a 3.3µF capacitor, see *Table 7 on page 21*).

Two of the three supplies monitored ( $V_{CC1}$  and  $V_{CC2}$ ) have fixed (customer-selectable, factory-trimmed) thresholds ( $V_{RST1}$  and  $V_{RST2}$ ). The third voltage is monitored using an externally adjustable RSTIN threshold (0.626V internal reference).

If any of the three monitored voltages drop below its factory-trimmed or adjustable thresholds, or if  $\overline{\text{MR}}$  is asserted to logic low, a  $\overline{\text{RST}}$  is asserted (driven low). Once asserted,  $\overline{\text{RST}}$  is maintained at Low for a minimum delay period (t<sub>rec</sub>) after ALL supplies rise above their respective thresholds and  $\overline{\text{MR}}$  returns to High. These devices are guaranteed to be in the correct reset output logic state when V<sub>CC1</sub> and/or V<sub>CC2</sub> is greater than 0.8V.

These devices are available in a standard 5-pin or 6-pin SOT23 packages (see *Table 1 on page 1*).

Figure 1. Logic diagram (STM6717/18)

Figure 2. Logic diagram (STM6777/78)

Figure 3. Logic diagram (STM6719/20)

Figure 4. Logic diagram (STM6779/80)

Table 2. Signal names

|                  | g                                 |

|------------------|-----------------------------------|

| MR               | Push-button reset input           |

| MRC              | Manual reset delay input          |

| RST              | Active-low reset output           |

| V <sub>CC1</sub> | Primary supply voltage input      |

| V <sub>CC2</sub> | Secondary supply voltage input    |

| RSTIN            | Adjustable reset comparator input |

| V <sub>SS</sub>  | Ground                            |

Figure 6. STM6777/78 SOT23-6 connections

RST 1 6 Vcc1

Vss 2 5 MRC

MR 3 4 Vcc2

Al10418

Figure 7. STM6719/20 SOT23-6 connections

### **Pin Descriptions**

### Active-Low, Push-pull Reset Output (RST) - STM6718/20/78/80

The  $\overline{RST}$  pin is driven low and stays low whenever  $V_{CC1}$  or  $V_{CC2}$  or RSTIN falls below its factory-trimmed or adjustable reset threshold or when MR goes to logic low. It remains low for  $t_{rec}$  after ALL supply voltages being monitored rise above their reset thresholds and  $\overline{MR}$  goes from low to high. (Push-pull outputs are referenced to  $V_{CC1}$ .)

### Active-Low, Open Drain Reset Output (RST) - STM6717/19/77/79

The  $\overline{RST}$  pin is driven low and stays low whenever  $V_{CC1}$  or  $V_{CC2}$  or RSTIN falls below its factory-trimmed or adjustable reset threshold or when  $\overline{MR}$  goes to logic low. It remains low for  $t_{rec}$  after ALL supply voltages being monitored rise above their reset thresholds and  $\overline{MR}$  goes from low to high. Connect an external pull-up resistor to  $V_{CC1}$ . A  $10k\Omega$  pull-up resistor should be sufficient for most applications.

## Push-Button Reset Input (MR)

When  $\overline{MR}$  goes low the  $\overline{RST}$  output is driven low.  $\overline{RST}$  remains low as long as  $\overline{MR}$  is low and for  $t_{rec}$  after  $\overline{MR}$  returns to high. This active-low input has an internal  $50k\Omega$  pull-up resistor to

$V_{CC1}$ . It can be driven from a TTL or CMOS logic line, or with open drain/collector outputs, or connected to  $V_{SS}$  through a switch. If unused, leave this pin open or connect it to  $V_{CC1}$ .

Connect a normally open momentary switch from  $\overline{MR}$  to  $V_{SS}$ ; external debounce circuitry is not required. (If  $\overline{MR}$  is driven from long cables or if the device is used in noisy environments, connecting a  $0.1\mu F$  capacitor from  $\overline{MR}$  to  $V_{SS}$  provides additional noise immunity.

#### Manual Reset Delay Input (MRC) - STM6777/78/79/80)

This pin is either left open or connected to  $V_{SS}$  via a capacitor. By selecting the appropriate capacitor, the manual reset process, initiated by pressing the push-button Manual Reset Input, can be delayed by any value from 6 $\mu$ s or more (see *Table 7 on page 21*).

#### Primary Supply Voltage Monitoring Input (V<sub>CC1</sub>)

It also is the input for the primary reset threshold monitor. Available fixed (customer-selectable, factory-programmed) reset thresholds include 4.63V to 1.58V.

### Secondary Supply Voltage Monitoring Input (V<sub>CC2</sub>)

This function is available on the STM6717/18/19/20/77/78. Fixed (customer-selectable, factory-programmed) reset thresholds include 3.08V to 0.79V.

#### Adjustable Reset Comparator Input (RSTIN; STM6719/20/79/80)

This is a high impedance input.  $\overline{RST}$  is driven low when the voltage at the RSTIN pin falls below 0.626V (internal reference voltage at this comparator). The monitored voltage reset threshold is set with an external resistor-divider network.

Table 3. Pin functions

| Pin                |                    |                    |                    | Name             | Function                          |

|--------------------|--------------------|--------------------|--------------------|------------------|-----------------------------------|

| STM6717<br>STM6718 | STM6719<br>STM6720 | STM6777<br>STM6778 | STM6779<br>STM6780 |                  |                                   |

| 1                  | 1                  | 1                  | 1                  | RST              | Active-low reset output           |

| 3                  | 3                  | 3                  | 3                  | MR               | Push-button reset input           |

| _                  | _                  | 5                  | 4                  | MRC              | Manual reset delay input          |

| 5                  | 6                  | 6                  | 6                  | V <sub>CC1</sub> | Primary supply voltage input      |

| 4                  | 4                  | 4                  | _                  | $V_{CC2}$        | Secondary supply voltage input    |

| _                  | 5                  | _                  | 5                  | RSTIN            | Adjustable reset comparator input |

| 2                  | 2                  | 2                  | 2                  | V <sub>SS</sub>  | Ground                            |

Figure 9. Block diagram

- 1.  $V_{CC2}$  Input is available on STM6717/18/19/20/77/78.

- 2. RSTIN available only on STM6719/20/79/80.

- 3. MRC available only on STM6777/78/79/80.

Figure 10. Hardware hookup

- 1.  $V_{CC2}$  is available only on STM6717/18/19/20/77/78.

- 2. RSTIN available only on STM6719/20/79/80.

- 3. MRC available only on STM6777/78/79/80.

### **Operation**

### **Applications Information**

1. Interfacing to Processors with Bi-directional Reset Pins

Most processors with bi-directional reset pins can interface directly to the open drain  $\overline{\text{RST}}$  outputs (STM6717/19/77/79). Systems simultaneously requiring a push-pull  $\overline{\text{RST}}$  output and a bi-directional reset interface can be in logic contention. To prevent this contention, connect a  $4.7 \text{k}\Omega$  resistor between  $\overline{\text{RST}}$  and the processor's Reset I/O as shown in *Figure 11*.

2. Ensuring a Valid  $\overline{RST}$  Output Down to  $V_{CC} = 0V$

The STM67xx Supervisors are guaranteed to be in the correct  $\overline{RST}$  output logic state when  $V_{CC1}$  and/or  $V_{CC2}$  is greater than 0.8V. In applications which require valid reset levels down to  $V_{CC}=0$ , a pull-down resistor to active-low outputs (push-pull only, see *Figure 12*) will ensure that the reset line is valid while the reset output can no longer sink or source current. This scheme does NOT work with the open drain outputs of the STM6717/19/77/79.

The resistor value used is not critical, but it must be large enough not to load the reset output when  $V_{CC}$  is above the reset threshold. For most applications,  $100k\Omega$  is adequate.

Figure 11. STM67xx interface to processor with bi-directional reset pins

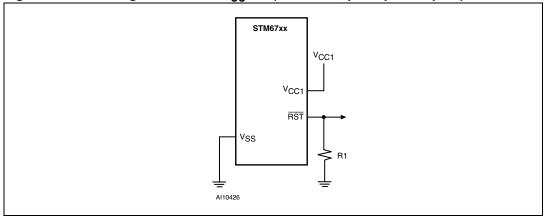

Figure 12. Ensuring RST valid to  $V_{CC} = 0$  (active-low, push-pull outputs)

## **Typical operating characteristics**

Note: Typical values are at  $T_A = 25$ °C unless otherwise noted.

Figure 14. Supply current vs. temperature ( $V_{CC1} = 3.6V$ ;  $V_{CC2} = 2.75V$ )

Supply current vs. temperature ( $V_{CC1} = 3.0V$ ;  $V_{CC2} = 2.0V$ ) Figure 15.

Figure 17. Normalized  $V_{CC}$  reset time-out period vs. temperature

Normalized V<sub>RST1</sub> threshold vs. temperature

Figure 21. Reset input threshold vs. temperature

Figure 23. Reset input-to-reset output delay vs. temperature

## **Maximum rating**

Stressing the device above the rating listed in the Absolute Maximum Ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 4. Absolute maximum ratings

| Symbol                              | Parameter                                 | Value                     | Unit                      |    |

|-------------------------------------|-------------------------------------------|---------------------------|---------------------------|----|

| T <sub>STG</sub>                    | Storage temperature (V <sub>CC</sub> Off) | -55 to 150                | °C                        |    |

| T <sub>SLD</sub> <sup>(1)</sup>     | Lead solder temperature for 10 seconds    | 260                       | °C                        |    |

| V <sub>IO</sub>                     | Input or output voltage                   | $-0.3$ to $V_{CC1} + 0.3$ | V                         |    |

| V IO                                | Imput or output voltage                   |                           | $-0.3$ to $V_{CC2} + 0.3$ | V  |

| V <sub>CC1</sub> , V <sub>CC2</sub> | Supply voltage                            |                           | -0.3 to 7.0               | V  |

| I <sub>IO</sub>                     | Input or output current (all pins)        |                           | 20                        | mA |

| D                                   | Power dissipation                         | SOT23-5                   | 654                       | mW |

| P <sub>D</sub>                      | Fower dissipation                         | SOT23-6                   | 675                       | mW |

Note:

Reflow at peak temperature of 255°C to 260°C for < 30 seconds (total thermal budget not to exceed 180°C for between 90 to 150 seconds).

## DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristics Tables that follow, are derived from tests performed under the Measurement Conditions summarized in *Table 5*, Operating and AC Measurement Conditions. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

Table 5. Operating and AC measurement conditions

| Parameter                                       | STM67xx                   | Unit |

|-------------------------------------------------|---------------------------|------|

| V <sub>CC</sub> supply voltage                  | 0.8 to 5.5                | V    |

| Ambient operating temperature (T <sub>A</sub> ) | -40 to 85                 | °C   |

| Input rise and fall times                       | ≤ 5                       | ns   |

| Input pulse voltages                            | 0.2 to 0.8V <sub>CC</sub> | V    |

| Input and output timing ref. voltages           | 0.3 to 0.7V <sub>CC</sub> | V    |

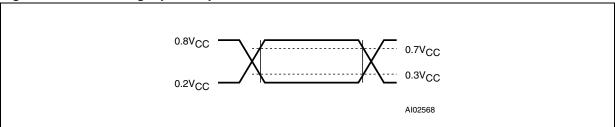

Figure 25. AC Testing Input/Output Waveforms

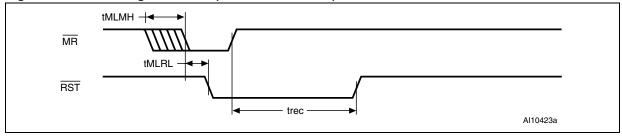

Figure 26. MR timing waveform (STM6717/18/19/20)

Figure 27.  $\overline{\rm MR}$  timing waveform (STM6777/78/79/80)

By connecting a certain capacitor between the MRC pin and V<sub>SS</sub>, the RST can be delayed from 6μs or more (t<sub>MLMH</sub>, see *Table 7 on page 21*).

57/

Table 6. DC and AC characteristics

| Sym                             | Alter-<br>native | Description                                       | Test Condition <sup>(1)</sup>                                                                     | Test Condition <sup>(1)</sup> Min |       | Max   | Unit |

|---------------------------------|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------|-------|-------|------|

| V <sub>CC</sub>                 |                  | Operating voltage                                 |                                                                                                   | 0.8                               |       | 5.5   | V    |

|                                 |                  | V supply surrent                                  | V <sub>CC1</sub> < 5.5V, all I/O pins open                                                        |                                   | 12    | 35    | μΑ   |

| I <sub>CC1</sub>                |                  | V <sub>CC1</sub> supply current                   | V <sub>CC1</sub> < 3.6V, all I/O pins open                                                        |                                   | 8     | 23    | μΑ   |

|                                 |                  | V supply surrent                                  | V <sub>CC2</sub> < 3.6V, all I/O pins open                                                        |                                   | 3     | 9     | μΑ   |

| I <sub>CC2</sub>                |                  | V <sub>CC2</sub> supply current                   | V <sub>CC2</sub> < 2.75V, all I/O pins open                                                       |                                   | 2.5   | 7     | μΑ   |

| I <sub>LI</sub> <sup>(2)</sup>  |                  | Input leakage current                             | $0V = V_{IN} = V_{CC}$                                                                            | -1                                |       | +1    | μΑ   |

| I <sub>LO</sub>                 |                  | Open drain RST output leakage current             | V <sub>CC1</sub> > V <sub>RST1</sub> , V <sub>CC2</sub> > V <sub>RST2</sub> ;<br>RST not asserted |                                   |       | 0.5   | μΑ   |

|                                 |                  |                                                   | $V_{CC1}$ or $V_{CC2} \ge 0.8V$ , $I_{SINK} = 1\mu A$ , $\overline{RST}$ asserted                 |                                   |       | 0.3   | V    |

|                                 |                  |                                                   | V <sub>CC1</sub> or V <sub>CC2</sub> ≥ 1.0V,<br>I <sub>SINK</sub> = 50μA, <del>RST</del> asserted |                                   |       | 0.3   | V    |

| V <sub>OL</sub>                 |                  | Output low voltage (RST; push-pull or open drain) | $V_{CC1}$ or $V_{CC2} \ge 1.2V$ ,<br>$I_{SINK} = 100\mu A$ , $\overline{RST}$ asserted            |                                   |       | 0.3   | V    |

|                                 |                  |                                                   | $V_{CC1}$ or $V_{CC2} \ge 2.7V$ , $I_{SINK} = 1.2$ mA, $\overline{RST}$ asserted                  |                                   |       | 0.3   | V    |

|                                 |                  |                                                   | $V_{CC1}$ or $V_{CC2} \ge 4.5V$ , $I_{SINK} = 3.2$ mA, $\overline{RST}$ asserted                  |                                   |       | 0.4   | ٧    |

|                                 |                  |                                                   | V <sub>CC1</sub> ≥ 1.8V, I <sub>SOURCE</sub> = 200μA,<br>RST not asserted                         | 0.8V <sub>CC1</sub>               |       |       | V    |

| V <sub>OH</sub>                 |                  | Output high voltage (RST; push-pull only)         | V <sub>CC1</sub> ≥ 2.7V, I <sub>SOURCE</sub> = 500μA,<br>RST not asserted                         | 0.8V <sub>CC1</sub>               |       |       | V    |

|                                 |                  |                                                   | $V_{CC1} \ge 4.5V$ , $I_{SOURCE} = 800\mu A$ , RST not asserted                                   | 0.8V <sub>CC1</sub>               |       |       | V    |

| t <sub>R</sub> <sup>(3)</sup>   |                  | Push-pull RST rise time<br>(STM6718/20/78/80)     | Rise time measured from 10% to 90% of $V_{CC}$ ; $C_L = 5pF$ , $V_{CC} = 3.3V$                    |                                   | 5     | 25    | ns   |

|                                 |                  |                                                   | Reset thresholds                                                                                  |                                   |       |       |      |

|                                 |                  |                                                   | L (falling)                                                                                       | 4.500                             | 4.625 | 4.750 | V    |

|                                 |                  |                                                   | M (falling)                                                                                       | 4.250                             | 4.375 | 4.500 | V    |

|                                 |                  |                                                   | T (falling)                                                                                       | 3.000                             | 3.075 | 3.150 | V    |

|                                 |                  |                                                   | S (falling)                                                                                       | 2.850                             | 2.925 | 3.000 | V    |

| V <sub>RST</sub> <sup>(4)</sup> | V <sub>TH1</sub> | V <sub>CC1</sub> reset threshold                  | R (falling)                                                                                       | 2.550                             | 2.625 | 2.700 | V    |

|                                 |                  |                                                   | Z (falling)                                                                                       | 2.250                             | 2.313 | 2.375 | V    |

|                                 |                  |                                                   | Y (falling)                                                                                       | 2.125                             | 2.188 | 2.250 | V    |

|                                 |                  |                                                   | W (falling)                                                                                       | 1.620                             | 1.665 | 1.710 | V    |

|                                 |                  |                                                   | V (falling)                                                                                       | 1.530                             | 1.575 | 1.620 | V    |

Table 6. DC and AC characteristics (continued)

| Sym                 | Alter-<br>native | Description                             | Test Condition <sup>(1)</sup>                                                    | Min   | Тур             | Max   | Unit |

|---------------------|------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|-----------------|-------|------|

|                     |                  |                                         | T (falling)                                                                      | 3.000 | 3.075           | 3.150 | V    |

|                     |                  |                                         | S (falling)                                                                      | 2.850 | 2.925           | 3.000 | V    |

|                     |                  |                                         | R (falling)                                                                      | 2.550 | 2.625           | 2.700 | ٧    |

|                     |                  |                                         | Z (falling)                                                                      | 2.250 | 2.313           | 2.375 | V    |

|                     |                  |                                         | Y (falling)                                                                      | 2.125 | 2.188           | 2.250 | V    |

|                     |                  |                                         | W (falling)                                                                      | 1.620 | 1.665           | 1.710 | ٧    |

|                     |                  |                                         | V (falling)                                                                      | 1.530 | 0 1.575 1.620 V |       |      |

| $V_{RST2}^{(4)}$    | V <sub>TH2</sub> | V <sub>CC2</sub> reset threshold        | I (falling)                                                                      | 1.350 | 1.388           | 1.425 | V    |

|                     |                  |                                         | H (falling)                                                                      | 1.275 | 1.313           | 1.350 | V    |

|                     |                  |                                         | G (falling)                                                                      | 1.080 | 1.110           | 1.140 | V    |

|                     |                  |                                         | F (falling)                                                                      | 1.020 | 1.050           | 1.080 | V    |

|                     |                  |                                         | K (falling)                                                                      | 0.895 | 0.925           | 0.955 | ٧    |

|                     |                  |                                         | J (falling)                                                                      |       | 0.875           | 0.905 | V    |

|                     |                  | E (falling) 0.8                         |                                                                                  | 0.810 | 0.833           | 0.855 | V    |

|                     |                  |                                         | D (falling)                                                                      | 0.765 | 0.788           | 0.810 | V    |

| V <sub>HYST</sub>   |                  | Reset threshold hysteresis              | Referenced to V <sub>RST</sub> typical                                           |       | 0.5             |       | %    |

|                     |                  | V to DOT delevi                         | $V_{CC1} = (V_{RST1} + 100 \text{mV}) \text{ to}$<br>$(V_{RST} - 100 \text{mV})$ |       | 20              |       | μs   |

| t <sub>RD</sub>     |                  | V <sub>CC</sub> to <del>RST</del> delay | $V_{CC2} = (V_{RST2} + 75mV)$ to $(V_{RST2} - 75mV)$                             |       | 20              |       | μs   |

| t <sub>rec</sub>    | t <sub>RP</sub>  | RST time-out period                     |                                                                                  | 140   | 210             | 280   | ms   |

|                     |                  | Adjustable reset                        | comparator input (STM6719/20/79/                                                 | 80)   |                 |       |      |

| V <sub>RSTIN</sub>  |                  | RSTIN input threshold                   |                                                                                  | 611   | 626.5           | 642   | mV   |

| I <sub>RSTIN</sub>  |                  | RSTIN input current                     |                                                                                  | -25   |                 | +25   | nA   |

|                     |                  | RSTIN hysteresis                        |                                                                                  |       | 3               |       | mV   |

| t <sub>RSTIND</sub> |                  | RSTIN to RST output delay               | V <sub>RSTIN</sub> to (V <sub>RSTIN</sub> – 30mV)                                |       | 22              |       | μs   |

Table 6. DC and AC characteristics (continued)

|                   | Bo and No ondiadonolios (continuou) |                                                                |                                                               |                     |     |                   |           |

|-------------------|-------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|---------------------|-----|-------------------|-----------|

| Sym               | Alter-<br>native                    | Description                                                    | Test Condition <sup>(1)</sup>                                 | Min                 | Тур | Max               | Unit      |

|                   |                                     | Manu                                                           | ual (push-button) reset input                                 |                     |     |                   |           |

| V <sub>IL</sub>   |                                     | MR input voltage                                               |                                                               |                     |     | 0.3V <sub>C</sub> | V         |

| $V_{IH}$          |                                     |                                                                |                                                               | 0.7V <sub>CC1</sub> |     |                   | V         |

|                   |                                     | MR minimum pulse width (STM6717/18/19/20)                      |                                                               | 1                   |     |                   | μs        |

| t <sub>MLMH</sub> | t <sub>MR</sub>                     | MR minimum pulse width (STM6777/78/79/80)                      | MRC connected via capacitor to V <sub>SS</sub> <sup>(5)</sup> |                     | 6   |                   | μs        |

| t <sub>MLRL</sub> | t <sub>MRD</sub>                    | $\overline{\text{MR}}$ to $\overline{\text{RST}}$ output delay |                                                               |                     | 200 |                   | ns        |

|                   |                                     | MR glitch immunity<br>(STM6717/18/19/20)                       |                                                               |                     | 100 |                   | ns        |

|                   |                                     | MR pull-up resistance                                          |                                                               | 25                  | 50  | 80                | $k\Omega$ |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = -40$  to  $85^{\circ}$ C;  $V_{CC1} = 0.8$  to 5.5V and  $V_{CC2} = 0.8$  to 3.6V (except where noted).

Table 7. t<sub>MLMH</sub> Minimum pulse width

| V <sub>CC1</sub> |       |       | Capacitor value <sup>(1)</sup> |       |       |       |  |  |  |

|------------------|-------|-------|--------------------------------|-------|-------|-------|--|--|--|

|                  | 100pF | 0.1μF | 2.2µF                          | 3.3µF | 4.7μF | 6.8µF |  |  |  |

| 1.6V             | 120µs | 120ms | 2.6s                           | 4.0s  | 5.6s  | 8.2s  |  |  |  |

| 2.0V             | 122µs | 122ms | 2.7s                           | 4.0s  | 5.8s  | 8.3s  |  |  |  |

| 3.0V             | 125µs | 125ms | 2.7s                           | 4.1s  | 5.9s  | 8.5s  |  |  |  |

| 4.0V             | 128µs | 129ms | 2.8s                           | 4.2s  | 6.0s  | 8.7s  |  |  |  |

| 5.0V             | 130µs | 130ms | 2.8s                           | 4.3s  | 6.1s  | 8.8s  |  |  |  |

1. At 25°C (typical)

<sup>2.</sup> Input leakage for the MRC pin is not tested.

<sup>3.</sup> Guaranteed by design.

$<sup>4. \</sup>quad \text{The leakage current measured on the } \overline{\text{RST}} \text{ pin is tested with the reset de-asserted (output high impedance)}.$

<sup>5.</sup> Selecting the appropriate external capacitor (preferably less than 100pF) allows systems designers to vary the minimum delay from 6µs (MRC pin left open) or more (see *Table 7*).

## Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97.

The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 28. SOT23-5 – 5-lead small outline transistor package mechanical drawing

Note:

Drawing is not to scale.

Table 8. SOT23-5 – 5-lead small outline transistor package mechanical data

| Symb | mm   |      |      | inches |       |       |

|------|------|------|------|--------|-------|-------|

|      | Тур  | Min  | Max  | Тур    | Min   | Max   |

| Α    | -    | -    | 1.45 | -      | -     | 0.057 |

| A1   | -    | _    | 0.15 | _      | _     | 0.006 |

| A2   | 1.15 | 0.90 | 1.30 | 0.045  | 0.035 | 0.051 |

| b    | -    | 0.30 | 0.50 | _      | 0.012 | 0.020 |

| С    | -    | 0.08 | 0.22 | _      | 0.003 | 0.009 |

| D    | 2.90 | -    | -    | 0.114  | _     | _     |

| E    | 2.80 | _    | _    | 0.110  | _     | _     |

| E1   | 1.60 | -    | -    | 0.063  | _     | _     |

| е    | 0.95 | -    | -    | 0.037  | _     | _     |

| e1   | 1.90 | _    | _    | 0.075  | _     | -     |

| L    | 0.45 | 0.30 | 0.60 | 0.018  | 0.012 | 0.024 |

| Q    | 4°   | 0°   | 8°   | 4°     | 0°    | 8°    |

| N    | 5    |      |      | 5      |       |       |

Note: Dimensions per JEDEC SOT/SOP Product Outline MO-178C, variation AA

Figure 29. SOT23-6 – 6-lead small outline transistor package mechanical drawing

Note: Drawing is not to scale.

Table 9. SOT23-6 – 6-lead small outline transistor package mechanical data

| Symb | mm   |      |      | inches |       |       |

|------|------|------|------|--------|-------|-------|

|      | Тур  | Min  | Max  | Тур    | Min   | Max   |

| Α    | -    | -    | 1.45 | -      | -     | 0.057 |

| A1   | -    | _    | 0.15 | _      | _     | 0.006 |

| A2   | 1.15 | 0.90 | 1.30 | 0.045  | 0.035 | 0.051 |

| b    | -    | 0.30 | 0.50 | _      | 0.012 | 0.020 |

| С    | -    | 0.08 | 0.22 | _      | 0.003 | 0.009 |

| D    | 2.90 | -    | -    | 0.114  | _     | _     |

| E    | 2.80 | _    | _    | 0.110  | _     | _     |

| E1   | 1.60 | -    | -    | 0.063  | _     | _     |

| е    | 0.95 | -    | -    | 0.037  | _     | _     |

| e1   | 1.90 | _    | _    | 0.075  | _     | _     |

| L    | 0.45 | 0.30 | 0.60 | 0.018  | 0.012 | 0.024 |

| Q    | 4°   | 0°   | 8°   | 4°     | 0°    | 8°    |

| N    | 6    |      |      | 6      |       |       |

Note: Dimensions per JEDEC SOT/SOP product outline MO-178C variation AA

## Part numbering

| Table 10.                       | Ordering infor                                                  | mation scheme                            | •                    |    |    |   |   |

|---------------------------------|-----------------------------------------------------------------|------------------------------------------|----------------------|----|----|---|---|

| Example:                        | •                                                               |                                          | STM67xx              | ĻŢ | WY | 6 | Ę |

| Device Type                     | <b>)</b>                                                        |                                          |                      |    |    |   |   |

| STM67xx                         |                                                                 |                                          |                      |    |    |   |   |

| Reset Thres                     | sholds (V <sub>RST1</sub> and<br>8/19/20/77/78 (V <sub>RS</sub> | V <sub>RST2</sub> ) for V <sub>CC1</sub> | and V <sub>CC2</sub> |    |    |   |   |

| Suffix                          | V <sub>RST1</sub>                                               | V <sub>RST2</sub>                        |                      |    |    |   |   |

| LT                              | 4.625                                                           | 3.075                                    |                      |    |    |   |   |

| MS                              | 4.375                                                           | 2.925                                    |                      |    |    |   |   |

| MR                              | 4.375                                                           | 2.625                                    |                      |    |    |   |   |

| TZ <sup>(1)</sup>               | 3.075                                                           | 2.313                                    |                      |    |    |   |   |

| $TW^{(1)}$                      | 3.075                                                           | 1.665                                    |                      |    |    |   |   |

| TI                              | 3.075                                                           | 1.388                                    |                      |    |    |   |   |

| TG <sup>(1)</sup>               | 3.075                                                           | 1.110                                    |                      |    |    |   |   |

| TK                              | 3.075                                                           | 0.925                                    |                      |    |    |   |   |

| TE                              | 3.075                                                           | 0.833                                    |                      |    |    |   |   |

| SY <sup>(1)</sup>               | 2.925                                                           | 2.188                                    |                      |    |    |   |   |

| SV <sup>(1)</sup>               | 2.925                                                           | 1.575                                    |                      |    |    |   |   |

| SH                              | 2.925                                                           | 1.313                                    |                      |    |    |   |   |

| SF <sup>(1)</sup>               | 2.925                                                           | 1.050                                    |                      |    |    |   |   |

| SJ                              | 2.925                                                           | 0.875                                    |                      |    |    |   |   |

| SD                              | 2.925                                                           | 0.788                                    |                      |    |    |   |   |

| YV                              | 2.188                                                           | 1.575                                    |                      |    |    |   |   |

| ΥH                              | 2.188                                                           | 1.313                                    |                      |    |    |   |   |

| YF                              | 2.188                                                           | 1.050                                    |                      |    |    |   |   |

| YJ                              | 2.188                                                           | 0.875                                    |                      |    |    |   |   |

| YD                              | 2.188                                                           | 0.788                                    |                      |    |    |   |   |

| VH                              | 1.575                                                           | 1.313                                    |                      |    |    |   |   |

| VF                              | 1.575                                                           | 1.050                                    |                      |    |    |   |   |

| VJ                              | 1.575                                                           | 0.875                                    |                      |    |    |   |   |

| VD                              | 1.575                                                           | 0.788                                    |                      |    |    |   |   |

|                                 | (V <sub>RST1</sub> only)                                        |                                          |                      |    |    |   |   |

| L–                              | 4.625                                                           | _                                        |                      |    |    |   |   |

| T–                              | 3.075                                                           | _                                        |                      |    |    |   |   |

| S-                              | 2.925                                                           | _                                        |                      |    |    |   |   |

| Y–                              | 2.188                                                           | _                                        |                      |    |    |   |   |

| V–                              | 1.575                                                           | _                                        |                      |    |    |   |   |

| R-                              | 2.625                                                           | _                                        |                      |    |    |   |   |

| Z-                              | 2.313                                                           | _                                        |                      |    |    |   |   |

| Package                         |                                                                 |                                          |                      |    |    |   |   |

| WY = SOT23                      | 3-5                                                             |                                          |                      |    |    |   |   |

| WB = SOT23                      |                                                                 |                                          |                      |    |    |   |   |

|                                 |                                                                 |                                          |                      |    |    |   |   |

| Temperature Range               |                                                                 |                                          |                      |    |    |   |   |

| 6 = -40 to 85°C                 |                                                                 |                                          |                      |    |    |   |   |

|                                 |                                                                 |                                          |                      |    |    |   |   |

| Shipping Method                 |                                                                 |                                          |                      |    |    |   |   |

|                                 | CK Package, Tubes                                               | 3                                        |                      |    |    |   | , |

| E - ECOPACK Package Tane & Reel |                                                                 |                                          |                      |    |    |   |   |

<sup>1.</sup> These are standard versions and are typically held in stock. A non-standard version may require a higher minimum volumes, and/or longer delivery times. For other options, or for more information on any aspect of this device, please contact the ST Sales Office nearest you

577

F = ECOPACK Package, Tape & Reel

# **Revision history**

Table 11. Document revision history

| Date        | Version | Revision details                                                                                                                                                |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 18-Oct-2004 | 1.0     | First draft                                                                                                                                                     |  |  |

| 25-Oct-2004 | 1.1     | Descriptive text, sales types (Table 10)                                                                                                                        |  |  |

| 14-Jan-2005 | 1.2     | Update characteristics, pin functions (Table 2)                                                                                                                 |  |  |

| 09-Feb-2005 | 1.3     | Update characteristics (Figure 9; Table 3)                                                                                                                      |  |  |

| 08-Apr-2005 | 1.4     | Update characteristics and mechanical dimensions; add table ( <i>Figure 9, 10, 27, 28, 29</i> ; <i>Table 4, 6, 10, 8, 9</i> )                                   |  |  |

| 28-Jul-2005 | 1.5     | Update characteristics, reset delay (Figure 10, 27; Table 4, 6, 7, 10)                                                                                          |  |  |

| 13-Sep-2005 | 2.0     | Add operating characteristics; update timings, document status, Lead-free text (Figure Figure 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 26, 27; Table 10) |  |  |

| 07-Oct-2005 | 3.0     | Marked STM6779/6780 as availability request parts (Table 1, 10)                                                                                                 |  |  |

| 07-Feb-2007 | 4.0     | Update STM6779/6780 availability (cover page, Table 1, 10)                                                                                                      |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com