## 3.3V DIFFERENTIAL LVPECL-to-LVTTL TRANSLATOR

Precision Edge™

SY89321L

### FEATURES

- 3.3V power supply

- 1.9ns typical propagation delay

- 275MHz  $f_{MAX}$  (clock bit stream, not pseudo-random)

- Differential LVPECL inputs

- 24mA LVTTL outputs

- Flow-through pinouts

- Internal input resistors: pulldown on IN, pulldown and pullup on /IN

- Q output will default LOW with inputs open

- $V_{BB}$  output

- Available in ultra-small 8-pin MLF™ (2mm x 2mm) package

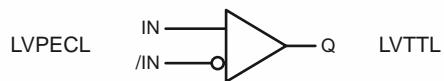

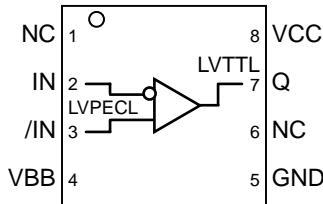

### BLOCK DIAGRAM

### DESCRIPTION

The SY89321L is a differential LVPECL-to-LVTTL translator requiring only a single +3.3V power. Because LVPECL (Low Voltage Positive ECL) levels are used, only +3.3V and ground are required. The SY89321L is functionally equivalent to the SY100EPT21L, but in an ultra-small 8-lead MLF™ package that features a 70% smaller footprint. This ultra-small package and low skew single gate design make the SY89321L ideal for applications that require the translation of a clock or data signal where minimal space, low power and low cost are critical.

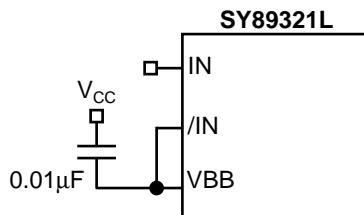

$V_{BB}$  allows a differential, single-ended, or AC-coupled interface to the device. If used, the  $V_{BB}$  output should be bypassed to  $V_{CC}$  with  $0.01\mu F$  capacitor.

Under open input conditions, the /IN will be biased at a  $V_{CC}/2$  voltage level and the IN input will be pulled to ground. This condition will force the Q output low to provide added stability.

The SY89321L is compatible with positive ECL 100k logic levels.

## PACKAGE/ORDERING INFORMATION

**8-Pin MLF™**

**Ultra-Small Outline (2mm x 2mm)**

## Ordering Information

| Part Number                 | Package Type | Operating Range | Package Marking |

|-----------------------------|--------------|-----------------|-----------------|

| SY89321LMITR <sup>(1)</sup> | MLF-8        | Industrial      | 321             |

**Note 1.** Tape and Reel.

## PIN DESCRIPTION

| Pin Number | Pin Name         | Type                     | Pin Function                                                                                                                                                                                                                                    |

|------------|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,6        | NC               |                          | No connection.                                                                                                                                                                                                                                  |

| 2          | IN               | 100K LVPECL Input        | Differential PECL Input: Internal 75kΩ pull-down resistor. If left open, pin defaults LOW. Q output will be LOW. See “ <i>Input Interface Applications</i> ” section for single-ended inputs.                                                   |

| 3          | /IN              | 100K LVPECL Input        | Differential PECL Input: Internal 75kΩ pull-up and pull-down resistors. If left floating, pin defaults to $V_{CC}/2$ . When not used, this input can be left open. See “ <i>Input Interface Applications</i> ” section for single-ended inputs. |

| 4          | VBB              | Reference Voltage Output | Bias Reference Voltage: $V_{CC}-1.3V$ . Used as reference voltage for single-ended inputs or AC-coupling to the IN, /IN inputs. Limit sink / source $\leq 0.5mA$ .                                                                              |

| 5          | GND, Exposed Pad | Ground                   | GND and Exposed pad must be tied to ground plane.                                                                                                                                                                                               |

| 7          | Q                | LVTTL Output             | Single-ended LVTTL Output: Defaults to LOW if IN inputs left open.                                                                                                                                                                              |

| 8          | VCC              | Positive Power Supply    | Positive Power Supply: Bypass with $0.1\mu F//0.01\mu F$ low ESR capacitors.                                                                                                                                                                    |

**Absolute Maximum Ratings (Note 1)**

|                                                   |                   |

|---------------------------------------------------|-------------------|

| Supply Voltage ( $V_{CC}$ ) .....                 | -0.5V to +3.8V    |

| Input Voltage ( $V_{IN}$ ) .....                  | -0.5V to $V_{CC}$ |

| LVTT Output Current ( $I_{OUT}$ )                 |                   |

| Continuous .....                                  | 50mA              |

| Surge .....                                       | 100mA             |

| Current ( $V_{BB}$ )                              |                   |

| Source or sink current on $V_{BB}$ , Note 3 ..... | $\pm 1.5$ mA      |

| Lead Temperature (soldering, 10 sec.) .....       | +220°C            |

| Storage Temperature ( $T_S$ ) .....               | -65°C to +150°C   |

**Operating Ratings (Note 2)**

|                                     |                |

|-------------------------------------|----------------|

| Supply Voltage ( $V_{CC}$ ) .....   | 3.0V to 3.6V   |

| Ambient Temperature ( $T_A$ ) ..... | -40°C to +85°C |

| Package Thermal Resistance, Note 4  |                |

| MLF™ ( $\theta_{JA}$ )              |                |

| Still-Air .....                     | 93°C/W         |

| 500lpm .....                        | 87°C/W         |

| MLF™ ( $\Psi_{JB}$ )                |                |

| Junction-to-Board .....             | 60°C/W         |

**LVTTL DC ELECTRICAL CHARACTERISTICS** $V_{CC} = +3.3V \pm 10\%$

| Symbol   | Parameter                    | Condition               | Min | Typ | Max  | Units |

|----------|------------------------------|-------------------------|-----|-----|------|-------|

| $I_{OS}$ | Output Short Circuit Current | $V_{OUT} = 0V$ , Note 5 | -80 | —   | -275 | mA    |

| $I_{CC}$ | Power Supply Current         |                         | —   | 14  | 20   | mA    |

| $V_{OH}$ | Output HIGH Voltage          | $I_{OH} = -3.0$ mA      | 2.0 | —   | —    | V     |

| $V_{OL}$ | Output LOW Voltage           | $I_{OL} = 24$ mA        | —   | —   | 0.5  | V     |

**LVPECL DC ELECTRICAL CHARACTERISTICS** $V_{CC} = +3.3V \pm 10\%$ ;  $T_A = -40^\circ C$  to  $+85^\circ C$  unless otherwise noted.

| Symbol   | Parameter             | Condition | Min            | Typ           | Max            | Units   |

|----------|-----------------------|-----------|----------------|---------------|----------------|---------|

| $V_{IH}$ | Input HIGH Voltage    |           | $V_{CC}-1.165$ | —             | $V_{CC}-0.880$ | V       |

| $V_{IL}$ | Input LOW Voltage     |           | $V_{CC}-1.810$ | —             | $V_{CC}-1.475$ | V       |

| $V_{BB}$ | Bias Voltage          |           | $V_{CC}-1.38$  | $V_{CC}-1.32$ | $V_{CC}-1.26$  | V       |

| $I_{IH}$ | Input HIGH Current    |           | —              | —             | 150            | $\mu A$ |

| $I_{IL}$ | Input LOW Current IN  |           | 0.5            | —             | —              | $\mu A$ |

|          | Input LOW Current /IN |           | -300           | —             | —              | $\mu A$ |

**Note 1.** Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

**Note 2.** The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

**Note 3.** Due to the limited drive capability use for input of the same package only.

**Note 4.** Package thermal resistance assumes exposed pad is soldered (or equivalent) to the devices most negative potential (GND) on the PCB.

**Note 5.** Max. limit only applicable for short durations, not for continuous operation!

## AC ELECTRICAL CHARACTERISTICS

$V_{CC} = +3.3V \pm 10\%$ ;  $C_L = 20pF$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$  unless otherwise noted.

| Symbol         | Parameter                               | Condition                           | Min | Typ | Max      | Units                      |

|----------------|-----------------------------------------|-------------------------------------|-----|-----|----------|----------------------------|

| $f_{MAX}$      | Maximum Input Frequency                 | <b>Note 6</b>                       | 275 | —   | —        | MHz                        |

| $t_{pd}$       | Propagation Delay                       |                                     | 1.5 | 1.9 | 2.5      | ns                         |

| $t_{skpp}$     | Part-to-Part Skew                       | $V_{IN} \geq 100mV$ , <b>Note 7</b> | —   | —   | 0.5      | ns                         |

| $V_{CMR}$      | Common Mode Range                       |                                     | 1.2 | —   | $V_{CC}$ | V                          |

| $V_{PP}$       | Minimum Peak-to-Peak Input              | <b>Note 8</b>                       | 100 | —   | —        | mV                         |

| $t_r$<br>$t_f$ | Output Rise/Fall Time<br>(1.0V to 2.0V) |                                     | 0.5 | —   | 1.0      | ns                         |

| $t_{JITTER}$   | Cycle-to-cycle (rms)                    | <b>Note 9</b>                       |     |     | 2        | $\text{ps}_{\text{rms}}$   |

|                | Total jitter (pk-pk)                    | <b>Note 10</b>                      |     |     | 15       | $\text{ps}_{\text{pk-pk}}$ |

**Note 6.** The  $f_{MAX}$  value is specified as the minimum guaranteed maximum frequency (While maintaining TTL swing of 0.8V to 2.0V). Actual operational maximum frequency may be greater.

**Note 7.** Part-to-Part Skew considering HIGH-to-HIGH transitions at common  $V_{CC}$  level.

**Note 8.**  $V_{PP}(\text{min})$  is the minimum input swing for which AC parameters are guaranteed.

**Note 9.** Cycle-to-cycle jitter definition: The variation of periods between adjacent cycles,  $T_n - T_{n-1}$ , where T is the time between rising edges of the output signal.

**Note 10.** Total jitter definition: with an ideal clock input of frequency  $\leq f_{MAX}$ , no more than one output edge in  $10^{12}$  output edge will deviate by more than the specified peak-to-peak jitter value.

## INPUT INTERFACE APPLICATIONS

Single-Ended Input

(Terminating unused input)

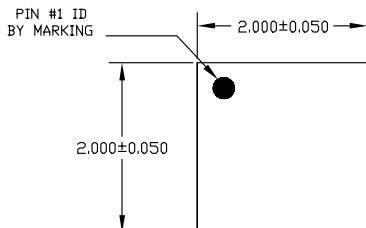

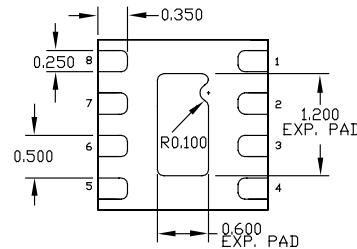

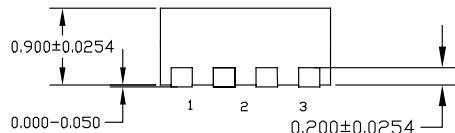

## 8 LEAD ULTRA-SMALL EPAD-MicroLeadFrame™ (MLF-8)

TOP VIEW

BOTTOM VIEW

SIDE VIEW

NOTE:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. MAX. PACKAGE WARPAGE IS 0.05 mm.

3. MAXIMUM ALLOWABLE BURRS IS 0.076 mm IN ALL DIRECTIONS.

4. PIN #1 ID ON TOP WILL BE LASER/INK MARKED.

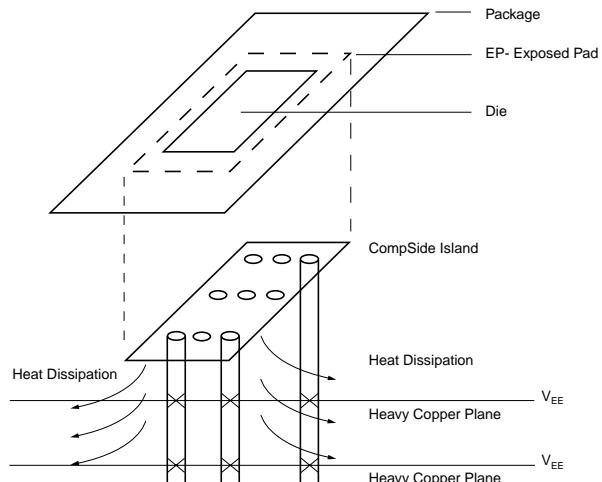

## PCB Thermal Consideration for 8-Pin MLF™ Package

## Package Notes:

Note 1. Package meets Level 2 qualification.

Note 2. All parts are dry-packaged before shipment.

Note 3. Exposed pads must be soldered to a ground for proper thermal management.

**MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA**

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB <http://www.micrel.com>

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.