#### 查询T7264供应商

Data Sheet April 1998

# 捷多邦,专业PCB打样工厂,24小时加急出货

microelectronics group

### Lucent Technologies Bell Labs Innovations

# T7264 U-Interface 2B1Q Transceiver

#### Features

- U-interface 2B1Q transceiver

- Range over 18 kft on 26 AWG

- ISDN basic-rate 2B+D

- Full-duplex, 2-wire operation

- 2B1Q four-level line code

- Conforms to ANSI North American Standard T1.601-1992

- Supports NT quiet mode and insertion loss test mode for maintenance

- K2 interface

- 2B+D data

- 512 kbits/s TDM interface

- Frame and superframe markers

- Embedded operations channel (eoc)

- U-interface M bits and crc results

- Device control and status

- Other

- Single +5 V (±5%) supply

- -40 °C to +85 °C

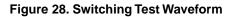

- 44-pin PLCC

- Power consumption

- Operating 275 mW typical

- Idle mode 30 mW typical

- Analog front end

- On-chip line driver for 2.5 V pulses

- On-chip balance network

- Sigma-delta A/D converter

- Internal 15.36 MHz crystal oscillator

- Supports 15.36 MHz external clock input

- Digital signal processor

- Digital timing recovery (pull range ±250 ppm)

- Echo cancellation (linear and nonlinear)

- Accommodates distortion from bridged taps

- Scrambling/descrambling

- crc calculations

- Selectable LT or NT operation

- Start-up sequencing with timers

- Activation/deactivation support

- Cold start in 3.5 seconds (typical)

- Warm start in 200 ms (typical)

- U-frame formatting and decoding

### Description

The Lucent Technologies Microelectronics Group T7264 U-Interface 2B1Q Transceiver integrated circuit provides full-duplex, basic-rate (2B+D) integrated services digital network (ISDN) communications on a 2-wire digital subscriber loop at either the LT or NT and conforms to the ANSI North American Standard T1.601-1992. The single +5 V CMOS device is packaged in a 44-pin plastic leaded chip carrier (PLCC).

# **Table of Contents**

### Contents

## Page Contents

| Page |

|------|

|------|

| Features                                      | 1    |

|-----------------------------------------------|------|

|                                               |      |

| Description                                   |      |

| Pin Information                               | 3    |

| Functional Overview                           | 6    |

| Device laterface and Ocean atting             |      |

| Device Interface and Connections              |      |

| Analog Device Interface                       | 7    |

| Power Supply Connections                      | Q    |

|                                               | 0    |

| Clock Operation                               | 8    |

| Reset Operation                               | 8    |

| Reset Sequences and Clock Synchronization     | õ    |

| Reset Sequences and Clock Synchionization     | 0    |

| Reset Time                                    | 9    |

| Idle Mode                                     | . 10 |

| NT Maintenance                                |      |

|                                               |      |

| K2 Interface Description                      | 11   |

| K2 NT and LT Timing Sources                   | . 12 |

| K2 Bits Description                           | 12   |

|                                               | 13   |

| K2 Bit Levels                                 | 20   |

| U-Interface Description                       | 21   |

| K2 Functional Description                     | 22   |

|                                               | 22   |

| K2 Framing Bits                               | 23   |

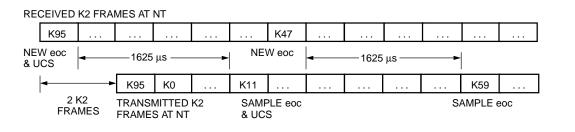

| K2 eoc and Loopback Response Timing           | 24   |

| K2 Device Status and Control Bits             | 25   |

|                                               |      |

| The adea Bit                                  | 26   |

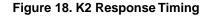

| The nebe, febe, rfebe, and ccrc Bits          | 27   |

| NT or LT Operation                            | 28   |

| Minimal Example                               | 20   |

| winimai Example                               | 29   |

| Activation and the K2 Interface               | 30   |

| Priority                                      | 31   |

| Applications                                  |      |

|                                               |      |

| Absolute Maximum Ratings                      | 34   |

| Handling Precautions                          | 34   |

| Recommended Operating Conditions              | 3/   |

| Flastelas I Okarastaristica                   |      |

| Electrical Characteristics                    |      |

| Loop-Range Performance Characteristics        | 36   |

| Timing Characteristics                        | 37   |

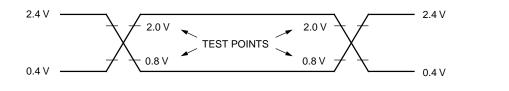

| Switching Test Input/Output Waveform          |      |

| Switching rest input/Output waveform          | 30   |

| Outline Diagram                               | 39   |

| Ordering Information                          | 39   |

| Appendix A. Questions and Answers             | 10   |

| Appendix A. Questions and Answers             | 40   |

| Introduction                                  |      |

| U-Interface                                   | 40   |

| K2 Interface                                  |      |

|                                               |      |

| Miscellaneous                                 | 49   |

| Appendix B. Differences Between the T-7264ML, |      |

| T-7264ML2 and T-7264AML Devices               | 52   |

|                                               |      |

| Technology                                    |      |

| Standard                                      | 53   |

|                                               | -    |

#### List of Figures

| Figure 1. T7264 Simplified Block Diagram         | 1  |

|--------------------------------------------------|----|

| Figure 2. Pin Diagram                            |    |

| Figure 3. Quat Example                           |    |

| Figure 4. Line Interface and Protection          |    |

| Figure 5. Recommended Power Supply               |    |

| Connections                                      | 8  |

| Figure 6. RESET Waveform Normal Operation        | 9  |

| Figure 7. RESET Timing for Synchronized Clocks . | 9  |

| Figure 8. K2 Interface Timing                    | 11 |

|                                                  |    |

| Figure 9. K2 Octets<br>Figure 10. K2 Interface LT and NT | 12 |

|----------------------------------------------------------|----|

| Figure 11. K2 Interface Frame Format                     |    |

| Figure 12. U-Interface Frame and Superframe              |    |

| Figure 13. U-Interface Superframe Bit Groups             |    |

| Figure 14. K2 Octet Description                          |    |

| Figure 15. K2 Functional Description                     |    |

| Figure 16. K2-to-U Mapping                               | 23 |

| Figure 17. U-to-K2 Mapping                               |    |

| Figure 18. K2 Response Timing                            |    |

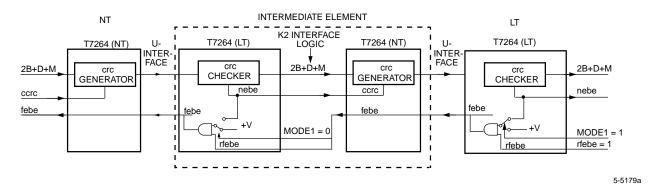

| Figure 19. T7264 nebe/febe/crc Block Diagram             | 28 |

| Figure 20. Use of rfebe in a Multilink Configuration     | 28 |

| Figure 21. State Sequence for DSL Transceiver            |    |

| Štart-Up                                                 | 32 |

| Figure 22. Loop Application                              |    |

| Figure 23. 2-Wire Terminal Application                   |    |

| Figure 24. Digital Pair Gain Application                 |    |

| Figure 25. Timing Diagram Referenced to F                |    |

| Figure 26. Timing Diagram Referenced to C                |    |

| Figure 27. RESET Timing Diagram                          |    |

| Figure 28. Switching Test Waveform                       |    |

|                                                          |    |

#### List of Tables

| Table 1. Pin Functions                               | 3    |

|------------------------------------------------------|------|

| Table 2. Pin Descriptions                            | 4    |

| Table 3. Clock Configuration                         | 6    |

| Table 4. K2 Interface Serial Data Bit Map            | 13   |

| Table 5. B1, B2, D, and S1 Octets (Overview)         | 15   |

| Table 6. B1, B2, D, and S1 Octets (Functions)        |      |

| Table 7. UM1 and UM2 Octets-eoc Bits (Overview)      | 16   |

| Table 8. UM1 and UM2 Octets-eoc Bits (Functions)     |      |

| Table 9. UM2 and UM3 Octet—UCS Bits (Overview)       |      |

| Table 10. UM2 and UM3 Octet—UCS Bits (Functions)     | 17   |

| Table 11. DS Octet (Overview)—Device Status          |      |

| Table 12. DS Octet (Functions)—Device Status         |      |

| Table 13. DC Octet (Overview)                        | 19   |

| Table 14. DC Octet (Functions)                       | 19   |

| Table 15. K2 Data Out (DO) Bit Levels                | 20   |

| Table 16. K2 Device Control (DC) Bit Levels          | 20   |

| Table 17. U-Interface Bit Assignment                 |      |

| Table 18. DC Octet Description (Control)             |      |

| Table 19. DS Octet Description (Status)              | 25   |

| Table 20. adea, Idea, and dea Function               | 26   |

| Table 21. MODE0 Pin Functionality                    | 28   |

| Table 22. Minimal Implementation                     |      |

| Table 23. Definitions of Signals During Start-Up     |      |

| Table 24. Power Consumption                          | 35   |

| Table 25. Performance Ratings                        | 35   |

| Table 26. Crystal Characteristics: Fundamental       |      |

| Mode Crystal                                         | 35   |

| Table 27. Internal PLL Characteristics               | 36   |

| Table 28. Digital dc Characteristics (Over Operating |      |

| Ranges)                                              | 36   |

| Table 29. Clock Timing                               | 37   |

| Table 30. MTC Requirements and Characteristics       |      |

| (LT Mode)                                            | 38   |

| Table 31. RESET Timing                               | . 38 |

### **Pin Information**

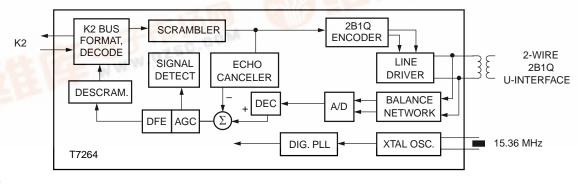

The U transceiver consists of a single chip composed of an analog front end (which performs the line interfacing and data conversion functions) and a digital signal processor (which performs the algorithm-specific signal processing, control, and access functions).

5-5804(F)

Notes:

C = crystal oscillator pins.

A = analog pins.

| Table 1. | Pin | Functio | ons |

|----------|-----|---------|-----|

|----------|-----|---------|-----|

| Device Pin Function                                                     | Туре    | Number of Pins |

|-------------------------------------------------------------------------|---------|----------------|

| +5 V Power & Ground (VDD, GND)                                          | Power   | 14             |

| Analog Line Interface (HP, HN, LOP, LON)                                | Analog  | 4              |

| Voltage Reference (VRP, VRN, VCM)                                       | Analog  | 3              |

| Receiver to A/D Converter (SDINN, SDINP)                                | Analog  | 2              |

| Clock Related (X1, X2, CKOUT, CKSEL, MCLK, RCLKEN)                      | Digital | 6              |

| K2 Interface Connection (MTC, C, DI, DO, F)                             | Digital | 5              |

| Device Status & Control (FFC, HIGHZ, ILOSS, MODE0, MODE1, OSYNC, RESET) | Digital | 7              |

| Do Not Connect                                                          | NC      | 3              |

| Total                                                                   |         | 44             |

Lucent Technologies Inc.

# Pin Information (continued)

### Table 2. Pin Descriptions

| Pin               | Symbol    | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1                 | DI        | Ι    | <b>K2 Transmit Data Input.</b> Serial data input passing transmit data across K2 interface at 512 kbits/s. Latched on falling edge of C clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2                 | MTC       | Ι    | <b>Master Timing Clock.</b> 8 kHz clock input. In LT mode (MODE0 = 1), all clocks except CKOUT in the 15.36 MHz and 7.68 MHz modes are locked to this input clock. In the NT mode (MODE0 = 0), this input is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 3                 | С         | 0    | <b>512 kbits/s K2 Bit Clock Output.</b> Synchronized to F. Defines K2 bit period (rising edge to rising edge).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 4                 | DO        | 0    | <b>K2 Receive Data Output.</b> Serial data output passing receive data across K2 interface at 512 kbits/s. Changes on the rising edge of C clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 5                 | F         | 0    | <b>8 kHz Clock Output.</b> Defines K2 frame (rising edge to rising edge). In LT mode (MODE0 = 1), this clock is locked to MTC at 0° phase shift with $\pm$ 65 ns of jitter (for jitter-free MTC). In NT mode (MODE0 = 0), this clock is derived from the U-interface signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 6, 17             | Vddd      | Р    | +5 V Supply for Digital Circuits. Internally connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 7                 | RESET     | Ι    | <b>Reset (Active-Low).</b> Asynchronous Schmitt trigger input. This pin maintains the transceiver in reset indefinitely without the need to access the K2 interface. It must be held low for three consecutive F clock periods for active or idle mode or 1.5 ms after power on. After power-on reset or idle mode reset, an additional 1.0 ms is required before the device is fully functional. RESET overrides all other transceiver control signals, halts loop transmission, clears the transceiver adaptive filter coefficients, and resets the phase-locked loop. After a reset, the next activation is a cold start. Unlike afrst (software reset via the K2 interface), when this pin is held low, synchronization is lost between F and MTC (LT). After this pin goes high, F and MTC regain synchronization. All output clocks remain functional during reset. |  |  |  |  |  |

| 8                 | FFC       | I    | <b>Freeze Frequency Control (Active-Low).</b> Asynchronous input. Freeze the clock frequency control (i.e., the internal state variables of the timing recovery remain constant). This control is operative in both LT and NT modes. This pin is latched on the rising edge of every RCLKEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 9                 | ILOSS     | I    | <b>Insertion Loss Test (Active-Low).</b> NT ONLY. When enabled, the transmitter continuously transmits the sequence SN1. The receiver remains reset. The transceiver performs a reset when this pin returns to its inactive state. ILOSS is latched on the rising edge of F. Leave this pin unconnected or tied to VDD in LT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 10, 11            | MODE[0:1] | I    | Mode 0 and 1. Two-pin field selecting chip mode:         MODE0       Action         0       Configure for chip being used on the NT end of loop.         1       Configure for chip being used on the LT end of loop.         MODE1       Action         0       Disables autoreporting of nebe to febe.         1       Enables autoreporting of nebe to febe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 12, 22,<br>27, 44 | GND⊳      | Р    | Ground Supply for Digital Circuits. Internally connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

# Pin Information (continued)

### Table 2. Pin Descriptions (continued)

| Pin           | Symbol | Туре | Name/Function                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|---------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 13,<br>14, 15 | NC     |      | <b>No Connect.</b> These pins are connected to internal nodes of the device. Make no connection to them.                                                                                                                                                                                    |  |  |  |  |  |

| 16            | OSYNC  | 0    | <b>Out of Sync (Active-Low).</b> Indicates that framing on the loop signal has not been ac-<br>quired (or has been lost). Equivalent to the K2 interface oof bit in the DS octet. Can sink<br>or source 1.6 mA to drive a low-current external LED. Clocked out on the rising edge<br>of C. |  |  |  |  |  |

| 18            | Vddo   | P/I  | <b>+5 V Supply for the Crystal Oscillator.</b> Ground when driving MCLK with an external 15.36 MHz clock.                                                                                                                                                                                   |  |  |  |  |  |

| 19            | GNDo   | Р    | Ground Supply for Oscillator.                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 20            | X1     | Ι    | Connection #1 for a 15.36 MHz Crystal.                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 21            | X2     | I    | Connection #2 for a 15.36 MHz Crystal.                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 23            | CKOUT  | 0    | Clock Output. See Table 3.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 24            | MCLK   | I    | Master Clock. See Table 3.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 25            | CKSEL  | I    | Clock Select. See Table 3.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 26            | HIGHZ  | I    | High Impedance (Active-Low). Causes all digital outputs to become 3-stated.                                                                                                                                                                                                                 |  |  |  |  |  |

| 28            | VCM    | _    | Common-Mode Voltage Reference for the Analog Circuits. Connect via a 0.1 $\mu$ F capacitor to GND <sub>A</sub> as close to this pin and pin 34 as possible.                                                                                                                                 |  |  |  |  |  |

| 29            | VRP    | _    | Positive Voltage Reference for the Analog Circuits. Connect via a 0.1 $\mu$ F capacitor o GND <sub>A</sub> as close to this pin and pin 34 as possible.                                                                                                                                     |  |  |  |  |  |

| 30            | VRN    |      | Negative Voltage Reference for the Analog Circuits. Connect via a 0.1 $\mu$ F capacitor to GNDA as close to this pin and pin 34 as possible.                                                                                                                                                |  |  |  |  |  |

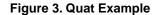

| 31            | HN     | Ι    | Hybrid Network Connection, Negative Side. Connect directly to the negative side of the transformer.                                                                                                                                                                                         |  |  |  |  |  |

| 32            | LOP    | 0    | Line Driver Output Terminal, Positive Side. Connect to the positive side of the transformer.                                                                                                                                                                                                |  |  |  |  |  |

| 33,<br>39, 42 | Vdda   | Ρ    | +5 V Supply for Analog Circuits.                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 34,<br>40, 41 | GNDA   | Ρ    | Ground Supply for Analog Circuits.                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 35            | LON    | 0    | <b>Line Driver Output Terminal, Negative Side.</b> Connect to the negative side of the transformer.                                                                                                                                                                                         |  |  |  |  |  |

| 36            | HP     | Ι    | Hybrid Network Connection, Positive Side. Connect directly to the positive side of the transformer.                                                                                                                                                                                         |  |  |  |  |  |

| 37            | SDINN  | I    | Sigma-Delta A/D Converter Input, Negative Side. Connect via an 820 pF $\pm$ 5% capacitor to SDNIP.                                                                                                                                                                                          |  |  |  |  |  |

| 38            | SDINP  | I    | Sigma-Delta A/D Converter Input, Positive Side. Connect via an 820 pF $\pm5\%$ capacitor to SDNIN.                                                                                                                                                                                          |  |  |  |  |  |

| 43            | RCLKEN | 0    | 80 kHz Receive Baud Clock. Defines receive baud period (rising edge to rising edge).                                                                                                                                                                                                        |  |  |  |  |  |

### Pin Information (continued)

#### **Table 3. Clock Configuration**

| Vddo       | MCLK                   | CKSEL  | CKOUT*                               |

|------------|------------------------|--------|--------------------------------------|

| +5 V       | 0                      | 0      | 15.36 MHz (free-running)             |

| +5 V       | 0                      | 1      | 10.24 MHz (phase-locked)             |

| +5 V       | 1                      | 0      | 7.68 MHz (free-running)              |

| +5 V       | 1                      | 1      | 3-stated (default)                   |

| 0 V<br>0 V | 15.36 MHz<br>15.36 MHz | 0<br>1 | 15.36 MHz (free-running)<br>3-stated |

\* The 10.24 MHz CKOUT is high for one-half of a 15.36 MHz period and low for one 15.36 MHz period. To compensate for the difference between the phase-locked and free-run frequencies, one-half 15.36 MHz clock periods are occasionally either removed from or added to the low time of the 10.24 MHz period.

### **Functional Overview**

5-5162F

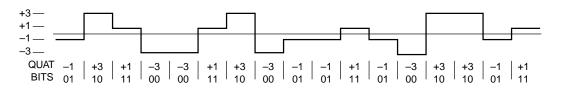

The T7264 chip conforms to the T1.601 ANSI North American 1992 Standard for 2B1Q line encoding. The 2B1Q line code provides a four-level pulse amplitude modulation code with no redundancy. Data is grouped into pairs of bits for conversion to quaternary (quat) symbols. Figure 3 above shows an example of this coding method.

The analog front end provides the 2B1Q line coder (D/A conversion), pulse shaper, line driver, first-order line balance network, crystal oscillator clock generation, and sigma-delta A/D conversion. The line driver provides pulses which allow the 2.5 V template of the T1.601 specification to be met when connected to the proper transformer and interface circuitry. The A/D converter is implemented using a double-loop, sigma-delta modulator.

A crystal oscillator provides the 15.36 MHz master clock for the chip. An on-chip, digital phase-locked loop provides the ability to synchronize the chip clock to the system clock in the LT or to the line clock in the NT. Provisions are made for using either an on-chip crystal oscillator with an external crystal, or using an external clock source.

The T7264 takes input at the K2 interface and formats this information for the U-interface through a scrambling algorithm and the addition of synchronization bits for U framing. This data is then transferred to the 2B1Q encoder for transmission over the U loop. Signals coming from the U loop are first passed through the sigmadelta A/D converter and then sent for extensive signal processing. The T7264 provides decimation of the sigma-delta output (DEC), linear and nonlinear echo cancellation, automatic gain control (AGC), signal detection, decision feedback equalization (DFE), timing recovery (TR), descrambling, line-code polarity detection, and rate adaption for output onto the K2 interface. The DFE circuit provides the functionality necessary for proper operation on subscriber loops with bridged taps.

### Functional Overview (continued)

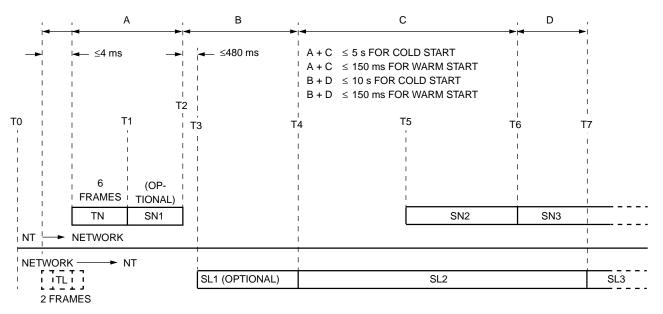

The device provides rapid cold start and warm start operation. From a cold start, the device is typically operational within 3.5 s. The device supports activation/ deactivation, and, when properly deactivated, it stores the adaptive filter coefficients such that upon the next activation request, a faster warm start is possible. A warm start typically requires 200 ms for the device to become operational.

The T7264 has an on-chip activation/deactivation state machine and timers, and automatically moves from state T0 to T7 (as specified in the T1.601 standard) during activation. This simplifies the implementation of the T1.601 (Appendix C) state table. The signals from the device control and status octets on the K2 interface provide the control necessary to complete the state table. The activation/deactivation process is controlled over the K2 interface.

The T7264 has a low-power mode which it automatically enters when it is in the idle state. The idle state occurs after deactivation, loss of sync on the U-interface, or releasing reset. In the low-power mode, power consumption is typically 30 mW.

### **Device Interface and Connections**

The T7264 transceiver allows systems to meet the loop-range requirements of ANSI Standard T1.601 when the transceiver is used with the proper peripheral circuitry. Devices achieve better than  $10^{-7}$  bit error rate over 18 kft of 26 AWG loop cable.

### **Analog Device Interface**

Proper line termination is required, utilizing appropriate interface components, to meet the 2.5 V pulse template. The output of the T7264 should first pass through a pair of 16.9  $\Omega$  resistors and into a 1.5:1 ratio transformer, such as the Lucent 2754H (or the short-lead version 2754H2). The output of the transformer is coupled through a 1.0  $\mu$ F capacitor, is passed through a pair of 16.9  $\Omega$  resistors, and then drives the 135  $\Omega$  line.

Surge protection circuitry is necessary on each side of the transformer when the U loop is external to a building. The protection between the 16.9  $\Omega$  resistors and the transformer should be a Lucent 521A surge protector or equivalent. A relay may be needed to disconnect the loop plant for local loopback testing. Figure 4 shows a recommended circuit for interfacing the T7264 to the line; however, the specific interface is system dependent.

Note: 3000 pF ± 1% capacitors from HP and HN to GNDA may improve operation of the tone decoder in the presence of interfering commonmode signals.

#### Figure 4. Line Interface and Protection

### **Device Interface and Connections**

(continued)

### **Power Supply Connections**

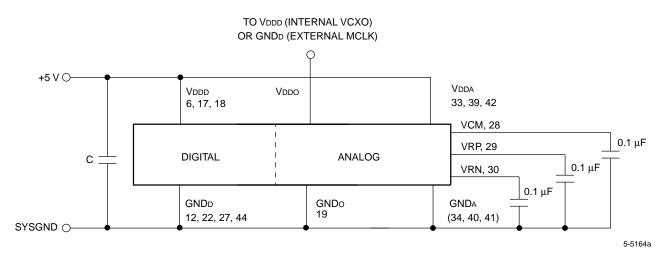

Figure 5 shows a recommended power supply connection. C is a 10  $\mu$ F capacitor. Each pair of power and ground pins should be decoupled with 0.1  $\mu$ F and 1.0  $\mu$ F capacitors. Each of the three leads (VCM, VRP, and VRN) associated with the voltage reference should be decoupled with 0.1  $\mu$ F capacitors. Place the capacitors as close as possible to the power or reference and ground pins which they decouple.

### **Clock Operation**

The master clock for the T7264 may either be internally generated by the on-chip crystal oscillator or supplied by the user via the MCLK pin. In the latter case, VDDO must be grounded. In the LT mode, an on-chip digital phase-locked loop phase locks the F clock to the externally supplied MTC clock, unless FFC is active-low. In NT mode, F synchronizes to the signal received from the LT through the U-interface. If the on-chip crystal oscillator is used, the crystal must conform to the requirements given in Table 26.

### **Reset Operation**

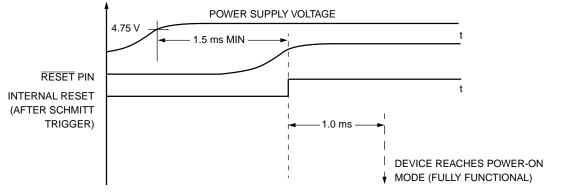

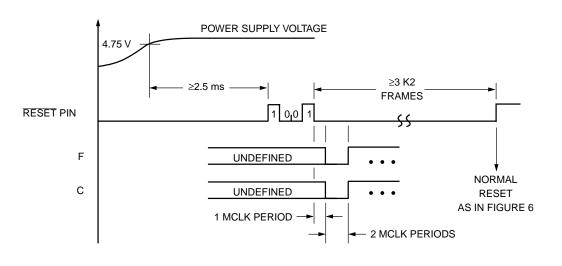

The T7264 can be reset via the K2 interface (issuing afrst for three consecutive K2 frames) or via hardware ( $\overline{\text{RESET}}$ ). The only difference between these two resets is that, in the LT mode, the timing recovery filter is reset

only by a hardware reset. The RESET pin can be used to hold the transceiver in reset indefinitely. If a hardware reset is used when the chip is being powered up, RESET must be held low for 1.5 ms; however, if the chip is already powered up, then holding RESET low for three K2 frames is sufficient.

The reset state is terminated, and the chip enters idle mode on the K2 frame following the end of the reset signal.

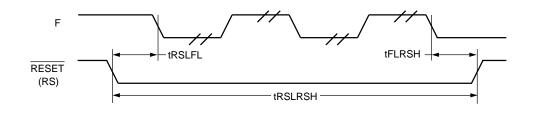

#### **Reset Sequences and Clock Synchronization**

In normal use, a power-on reset can be obtained by connecting a capacitor to the  $\overline{\text{RESET}}$  pin. The internal pull-up resistor, acting with an on-chip Schmitt trigger on this pin, can be used to reset the chip. In this case, the  $\overline{\text{RESET}}$  waveform is shown in Figure 6.

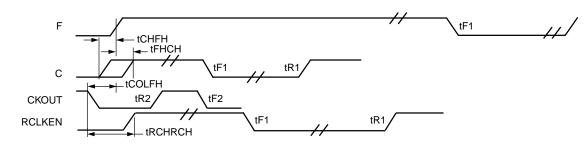

When using this reset procedure, the various clocks generated by the transceiver are not synchronized. However, during testing, it can be useful to initialize all the counters of the clock generator so that the various clocks generated by the transceiver can be synchronized to the test equipment. The RESET pin can accomplish this by applying the sequence shown in Figure 7. Furthermore, the **RESET** pin transitions should align with falling edges of MCLK. If the internal crystal oscillator is used, this can be accomplished by configuring CKOUT for 15.36 MHz and ensuring that RESET transitions align with the falling edge of CKOUT. The user should be aware, however, that if this clock synchronization reset sequence is used after a period of normal operation, the phase of the clocks generated by the T7264 (such as F, RCLKEN, C, CKOUT, etc.) may suddenly change as a result of the clock resynchronization.

**Figure 5. Recommended Power Supply Connections**

### Device Interface and Connections (continued)

#### **Reset Time**

Reset time depends on the conditions under which the chip is reset. There are three cases to consider:

- When the chip is initially powered on, the RESET pin must be held low (below 0.5 V) for 1.5 ms. This allows 1.0 ms for the oscillator start-up and 0.5 ms for the digital reset process. An additional 1.0 ms is needed to allow the analog circuitry to fully power up before the chip becomes fully functional.

- When the chip is in the idle mode, a software or hardware reset, applied for a minimum of three K2 frames, starts the reset process. As before, the analog circuitry requires an additional 1.0 ms before the chip becomes fully functional.

- If the chip is already fully powered up and functional, a software or hardware reset, applied for a minimum of three K2 frames, is sufficient to complete the reset process.

When the chip is in the reset state, the output of the line driver is at 0 V and the transmit data is also 0 V.

5-5165a

Figure 6. RESET Waveform Normal Operation

Figure 7. RESET Timing for Synchronized Clocks

5-5166a

# **Device Interface and Connections**

(continued)

### Idle Mode

A low-power idle mode is implemented on the T7264 to reduce the power consumption to typically 30 mW when it is not active. All internal coefficients are saved in this idle mode to reduce time for a subsequent start-up. There are three ways that idle mode can be entered:

- If the loop is operational, the local deactivation command (Idea) in the LT mode via the K2 interface causes the deactivation procedure specified in the ANSI standard. At the conclusion of the deactivation procedure, shutdown of the line driver and activation of the tone detector occurs. If no tone is detected within 48 ms, the idle mode is entered. This 48 ms window constitutes the RECEIVE RESET criteria in the ANSI standard.

- If a failure condition is encountered (e.g., the loop never comes up), a procedure similar to deactivation is followed. The only difference is the duration of the window, which is set internally by the type of failure condition.

- As long as either the afrst (via the K2 interface) or the RESET pin is active, the transceiver remains in the powerup reset state. At the cessation of the reset condition, the transceiver changes to the idle state.

There are four ways of bringing the device out of the idle mode:

- An initiate start-up procedure (istp) command is received via the K2 interface by the device.

- A reset (afrst or external RESET) command is received by the device.

- A tone is detected by the tone detector.

- A command to enter any of the test modes (loopback and insertion loss) is received by the device.

Internal timing ensures that the digital signal processor blocks do not change state during the idle mode-topowerup process. In addition, the start-up process has been designed to prevent glitches on the line as the driver powers up.

### **NT Maintenance**

ANSI T1.601-1992 defines NT quiet mode operation and an insertion loss measurement, and support for these is available from the T7264. Detection of the trigger signals is done by other hardware which notifies the system controller, and the system controller then signals the T7264 as needed to do the following:

- To enter the quiet mode, the chip is placed in reset.

- When an insertion loss measurement is requested, ILOSS (pin 9) is asserted low. This causes the transmitter to continuously send SN1 and places the receiver in reset. When the test is completed or terminated, ILOSS is asserted high and the chip is reset. Priority between RESET and ILOSS is described in the Priority section of this document (page 31).

## **K2 Interface Description**

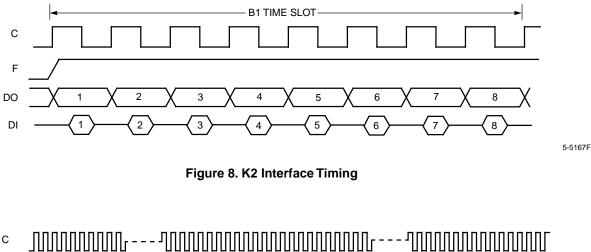

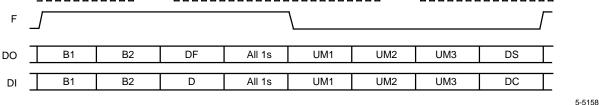

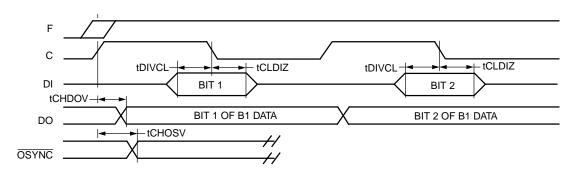

The K2 interface consists of five pins on the T7264: the data out (DO), data in (DI), data clock (C), K2 frame sync (F), and master timing clock (MTC). C is a 512 kHz output signal for clocking data into and out of the device with 1 bit per clock cycle. F is an 8 kHz signal indicating the beginning of a K2 frame. MTC is used in LT mode and must be an 8 kHz  $\pm$  32 ppm system clock to meet T1.601 requirements.

In LT mode, F is phase-locked to the MTC input through the on-chip digital phase-locked loop. Jitter in MTC is tracked by F at frequencies below 0.5 Hz. MTC jitter at frequencies higher than 0.5 Hz is attenuated by the phase-locked loop (PLL). In the NT mode, the F clock is derived from incoming data from the U loop. The first bit of a K2 frame begins simultaneously with the rising edge of F. Transitions on DO occur following the rising edge of C, and DI is latched on the falling edge of C. Figure 8 shows the relationship between the C, F, DO, and DI.

The K2 frame consists of eight octets for a total of 64 bits. These bits are transferred synchronously over a 512 kHz interface with a frame rate of 8 kHz or 125  $\mu$ s. The major purpose of the K2 interface is to provide 2B+D data transfer between other devices and the chip. In addition, there are framing bits (DF), U-interface maintenance and control bits (UM), and device control/status bits (DC/DS).

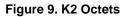

### **K2 NT and LT Timing Sources**

In LT applications, all devices typically derive their timing from the same MTC. Additional logic in the LT, such as a T7270, can provide concentration of multiple K2 interfaces onto a single higher-speed highway.

In a PBX application, the U-interface loops can be used as trunks. If more than one incoming U trunk is to be used, additional circuitry may be needed to provide elastic store, time-slot allocation, and master frame timing to synchronize the K2 interfaces received at each trunk onto a common interface.

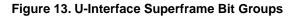

In NT1 applications, K2 frame timing is also derived from the received 2B1Q data on the U loop. A T7264 chip can be connected to an S/T-interface device (such as the T7252A) to form an NT1. Figure 10 shows the K2 interface connection in a CO application and NT1 application. For terminal applications, the derived K2 timing could be the source of all timing within the equipment (if only a single U-interface is needed).

Figure 10. K2 Interface LT and NT

### **K2 Bits Description**

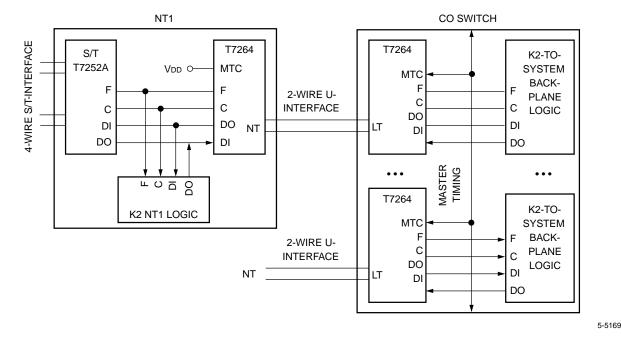

Table 4 summarizes the K2 interface bits which are common to all configurations. The K2 frame consists of eight octets of data. The first three octets contain the 18 bits of 2B+D data. Bits 5—8 of the third octet contain U frame and superframe timing (DF). Octet 4 (S1) is reserved for future use and should always be set to 1. Octets 5, 6, and 7 are directly mapped to the U-interface M (UM) maintenance bits which are transparent to the device, except the adea bit. Octet 8 is for device status (DS) and device control (DC). These bits must be manipulated according to the T1.601 standard to obtain proper system-level operation.

Figure 11 describes the four different K2 interface formats for DO and DI at the NT and LT. Tables 5—14 describe the position and meaning of the various bits on the K2 interface. Tables 15 and 16 show the active logic level for these bits, their value during reset/idle, and their value when the transceiver is operational.

#### Table 4. K2 Interface Serial Data Bit Map

Bits marked with 1 should always be set to a 1. Bits marked as Rxx are reserved by T1.601 and should be set to a 1.

| Time>  |       |       |       |       |       |       |               |               |       |

|--------|-------|-------|-------|-------|-------|-------|---------------|---------------|-------|

| Symbol | Octet | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6         | Bit 7         | Bit 8 |

| B1     | 1     | B11   | B12   | B13   | B14   | B15   | B16           | B17           | B18   |

| B2     | 2     | B21   | B22   | B23   | B24   | B25   | B26           | B27           | B28   |

| D      | 3     | D1    | D2    | 1     | 1     | 1     | 1             | 1             | 1     |

| DF     | 3     | D1    | D2    | 1     | 1     | RSF   | RF            | TSF           | TF    |

| S1     | 4     | 1     | 1     | 1     | 1     | 1     | 1             | 1             | 1     |

| UM1    | 5     | a1    | a2    | a3    | dm    | i1    | i2            | i3            | i4    |

| UM2    | 6     | i5    | i6    | i7    | i8    | act   | <b>R</b> 1, 5 | <b>R</b> 1, 6 | *     |

| UM3    | 7     | R2, 5 | *     | *     | *     | *     | <b>R</b> 6, 4 | *             | *     |

| DS     | 8     | nebe  | xact  | †     | 1     | oof   | 1             | rsksi         | 1     |

| DC     | 8     | ccrc  | istp  | lpbk  | afrst | ldea  | 1             | sksi          | хрсу  |

\* Items differ dependent upon NT or LT mode.

† Don't care.

5-5170

Figure 11. K2 Interface Frame Format

| Octet | Octet # | DO/DI | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 | Bit 8 |

|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| B1    | 1       | DO/DI | B11   | B12   | B13   | B14   | B15   | B16   | B17   | B18   |

| B2    | 2       | DO/DI | B21   | B22   | B23   | B24   | B25   | B26   | B27   | B28   |

| D     | 3       | DI    | D1    | D2    | 1     | 1     | 1     | 1     | 1     | 1     |

| DF    | 3       | DO    | D1    | D2    | 1     | 1     | RSF   | RF    | TSF   | TF    |

| S1    | 4       | DO/DI | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

### Table 6. B1, B2, D, and S1 Octets (Functions)

| Octet | Bit # | Symbol  | Name/Function                                                                                                                                                                                                                                                                                                                               |

|-------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1    | 1—8   | B11—B18 | <b>B1 Octet.</b> The B1 octet is used for transferring basic access channel B1. B11 is the first bit of the B1 octet sent or received.                                                                                                                                                                                                      |

| B2    | 1—8   | B21—B28 | <b>B2 Octet.</b> The B2 octet is used for transferring basic access channel B2. B21 is the first bit of the B2 octet sent or received.                                                                                                                                                                                                      |

| D     | 1—2   | D1, D2  | <b>D Octet.</b> The two D-channel bits are transmitted in the first 2 bits of the D octet. D1 is the first bit of the D pair sent or received.                                                                                                                                                                                              |

| DF    | 5     | RSF     | <ul> <li>Receive Superframing. 12.5% duty cycle at an 83.333 Hz rate (12 ms).</li> <li>0—Last 84 K2 frames of the superframe.</li> <li>0 to 1—Marks the first K2 frame of 2B+D data. Corresponds to the first 2B+D data of the U superframe.</li> <li>1—First 12 K2 frames and during reset state up to point T6 or T7.</li> </ul>          |

| DF    | 6     | RF      | <ul> <li>Receive Framing. 50% duty cycle at a 666.66 Hz rate (1.5 ms).</li> <li>0—Last six K2 frames of the U frame.</li> <li>0 to 1—Marks every 12th K2 frame of 2B+D data.</li> <li>Corresponds to the first 2B+D data of the U frame.</li> <li>1—First six K2 frames and during reset state up to point T6 or T7.</li> </ul>             |

| DF    | 7     | TSF     | <ul> <li>Transmit Superframing. 12.5% duty cycle at an 83.333 Hz rate (12 ms).</li> <li>0—Last 84 K2 frames of the superframe</li> <li>0 to 1—Marks the first K2 frame of 2B+D data.</li> <li>Corresponds to the first 2B+D data of the U superframe.</li> <li>1—First 12 K2 frames and during reset state up to point T6 or T7.</li> </ul> |

| DF    | 8     | TF      | <ul> <li>Transmit Framing. 50% duty cycle at a 666.66 Hz rate (1.5 ms).</li> <li>0—Last six K2 frames of the U frame.</li> <li>0 to 1—Marks every 12th K2 frame of 2B+D data.</li> <li>Corresponds to the first 2B+D data of the U frame.</li> <li>1—First six K2 frames and during reset state up to point T6 or T7.</li> </ul>            |

| S1    | 1—8   | S11—S18 | S1 Octet. All bits of the S1 octet are set to 1.                                                                                                                                                                                                                                                                                            |

#### Table 7. UM1 and UM2 Octets—eoc Bits (Overview)

| Octet | Octet # | DO/DI | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5          | Bit 6 | Bit 7 | Bit 8 |

|-------|---------|-------|-------|-------|-------|-------|----------------|-------|-------|-------|

| UM1   | 5       | DO/DI | a1    | a2    | a3    | dm    | i1             | i2    | i3    | i4    |

| UM2   | 6       | DO/DI | i5    | i6    | i7    | i8    | See next page. |       |       |       |

#### Table 8. UM1 and UM2 Octets—eoc Bits (Functions)

Additional details on eoc bits can be found in T1.601.

| Octet  | Bit #    | Symbol          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM1, 2 | 1—8, 1—4 | eoc             | <b>eoc Bits.</b> The eoc bits are passed transparently from the U-interface to the K2 interface and from the K2 to the U-interface. The transceiver maintains the eoc information at the K2 interface until a new block of eoc information is available.                                                                                                                                                                 |

| UM1    | 1—3      | a1—a3           | eoc Address.<br>000—NT address.<br>001—LT to NT intermediate address.<br>010—110—LT to NT, decrement address and pass on.<br>001—101—NT to LT, increment address and pass on.<br>111—Broadcast address.                                                                                                                                                                                                                  |

| UM1    | 4        | dm              | Data or Message Indicator.<br>0—Data.<br>1—Message.                                                                                                                                                                                                                                                                                                                                                                      |

| UM1, 2 | 5—8, 1—4 | i1—i4,<br>i5—i8 | Information. eoc channel message information.<br>01010000—Operate 2B+D loopback.<br>01010001—Operate B1 channel loopback.<br>01010010—Operate B2 channel loopback.<br>01010011—Request corrupt crc.<br>01010100—Notify of corrupted crc.<br>11111111—Return to normal.<br>00000000—Hold state.<br>10101010—Unable to comply.<br>Refer to T1.601 for codes which are reserved, nonstandard, or internal net-<br>work use. |

### Table 9. UM2 and UM3 Octet—UCS Bits (Overview)

| Octet | Octet # | DO/DI       | Bit 1              | Bit 2                            | Bit 3         | Bit 4         | Bit 5         | Bit 6         | Bit 7         | Bit 8  |

|-------|---------|-------------|--------------------|----------------------------------|---------------|---------------|---------------|---------------|---------------|--------|

| UM2   | 6       | DOLT/[DINT] | See previous page. |                                  |               |               | act           | <b>R</b> 1, 5 | <b>R</b> 1, 6 | ps1    |

| UM2   | 6       | DONT/[DILT] | See previous page. |                                  |               |               | act           | <b>R</b> 1, 5 | <b>R</b> 1, 6 | [a]dea |

| UM3   | 7       | DOLT/[DINT] | R2, 5              | R <sub>2,5</sub> [r]febe ps2 ntm |               |               | CSO           | <b>R</b> 6, 4 | sai           | nib    |

| UM3   | 7       | DONT/[DILT] | <b>R</b> 2, 5      | [r]febe                          | <b>R</b> 3, 4 | <b>R</b> 4, 4 | <b>R</b> 5, 4 | <b>R</b> 6, 4 | uoa           | aib    |

#### Table 10. UM2 and UM3 Octet—UCS Bits (Functions)

| Octet | Bit # | Symbol                    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM2   | 5     | act                       | Activation. Passed transparently from the K2 to the U-interface and from the U to the K2 except during a start-up when it is forced to a 0 on the K2.<br>0—Pending activation.<br>1—Ready to transmit information.                                                                                                                                                                                                                                       |

| UM2   | 6, 7  | <b>R</b> x, у             | <b>Reserved Bits.</b> Passed transparently from the K2 to the U-interface and from the U to the K2. Transmit should always be set to a 1.                                                                                                                                                                                                                                                                                                                |

| UM2   | 8     | ps1<br>(DOLT/<br>DINT)    | <ul> <li>Power Status #1. Passed transparently from the K2 to the U-interface at the NT and from the U to the K2 at the LT.</li> <li>0—Primary power out.</li> <li>1—Primary power is normal.</li> <li>When both ps1 and ps2 are 0, this indicates a dying gasp.</li> </ul>                                                                                                                                                                              |

| UM2   | 8     | [a]dea<br>(DΟΝΤ/<br>DILT) | <b>[AND with] Deactivate.</b> In LT mode, this bit is used in conjunction with the Idea bit from the K2, then passed to the U-interface as the transmitted dea bit. In NT mode, this bit is passed transparently from the U to the K2 interface. Allows deactivation warning to the far-end NT without deactivating the local transceiver.<br>0—Deactivation warning.<br>1—Normal.                                                                       |

| UM3   | 1, 6  | Rx, y                     | <b>Reserved Bits.</b> Passed transparently from the K2 to the U-interface and from the U to the K2 interface. Transmit should always be set to a 1.                                                                                                                                                                                                                                                                                                      |

| UM3   | 2     | [r]febe                   | <b>[Receive] Far-End Block Error.</b> If the MODE1 = 1, rfebe is ANDed with nebe and the result is sent out as the U-interface febe bit. If the MODE1 = 0, rfebe is passed transparently from the K2 ( $DO_{LT}/DI_{NT}$ ) to the U-interface febe bit. For either setting of MODE1, the febe bit is passed transparently from the U-interface to the K2 interface. 0—Error indication passed to the originator. 1—No error, or feature is not utilized. |

| UM3   | 3     | ps2<br>(DOLT/<br>DINT)    | Power Status #2. Passed transparently from the K2 to the U-interface at the NT and from the U to the K2 at the LT.<br>0—Secondary power out.<br>1—Secondary power normal.<br>When both ps1 and ps2 are 0, this indicates a dying gasp.                                                                                                                                                                                                                   |

| UM3   | 4     | ntm<br>(DO∟т/<br>DIℕт)    | NT Test Mode. Passed transparently from the K2 to the U-interface at the NT and from the U to the K2 at the LT.<br>0—The NT is currently in a test mode.<br>1—Normal.                                                                                                                                                                                                                                                                                    |

### Table 10. UM2 and UM3 Octet—UCS Bits (Functions) (continued)

| Octet | Bit #      | Symbol                 | Name/Function                                                                                                                                                                                                                                                |

|-------|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM3   | 5          | cso<br>(DOlt/<br>DInt) | <b>Cold Start Only.</b> Passed transparently from the K2 to the U-interface at the NT and from the U to the K2 at the LT.<br>0—Cold and warm start capability.<br>1—Cold start only.                                                                         |

| UM3   | 3, 4,<br>5 | Rx, y<br>(DONT/DILT)   | <b>Reserved Bits.</b> Passed transparently from the K2 to the U-interface (DILT) and from the U to the K2 interface (DONT). Transmit should always set to a 1.                                                                                               |

| UM3   | 7          | sai<br>(DInt/<br>DOLT) | <b>S/T-Interface Activity Indicator.</b> Passed transparently from the K2 to the U-interface at the NT and from the U to the K2 interface at the LT.<br>0—No activity at the S/T-interface.<br>1—Activity (INFO1 or INFO3) at S/T-interface.                 |

| UM3   | 7          | uoa<br>(DILT/<br>DONT) | U-Interface Only Activation. Passed transparently from the K2 to the U-interface<br>at the LT and from the U to the K2 interface at the NT.<br>0—Request S/T deactivation at the NT.<br>1—Allow S/T activation at the NT.                                    |

| UM3   | 8          | nib<br>(DInt/<br>DOlt) | <b>Network Indicator Bit.</b> Passed transparently from the K2 to the U-interface at the NT and from the U to the K2 interface at the LT. Reserved for network use. Normally set to 1 in customer premises equipment.                                        |

| UM3   | 8          | aib<br>(DILT/<br>DOnt) | Alarm Indication Bit. Passed transparently from the K2 to U-interface at the LT<br>and from the U to the K2 interface at the NT.<br>0—Failure of intermediate 2B+D transparent element.<br>1—Transmission path is established between NT and local exchange. |

#### Table 11. DS Octet (Overview)—Device Status

| Octet | Octet # | DO/DI | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 | Bit 8 |

|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| DS    | 8       | DO    | nebe  | xact  | —     | 1     | oof   | 1     | rsksi | 1     |

#### Table 12. DS Octet (Functions)—Device Status

| Octet | Bit #   | Symbol | Name/Function                                                                                                                                                                           |

|-------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS    | 1       | nebe   | Near-End Block Error.<br>0—crc error detected in previously received U frame.<br>1—Normal.                                                                                              |

| DS    | 2       | xact   | Transceiver Active.<br>0—Transceiver in reset state.<br>0 to 1—Detection of a tone or istp = 0.<br>1—Transceiver active.<br>1 to 0—On reset, 480 ms after loss of sync or deactivation. |

| DS    | 3       | _      | Undefined. May be either a 1 or a 0.                                                                                                                                                    |

| DS    | 4, 6, 8 |        | Reserved. In normal operation, these bits are 1.                                                                                                                                        |

| DS    | 5       | oof    | Out of Frame.<br>0—Out of frame.<br>1 to 0—Initiates the 480 ms loss of synchronization timer.<br>1—Normal.                                                                             |

| DS    | 7       | rsksi  | <b>Reflected System-to-K2.</b> This bit reflects the value of the sksi bit received over the K2 interface.                                                                              |

### Table 13. DC Octet (Overview)

| Octet | Octet # | DO/DI | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 | Bit 8 |

|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| DC    | 8       | DI    | ccrc  | istp  | lpbk  | afrst | ldea  | 1     | sksi  | хрсу  |

### Table 14. DC Octet (Functions)

| Octet | Bit # | Symbol | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC    | 1     | ccrc   | <b>Corrupt Cyclic Redundancy Check.</b> This bit is used to corrupt the crc information transmitted by the transceiver to the U-interface.<br>0—Corrupt crc generation as long as bit is low.<br>1—Generate correct crc (normal).                                                                                                                                                                                                                                                                                                                     |

| DC    | 2     | istp   | Initiate Start-Up. This bit is used to notify the transceiver of an activation request.<br>Should be set to a 1 during loopback. If xact = 1, istp is ignored; if xact = 0:<br>0—Initiate start-up (activation request).<br>1—Reset state (transceiver inactive).                                                                                                                                                                                                                                                                                     |

| DC    | 3     | lpbk   | Local Loopback.<br>0—Loopback.<br>1—Normal.<br>Loop back the complete 160 kbits/s U-interface bit stream at the analog output. Loop-<br>back turns off echo canceler and reconfigures the descrambler. Device should be re-<br>set and line disconnected before loopback test; istp should be set to a 1 during<br>loopback.                                                                                                                                                                                                                          |

| DC    | 4     | afrst  | Adaptive Filter Reset.<br>0—Normal.<br>1—Reset.<br>2B+D and UM set equal to 1 on DO. Reset halts loop transmission and clears the<br>transceiver's adaptive filter coefficients, overriding all other transceiver control sig-<br>nals. This provides the same functionality as the RESET pin on the T7264, except F<br>to MTC synchronization (LT) is not lost.                                                                                                                                                                                      |

| DC    | 5     | ldea   | Local Deactivation.<br>0 — Normal.<br>1 — Deactivate. DO 2B+D and UM set equal to 1.<br>Upon receiving Idea = 1 from the system device, the transceiver will save adaptive fil-<br>ter coefficients. In the LT, the device sends three or four U superframes of dea = 0,<br>then ceases transmission and enters the idle state. In the NT, the device deactivates<br>upon signal loss and enters the idle state. In the NT, Idea should be set before the loss<br>of signal (on second dea = 0) and held until xact goes low for proper deactivation. |

| DC    | 6     |        | Reserved. For normal operation, this bit must be set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DC    | 7     | sksi   | <b>System-to-K2.</b> This bit may be set high or low without affecting the state of the transceiver. sksi is reflected back from the T7264 across the K2 interface by means of the rsksi bit.                                                                                                                                                                                                                                                                                                                                                         |

| DC    | 8     | хрсу   | Transparency.<br>0—Transparent 2B+D.<br>1—LT mode 2B+D = 0 transmitted across the U-interface.<br>1—NT mode 2B+D = 1 transmitted across the U-interface.<br>This bit only affects the data transmitted on the U-interface. The U-to-K2 interface al-<br>ways remains transparent after start-up.                                                                                                                                                                                                                                                      |

### K2 Bit Levels

#### Table 15. K2 Data Out (DO) Bit Levels

(+) Active = 1 (T) Transparent

(-) Active = 0 (P) Pulsing

| Bit Name | Description                  | True Level      | Reset/Idle | Operational |

|----------|------------------------------|-----------------|------------|-------------|

|          | U-In                         | terface Related |            | 1           |

| B1, B2   | ISDN 64 kbits/s B1, B2 Octet |                 | 1          | Т           |

| D        | ISDN 16 kbits/s D Bits       |                 | 1          | Т           |

| RSF, TSF | Receive/Transmit Superframe  | +               | 1          | Р           |

| RF, TF   | Receive/Transmit Frame       | +               | 1          | Р           |

|          |                              | UM Bits         |            |             |

| eoc      | eoc addr, d/m, and info bits | +               | 1          | Т           |

| act      | Activate                     | +               | 0          | 1           |

| dea      | Deactivate                   | _               | 1          | 1           |

| ps1, ps2 | Primary/Sec. Power Status    | +               | 1          | 1           |

| febe     | Far-end Block Error          | _               | 1          | 1           |

| ntm      | NT in Test Mode              | -               | 1          | 1           |

| CSO      | Cold Start Only              | +               | 1          | 0 or 1      |

| sai      | S/T Activity Indicator       | +               | 1          | 1           |

| uoa      | U Only Activation            | _               | 1          | 1           |

| nib      | Network Indicator Bit        | -               | 1          | 1           |

| aib      | Alarm Indication Bit         | _               | 1          | 1           |

| R        | Reserved                     | _               | 1          | 1           |

|          |                              | DS Bits         |            |             |

| nebe     | Near-end Bit Error           | _               | 1          | 1           |

| xact     | Transceiver Active           | +               | 0          | 1           |

| oof      | Out of Frame                 | _               | 0          | 1           |

#### Table 16. K2 Device Control (DC) Bit Levels

(+) Active = 1 (x) Either 1 or 0

(-) Active = 0

| Bit Name | Description              | True Level | Reset/Idle | Operational |  |

|----------|--------------------------|------------|------------|-------------|--|

| ccrc     | Corrupt the Outgoing crc | _          | x          | 1           |  |

| istp     | Initiate Start-up        | _          | 1          | 0 then x    |  |

| lpbk     | Loopback                 | _          | 1          | 1           |  |

| afrst    | Reset                    | +          | 1 then x   | 0           |  |

| ldea     | Local Deactivate         | +          | 1 then x   | 0           |  |

| хрсу     | Transparency             | _          | 1          | 0           |  |

### **U-Interface Description**

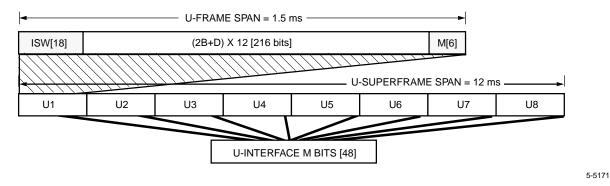

Data is transmitted over the U-interface in 240-bit groups called U frames. Each U frame consists of an 18-bit synchronization word (ISW or SW), 12 blocks of 2B+D data (216 bits), and six overhead bits (M). A U-interface superframe consists of eight U frames grouped together. The beginning of a U superframe is indicated by the inverted sync word (ISW). The six overhead bits from each of the eight U frames, when taken together, form the 48 M bits. The following diagram shows how U frames, superframes, and M bits are mapped.

Figure 12. U-Interface Frame and Superframe

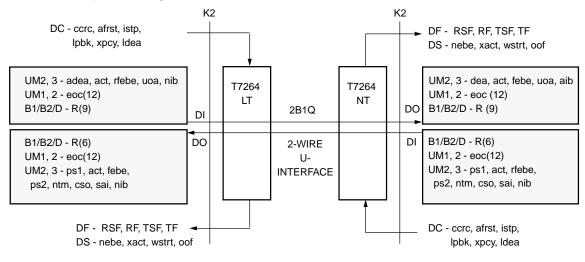

Of the 48 M bits, 24 bits form the embedded operations channel (eoc) for sending messages from the LT to the NT and responses from the NT to the LT. There are two eoc messages per superframe with 12 bits per eoc message (eoc1 and eoc2). Another 12 bits serve as control and status bits (UCS). The last 12 bits form the cyclic redundancy check (crc) which is calculated over the 2B+D data and the M4 bits of the previous superframe. Figure 13 shows the different groups of bits in the superframe.

| BIT #   | 1—18 | 19—234   | 235 | 236  | 237 | 238     | 239         | 240 |

|---------|------|----------|-----|------|-----|---------|-------------|-----|

| FRAME # | Sync | 12(2B+D) | M1  | M2   | M3  | M4      | M5          | M6  |