Integrated Device Technology, Inc.

# 16K x 32 CMOS DUAL-PORT STATIC RAM MODULE

IDT7M1002

## FEATURES

- High-density 512K CMOS Dual-Port RAM module

- Fast access times

- Commercial: 30, 35ns

- Military: 40, 45ns

- Fully asynchronous read/write operation from either port

- Easy to expand data bus width to 64 bits or more using the Master/Slave function

- Separate byte read/write signals for byte control

- On-chip port arbitration logic

- INT flag for port-to-port communication

- Full on-chip hardware support of semaphore signaling between ports

- Surface mounted fine pitch (25 mil) LCC packages allow through-hole module to fit into 121 pin PGA footprint

- Single 5V ( $\pm 10\%$ ) power supply

- Inputs/outputs directly TTL-compatible

## DESCRIPTION

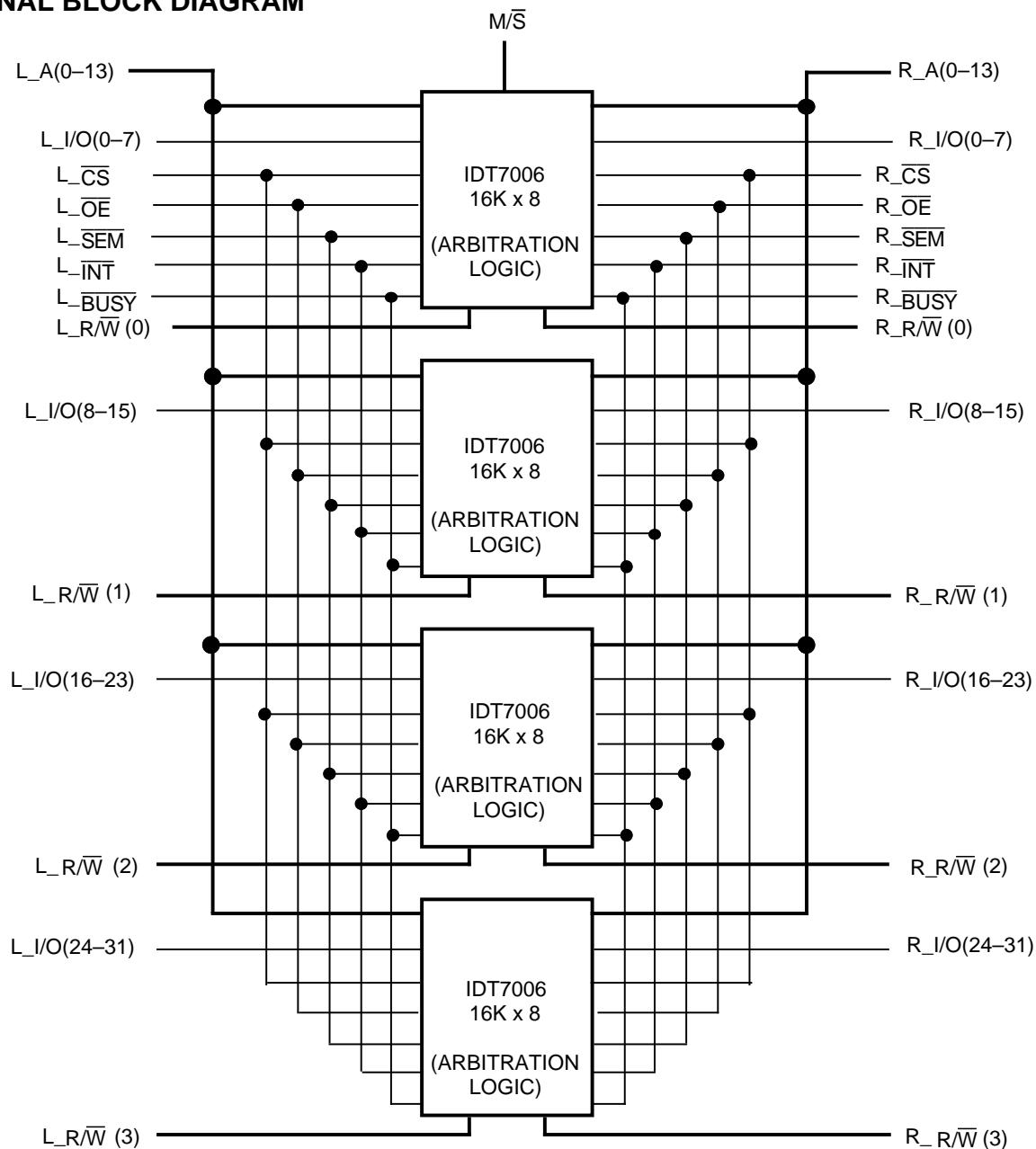

The IDT7M1002 is a 16K x 32 high-speed CMOS Dual-Port Static RAM Module constructed on a co-fired ceramic substrate using four 16K x 8 (IDT7006) Dual-Port Static RAMs in surface-mounted LCC packages. The IDT7M1002 module is designed to be used as stand-alone 512K Dual-Port RAM or as a combination Master/Slave Dual-Port RAM for 64-bit or more word width systems. Using the IDT Master/Slave approach in such system applications results in full-speed, error-free operation without the need for additional discrete logic.

The module provides two independent ports with separate control, address, and I/O pins that permit independent and asynchronous access for reads or writes to any location in memory. System performance is enhanced by facilitating port-to-port communication via additional control signals SEM and INT.

The IDT7M1002 module is packaged in a ceramic 121 pin PGA (Pin Grid Array) 1.35 inches on a side. Maximum access times as fast as 30ns are available over the commercial temperature range and 40ns over the military temperature range.

All IDT military modules are constructed with semiconductor components manufactured in compliance with the latest revision of MIL-STD-883, Class B making them ideally suited to applications demanding the highest level of performance and reliability.

## PIN CONFIGURATION

|   | 1         | 2         | 3         | 4         | 5         | 6        | 7        | 8        | 9         | 10        | 11        | 12        | 13        |

|---|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|

| A | L_I/O(24) | L_I/O(26) | L_I/O(28) | L_I/O(30) | L_CS      | L_OE     | L_R/W(3) | R_OE     | R_CS      | R_I/O(30) | R_I/O(28) | R_I/O(26) | R_I/O(24) |

| B | L_I/O(23) | L_I/O(25) | L_I/O(27) | L_I/O(29) | L_I/O(31) | L_A(0)   | L_R/W(4) | R_A(0)   | R_I/O(31) | R_I/O(29) | R_I/O(27) | R_I/O(25) | R_I/O(23) |

| C | L_I/O(21) | L_I/O(22) | VCC       | L_A(3)    | L_A(2)    | L_A(1)   | GND      | R_A(1)   | R_A(2)    | R_A(3)    | GND       | R_I/O(22) | R_I/O(21) |

| D | L_I/O(19) | L_I/O(20) | L_A(4)    | GND       |           |          |          |          |           |           | R_A(4)    | R_I/O(20) | R_I/O(19) |

| E | L_I/O(17) | L_I/O(18) | L_A(5)    |           |           |          |          |          |           |           | R_A(5)    | R_I/O(18) | R_I/O(17) |

| F | L_SEM     | L_I/O(16) | L_A(6)    |           |           |          |          |          |           |           | R_A(6)    | R_I/O(16) | R_SEM     |

| G | L_BUSY    | L_INT     | GND       |           |           |          |          |          |           |           | GND       | R_INT     | R_BUSY    |

| H | L_R/W(1)  | L_R/W(2)  | L_A(7)    |           |           |          |          |          |           |           | R_A(7)    | R_R/W(2)  | R_R/W(1)  |

| I | L_I/O(15) | L_I/O(14) | L_A(8)    |           |           |          |          |          |           |           | R_A(8)    | R_I/O(14) | R_I/O(15) |

| J | L_I/O(13) | L_I/O(12) | L_A(9)    |           |           |          |          |          |           |           | R_A(9)    | R_I/O(12) | R_I/O(13) |

| K | L_I/O(11) | M/S       | GND       | L_A(10)   | L_A(11)   | L_A(12)  | GND      | R_A(12)  | R_A(11)   | R_A(10)   | VCC       | GND       | R_I/O(11) |

| L | L_I/O(10) | L_I/O(8)  | L_I/O(6)  | L_I/O(4)  | L_I/O(2)  | L_A(13)  | R_R/W(4) | R_A(13)  | R_I/O(2)  | R_I/O(4)  | R_I/O(6)  | R_I/O(8)  | R_I/O(10) |

| M | L_I/O(9)  | L_I/O(7)  | L_I/O(5)  | L_I/O(3)  | L_I/O(1)  | L_I/O(0) | R_R/W(3) | R_I/O(0) | R_I/O(1)  | R_I/O(3)  | R_I/O(5)  | R_I/O(7)  | R_I/O(9)  |

PGA

TOP VIEW

2795 drw 01

The IDT logo is a registered trademark of Integrated Device Technology Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

DECEMBER 1995

©1996 Integrated Device Technology, Inc.

DSC-2795/5

## FUNCTIONAL BLOCK DIAGRAM

## PIN NAMES

2795 drw 02

| Left Port    | Right Port   | Description          |

|--------------|--------------|----------------------|

| L_A (0-13)   | R_A (0-13)   | Address Inputs       |

| L_I/O (0-31) | R_I/O (0-31) | Data Inputs/Outputs  |

| L_R/W (1-4)  | R_R/W (1-4)  | Read/Write Enables   |

| L_CS         | R_CS         | Chip Select          |

| L_OE         | R_OE         | Output Enable        |

| L_BUSY       | R_BUSY       | Busy Flag            |

| L_INT        | R_INT        | Interrupt Flag       |

| L_SEM        | R_SEM        | Semaphore Control    |

| M/S          |              | Master/Slave Control |

| VCC          |              | Power                |

| GND          |              | Ground               |

2795 tbl 01

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Rating                               | Commercial   | Military     | Unit |

|--------|--------------------------------------|--------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | V    |

| TA     | Operating Temperature                | 0 to +70     | -55 to +125  | °C   |

| TBIAS  | Temperature Under Bias               | -55 to +125  | -65 to +135  | °C   |

| TSTG   | Storage Temperature                  | -55 to +125  | -65 to +150  | °C   |

| IOUT   | DC Output Current                    | 50           | 50           | mA   |

2795 tbl 02

**NOTE:**

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2795 tbl 03

## RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Ambient Temperature | GND | VCC        |

|------------|---------------------|-----|------------|

| Military   | -55°C to +125°C     | 0V  | 5.0V ± 10% |

| Commercial | 0°C to +70°C        | 0V  | 5.0V ± 10% |

2795 tbl 04

## RECOMMENDED DC OPERATING CONDITIONS

| Symbol | Parameter          | Min.                | Typ. | Max. | Unit |

|--------|--------------------|---------------------|------|------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5  | V    |

| GND    | Supply Voltage     | 0                   | 0    | 0    | V    |

| VIH    | Input High Voltage | 2.2                 | —    | 6.0  | V    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | —    | 0.8  | V    |

**NOTE:**

1. VIL ≥ -3.0V for pulse width less than 20ns

## DC ELECTRICAL CHARACTERISTICS

(VCC = 5V ± 10%, TA = -55°C to +125°C or 0°C to +70°C)

| Symbol          | Parameter                         | Test Conditions                             | Min. |      | Max. |      | Units |

|-----------------|-----------------------------------|---------------------------------------------|------|------|------|------|-------|

|                 |                                   |                                             | Min. | Max. | Min. | Max. |       |

| I <sub>L1</sub> | Input Leakage (Address & Control) | Vcc = Max.<br>VIN = GND to Vcc              | —    | —    | 40   | —    | µA    |

| I <sub>L2</sub> | Input Leakage (Data)              | Vcc = Max.<br>VIN = GND to Vcc              | —    | —    | 10   | —    | µA    |

| I <sub>LO</sub> | Output Leakage (Data)             | Vcc = Max.<br>CS ≥ VIH, VOUT = GND to Vcc   | —    | —    | 10   | —    | µA    |

| V <sub>OL</sub> | Output Low                        | Vcc = Min. I <sub>OL</sub> = 4mA<br>Voltage | —    | —    | 0.4  | —    | V     |

| V <sub>OH</sub> | Output High Voltage               | Vcc = Min, I <sub>OH</sub> = -4mA           | 2.4  | —    | —    | —    | V     |

2795 tbl 05

## DC ELECTRICAL CHARACTERISTICS

(VCC = 5V ± 10%, TA = -55°C to +125°C or 0°C to +70°C)

| Symbol           | Parameter                                         | Test Conditions                                                                          | Commercial |      | Military |      | Units |

|------------------|---------------------------------------------------|------------------------------------------------------------------------------------------|------------|------|----------|------|-------|

|                  |                                                   |                                                                                          | Min.       | Max. | Min.     | Max. |       |

| I <sub>CC2</sub> | Dynamic Operating Current (Both Ports Active)     | Vcc = Max., CS ≤ VIL, SEM = Don't Care Outputs Open, f = f <sub>MAX</sub>                | —          | 1360 | —        | 1600 | mA    |

| I <sub>SB</sub>  | Standby Supply Current (Both Ports Inactive)      | Vcc = Max., L_CS and R_CS ≥ VIH Outputs Open, f = f <sub>MAX</sub>                       | —          | 280  | —        | 340  | mA    |

| I <sub>SB1</sub> | Standby Supply Current (One Port Inactive)        | Vcc = Max., L_CS or R_CS ≥ VIH Outputs Open, f = f <sub>MAX</sub>                        | —          | 1000 | —        | 1160 | mA    |

| I <sub>SB2</sub> | Full Standby Supply Current (Both Ports Inactive) | L_CS and R_CS ≥ Vcc - 0.2V<br>VIN > Vcc - 0.2V or < 0.2V<br>L_SEM and R_SEM ≥ Vcc - 0.2V | —          | 60   | —        | 120  | mA    |

2795 tbl 06

**CAPACITANCE<sup>(1)</sup>** (TA = +25°C, f = 1.0MHz)

| Symbol              | Parameter                                | Condition             | Max. | Unit |

|---------------------|------------------------------------------|-----------------------|------|------|

| C <sub>IN</sub> (1) | Input Capacitance (CS, OE, SEM, Address) | V <sub>IN</sub> = 0V  | 40   | pF   |

| C <sub>IN</sub> (2) | Input Capacitance (R/W, I/O, INT)        | V <sub>IN</sub> = 0V  | 12   | pF   |

| C <sub>IN</sub> (3) | Input Capacitance (BUSY, M/S)            | V <sub>IN</sub> = 0V  | 45   | pF   |

| C <sub>OUT</sub>    | Output Capacitance (I/O)                 | V <sub>OUT</sub> = 0V | 12   | pF   |

2795 tbl 07

**NOTE:**

1. This parameter is guaranteed by design but not tested.

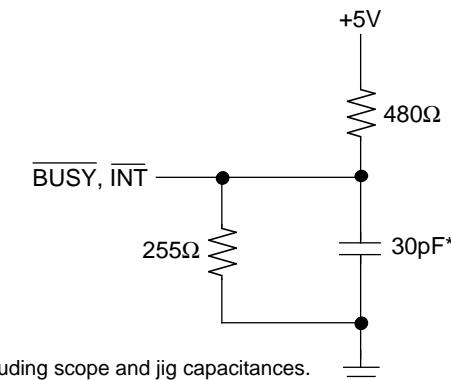

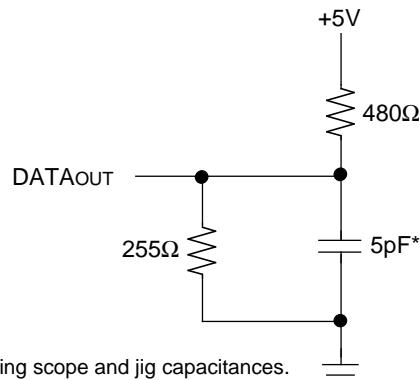

**AC TEST CONDITIONS**

|                               |                     |

|-------------------------------|---------------------|

| Input Pulse Levels            | GND to 3.0V         |

| Input Rise/Fall Times         | 5ns                 |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

2795 tbl 08

\*Including scope and jig capacitances.

Figure 1. Output Load

2795 drw 03

\*Including scope and jig capacitances.

Figure 2. Output Load

2795 drw 04

**AC ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 5V ± 10%, TA = -55°C to +125°C or 0°C to +70°C)

| Symbol                          | Parameter                          | 7M1002SxxG |      |      |      | 7M1002SxxGB |      |      |      | Unit |  |

|---------------------------------|------------------------------------|------------|------|------|------|-------------|------|------|------|------|--|

|                                 |                                    | 30         |      | -35  |      | -40         |      | -45  |      |      |  |

|                                 |                                    | Min.       | Max. | Min. | Max. | Min.        | Max. | Min. | Max. |      |  |

| <b>Read Cycle</b>               |                                    |            |      |      |      |             |      |      |      |      |  |

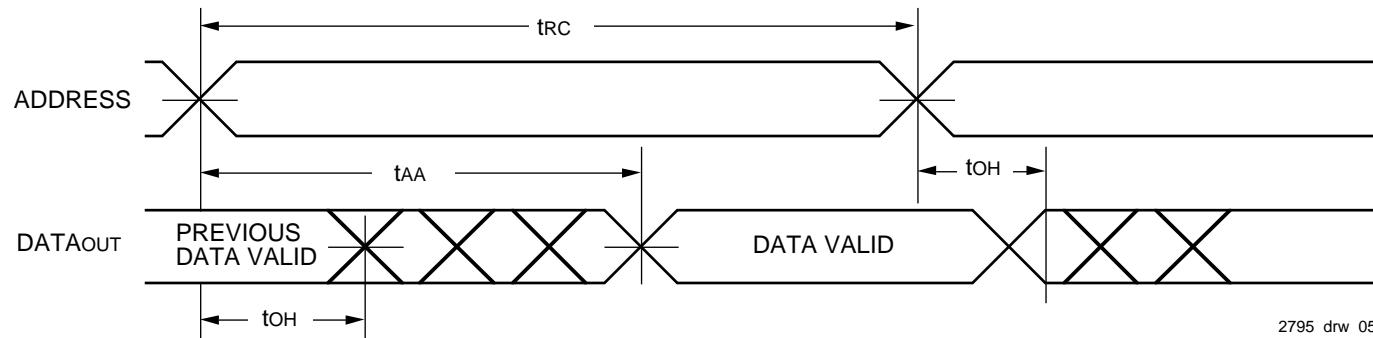

| t <sub>RC</sub>                 | Read Cycle Time                    | 30         | —    | 35   | —    | 40          | —    | 45   | —    | ns   |  |

| t <sub>AA</sub>                 | Address Access Time                | —          | 30   | —    | 35   | —           | 40   | —    | 45   | ns   |  |

| t <sub>ACS</sub> <sup>(2)</sup> | Chip Select Access Time            | —          | 30   | —    | 35   | —           | 40   | —    | 45   | ns   |  |

| t <sub>OE</sub>                 | Output Enable Access Time          | —          | 17   | —    | 20   | —           | 22   | —    | 25   | ns   |  |

| t <sub>OH</sub>                 | Output Hold from Address Change    | 3          | —    | 3    | —    | 3           | —    | 3    | —    | ns   |  |

| t <sub>LZ</sub> <sup>(1)</sup>  | Output to Low-Z                    | 3          | —    | 3    | —    | 3           | —    | 5    | —    | ns   |  |

| t <sub>HZ</sub> <sup>(1)</sup>  | Output to High-Z                   | —          | 15   | —    | 15   | —           | 17   | —    | 20   | ns   |  |

| t <sub>PU</sub> <sup>(1)</sup>  | Chip Select to Power Up Time       | 0          | —    | 0    | —    | 0           | —    | 0    | —    | ns   |  |

| t <sub>PD</sub> <sup>(1)</sup>  | Chip Deselect to Power Up Time     | —          | 50   | —    | 50   | —           | 50   | —    | 50   | ns   |  |

| t <sub>SOUP</sub>               | Sem. Flag Update Pulse (OE or SEM) | 15         | —    | 15   | —    | 15          | —    | 15   | —    | ns   |  |

| <b>Write Cycle</b>              |                                    |            |      |      |      |             |      |      |      |      |  |

| t <sub>WC</sub>                 | Write Cycle Time                   | 30         | —    | 35   | —    | 40          | —    | 45   | —    | ns   |  |

| t <sub>CW</sub> <sup>(2)</sup>  | Chip Select to End-of-Write        | 25         | —    | 30   | —    | 35          | —    | 40   | —    | ns   |  |

| t <sub>AW</sub>                 | Address Valid to End-of-Write      | 25         | —    | 30   | —    | 35          | —    | 40   | —    | ns   |  |

| t <sub>AS</sub>                 | Address Set-Up Time                | 0          | —    | 0    | —    | 0           | —    | 0    | —    | ns   |  |

| t <sub>WP</sub>                 | Write Pulse Width                  | 25         | —    | 30   | —    | 35          | —    | 35   | —    | ns   |  |

| t <sub>WR</sub>                 | Write Recovery Time                | 0          | —    | 0    | —    | 0           | —    | 0    | —    | ns   |  |

(Continued on next page)

2795 tbl 09

## AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = 5V ± 10%, T<sub>A</sub> = 55°C to +125°C or 0°C to +70°C)

| Symbol                                      | Parameter                           | 7M1002SxxG |        |      |        | 7M1002SxxGB |        |      |        | Unit |  |

|---------------------------------------------|-------------------------------------|------------|--------|------|--------|-------------|--------|------|--------|------|--|

|                                             |                                     | 30         |        | -35  |        | -40         |        | -45  |        |      |  |

|                                             |                                     | Min.       | Max.   | Min. | Max.   | Min.        | Max.   | Min. | Max.   |      |  |

| <b>Write Cycle (continued)</b>              |                                     |            |        |      |        |             |        |      |        |      |  |

| tDW                                         | Data Valid to End-of-Write          | 22         | —      | 25   | —      | 25          | —      | 25   | —      | ns   |  |

| tDH                                         | Data Hold Time                      | 0          | —      | 0    | —      | 0           | —      | 0    | —      | ns   |  |

| tHZ <sup>(1)</sup>                          | Output to High-Z                    | —          | 15     | —    | 15     | —           | 17     | —    | 20     | ns   |  |

| tOW <sup>(1)</sup>                          | Output Active from End-of-Write     | 0          | —      | 0    | —      | 0           | —      | 0    | —      | ns   |  |

| tSWRD                                       | SEM Flag Write to Read Time         | 10         | —      | 10   | —      | 10          | —      | 10   | —      | ns   |  |

| tSPS                                        | SEM Flag Contention Window          | 10         | —      | 10   | —      | 10          | —      | 10   | —      | ns   |  |

| <b>Busy Cycle-Master Mode<sup>(3)</sup></b> |                                     |            |        |      |        |             |        |      |        |      |  |

| tbAA                                        | BUSY Access Time to Address         | —          | 30     | —    | 35     | —           | 35     | —    | 35     | ns   |  |

| tbDA                                        | BUSY Disable Time to Address        | —          | 25     | —    | 30     | —           | 30     | —    | 30     | ns   |  |

| tbAC                                        | BUSY Access Time to Chip Select     | —          | 25     | —    | 30     | —           | 30     | —    | 30     | ns   |  |

| tbDC                                        | BUSY Disable Time to Chip Deselect  | —          | 25     | —    | 25     | —           | 25     | —    | 25     | ns   |  |

| twDD <sup>(5)</sup>                         | Write Pulse to Data Delay           | —          | 55     | —    | 60     | —           | 65     | —    | 70     | ns   |  |

| tDDD                                        | Write Data Valid to Read Data Delay | —          | 40     | —    | 45     | —           | 50     | —    | 55     | ns   |  |

| tAPS <sup>(6)</sup>                         | Arbitration Priority Set-Up Time    | 5          | —      | 5    | —      | 5           | —      | 5    | —      | ns   |  |

| tbDD                                        | BUSY Disable to Valid Time          | —          | NOTE 9 | —    | NOTE 9 | —           | NOTE 9 | —    | NOTE 9 | ns   |  |

| <b>Busy Cycle-Slave Mode<sup>(4)</sup></b>  |                                     |            |        |      |        |             |        |      |        |      |  |

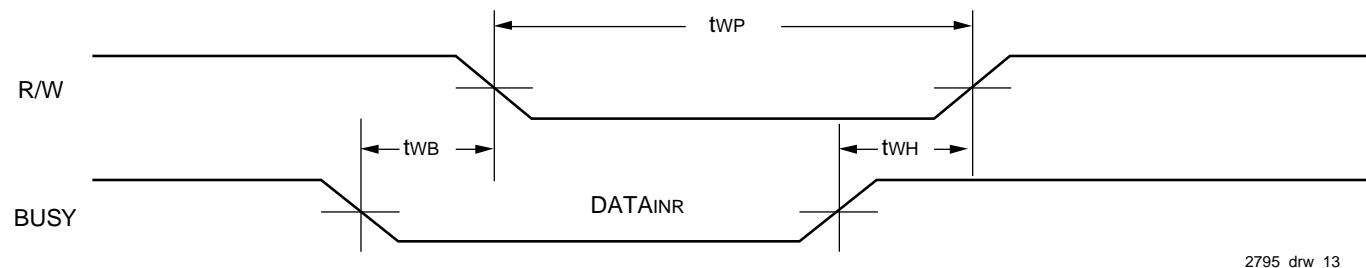

| twB <sup>(7)</sup>                          | Write to BUSY Input                 | 0          | —      | 0    | —      | 0           | —      | 0    | —      | ns   |  |

| tWH <sup>(8)</sup>                          | Write Hold after BUSY               | 25         | —      | 25   | —      | 25          | —      | 25   | —      | ns   |  |

| twDD <sup>(5)</sup>                         | Write Pulse to Data Delay           | —          | 55     | —    | 60     | —           | 65     | —    | 70     | ns   |  |

| <b>Interrupt Timing</b>                     |                                     |            |        |      |        |             |        |      |        |      |  |

| tAS                                         | Address Set-Up Time                 | 0          | —      | 0    | —      | 0           | —      | 0    | —      | ns   |  |

| tWR                                         | Write Recovery Time                 | 0          | —      | 0    | —      | 0           | —      | 0    | —      | ns   |  |

| tINS                                        | Interrupt Set Time                  | —          | 25     | —    | 30     | —           | 32     | —    | 35     | ns   |  |

| tINR                                        | Interrupt Reset Time                | —          | 25     | —    | 30     | —           | 32     | —    | 35     | ns   |  |

2795tbl 10

### NOTES:

1. This parameter is guaranteed by design but not tested.

2. To access RAM, CS ≤ V<sub>IL</sub> and SEM ≥ V<sub>IH</sub>. To access semaphore, CS ≥ V<sub>IH</sub> and SEM ≤ V<sub>IL</sub>.

3. When the module is being used in the Master Mode (M/S ≥ V<sub>IH</sub>).

4. When the module is being used in the Slave Mode (M/S ≤ V<sub>IL</sub>).

5. Port-to-Port delay through the RAM cells from the writing port to the reading port.

6. To ensure that the earlier of the two ports wins.

7. To ensure that the write cycle is inhibited during contention.

8. To ensure that a write cycle is completed after contention.

9. tBDD is a calculated parameter and is the greater of 0, tWDD - tWP (actual), or tDDD - tWP (actual).

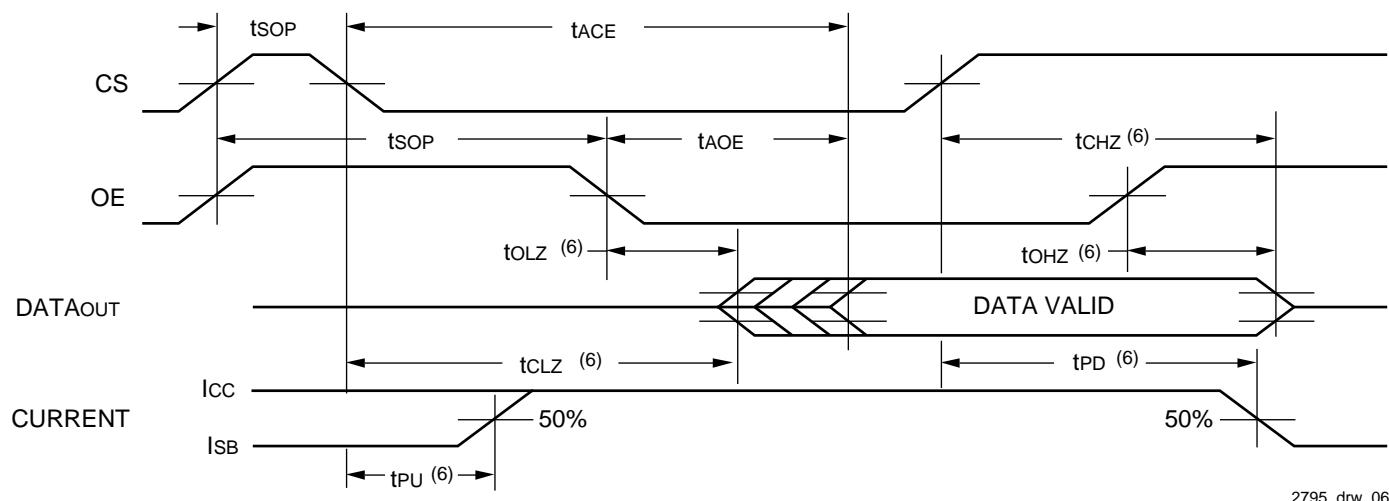

**TIMING WAVEFORM OF READ CYCLE NO. 1, EITHER SIDE<sup>(1, 2, 4)</sup>**

**TIMING WAVEFORM OF READ CYCLE NO. 2, EITHER SIDE<sup>(1, 3, 5)</sup>**

**NOTES:**

1. R/W is HIGH for Read Cycles

2. Device is continuously enabled  $\overline{CS} \leq V_{IL}$ . This waveform cannot be used for semaphore reads.

3. Addresses valid prior to or coincident with  $\overline{CS}$  transition LOW.

4.  $\overline{OE} \leq V_{IL}$

5. To access RAM,  $\overline{CS} \leq V_{IL}$  and  $\overline{SEM} \geq V_{IH}$ . To access semaphore,  $\overline{CS} \geq V_{IH}$  and  $\overline{SEM} \leq V_{IL}$ .

6. This parameter is guaranteed by design but not tested.

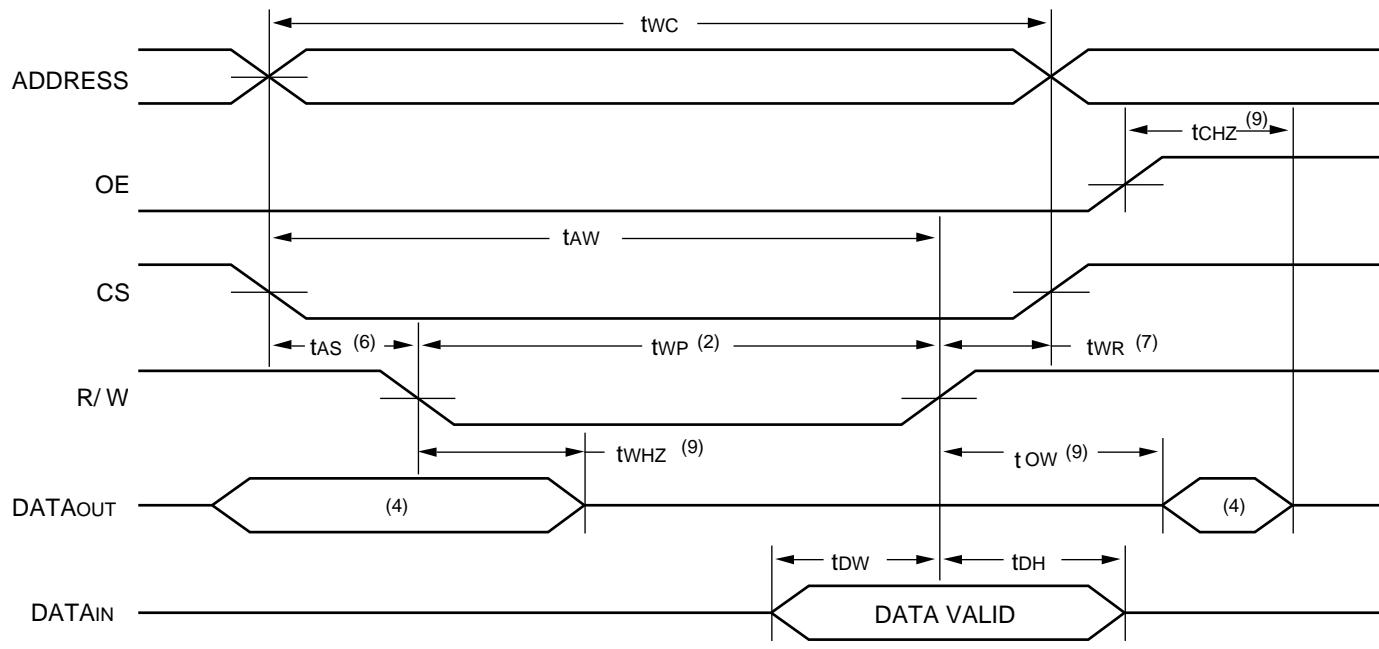

**TIMING WAVEFORM OF WRITE CYCLE NO. 1 (R/W CONTROLLED TIMING)<sup>(1, 2, 4)</sup>**

2795 drw 07

**TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CS CONTROLLED TIMING)<sup>(1, 2, 4)</sup>**

2795 drw 08

**NOTES:**

1. R/W must be HIGH during all address transitions.

2. A write occurs during the overlap (twp) of a LOW CS and a LOW R/W.

3. tWR is measured from the earlier of CS or R/W (or SEM or R/W) going HIGH to the end of write cycle.

4. During this period, the I/O pins are in the output state and input signals must be applied.

5. If the CS or SEM low transition occurs simultaneously with or after the R/W low transition, the outputs remain in the high impedance state.

6. Timing depends on which enable signal is asserted last.

7. Timing depends on which enable signal is de-asserted first.

8. If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of twp or (twz + tdw) to allow the I/O drivers to turn off and data to be placed on the bus for the required tdw. If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

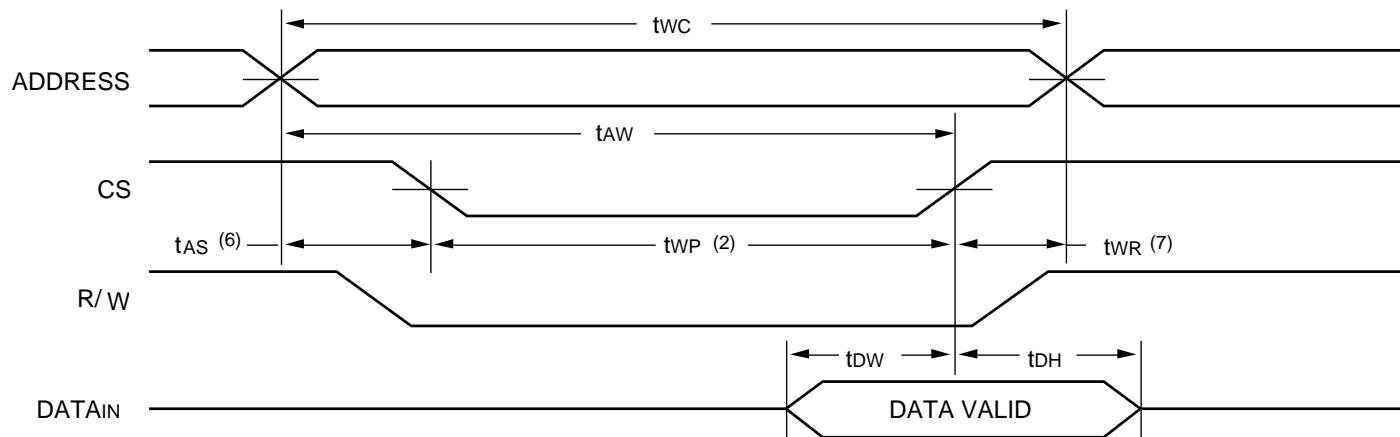

**TIMING WAVEFORM OF SEMAPHORE READ AFTER WRITE, EITHER SIDE<sup>(1)</sup>**

2795 drw 09

**NOTE:**

1.  $CS \geq V_{IH}$  for the duration of the above timing (both write and read cycle).

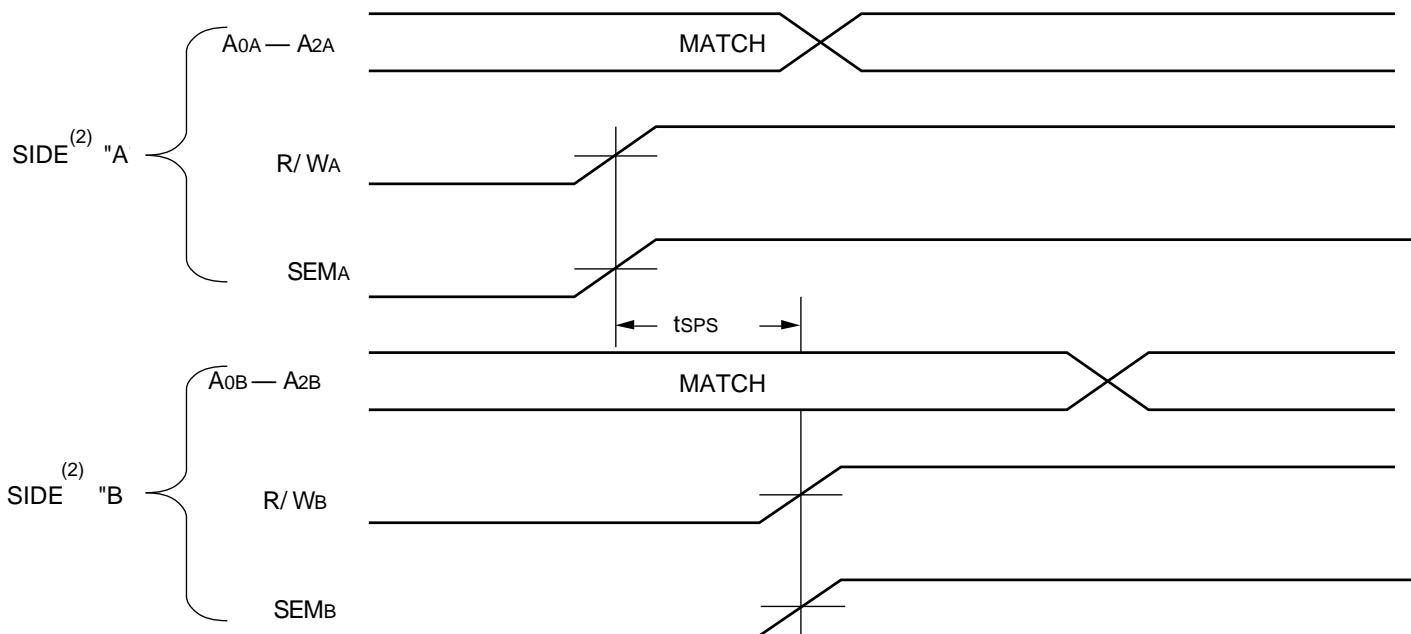

**TIMING WAVEFORM OF SEMAPHORE CONTENTION<sup>(1, 3, 4)</sup>**

2795 drw 10

**NOTES:**

1.  $DOL \leq V_{IL}$ ,  $(L\_CS = R\_CS) \geq V_{IH}$  Semaphore Flag is released from both sides (reads as ones from both sides) at cycle start.

2. "A" may be either left or right port. "B" is the opposite port from "A".

3. This parameter is measured from R/WA or SEMA going HIGH to R/WB or SEMB going HIGH.

4. If tSPS is violated, the semaphore will fall positively to one side or the other, but there is no guarantee which side will obtain the flag.

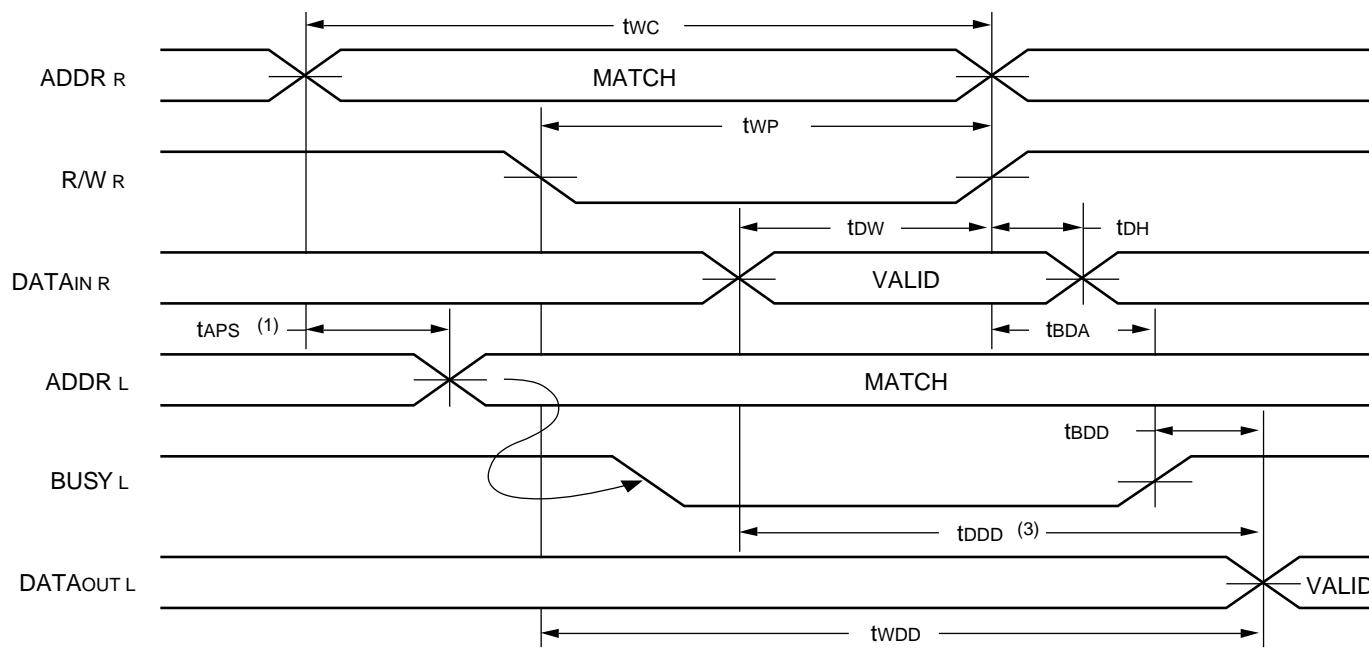

**TIMING WAVEFORM OF READ WITH  $\overline{\text{BUSY}} (\text{M/S} \geq \text{VIH})^{(2)}$**

**NOTES:**

1. To ensure that the earlier of the two ports wins.

2.  $(\text{L}_- \overline{\text{CS}} = \text{R}_- \overline{\text{CS}}) \leq \text{VIL}$

3.  $\overline{\text{OE}} \leq \text{VIL}$  for the reading port.

2795 drw 11

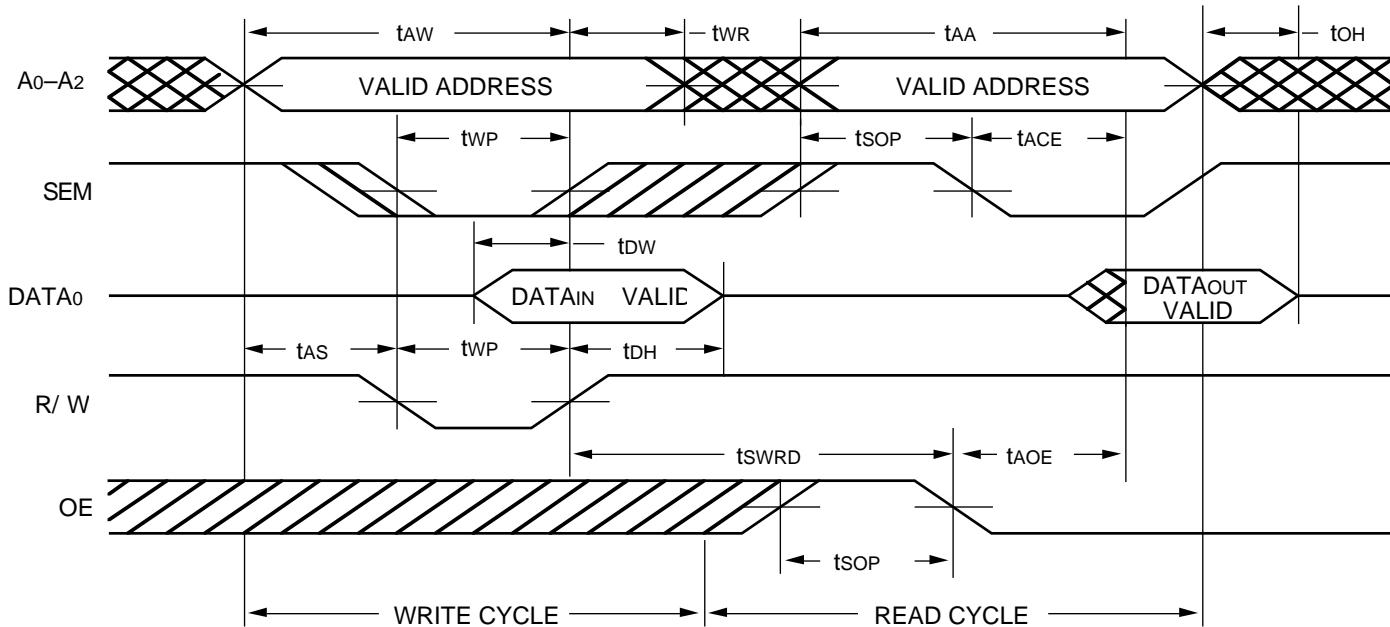

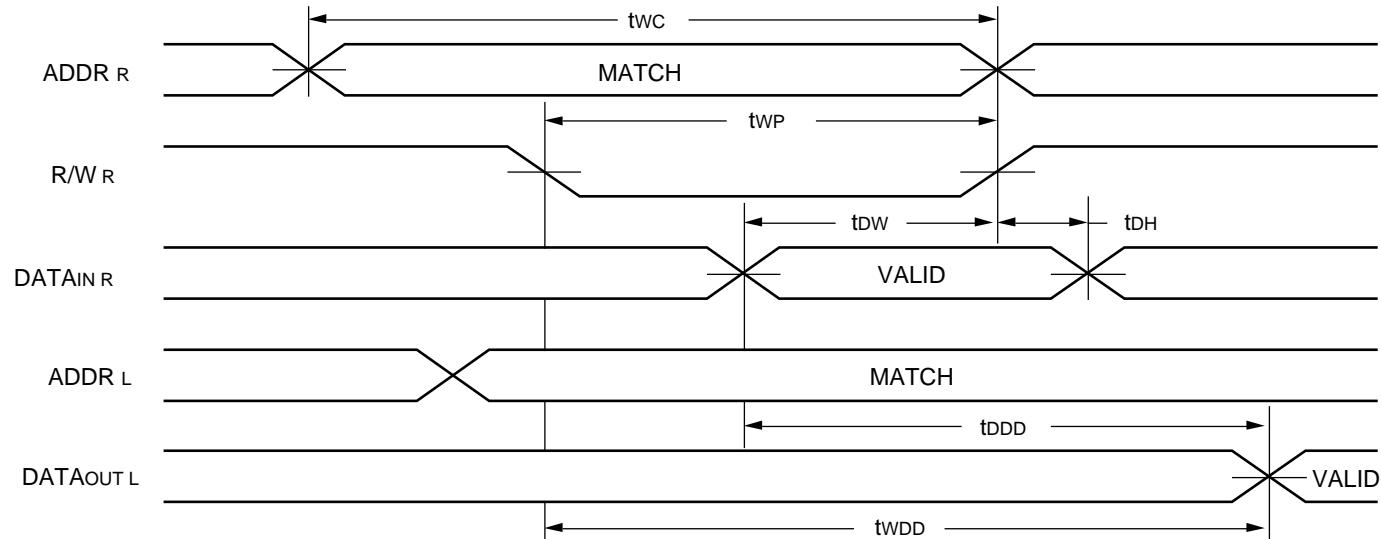

**TIMING WAVEFORM OF WRITE WITH PORT-TO-PORT DELAY ( $\text{M/S} \leq \text{VIH}$ )<sup>(1, 2)</sup>**

**NOTES:**

1.  $\overline{\text{BUSY}}$  input equals HIGH for the writing port.

2.  $(\text{L}_- \overline{\text{CS}} = \text{R}_- \overline{\text{CS}}) \leq \text{VIL}$

2795 drw 12

**TIMING WAVEFORM OF WRITE WITH  $\overline{\text{BUSY}}$  INPUT ( $M/\bar{S} \leq V_{IL}$ )**

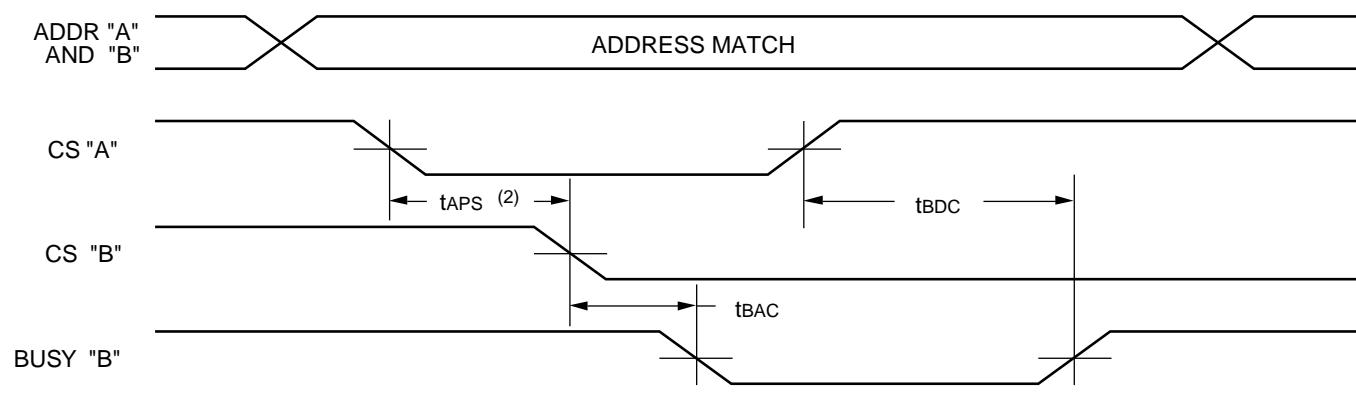

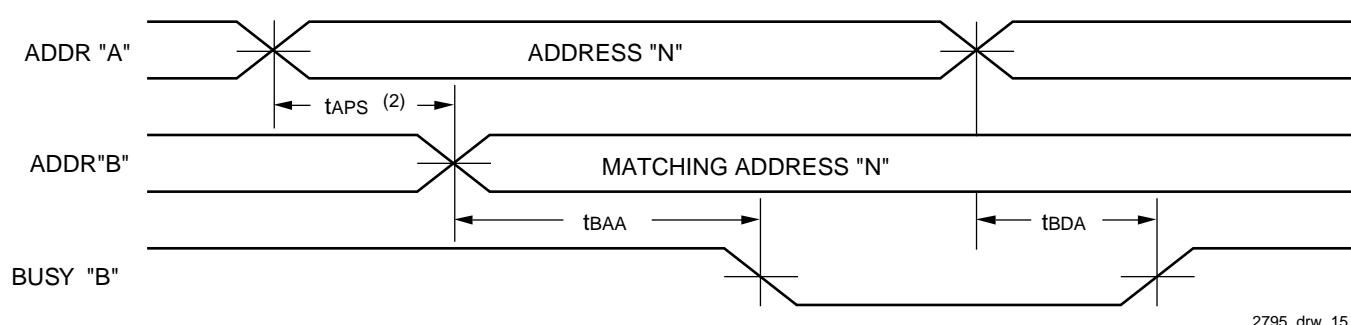

**TIMING WAVEFORM OF BUSY ARBITRATION ( $\overline{\text{CS}}$  CONTROLLED TIMING)<sup>(1)</sup>**

**TIMING WAVEFORM OF BUSY ARBITRATION (CONTROLLED BY ADDRESS MATCH TIMING)<sup>(1)</sup>**

**NOTES:**

1. All timing is the same for the left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from "A".

2. If tAPS is violated, the busy signal will be asserted on one side or another but there is no guarantee on which side busy will be asserted.

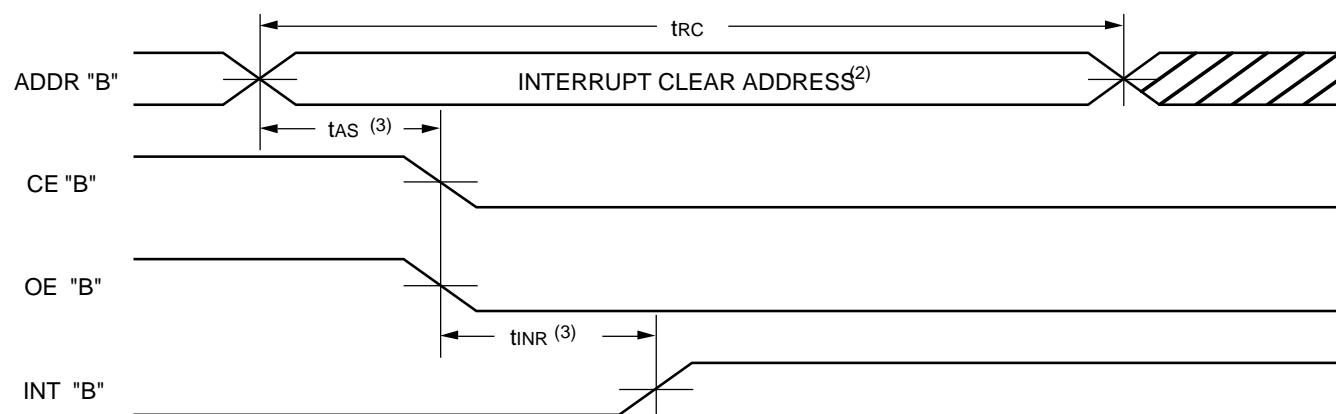

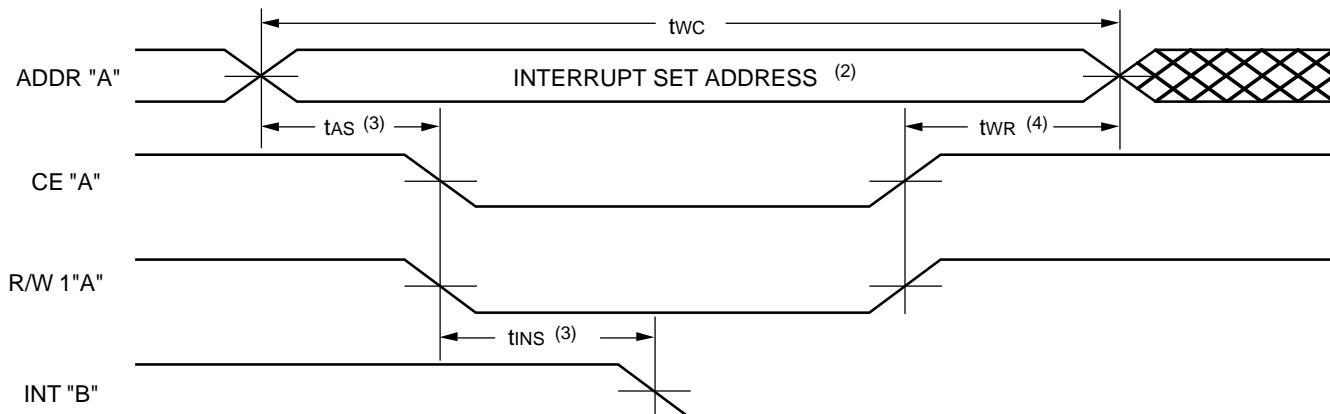

## TIMING WAVEFORM OF INTERRUPT CYCLE<sup>(1)</sup>

### NOTES:

1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from "A".

2. See Interrupt truth table.

3. Timing depends on which enable signal is asserted last.

4. Timing depends on which enable signal is de-asserted first.

## TRUTH TABLE I: Non-Contention Read/Write Control<sup>(1)</sup>

| Inputs    |            |           |            | Outputs  | Mode                     |

|-----------|------------|-----------|------------|----------|--------------------------|

| <b>CS</b> | <b>R/W</b> | <b>OE</b> | <b>SEM</b> | I/O      | Description              |

| H         | X          | X         | H          | High-Z   | Deselected or Power Down |

| L         | L          | X         | H          | Data_In  | Write                    |

| L         | H          | L         | H          | Data_OUT | Read                     |

| X         | X          | H         | X          | High-Z   | Outputs Disabled         |

### NOTE:

1. The conditions for non-contention are L\_A (0-13) ≠ R\_A (0-13).

2. ↗ denotes a LOW to HIGH waveform transition.

2795 tbl 13

## TRUTH TABLE II: Semaphore Read/Write Control

| Inputs <sup>(2)</sup> |            |           |            | Outputs  | Mode                         |

|-----------------------|------------|-----------|------------|----------|------------------------------|

| <b>CS</b>             | <b>R/W</b> | <b>OE</b> | <b>SEM</b> | I/O      | Description                  |

| H                     | H          | L         | L          | Data_OUT | Read Data in Semaphore Flag  |

| H                     | ↗          | X         | L          | Data_IN  | Write Data_IN (0, 8, 16, 24) |

| L                     | X          | X         | L          | —        | Not Allowed                  |

2795 tbl 14

## INTERRUPT/BUSY FLAGS, DEPTH & WIDTH EXPANSION, MASTER/SLAVE CONTROL, SEMAPHORES

For more details regarding Interrupt/Busy flags, depth and/or width expansion, master/slave control, or semaphore operations, please consult the IDT7006 data sheet.

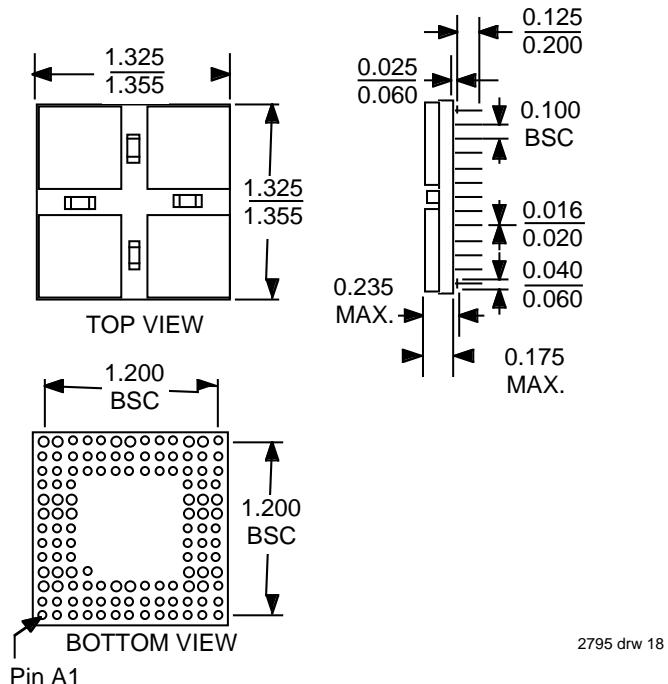

### PACKAGE DIMENSIONS

### ORDERING INFORMATION

| IDT | XXXX        | A     | 999   | A       | A                             |                                                                                       |

|-----|-------------|-------|-------|---------|-------------------------------|---------------------------------------------------------------------------------------|

|     | Device Type | Power | Speed | Package | Process/<br>Temperature Range |                                                                                       |

|     |             |       |       |         | BLANK                         | Commercial (0°C to +70°C)                                                             |

|     |             |       |       |         | B                             | Military (-55°C to +125°C) Semiconductor Components compliant to MIL-STD-883, Class B |

|     |             |       |       |         | G                             | Ceramic PGA (Pin Grid Array)                                                          |

|     |             |       |       |         | 30                            | (Commercial Only)                                                                     |

|     |             |       |       |         | 35                            | (Commercial Only)                                                                     |

|     |             |       |       |         | 40                            | (Military Only)                                                                       |

|     |             |       |       |         | 45                            | (Military Only)                                                                       |

|     |             |       |       |         |                               | Speed in Nanoseconds }                                                                |

|     |             |       |       |         | S                             | Standard Power                                                                        |

|     |             |       |       |         | 7M1002                        | 16K x 32 CMOS Dual-Port Static RAM Module                                             |

2795 drw 19

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

[www.AllDataSheet.com](http://www.AllDataSheet.com)

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

[www.AllDataSheet.com](http://www.AllDataSheet.com)