# TOSHIBA

TB2110FN

TOSHIBA BI-CMOS INTEGRATED CIRCUIT SILICON MONOLITHIC

# T B 2 1 1 0 F N

# PLL FOR DTS

The TB2110FN is a high-speed PLL LSI built in a 2 modulus prescaler that can operate with a 1.5 V power supply.

Each function is controlled via three serial bus lines, allowing you to configure a high-performance digital tuning system.

#### **FEATURES**

- Due to a Bi-CMOS structure, the 1.5 V power supply is stepped up and stabilized by a bipolar circuit to drive the CMOS section. Therefore, this chip is best suited for digital tuning system in headphone stereos.

- Built in a prescaler, This IC can operate with TV: 50~250 MHz and FM: 40~150 MHz (2 modulus type) for the FMIN input or at 0.5~40 MHz for the AMIN input (2) modulus type or directly divided).

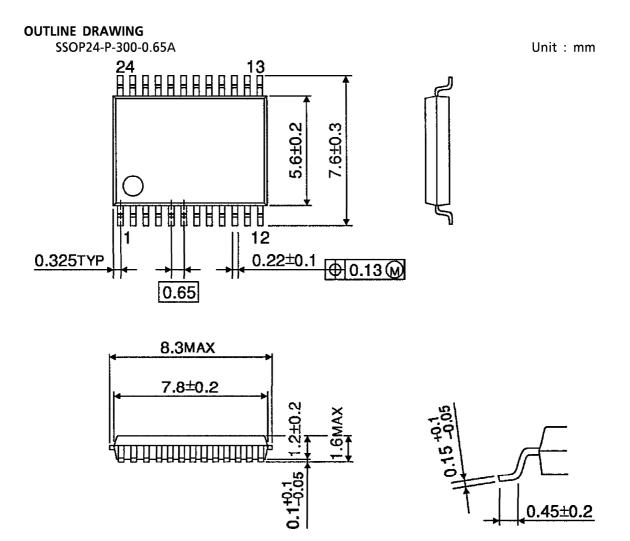

Weight: 0.31 g (Typ.)

- Comes with a 20 bit programmable counter, two parallel output phase comparators, crystal M.M.M.D.S oscillator, reference counter, and a DC/DC converter control circuit.

- The crystal oscillator (X'tal) used in this IC is a 75 kHz resonator.

- The reference frequency can be selected from seven frequencies available. (Ref =  $1.0 \sim 25 \text{ kHz}$ )

- A 20 bit general-purpose counter is built in that can measure the IF and other frequencies.

- All device operations are controlled via three serial bus lines.

- Operating voltage range :  $V_{CC} = 1.0 \sim 2.5 \text{ V}$  (Ta =  $-20 \sim 75 ^{\circ}\text{C}$ )

- Package is SSOP24pin.

f.dzsc.com

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

#### **PIN CONNECTION**

(Note) This device is vulnerable to surge voltages. Take it into account when using this device in your system.

#### **BLOCK DIAGRAM**

# PIN FUNCTION

| PIN No.          | SYMBOL                           | PIN NAME                      | FUNCTION                                                                                                     | REMARKS                                                |

|------------------|----------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 1 2              | XI<br>XO                         | Crystal oscillator pins       | Connect a 75 kHz crystal oscillator for the reference frequency to these pins.                               | 10 MΩ VDD C 300 XI |

| 3                | DATA                             | Serial data input/<br>output  | Serial I/O port. Use this pin to set the divide ratio and divide                                             | VDD Y Y YDD                                            |

| 4                | CLOCK                            | Clock signal input            | method, as well as transfer data to and from the                                                             |                                                        |

| 5                | PERIOD                           | Period signal input           | controller to control the general-purpose counter and general-purpose I/O port.                              | DATA CLOCK, PERIOD                                     |

| 6<br>7<br>8<br>9 | OUT-1<br>OUT-2<br>OUT-3<br>OUT-4 | General-purpose output port   | This is an open-collector output port. Use this port to output control signals.                              |                                                        |

| 10               | IN PORT                          | General-purpose input<br>port | This port accepts the data to be fed to the output bit (OUT-5).                                              | V <sub>DD</sub>                                        |

| 11               | VCONT                            | DC/DC converter control pin   | This pin controls the DC/DC converter.                                                                       | -V <sub>cc</sub>                                       |

| 12               | V <sub>DD</sub>                  | CMOS section power supply     | The V <sub>DD</sub> power supply from<br>the DC/DC converter is<br>applied to this pin.                      | _                                                      |

| 13               | STAND-BY                         | Standby                       | The device is placed in standby mode when a "L" is input. The device is in active state when a "H" is input. | 20 kΩ                                                  |

| 14               | IF-FM                            | General-purpose counter input | Use this pin for IF signal input on the FM side.                                                             | IF-AM (Pin 16) IF-FM (Pin 14)                          |

| 15               | V <sub>REF2</sub>                | Reference pin                 | Use this pin as the reference of the IF signal.                                                              | #                                                      |

| 16               | IF-AM                            | General-purpose counter input | Use this pin for IF signal input on the AM side.                                                             | Vref2 (Pin 15)                                         |

| 17               | A-GND                            | Bipolar section GND           | _                                                                                                            | _                                                      |

| PIN No. | SYMBOL            | PIN NAME                     | FUNCTION                                           | REMARKS                       |

|---------|-------------------|------------------------------|----------------------------------------------------|-------------------------------|

| 18      | AM-IN             | AM/SW signal input pin       | Use this pin for AM/SW signal input.               | FM-IN (Pin 20) AM-IN (Pin 18) |

| 19      | V <sub>REF1</sub> | Reference pin                | Use this pin as the reference of the AM/FM signal. |                               |

| 20      | FM-IN             | FM / TV signal input pin     | Use this pin for FM/TV signal input.               | Vref1<br>(Pin 19)             |

| 21      | V <sub>C</sub> C  | Bipolar section power supply | _                                                  | _                             |

|         |                   |                              | This is a tri-state output of                      | V <sub>DD</sub> ⊀             |

| 22      | DO1               | Phase comparator             | the phase comparator.                              |                               |

| 23      | DO2               | output                       | DO1~DO2 are parallel outputs.                      |                               |

| 24      | D-GND             | MOS section GND              | _                                                  | _                             |

#### **OPERATION**

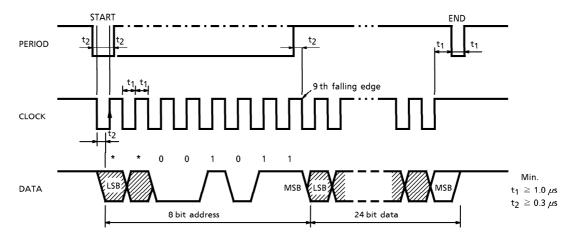

### ○ Serial I/O port

The TB2110FN has two pairs of 24 bit registers, so it can set data to a total of 48 bits to control each function. Each data in these registers are transferred to and from the controller through a serial port using three pins: DATA, CLOCK, and PERIOD. A total of 32 bits consisting of 8 bit address and 24 data bits can be handled in one serial transfer.

Because all operations are controlled via register, this section describes mainly the function of 8 bit address and each register. The registers are configured in units of 24 bits, and are selected by an 8 bit address. The address mapping of each register is listed in the next page as "Register allocation."

| REGISTER             | ADDRESS | CONTENTS OF 24 BITS                                                                         | No. OF BITS                   |

|----------------------|---------|---------------------------------------------------------------------------------------------|-------------------------------|

| Input<br>Register 1  | D0H     | PLL dividend number setting Reference frequency setting PLL input and mode setting Not used | 16<br>3<br>2<br>3<br>Total 24 |

| Input<br>Register 2  | D2H     | General-purpose counter control<br>Test bit<br>Output data<br>Not used                      | 7<br>1<br>4<br>12<br>Total 24 |

| Output<br>Register 1 | D1H     | General-purpose counter numeric data<br>Not used                                            | 22<br>2<br>Total 24           |

| Output<br>Register 2 | D3H     | Data in register D2<br>Lock detection data<br>Input data<br>Not used                        | 8<br>2<br>1<br>13<br>Total 24 |

The input data is latched into register 1 or register 2 at the falling edge of PERIOD to put each function to work.

The output data that comes in parallel is latched into the output register at the 9th falling edge of CLOCK, and is serially output from the DATA pin.

(Note)Transmit dummy data at least once before transferring regular data to initialize the device's internal circuits after power-on.

| REGISTER ALLOCATION         T—BUS format       LSB         Input register "D0" "0" "0" "1" "1" "1" "1" "1" "1" "1" " | LSB | Output register "DI"   T-bus = "D"   T-bus = | Usput register "D3" |

|----------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|----------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

TB2110FN-7

(Note 3) \* value is undecided when power on

: Don't care

(Note 2)

#### O Serial transfer format

• The serial transfer format consists of 8 bit address and 24 bit data as shown above.

The addresses used here are D0H to D3H.

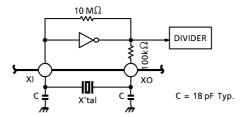

# O Crystal oscillator connecting pins (XI, XO)

Connect a crystal oscillator and capacitors to these pins as shown in Figure 1 to generate the clock required for the device's internal operation. Use a 75 kHz crystal oscillator here.

(Note)Choose a crystal oscillator that has a small CI value and good startup characteristics.

Figure 1

#### O Programmable counter

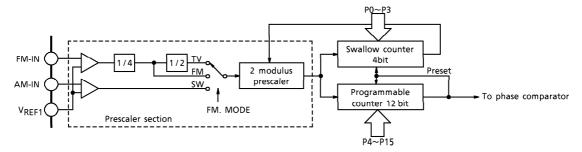

The programmable counter section consists of 1/4 + 1/2 prescalers, 2 modulus prescaler, and 4bit + 12bit programmable binary counters.

1. Setting the programmable counter section

The programmable counter need to be set for the divisor (16 bits) and the dividing mode (2 bits).

(1) Setting the dividing mode

Use the FM and MODE bit to choose the input setting and the dividing mode (pulse swallow mode or direct dividing mode). Four mode are available as listed below. Choose the desired one according to the frequency bands used.

| MODE | FM | MODE | DIVIDING MODE          | TYPICAL<br>RECEIVING BAND | INPUT FREQUENCY<br>RANGE | INPUT<br>PIN | DIVISOR |

|------|----|------|------------------------|---------------------------|--------------------------|--------------|---------|

| AM   | 0  | 0    | Direct dividing mode   | LW, MW                    | 0.5~10 MHz               | AMIN         | n       |

| SW   | 0  | 1    | Pulse swallow mode     | SW                        | 3~40 MHz                 | AIVIIII      | n       |

| FM   | 1  | 0    | 1/4+pulse swallow mode | FM                        | 40~150 MHz               | FMIN         | 4·n     |

| TV   | 1  | 1    | 1/8+pulse swallow mode | TV                        | 50~250 MHz               | FIVILIN      | 8∙n     |

(Note) 'n' denotes the set value.

#### (2) Setting the divisor

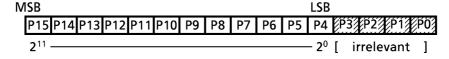

To determine the programmable counter's divisor, set binary data to the P0~P15 bits.

• For the pulse swallow mode (16 bits, SW, FM, and TV BAND)

Range of divisor set (pulse swallow mode)  $n = 210 \text{ H} \sim \text{FFFFH}$  (528~65535)

(Note) The actual divisor is 4 times the programmed number for the 1/4 + pulse swallow mode, and 8 times the programmed number for the 1/8 + pulse swallow mode.

• Direct divide method (12 bits)

Range of divisor set (direct divide mode)  $n = 10 \text{ H} \sim \text{FFFH}$  (16~4095)

(Note) In the direct divide method, the data in P0~P3 becomes irrelevant and the P4 port becomes the LSB.

- 2. Circuit configuration of prescaler and programmable counter

- (1) Circuit configuration in the pulse swallow mode

The circuit is configured with a 2 modulus prescaler, swallow counter (4 bits), and a programmable counter (12 bits).

In FM and TV modes, a 1/4 and a 1/8 prescaler are added in the front stage.

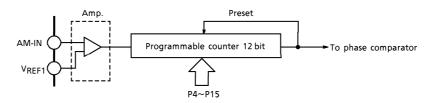

(2) Circuit configuration in the direct divide method

In the direct divide method, the prescaler section is passed through and the circuit consists of only a programmable counter (12 bits).

- (3) The FM-IN and AM-IN inputs each have a built-in amp, and are therefore capable of capacitor-coupled, small-amplitude operation.

- O Reference counter (divider to generate the reference frequency)

The reference counter section is configured with a crystal oscillator and a counter. Using a 75 kHz crystal oscillator, this circuit can generate seven types of reference frequencies.

1. Setting the reference frequency

Use the R0~R2 bits to set the reference frequency.

| R2 | R1 | R0 | REFERENCE<br>FREQUENCY |

|----|----|----|------------------------|

| 0  | 0  | 0  | 1 kHz                  |

| 0  | 0  | 1  | 3 kHz                  |

| 0  | 1  | 0  | 3.125 kHz              |

| 0  | 1  | 1  | 5 kHz                  |

| 1  | 0  | 0  | 6.25 kHz               |

| 1  | 0  | 1  | 12.5 kHz               |

| 1  | 1  | 0  | 25 kHz                 |

| 1  | 1  | 1  | Standby mode           |

When REF code = 7 H (R0~R2 = 1), the device is placed in standby mode.

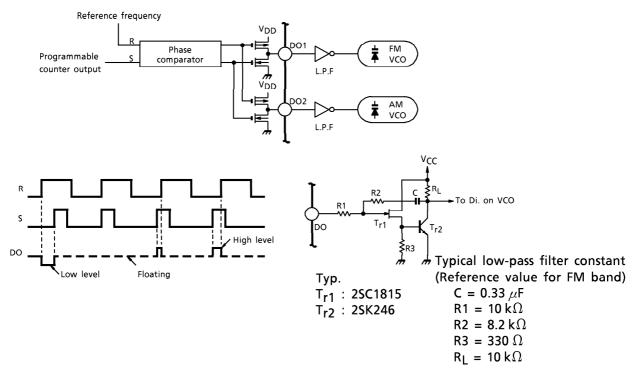

#### O Phase comparator

The phase comparator compares the phase difference between the reference frequency signal fed from the reference frequency divider and the divided output from the programmable counter, and outputs the difference. In this way it controls the VCO through a low-pass filter to ensure that the frequencies and the phases of these two signals are matched to each other.

Because this phase comparator has two tri-state buffers DO1 and DO2 connected in parallel as its outputs, you can design the optimum filter constant for each of the FM and AM bands. Furthermore, you can use the DOHZ bit of register D2 to place the DO2 output in a high-

DOHZ "1": The DO2 pin is placed in the high-impedance state.

"0": Nomal operation

impedance state as necessary.

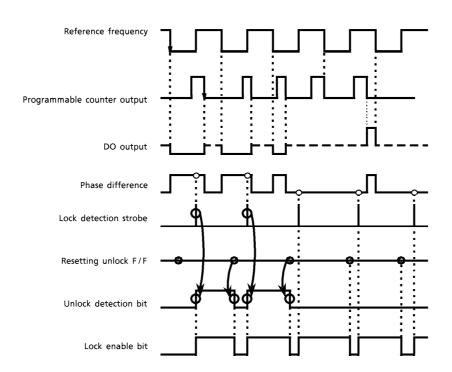

DO output timing chart

Example of an active low-pass filter circuit

Shown above is a DO output timing chart and a typical active low-pass filter circuit based on a Darlington connection of FET and bipolar transistors.

The filter circuit shown above is just one example. When designing the actual circuit, consider the band configuration and the desired characteristics of your system.

#### O Unlock detection bit

This bit is used to detect an unlock condition of the PLL circuit. When not locked (i.e., the reference frequency and the programmable counter's divided output are not locked in phase), the phase comparator outputs a pulse to the unlock F/F synchronously with the period of the reference frequency. The unlock F/F is set by this pulse. The unlock F/F is reset each time the RESET bit of register 2 (unlock reset bit) is set to 1.

After the unlock F/F is reset in this way, you can access the unlock detection bit to see if the PLL circuit is in lock condition. Because the pulse is input synchronously with the period of the reference frequency, you must wait for a duration greater than the period of the reference frequency after resetting the unlock F/F before you can access the unlock detection bit (UNLOCK). If this duration is short, you cannot detect the correct lock condition.

To solve this problem, the device has a lock enable F/F. This F/F is reset each time the unlock reset bit is set to 1, and lock enable bit is set to 1 with the unlock detection timing. This means that you can detect the correct unlock condition when the lock enable bit (ENABLE) is 1.

| ENABLE | UNLOCK | STATE  |

|--------|--------|--------|

| 0      | *      | _      |

| 1      | 0      | LOCK   |

| 1      | 1      | UNLOCK |

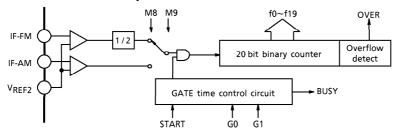

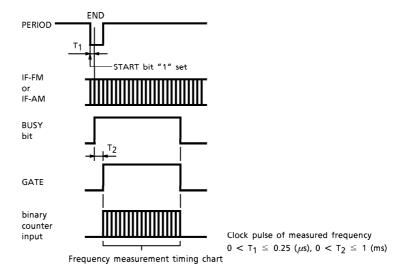

#### ○ General-purpose counter

The general-purpose counter is used to count frequencies such as the FM/AM band IF frequency to detect the auto stop signal during auto search tuning.

For this frequency counting, the general-purpose counter uses a frequency measurement (IF-AM, IF-FM input) method to count the number of pulses input to the counter during a certain duration of time (gate time).

1. General-purpose counter control bits

(1) G0, G1 bits ... These bits choose the general-purpose counter's gate time.

| G0 | G1 | GATE TIME |

|----|----|-----------|

| 0  | 0  | 1 ms      |

| 1  | 0  | 4 ms      |

| 0  | 1  | 16 ms     |

| 1  | 1  | 64 ms     |

- (2) START bit ... Each time the START bit is set to 1, measurement is restarted after resetting the general-purpose counter.

- (3) M8, M9 bits ... These bits choose the general-purpose counter's measurement mode and input pin.

| M8 | M9 | PIN<br>SELECTION | INPUT FREQUENCY<br>RANGE | REMARKS                                       |

|----|----|------------------|--------------------------|-----------------------------------------------|

| 0  | 1  | IF-AM            | 0.3~1.0 MHz              | Direct input to IF counter                    |

| 1  | 0  | IF-FM            | 8~16 MHz                 | IF frequency divided by 2 input to IF counter |

(Note)In the IF-FM mode, the general-purpose counter (20 bit binary counter) is preceded by an additionally inserted 1/2 prescaler. Therefore, the input signal from IF-FM is divided by 2 before being fed into the general-purpose counter.

- 2. General-purpose counter data output bits (f0~f19)

- (1) General-purpose counter count data bits (f0~f19)

The resulting count of the general-purpose counter can be read in binary from the output registers f0 through f19.

(2) General-purpose counter operation detect bits

| OVER ··· General-purpose counter — overflow bit | condition.                                                                                                                   |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                                                 | General-purpose counter data is valid.  General-purpose counter is counting.  General-purpose counter has finished counting. |

(Note)When using the general-purpose counter, check to see that the BUSY bit is 0 (finished counting) and that the OVER bit is 0 (valid data) before you reference the contents of the general-purpose counter data bits (f0~f19).

#### 3. Circuit configuration of general-purpose counter

The general-purpose counter section is configured with an input amp., a gate time control circuit, and a 20 bit binary counter.

#### 4. Measurement timing of general-purpose counter

(Note) IF-FM and IF-AM are capable of C-coupled, small-amplitude operation using a bipolar input.

#### O General-purpose input/output ports

The device has general-purpose input/output ports controlled by serial port.

1. General-purpose output ports (OT-1~OT-4)

The data set to the O1~O4 bits of input register 2 are output in parallel from their dedicated output ports OT-1~OT-4.

2. General-purpose input port (IN)

The data input from the IN pin can be read out from the DATA pin as OUT-5 of the output register.

(Note)The output ports are set to "0" when the device is powered on. (Therefore, the general-purpose output ports are held Low at power-on.)

(Note)The TS bit of input register 2 must always be set to "0".

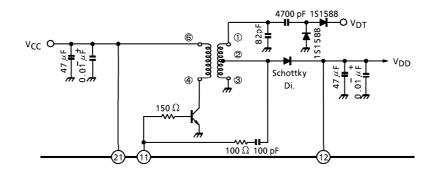

# O DC/DC converter

The TB2110FN uses a coil-type DC/DC converter (boosted voltage circuit) to allow for low-voltage operation.

Coil: (SUMIDA ELECTRIC CO., LTD, CP-4LB)

| TEST      | L (μH) 1-3 CO (pF) |   | (O (pE)   OO |     | TURNS | WIRE (mm $\phi$ ) |                 |

|-----------|--------------------|---|--------------|-----|-------|-------------------|-----------------|

| FREQUENCY |                    |   | QU           | 1-2 | 2-3   | 6-4               | VVIKE (IIIIIIφ) |

| 2.52 MHz  | 15.6 ± 3%          | _ | _            | 18T | 14T   | 2T                | 0.08 UEW        |

#### **BOTTOM VIEW**

# MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                   | UNIT |

|-----------------------|------------------|--------------------------|------|

| Supply Voltage        | $V_{DD}$         | - 0.3~4.5                | V    |

| Input Voltage         | VIN              | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Power Dissipation     | PD               | 400                      | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>- 20∼75</b>           | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>- 65∼150</b>          | °C   |

ELECTRICAL CHARACTERISTICS (Unless otherwise specified, Ta =  $-20\sim75^{\circ}$ C, V<sub>CC</sub> =  $1.0\sim2.5$  V, V<sub>DD</sub> = 2.4 V)

| CHARACT                   | ERISTIC                        | SYMBOL   | TEST<br>CIR-<br>CUIT | TEST CONDITION                               | MIN. | TYP. | MAX. | UNIT |

|---------------------------|--------------------------------|----------|----------------------|----------------------------------------------|------|------|------|------|

| Operating<br>Power Supply | Biplor Unit                    | VCC      |                      | PLL operation<br>(Normal operating)          | 1.2  | 1.5  | 2.5  | ٧    |

| Voltage                   | MOS Unit                       | $V_{DD}$ |                      | Step-up control circuit operating            | 2.2  | 2.4  | 3.6  |      |

| Operating Pov             | wer Supply                     | lcc      |                      | PLL operation<br>(Normal operating), TV mode |      | 18   | 40   | m ^  |

| Current                   | Operating Power Supply Current |          |                      | PLL operation<br>(Normal operating), TV mode | -    | 1.5  | 7    | mA   |

# (Stand-by mode)

| Operating Power Supply | lec | Vcc - 15V                   | <br>30 | 50 | μA      |

|------------------------|-----|-----------------------------|--------|----|---------|

| Current                | ics | ν <u>(</u> ( = 1.5 <b>ν</b> | 30     | 3  | $\mu$ A |

# (Operating frequency)

| Crystal Oscillation<br>Frequency | fxT                | _ | Crystal oscillator connected to XI and XO pins. | _   | 75 | _   | kHz |

|----------------------------------|--------------------|---|-------------------------------------------------|-----|----|-----|-----|

| TV in                            | fTV                | _ | TV mode                                         | 50  | ~  | 250 | MHz |

| FM in                            | f <sub>FM</sub>    | _ | FM mode                                         | 40  | ~  | 150 | MHz |

| SW in                            | fsw                | _ | SW mode                                         | 3   | ~  | 40  | MHz |

| AM in                            | fAM                | _ | AM mode                                         | 0.5 | ~  | 10  | MHz |

| IF-FM                            | f <sub>IF-FM</sub> | _ | IF-FM                                           | 8   | ~  | 16  | MHz |

| IF-AM                            | f <sub>IF-AM</sub> | _ | IF-AM                                           | 0.3 | ~  | 1.0 | MHz |

# (Input voltage)

| TV in | V <sub>TVin</sub>  | _ | TV mode |    |   |     |                   |

|-------|--------------------|---|---------|----|---|-----|-------------------|

| FM in | V <sub>FMin</sub>  | _ | FM mode |    | _ | 300 |                   |

| SW in | V SWin             | _ | SW mode | 25 |   |     | m\/               |

| AM in | V <sub>AMin</sub>  | _ | AM mode | 23 |   |     | mV <sub>rms</sub> |

| IF-FM | V <sub>IF-FM</sub> | _ | IF-FM   |    |   |     |                   |

| IF-AM | V <sub>IF-AM</sub> | _ | IF-AM   |    |   |     |                   |

# (OT-1~OT-4 open-collector output current)

| CHARACT           | ERISTIC   | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION   | MIN. | TYP. | MAX. | UNIT |

|-------------------|-----------|------------------|----------------------|------------------|------|------|------|------|

| Output<br>Current | "L" Level | l <sub>OL1</sub> |                      | $V_{OL} = 0.2 V$ | 1.0  | 3.0  |      | mA   |

# (DATA, CLOCK, PERIOD, I/O)

| Input   | "H" Level | $V_{IH}$         | _ | _                                      | 1.7   | ~     | $V_{DD}$ | V       |

|---------|-----------|------------------|---|----------------------------------------|-------|-------|----------|---------|

| Voltage | "L" Level | $V_{IL}$         | _ | _                                      | 0.0   | ?     | 0.5      | V       |

| Input   | "H" Level | lін              | _ | V <sub>IH</sub> = 2.4 V                | _     | _     | ± 0.5    |         |

| Current | "L" Level | IJL              | _ | V <sub>IL</sub> = 0.0 V                | _     | _     | ± 1.0    | $\mu$ A |

| Output  | "H" Level | I <sub>OH2</sub> | _ | V <sub>OH</sub> = 2.0 V, Only DATA pin | - 0.2 | - 1.0 | _        | A       |

| Current | "L" Level | l <sub>OL2</sub> | _ | V <sub>OL</sub> = 0.4 V, Only DATA pin | 0.2   | 1.0   | _        | mA      |

# (DO1, DO2)

| Input          | "H" Level | IOH3             | _ | $V_{OH} = 2.0 V$                   | - 0.2 | - 1.0 |       | mA |

|----------------|-----------|------------------|---|------------------------------------|-------|-------|-------|----|

| Voltage        | "L" Level | l <sub>OL3</sub> | - | $V_{OL} = 0.4 V$                   | 0.2   | 1.0   |       |    |

| Tri-State Leak | Current   | lTL              | 1 | $V_{TLH} = 2.4 V, V_{TLL} = 0.0 V$ |       |       | ± 0.1 | μΑ |

| Auto Clear Voltage | V <sub>CL1</sub> | _ | Clear release voltage | _   |  | 1.9 | V     |

|--------------------|------------------|---|-----------------------|-----|--|-----|-------|

|                    | $V_{CL2}$        | - | Clear voltage         | 1.4 |  |     | \ \ \ |

| Vacan Output Current             |        |   | Boosting voltage transistor drive    | 100 | 150 |     |         |

|----------------------------------|--------|---|--------------------------------------|-----|-----|-----|---------|

| V <sub>CONT</sub> Output Current | ICONT  | _ | current<br>V <sub>CONT</sub> = 0.8 V | 100 | 150 | _   | $\mu$ A |

| Standby Release                  | VSTOFF | _ | Standby mode released                | 0.7 | ~   | ۷cc | V       |

| Standby Mode                     | VSTON  | _ | Placed in standby mode               | 0.0 | ~   | 0.6 | V       |

Weight: 0.31 g (Typ.)