TOSHIBA BI-CMOS INTEGRATED CIRCUIT SILICON MONOLITHIC

# TB31206FN, TB31206AFN

## PLL FREQUENCY SYNTHESIZER

### **FEATURES**

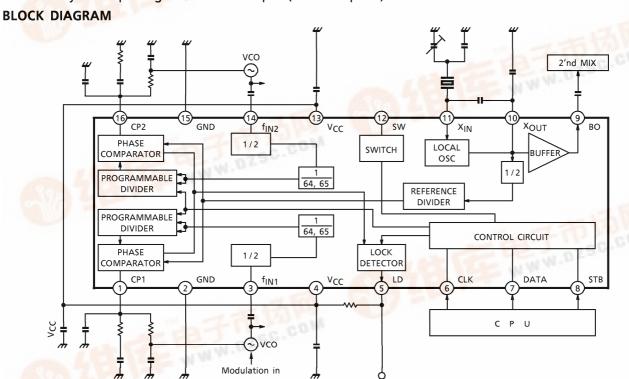

One packaging CH1/CH2 two systems prescaler and PLL.

Low operating power supply voltage

$V_{CC} = 2.7 \sim 5.5 \text{ V}$

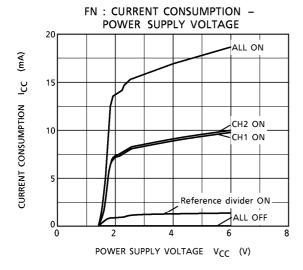

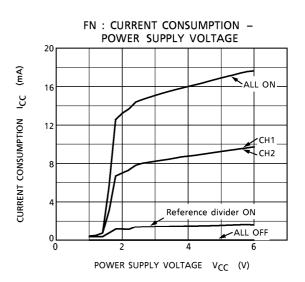

Low current consumption

FN : I<sub>CC</sub> = 16.5 mA (Typ.)

AFN :  $I_{CC} = 14.5 \text{ mA (Typ.)}$

• Input frequency :  $f_{IN} = 520 \sim 1100 \text{ MHz}$

• High input sensitivity :  $V_{IN} = 92 \sim 107 \, dB \mu V$

Charge pump is constant current type, and is able to change output current by serial data

Reference oscillation circuit is adopted circuit of bipolar, so getting the stable X'tal oscillation circuit

Available standby control in CH1 and CH2 independent of each other

• The very small package : SSOP16pin (0.65 mm pitch)

Weight: 0.07 g (Typ.)

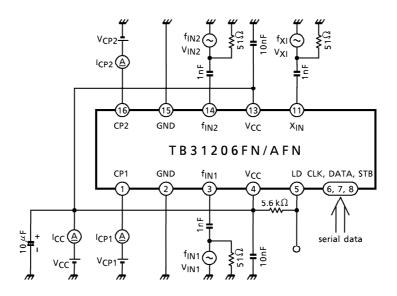

### PIN FUNCTION (The values of resistor and capacitor are typical.)

| PIN<br>No. | PIN<br>NAME      | FUNCTION                                                                                                      |                                                                 | INTERNAL EQUIVALENT CIRCUIT |  |  |  |

|------------|------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------|--|--|--|

| 1          | CP1              | Output terminal of charge pump<br>Charge pump is constant current                                             | Vcc                                                             |                             |  |  |  |

| 16         | CP2              | output current is varied by inpu                                                                              | t serial data.                                                  | GND SND                     |  |  |  |

| 2          | GND              | GND Terminal.                                                                                                 |                                                                 |                             |  |  |  |

| 15         | GND              | GIVE Terrimian.                                                                                               |                                                                 | _                           |  |  |  |

| 3          | fIN1             | Input terminal of RF oscillation s                                                                            | signal.                                                         | VCC                         |  |  |  |

| 14         | fIN2             |                                                                                                               |                                                                 | GND GND                     |  |  |  |

| 4          | Vcc              | Power Supply Terminal.                                                                                        |                                                                 |                             |  |  |  |

| 13         | Vcc              |                                                                                                               |                                                                 |                             |  |  |  |

| 5          | LD               | Output terminal of lock detector It is the open drain output.                                                 | S 200Ω ——————————————————————————————————                       |                             |  |  |  |

| 12         | SW               | Switchover terminal for constant It is the open drain output. When don't switch constant of I general output. | V <sub>CC</sub> 200Ω 12 4 4 5 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 |                             |  |  |  |

| 6          | CLK              | Input terminal of clock.                                                                                      |                                                                 | 6 1kΩ                       |  |  |  |

| 7          | DATA             | Input terminal of serial data.                                                                                | Input the serial data for controlling IC.                       | 7 8 4                       |  |  |  |

| 8          | STB              | Input terminal of strobe signal.                                                                              |                                                                 | <i>m</i>                    |  |  |  |

| 9          | во               | Output terminal of buffer amplitude The signal of local oscillation is buffer amplifier.                      | V <sub>CC</sub> 100Ω 5 6 w                                      |                             |  |  |  |

| 10         | X <sub>OUT</sub> | Output terminal of local oscillati                                                                            | 10 + 1002/                                                      |                             |  |  |  |

| 11         | Χ <sub>IN</sub>  | Input terminal of local oscillation<br>In case of external input, connecterminal.                             | 9 500Ω 1kΩ GND                                                  |                             |  |  |  |

### **DESCRIPTION OF FUNCTION AND OPERATION**

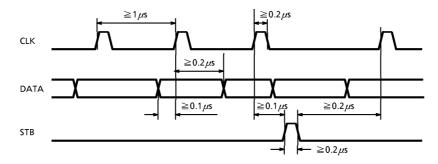

- 1. Entry of serial data

- Serial data used to control the IC is input through three terminals, CLK, DATA and STB.

- ① During the rise of a clock pulse, data is fed to the shift register in the IC in order from the LSB.

- ② Upon the reception of all data, the strobe signal (STB) is made "H".

- 3 After the situation of 2, the data stored in the shift register is transferred to the latch in the block selected by the group code, whereby the IC is controlled.

- The three terminals, CLK, DATA and STB, contains Schmitt trigger circuits to prevent the data errors by noise, etc.

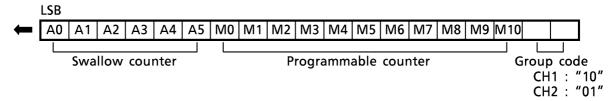

- O Serial data group and group code

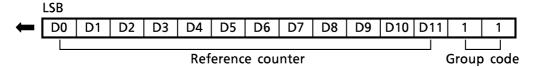

- The IC has control divided into four groups so that they may be controlled independent of one another. Each group is identified by a two-bit group code attached at the data end.

| CODE | ITEM                                                                |

|------|---------------------------------------------------------------------|

| 10   | Number of divisions by CH1 programmable divider (f <sub>IN1</sub> ) |

| 01   | Number of divisions by CH2 programmable divider (f <sub>IN2</sub> ) |

| 11   | Number of divisions by reference divider (X <sub>IN</sub> )         |

| 00   | Optional control                                                    |

### O Serial data input timing

- 2. CHANNEL dividers (CH1, CH2)

- These programmable dividers are composed of a half fixed divider, a 6bit swallow counter (6bit programmable divider), a 11bit programmable counter, and a two-modulars prescaler providing 64 and 65 divisions.

- The strategy of a swallow counter is used to set high reference frequency.

- Sending certain data to the swallow counter and the programmable counter allows the setting of any of 8064 to 262142 divisions (multiple of two).

- The programmable counter and swallow counter are set by each channel. Each channel is specified by a group code.

$\begin{cases} A = A0 + A1 \times 2^{1} + \cdots + A5 \times 2^{5} \\ M = M0 + M1 \times 2^{1} + \cdots + M10 \times 2^{10} \\ \text{Number of divisions} = 2 (64N + A) \\ 8064 \leq \text{Number of divisions} \leq 262142 \end{cases}$

(EX) A Signal of 900MHz is entered into  $f_{\text{IN1}}$ , being divided into 25.0kHz step. (Reference frequency is 12.5kHz)  $900\times10^6\div(25.0\times10^3\div2)=72000$   $72000=2\ (64N+A)$   $\therefore$  N = 562, A = 32

- 3. Reference divider

- This block generates the reference frequency for the PLL.

- This reference divider is composed of a 12bit reference counter and a half fixed divider.

- Sending certain data to the reference divider allows the setting of any of 6 to 8190 divisions (multiple of two).

$\begin{cases}

D = D0 + D1 \times 2^{1} + \dots D10 \times 2^{10} + D11 \times 2^{11} \\

\text{Number of divisions} = 2D \\

6 \le \text{Number of divisions} \le 8190

\end{cases}$

(EX) With a 12.8MHz X'tal oscillator connected, being divided into 25.0kHz step. (Reference frequency is 12.5kHz)  $12.8\times10^6\div(25.0\times10^3\div2)=1024$  2D=1024

4

$\therefore$  D = 512

2002-03-29

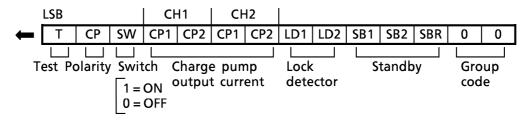

### 4. Optional control

- The optional control below is available.

- 1) Test mode (Usually set up T = "0").

- ② Control and polarity control of the charge pump output current for each channel.

- 3 Output terminal for lock detector.

- 4 Standby control of CH1, CH2 and reference divider.

- ⑤ Control of filter switch.

T: Bit for test mode

CP : Switchover bit for charge pump output polarity

SW : Control bit for filter switch

CP1, 2: Switchover bit for charge pump output current

LD1, 2: Control bit for lock detector output SB1, 2: Standby control bit for CH1, CH2

SRB : Standby control bit for reference divider

- Description of options including their control

- ① Test mode (T)

Bit "T" is for test mode. In other than the test mode, set this bit at "0".

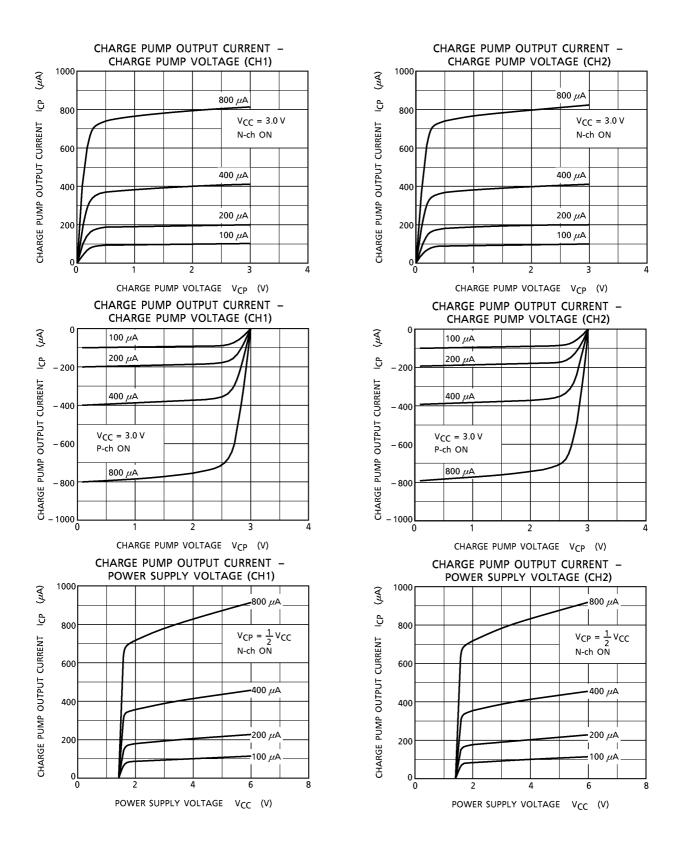

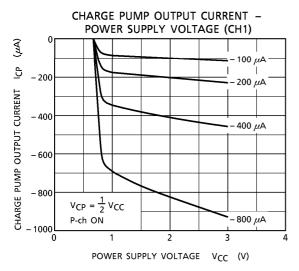

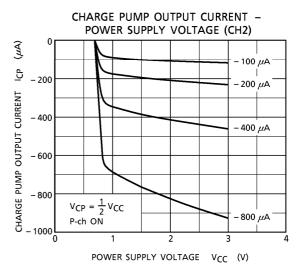

2 Control of charge pump output current (CP1, CP2)

This IC uses a constant current output type charge pump circuit. Output current is varied by serial data "CP1" and "CP2".

### **CHARGE PUMP OUTPUT CURRENT**

| CONTR | OL BIT | CHARGE PUMP    |  |  |

|-------|--------|----------------|--|--|

| CP1   | CP2    | OUTPUT CURRENT |  |  |

| 0     | 0      | ± 100μA        |  |  |

| 0     | 1      | ± 200μA        |  |  |

| 1     | 0      | ± 400μA        |  |  |

| 1     | 1      | ±800μA         |  |  |

High speed lock up is possible by switching charge pump output current.

5

Charge pump output polarity (CP)

Bit "CP" can be reversed charge pump output polarity.

### CHARGE PUMP OUTPUT POLARITY

| СР | OUTPUT POLARITY |

|----|-----------------|

| 0  | Normal          |

| 1  | Reverse         |

### 3 Lock detector output

When phase comparator detects phase difference, LD terminal (pin 5) outputs "L". When phase comparator locks, LD terminal outputs "H". On standby, outputs "H". LD terminal output is controlled by "SB1", "SB2", "LD1" and "LD2".

|     | CONTR | OL BIT |     | - 5PIN OUTPUT   |                        |                    |   |   |   |   |   |  |

|-----|-------|--------|-----|-----------------|------------------------|--------------------|---|---|---|---|---|--|

| SB1 | SB2   | LD1    | LD2 | 3 SPIN OUTPUT   |                        |                    |   |   |   |   |   |  |

|     |       | 0      | 0   | L               |                        |                    |   |   |   |   |   |  |

| 0   | 0     | 0      | 1   | CH2 only detect |                        |                    |   |   |   |   |   |  |

|     | 0     | 1      | 0   | CH1 only detect | Logical multiplication |                    |   |   |   |   |   |  |

|     |       | 1      | 1   | CH1 * CH2       | → (AND) of CH1, CH2    |                    |   |   |   |   |   |  |

|     |       | 0      | 0   | L               | (, c, c                |                    |   |   |   |   |   |  |

| 0   | 1     | 0      | 1   | Н               |                        |                    |   |   |   |   |   |  |

|     |       | '      | 1   | 0               | CH1 only detect        | About SB1, SB2 bit |   |   |   |   |   |  |

|     |       | 1      | 1   | CH1 only detect | □ Normal operation     |                    |   |   |   |   |   |  |

|     | 0     |        | 0   | 0               | L                      | l                  |   |   |   |   |   |  |

| 1 1 |       | 0      | 1   | CH2 only detect | ∟1 : Standby           |                    |   |   |   |   |   |  |

| '   |       | U      | U   | U               | U                      | U                  | U | U | 1 | 0 | Н |  |

|     |       | 1      | 1   | CH2 only detect |                        |                    |   |   |   |   |   |  |

|     |       | 0      | 0   | L               |                        |                    |   |   |   |   |   |  |

| 1   | 1     | 0      | 1   | Н               |                        |                    |   |   |   |   |   |  |

| '   | '     | 1      | 0   | Н               |                        |                    |   |   |   |   |   |  |

|     |       | 1      | 1   | Н               |                        |                    |   |   |   |   |   |  |

6

2002-03-29

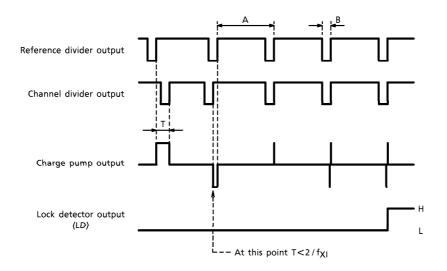

f<sub>XI</sub> .. X<sub>IN</sub> operating frequency (X'tal OSC)

T .... The time difference of the pulse between reference divider output and channel divider output. (Phase difference)

fpc .. Phase comparison frequency

$$A = \frac{Number of divisions by reference divider}{f_{XI}} (s) = \frac{1}{f_{PC}} (s)$$

$$B = 2 / f_{XI} (s)$$

When the situation that T is less than B (T<B) continues more than 3/fpC (s), lock detector outputs "H".

### 4 Standby control (SB1, SB2, SBR)

Standby control by three bits (SB1, SB2, SBR).

Bits "SB1" and "SB2" do standby control of CH1, CH2. Bit "SBR" does standby control of reference divider.

| С   | ONTROL BI | T   | STATE |     |                      |                      |

|-----|-----------|-----|-------|-----|----------------------|----------------------|

| SB1 | SB2       | SBR | CH1   | CH2 | REFERENCE<br>DIVIDER |                      |

| 0   | 0         | *   | ON    | ON  | ON                   | ¬                    |

| 0   | 1         | *   | ON    | OFF | ON                   | Interlocking<br>mode |

| 1   | 0         | *   | OFF   | ON  | ON                   | 7                    |

| 1   | 1         | 0   | OFF   | OFF | ON                   | — REFERENCE          |

| 1   | 1         | 1   | OFF   | OFF | OFF                  | DIVIDER ON mode      |

Note: \* is don't care.

2002-03-29

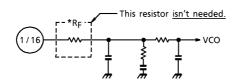

### **⑤** Filter switch control (SW)

Control of SW terminal by bit "SW".

This terminal is for switching constant of loop filter.

Output type of this terminal is open drain output. Switching the resistor of loop filter by this terminal with switching charge pump output current, high mode and normal mode can operate PLL by ideal braking factor.

When constant of loop filter don't change switch, available general output.

### FILTER SWITCH CONTROL

| SW | OUTPUT |  |

|----|--------|--|

| 0  | OFF    |  |

| 1  | ON     |  |

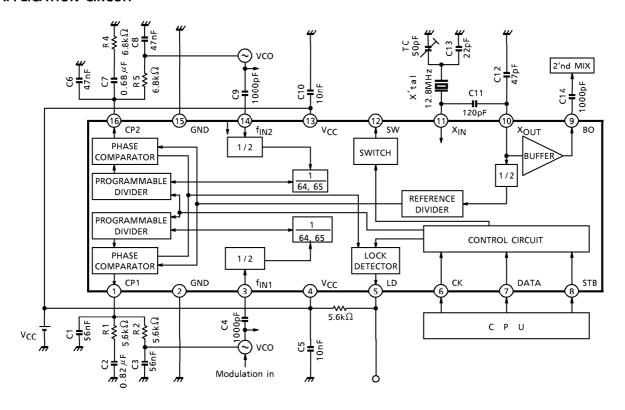

### 5. X'tal oscillation circuit and buffer amplifier

This IC has a stable oscillation circuit composed of bipolar.

In case of the external input of reference frequency directly, use X<sub>IN</sub> terminal (pin 11). For the common use of X'tal of the X'tal oscillation circuit for the PLL and X'tal of the local oscillation to 2'nd MIX, output terminal of local oscillation signal with buffer amplifier (pin 9) may be used.

This terminal (pin 9) is provided with a buffer amplifier.

TOSHIBA TB31206FN/AFN

### **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING   | UNIT |

|-----------------------|------------------|----------|------|

| Power Supply Voltage  | Vcc              | 6        | V    |

| Power Dissipation     | PD               | 560      | mW   |

| Operating Temperature | T <sub>opr</sub> | - 30~85  | °C   |

| Storage Temperature   | T <sub>stg</sub> | - 55~150 | °C   |

### **ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified, V<sub>CC</sub> = 3.0V, Ta = 25°C)

| CHARACTERISTIC                         | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                           | MIN.                      | TYP.            | MAX.                      | UNIT     |  |

|----------------------------------------|------------------|----------------------|----------------------------------------------------------|---------------------------|-----------------|---------------------------|----------|--|

| Operating Power<br>Supply Voltage      | Vcc              | 1                    |                                                          | 2.7                       | 3.0             | 5.5                       | V        |  |

| Operating Current<br>Consumption : FN  | 1                | 1                    | CH1, CH2 operating                                       | 1                         | 16.5            | 21.5                      | mΛ       |  |

| Operating Current<br>Consumption: AFN  | lccQ             | '                    | Chi, Ch2 operating                                       | _                         | 14.5            | 19.5                      | mA       |  |

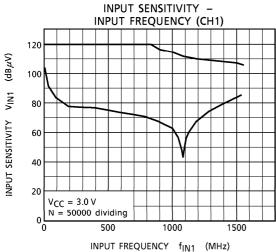

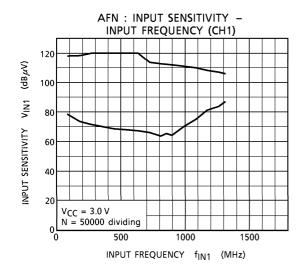

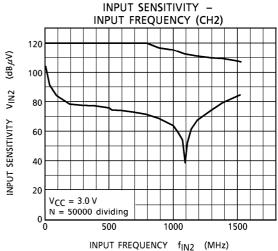

| f <sub>IN</sub> Operating              | fIN1             | 1                    | $V_{\text{IN1}} = 92 \sim 107 \text{dB} \mu \text{V}$ *1 | 520                       | _               | 1100                      | MHz      |  |

| Frequency                              | fIN2             | 1                    | $V_{1N2} = 92 \sim 107 dB \mu V$ *1                      | 520                       | _               | 1100                      | IVITZ    |  |

| for Input Consistivity                 | V <sub>IN1</sub> | 1                    | f <sub>IN1</sub> = 520~1100MHz *1                        | 92                        | _               | 107                       | dD\/     |  |

| f <sub>IN</sub> Input Sensitivity      | $V_{IN2}$        | 1                    | $f_{1N2} = 520 \sim 1100 MHz$ *1                         | 92                        | _               | 107                       | $dB\muV$ |  |

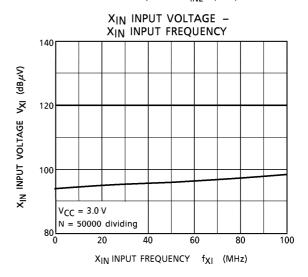

| X <sub>IN</sub> Operating<br>Frequency | fxı              | 1                    | $V_{XI}$ = 102~112dB $\mu$ V Sin-wave*1                  | 5                         | _               | 25                        | MHz      |  |

| X <sub>IN</sub> Input Voltage          | V <sub>XI</sub>  | 1                    | f <sub>XI</sub> = 5~25MHz                                | 102                       | 107             | 112                       | $dB\muV$ |  |

| Input Voltage                          | V <sub>IH</sub>  | _                    | STB, DATA, CLK                                           | V <sub>C</sub> C<br>× 0.8 | V <sub>CC</sub> | 5.7                       | V        |  |

| imput voitage                          | V <sub>IL</sub>  |                      | STB, DATA, CLK                                           | - 0.2                     | 0               | V <sub>C</sub> C<br>+ 0.2 | 1 "      |  |

| CLK Input Frequency                    | fCLK             | _                    | CLK                                                      |                           | _               | 1.0                       | MHz      |  |

|                                        | I <sub>CP1</sub> | 1                    | "CP1" = 0, "CP2" = 0, $V_{CP} = 1.5V$                    |                           | ± 100           | _                         |          |  |

| Charge Pump Output                     | I <sub>CP2</sub> | 1                    | "CP1" = 0, "CP2" = 1, $V_{CP} = 1.5V$                    |                           | ± 200           | _                         |          |  |

| Current                                | ICP3             | 1                    | "CP1" = 1, "CP2" = 0, V <sub>CP</sub> = 1.5V             |                           | ± 400           | _                         | $\mu$ A  |  |

|                                        | I <sub>CP4</sub> | 1                    | "CP1" = 1, "CP2" = 1, V <sub>CP</sub> = 1.5V             | _                         | ±800            | _                         |          |  |

| Charge Pump OFF Leak<br>Current        | CPOFF            | 1                    | Standby mode, $V_{CP} = 1.5V$                            | - 1.0                     | _               | 1.0                       | μΑ       |  |

<sup>\*1:</sup> When input is terminated with 50  $\!\Omega.$

### **REFERENCE DATA** (Typ.)

|     | () [, |           |            |      |         |  |

|-----|-------|-----------|------------|------|---------|--|

| CH1 | CH2   | REFERENCE | CURRENT CC | UNIT |         |  |

| СПІ | CHZ   | DIVIDER   | FN         | AFN  | UNIT    |  |

| N   | N     | ON        | 16.5       | 14.5 | mA      |  |

| N   | S     | ON        | 9.0        | 8.0  | mΑ      |  |

| S   | N     | ON        | 9.0        | 8.0  | mA      |  |

| S   | S     | ON        | 1.4        | 1.4  | mΑ      |  |

| S   | S     | OFF       | 0          | 0    | $\mu$ A |  |

N: Normal operating

S : Standby mode

### **TEST CIRCUIT**

### **APPLICATION CIRCUIT**

### Set up conditions (E-TACS)

Frequency bandwidth ; 32.975MHz

Frequency probability error ; ±1kHz

3. Lock up time ; 30ms (calculated value)

4. X'tal frequency ( $f_{XI}$ ) ; 12.8MHz 5. Phase comparison frequency ( $f_{PC}$ ) ; 12.5kHz 6. Charge pump current ( $I_{CP}$ ) ; 800 $\mu$ A

TX (CH1)

·VCO frequency ; 888.5MHz (center)

·VCO conversion sensitivity ; 14MHz/V

RX (CH2)

·VCO frequency ; 978.5MHz (center)

·VCO conversion sensitivity ; 13MHz/V

Weight: 0.07 g (Typ.)

# PACKAGE DIMENSIONS SSOP16-P-225-0.65B Unit : mm 0.23TYP 0.65 5.5MAX 5.0±0.2 0.45±0.2

### **RESTRICTIONS ON PRODUCT USE**

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- ◆ The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.