# PLL-Frequenzsynthesizer mit 3-Leiter-Bus

CMOS-Schaltung

| Тур       | Bestellnummer | Gehäuse        |

|-----------|---------------|----------------|

| TBB 206   | Q67100-H8722  | P-DIP-14       |

| TBB 206 G | Q67100-H8723  | P-DSO-14 (SMD) |

### Vorläufige Daten

Der TBB 206 ist ein CMOS-IC, der speziell für den Einsatz in batteriebetriebenen Funkgeräten und Telefonen entwickelt wurde, und ist u.a. für den Einsatz in GSM Konzepte vorgesehen. Er ist sowohl für einfache Frequenzsynthese als auch Dual-Modulus-Synthese geeignet.

#### Eigenschaften

- Serieller Bus (3-Leiter-Bus: Data, Clock, Enable) für schnelle Programmierung (f<sub>max</sub> ~ 1,3 MHz)

- Modulus-Umschaltung

- mitintegrierter Spannungsverdoppler f

ür großen Phasendetektoraussteuerbereich

- hohe Eingangsempfindlichkeit (100 mV), hohe Eingangsfrequenzen (90 MHz)

bei Single-Modulus-Betrieb (bei U<sub>DD</sub> = 5 V, T<sub>U</sub> = 25 °C)

- geringe Betriebsstromaufnahme (typ. 2,5 mA)

- Standby-Schaltung

- extrem schneller Phasendetektor mit sehr kurzem Antibacklashimpuls

- Linearisierung des Phasendetektorausganges durch Stromquellen

- große Teilerverhältnisse für kleine Rasterfrequenzen

A-Teiler 0 bis 127

N-Teiler 3 bis 4095

R-Teiler 3 bis 65535

- Polarität und Nachstimmsteilheit des Phasendetektors durch Bus umschaltbar

- synchrone Programmierung der Teiler (N(N/A), R-Teiler)

- 2 Multifunktionsausgänge (über Bus steuerbar)

ØR, ØVN (digitale Phasendetektorausgangssignale

(z. B. für externe Charge-Pump)

FRN, FVN Ausgänge der R- und N-Teiler

- PRFT 1, 2 PORT-Ausgänge (z. B. für Standby des Prescalers)

- Strom externe Stromeinstellung für PD-Ausgang

Lockdetektausgang (der Lockdetektausgang ist zusätzlich über Bus abfragbar)

### Schaltungsbeschreibung

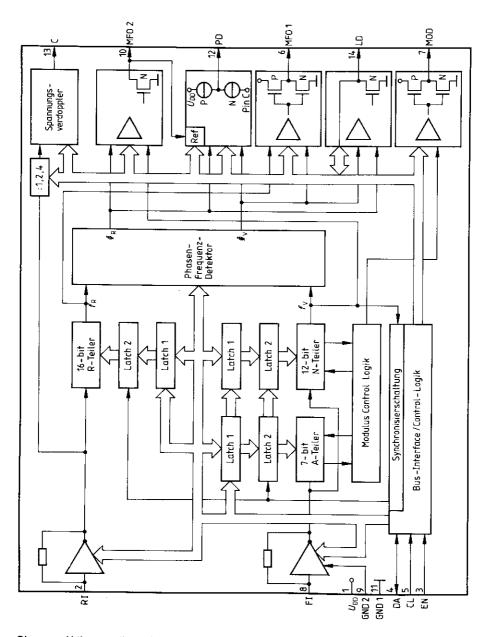

Der TBB 206 ist eine komplexe PLL-Schaltung in CMOS-Technologie für prozessorgesteuerte Frequenzsynthese. Durch integrierte aktive Stromquellen (Charge Pump) mit programmierbaren Phasendetektorkonstanten lassen sich z. B. die Forderungen des GSM-Konzeptes mit schnellen Schleifen erfüllen. Weiterhin zeichnet sich der Baustein durch Flexibilität und geringe Verlustleistung für unterschiedliche Anwendungen aus.

Die Funktionseinstellung (Single- bzw. Dual-Modulus Betrieb) und Wahl der Teilverhältnisse erfolgt dabei über einen 3-Leiter-Bus mit den Anschlüssen CL, DA, EN. Zur Initialisierung müssen zunächst alle Daten (S: 50 Bits, D: 57 Bits) übertragen werden. Das Bus-Interface ist so organisiert, daß Änderungen möglichst schnell durchgeführt werden können. Ein Kanalwechsel benötigt hierbei 15 Bits (S) bzw. 22 Bits (D).

Zur Reduzierung der Stromaufnahme besitzt der TBB 206 ein Stand-By-Mode. Hierbei können wahlweise die Teiler bzw. die Vorverstärker abgeschaltet werden. Die Aktivierung nach Stand-By kann mit dem kurzen Status Wort (Status 1:8 Bits) vorgenommen werden, d. h. die vormals programmierten Teilerverhältnisse und sonstige Einstellungen bleiben erhalten.

Die Referenzfrequenz wird am Eingang RI eingespeist; sie darf max. 30 MHz betragen. Die VCO-Frequenz wird am Eingang FI eingespeist. Sie darf im Single-Modulus Betrieb max. 90 MHz und im Dual-Modulus Betrieb max. 30 MHz betragen.

Die PLL kann wahlweise mit oder ohne internen Spannungsverdoppler betrieben werden, je nach erforderlicher Frequenzvariation (Varicap). Die Frequenz ( $f_{VD}$ ) wird von RI abgeleitet. Der Teiler-Faktor wird über den 3-Leiter-Bus eingestellt.

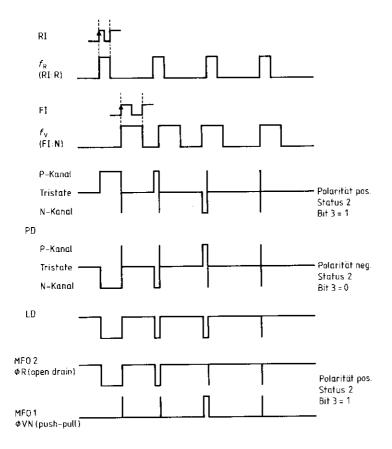

Der Ausgang PD liefert das Phasendetektorsignal mit besonders kurzen Antibacklashimpulsen zur Vermeidung einer Totzeitzone ('dead-zone') und zur Ausregelung kleinster Phasenabweichungen. Hierbei werden Phasendifferenzen von 100ps noch aufgelöst. Der PD-Ausgang ist als Stromquelle ausgelegt, so daß mit einfachen, passiven Bauelementen das Loopfilter (Integrator) aufgebaut werden kann. Polarität und Stromergiebigkeit des PD-Ausgangs sind über den 3 Leiter-Bus umschaltbar. Der open drain Ausgang LD liefert das Lock-Detect Signal. Der Lock-Detect Ausgang ist über Bus abfragbar.

Die Funktion der Multifunktionsausgänge MFO1, MFO2 ist über Status 2 Programmierung wählbar.

Die Ausgänge können 4 Funktionen erfüllen, diese sind:

- a- PRT, wobei PORT 1 (MFO1) ein push-pull Ausgang ist, w\u00e4hrend Port 2 (MFO2) ein opendrain Ausgang mit gro\u00dfer Spannungsfestigkeit darstellt.

- b- Phasendetektorstrom stufenlos einstellbar über externen Widerstand R im Bereich 0,1..4 mA (interner Referenzwiderstand ist abgeschaltet).

- c- Testausgänge FVN = FI : NT, FRN = RI : RT

- d- Digitale Schaltausgänge des Phasendetektors ØR, ØVN zur Ansteuerung z. B. externer aktiver Stromquellen oder aktiver Filter zur Vergrößerung der Phasendetektorkonstante.

Um beim Kanalwechsel extreme Phasenabweichungen zu vermeiden, werden die neuen Daten für den N (N + A) und R Zähler synchron zur Referenzfrequenz (FI:N) übernommen (programmierbarer Zähler hat Stand Null erreicht). Hierdurch ist gewährleistet, daß der Regelvorgang mit der Phasendifferenz 'Null' beginnt.

# Anschlußanordnung

(Ansicht von oben)

# **TBB 206**

**TBB 206 G**

| $U_{\rm DD}$ | ႕  | 1 | 14 | Ь | LD    |

|--------------|----|---|----|---|-------|

| RI           |    | 2 | 13 |   | С     |

| EN           | Ш  | 3 | 12 |   | PD    |

| DA           |    | 4 | 11 |   | GND 1 |

| CL           | Ш  | 5 | 10 | 口 | MF0 2 |

| MFO          | ıШ | 6 | 9  |   | GND 2 |

| MOD          | Ш  | 7 | 8  |   | FI    |

# Anschlußbelegung

| Anschluß    | Symbol          | Funktion                                                          |

|-------------|-----------------|-------------------------------------------------------------------|

| 1           | U <sub>DD</sub> | Speisespannung                                                    |

| 2           | RI              | Referenz-Frequenz                                                 |

| 3<br>4<br>5 | EN<br>DA<br>CL  | 3-Leiter-Bus: Enable<br>3-Leiter-Bus: Daten<br>3-Leiter-Bus: Takt |

| 6           | MFO1            | Multifunktionsausgang                                             |

| 7           | MOD             | Modulus-Kontrolle                                                 |

| 8           | FI              | VCO-Frequenz                                                      |

| 9           | GND2            | Masse, FI-Vorverstärker                                           |

| 10          | MOF2            | Multifunktionsausgang                                             |

| 11          | GND1            | Masse                                                             |

| 12          | PD              | Phasendetektor                                                    |

| 13          | С               | Spannungsverdopplungs-C                                           |

| 14          | LD              | Lock-Detektor                                                     |

# **Blockschaltbild**

### Grenzdaten

$T_{\rm H} = -40$  °C bis +85 °C

| Bezeichnung                                                                                             | Symbol                                                                      | min.                                            | typ. | max.                                                    | Einheit          | Anmerkung   |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------|------|---------------------------------------------------------|------------------|-------------|

| Speisespannung Eingangsspannung Ausgangsspannung C Ausgangsspannung (außer MFO1) Ausgangsspannung MFO 2 | U <sub>DD</sub> U <sub>I</sub> U <sub>C</sub> U <sub>O</sub> U <sub>H</sub> | -0,3<br>-0,3<br>- <i>U</i> <sub>DD</sub><br>GND |      | 6<br>U <sub>DD</sub> +0,3<br>0<br>U <sub>DD</sub><br>10 | V<br>V<br>V<br>V | Ausnahme: C |

| Verlustleistung je Ausgang<br>Gesamtverlustleistung                                                     | P <sub>Q</sub><br>P <sub>tot</sub>                                          | -                                               |      | 10<br>300                                               | mW<br>mW         |             |

| Umgebungstemperatur<br>Lagertemperatur                                                                  | $T_{\rm U}$ $T_{\rm stg}$                                                   | -40<br>-50                                      |      | 85<br>125                                               | ိုင<br>-         |             |

### **Funktionsbereich**

| Speisespannung                                                           | UDD                                 | 4,5 | 5               | 5,5      | V              | 1)             |

|--------------------------------------------------------------------------|-------------------------------------|-----|-----------------|----------|----------------|----------------|

| Speisestrom Single Mode Dual Mode Standby Teiler Standby Vorver- stärker | $I_{ m DD}$ $I_{ m DD}$ $I_{ m DD}$ |     | 2,5<br>2<br>1,5 | 3,5<br>3 | mA<br>mA<br>mA | 2)<br>3)<br>4) |

| Umgebungstemperatur                                                      | Τ <sub>U</sub>                      | -40 |                 | 85       | °C             |                |

| Ausgangsspannung MFO 2                                                   | U <sub>QH</sub>                     | 1   |                 | 8,5      | V              |                |

### Anmerkungen

<sup>1)</sup> Der Baustein kann auch mit leicht eingeschränkten Eigenschaften mit  $U_{\rm DD}=3$  V betrieben werden, insbesondere reduziert sich die Eingangsempfindlichkeit an Fl (200 mV, 35 MHz). Zur optimalen Anwendung bei  $U_{\rm DD}=3$  V mit Spannungsverdoppler sollte die Anti-Backlash Zeit auf den höheren Wert gesetzt werden (siehe Programmierung).

| <sup>2</sup> ) $f_1 = 50 \text{ MHz},$ | $U_{\rm FI} = 150~{\rm mV_{eff}}$      | NT, RT > 1000, | ohne Spannungsverdoppler, $I_{\rm PD} = I_{\rm PD \; min}$                   |

|----------------------------------------|----------------------------------------|----------------|------------------------------------------------------------------------------|

| 3) $f_1 = 10 \text{ MHz},$             | $U_{\rm Fl} = 500~{\rm mV}_{\rm eff}$  | NT, RT > 1000, | ohne Spannungsverdoppler, $I_{\mathrm{PD}} = I_{\mathrm{PD}}\mathrm{_{min}}$ |

| 4) $f_i = 50 \text{ MHz},$             | $U_{\rm Fl}$ = 150 mV <sub>eff</sub> , | NT, RT > 1000, | Ausgangsbeschaltung siehe<br>Meßschaltung                                    |

Ausgangsbeschaltung siehe Meßschaltung Eingänge RI, FI offen

Alle Anschlüsse besitzen ESD Schutzschaltungen gegen  $U_{\rm DD}$  und GND, mit Ausnahme von MFO 2 (nur gegen GND). Unbenutzte Eingänge müssen auf  $U_{\rm DD}$  oder GND gelegt werden.

### Kenndaten

$U_{\rm DD} = 4.5 \, \text{V}$  bis 5.5 V;  $T_{\rm U} = -40 \, \text{bis} + 80 \, ^{\circ} \text{C}$

| Bezeichnung                                                                                                                          | Symbol                                                                                    | Prüfbedingungen                                                        | min.                       | typ.           | max.                                                 | Einheit                               |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------|----------------|------------------------------------------------------|---------------------------------------|

| Eingangssignale DA, (                                                                                                                | CL, EN                                                                                    |                                                                        |                            |                | , the sui                                            |                                       |

| H-Eingangsspannung<br>L-Eingangsspannung<br>Eingangskapazität<br>Eingangsstrom                                                       | $egin{array}{c} U_{ m IH} & & & & & & & & & & & & & & & & & & &$                          | $U_{\rm I} = U_{\rm DD} = 5.5  \rm V$                                  | 0,7 x U <sub>DD</sub><br>0 |                | U <sub>DD</sub><br>0,3 x U <sub>DD</sub><br>10<br>10 | V<br>V.<br>pF<br>μA                   |

| Eingangssignal RI                                                                                                                    |                                                                                           |                                                                        |                            |                |                                                      |                                       |

| Eingangsfrequenz<br>Eingangsspannung<br>Eingangskapazität<br>Eingangsstrom                                                           | f<br>U <sub>1</sub><br>C <sub>1</sub><br>I <sub>1</sub>                                   | $U_{\rm DD} = 4,5 \text{ V}$ (Sinus)* $U_{\rm I} = U_{\rm DD}$         | 100                        |                | 30<br>10<br>10                                       | MHz<br>mV <sub>eff</sub><br>pF<br>μΑ  |

| Eingangssignal FI (Du                                                                                                                | al-Modul                                                                                  | ıs)                                                                    |                            |                |                                                      |                                       |

| ingangsfrequenz<br>Eingangsspannung<br>Eingangskapazität<br>Eingangsstrom                                                            | t<br>U <sub>1</sub>                                                                       | $U_{\rm DD} = 4.5 \text{ V}$ (Sinus)* $U_{\rm l} = U_{\rm DD}$         | 0,1<br>50                  | -              | 30<br>10<br>10                                       | MHz<br>mV <sub>eff</sub><br>pF<br>μΑ  |

| Eingangssignal FI (Sin                                                                                                               |                                                                                           |                                                                        | <u> </u>                   |                | <u> </u>                                             | <u> </u>                              |

| ingangsfrequenz<br>Ingangsspannung<br>ingangskapazität<br>Ingangsstrom                                                               | f U <sub>i</sub> C <sub>i</sub> I <sub>i</sub>                                            | $U_{\rm DD} = 4.5 \text{ V}$ (Sinus)* $U_{\rm I} = U_{\rm DD}$         | 0,1<br>100                 |                | 90<br>10<br>10                                       | MHz<br>mV <sub>eff</sub><br>pF<br>μΑ  |

| Eingangssignal MFO2<br>externe PD-Stromeinstel                                                                                       | luna. Funk                                                                                | tion: Strom)                                                           |                            |                | <u>-</u>                                             | · · · · · · · · · · · · · · · · · · · |

| ingangsstrom**                                                                                                                       | I <sub>I</sub>                                                                            | $U_{\rm DO} = 5 \text{ V}$                                             |                            | 55             |                                                      | μА                                    |

| Ausgangssignal PD (Ti                                                                                                                | ristate-Ou                                                                                | ıtput)                                                                 | ,                          |                | <del></del>                                          | I-i-                                  |

| Ausgangsstrom (extrem eingestellt) Current mode "0,25" Current mode "0,5" Current mode "1" Current mode "2" Current mode "Tri-State" | I <sub>O</sub> I <sub>O</sub> I <sub>O</sub> I <sub>O</sub> I <sub>O</sub> I <sub>O</sub> | $U_{DD} = 5 \text{ V}$ $T_{U} = -25^{\circ}+6$ $T_{U} = -25^{\circ}+6$ | 0°C                        | ±(<br>±(<br>±2 | 1                                                    | mA<br>mA<br>mA<br>mA<br>mA            |

nur Funktionsmessung, Eingangsempfindlichkeit siehe Meßschaltung.

Eingangsstrom für Ausgangsstrom PD von typ 1 mA, siehe Programmiertabelle Zeile 7.

# Kenndaten

$U_{\rm DD} = 4.5 \,\text{V}$  bis 5.5 V;  $T_{\rm U} = -40 \,\text{bis} + 85 \,^{\circ}\text{C}$

| Bezeichnung                                                                | Symbol                                                  | Prüfbedingungen                                                 | min.                 | typ. | max. | Einheit |

|----------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------|----------------------|------|------|---------|

| Ausgangssignal MFO1                                                        | (push-pull)                                             |                                                                 |                      |      |      |         |

| H-Ausgangsspannung                                                         | U <sub>QH</sub>                                         | $I_{\text{QH}} = 2 \text{ mA}$<br>$U_{\text{DD}} = 5 \text{ V}$ | U <sub>DD</sub> -1   |      |      | ٧       |

| L-Ausgangsspannung                                                         | UQL                                                     | $I_{\text{QL}} = 2 \text{ mA}$ $U_{\text{DO}} = 5 \text{ V}$    |                      |      | 1    | V       |

| Ausgangssignal MFO2                                                        | (N-Kanal ope                                            | en drain)                                                       |                      |      |      |         |

| L-Ausgangssignal                                                           | UQL                                                     | $I_{\rm QL}$ = 2 mA<br>$U_{\rm DD}$ = 5 V                       |                      |      | 1    | V       |

| H-Ausgangssignal                                                           | $I_{QH}$                                                | $U_{QH} = U_{DD} + 3 \text{ V}$ $U_{DD} = 5 \text{ V}$          |                      |      | 1    | μА      |

| Ausgangssignale MOI                                                        | ) (push-pull)                                           |                                                                 |                      |      |      |         |

| H-Ausgangsspannung                                                         | UQH                                                     | $I_{\mathrm{QH}}$ = 0,5 mA<br>$U_{\mathrm{DD}}$ = 5 V           | U <sub>DD</sub> -0,4 |      |      | ٧       |

| L-Ausgangsspannung                                                         | $U_{\mathrm{QL}}$                                       | $I_{\rm QL} = 0.5 \text{ mA}$<br>$U_{\rm DD} = 5 \text{ V}$     |                      |      | 0,4  | V       |

| Ausgangssignal MOD                                                         | (K-Kanal ope                                            | n drain)                                                        |                      |      |      |         |

| L-Ausgangsspannung                                                         | U <sub>QL</sub>                                         | $I_{\rm QL}$ = 0,5 mA<br>$U_{\rm DD}$ = 5 V                     |                      |      | 0,4  | V       |

| Ausgangssignal DA (N                                                       | i-Kanal open                                            | drain)                                                          |                      |      |      |         |

| L-Ausgangsspannung $U_{\rm DD} = 5 \text{ V}$ $C_{\rm L} = 400 \text{ pF}$ | U <sub>QL</sub>                                         | $I_{\mathrm{QL}}=3,0~\mathrm{mA}$                               | 0,4                  |      |      | ٧       |

| Ausgangssignal LD (N                                                       | l-Kanal open                                            | drain)                                                          |                      |      |      |         |

| L-Ausgangssignal                                                           | $U_{QL}$ $U_{DD} = 5 \text{ V}$ $C_{L} = 30 \text{ pF}$ | $I_{\mathrm{QL}}$ = 3 mA                                        |                      |      | 0,4  | V       |

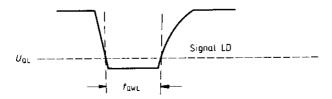

| L-Ausg. Impulsweite                                                        | t <sub>QWL</sub>                                        | PLL eingerastet,<br>STATUS 2, Bit 6=0                           |                      | 20   | 40   | ns      |

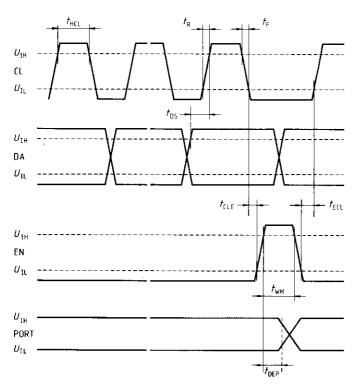

# Impulsdiagramm

### Dynamische Kenndaten

$U_{DD} = 5 \text{ V}; T_{U} = -40 \text{ bis } +85 \,^{\circ}\text{C}$

| Bezeichnung                                                       | Symbol                                                  | Prüfbedingungen                                                                                                | min.                            | typ. | max.            | Einheil        |

|-------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------|------|-----------------|----------------|

| Spannungsverdopple                                                | r                                                       |                                                                                                                |                                 |      |                 |                |

| Ausgangsspannung                                                  | U <sub>QC</sub>                                         | $f_{\rm VD} = 2$ MHz<br>$I_{\rm QC} = 0$ $\mu$ A<br>$U_{\rm DD} = 5$ V<br>PLL eingerastet                      | -U <sub>DD</sub> +0,8V          |      | U <sub>DD</sub> | ٧              |

| Ausgangsspannnung                                                 | Ugc                                                     | $f_{\rm VD} = 2 \text{ mHz}$<br>$I_{\rm QC} = 100 \mu\text{A}$<br>$U_{\rm DD} = 5 \text{V}$<br>PLL eingerastet | − <i>U</i> <sub>DD</sub> +1,5 V |      | U <sub>DD</sub> | V              |

| Stromaufnahme                                                     | $I_{ m VD}$                                             | $U_{\rm DD}$ = 5 V<br>$I_{\rm QC}$ = 0 $\mu$ A<br>$f_{\rm VD}$ = 2 MHz<br>PLL eingerastet                      |                                 | 250  |                 | μА             |

| Ausgangssignal MFO                                                | 1, MFO2, I                                              | Funktion: FVN, FR                                                                                              | N, ØR, ØVN                      |      |                 |                |

| Anstiegszeit (push pull)<br>Abfallzeit (open drain,<br>push pull) | t <sub>QR</sub>                                         | $C_L = 30 \text{ pF}$ $C_L = 30 \text{ pF}$                                                                    |                                 |      | 10<br>10        | ns<br>ns       |

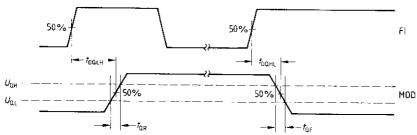

| Ausgangssignal MOD                                                | (push pu                                                | II)                                                                                                            |                                 |      |                 | •              |

| Anstiegszeit<br>Abfallzeit<br>Verzögerungszeit<br>L-H gegen Fl    | t <sub>QR</sub><br>t <sub>QF</sub><br>t <sub>DQLH</sub> | $C_L = 30 \text{ pF}$<br>$C_L = 30 \text{ pF}$<br>$C_L = 30 \text{ pF}$                                        |                                 |      | 10<br>10<br>25  | ns<br>ns<br>ns |

| Verzögerungszeit<br>H-L gegen FI                                  | t <sub>QDHL</sub>                                       | C <sub>L</sub> = 30 pF                                                                                         |                                 |      | 15              | ns             |

### Anmerkung:

### Meßschaltungen

PLL-Grundfunktion entsprechend Meßschaltung TBB 200 (s. Seite 17). Eingangsempfindlichkeit, Meßschaltung und Kurvenverlauf entsprechend TBB 200 (s. Seite 18 und 19).

externe PD-Stromeinstellung Eingangssignal MFOR (Funktion: Strom)

# Impulsdiagramm

# Phasendetektor/Lockdetektor

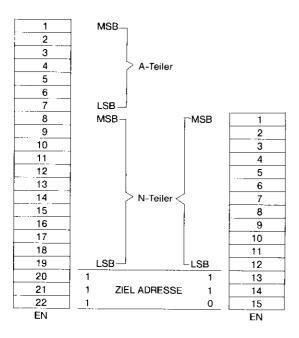

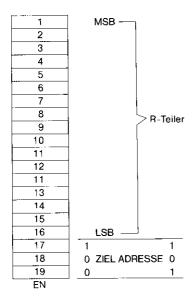

#### **Programmierung**

Die Programmierung der Teiler als auch die Status-Steuerung erfolgt beim TBB 206 über einen 3-Leiter-Bus. Die Zuordnung des Inhalts der Telegramme zu den Funktionseinheiten erfolgt hierbei über eine Zieladresse, die in den letzten drei Bits des Telegrammes vor dem EN-Signal abgelegt ist.

Die Zieladresse selbst enthält neben der Zuordnungsinformation auch noch 'Status'-Informationen:

Single/Dual Betrieb und synchrone/asynchrone Datenübernahme.

Folgende Adressen sind gültig:

...001 EN : Status 1 ...010 EN : Status 2 ...011 EN : Status 3

...110 EN: N-Counter Single Betrieb ...111 EN: N/A-Counter Dual Betrieb

...101 EN : R-Counter + synchrone Übernahme ...100 EN : R-Counter + asynchrone Übernahme

Die Entscheidung Single/Dual-Modulus erfolgt gleichzeitig mit der Programmierung des N-bzw. N/A-Teilers.

Die Zieladresse 000 ist für Testzwecke reserviert.

Im TBB 206 ist vorgesehen, die programmierbaren Teiler synchron zur Referenzfrequenz neu zu programmieren. Hierdurch ist gewährleistet, daß bei Frequenz/Kanaländerungen die Regelung vom momentanen Zustand des Phasendetektors ausgeht. Insbesonders im 'Lock-In'-Fall beginnt der Regelvorgang mit der Phasendifferenz 'Null'. Kurzzeitige Fehlsignale am Phasendetektor, wie sie bei asynchroner Datenübernahme vorkommen können, sind hiermit ausgeschlossen.

Bei der **asynchronen** Programmierung werden die "neuen" Daten asynchron zum jeweiligen Zustand des R-, N- (N/A) Teilers in die Zwischenregister L2 übernommen. Da die rechtzeitige Bereitstellung aller Daten, d. h. R- und N- (N/A) Teiler, nicht gewährleistet ist, ergeben sich, durch nicht korrespondierende Teilerfaktoren in den Zählern, Fehlersignale am Phasendedektorausgang, die vom System als Phasendifferenz bewertet und somit zusätzlich ausgeregelt werden müssen.

### **Programmierung**

Die **synchrone** Programmierung bietet die Möglichkeit der Datenübernahme unter Beibehaltung der zum (internen) Programmierzeitpunkt bestehenden Phasendifferenz. Dies geschieht folgendermaßen:

- Einstellung der Betriebsart "synchrone Übernahme" durch entsprechende R-Teiler Programmierung. Diese Einstellung bleibt erhalten bis gegenteilige Programmierung erfolgt.

Mit dem EN der R-Teiler Programmierung werden die "neuen" Daten nur in das Auffangregister L1 übernommen.

- 2. Programmierung vom N- bzw. N/A-Teiler. Mit dem EN Signal der Programmierung werden die "neuen" Daten ebenfalls nur in das Auffangregister L1 übernommen. Gleichzeitig wird für alle Teiler die synchrone Übernahme in das Zwischenregister L2 vorbereitet. Die Übernahme erfolgt dann beim nächsten Null-Durchgang des jeweiligen Teilers. Eine zum Übernahmezeitpunkt vorhandene Phasendifferenz bleibt erhalten, sie ist Anfangsbedingung für den weiteren Regelvorgang, basierend auf den "neu" übernommenen Deten.

Bedingt durch die Synchronisierschaltung beträgt die Verzögerung der Datenübernahme daher maximal  $2\cdot 1/t_{\rm ref}$ .

Der synchrone Programmiervorgang wird immer durch das EN-Signal des N- bzw. N/A-Teilers ausgelöst und gilt auch für den R-Teiler, auch wenn dessen Daten nicht geändert wurden. Soll der Dateninhalt des R-Teilers (z. B. beim Referenzfrequenzwechsel) geändert werden, so ist dies daher **vor** der N- bzw. N/A-Teiler Programmierung zu machen.

Die synchrone Übernahme ist dann von besonderem Vorteil, wenn bei geforderter kleiner Einschwingzeit größere Kanalsprünge durchgeführt werden sollen. Hierzu wird zum schnellen "groben" Einschwingen auf eine größere Referenzfrequenz umgeschaltet, wodurch die Bandbreite der Schleife vergrößert wird. Beim Erreichen des "Quasi-Soll"-Zustandes wird wieder auf die ursprüngliche Referenzfrequenz zurückgeschaltet. Die Ausregelung auf den "Ist"-Wert erfolgt dann mit dem gewohnten Einschwingverhalten wie bei kleinen Kanalsprüngen. Durch die synchrone Übernahme ist gewährleistet, daß durch den Wechsel derr Referenzfrequenzen keine zusätzliche Phasenfehler entstehen.

#### Programmierung: Zeiten

Initialisierung, Reihenfolge: R-Teiler vor N-Teiler

| Single Mode: | 50 Bits | Dual Mode: | 57 Bits |

|--------------|---------|------------|---------|

| Status 2     | 16 Bits | Status 2   | 16 Bits |

| R-Teiler     | 19 Bits | R-Teiler   | 22 Bits |

| N-Teiler     | 15 Bits | N/A-Teiler | 22 Bits |

Kanalwechsel bei gleicher Referenzfrequenz

Single Mode 15 Bits Dual Mode 22 Bits

Wird die Referenzfrequenz geändert, so ist zusätzlich der R-Teiler zu laden (+19 Bits).

Maximale Wiederholrate für Kanalwechsel (f<sub>FI</sub>: N)

#### Anmerkung:

Nach Anlegen der Speisespannung müssen vor dem ersten Telegramm mindestens 3 Takte am Clock-Eingang anliegen, während EN = LOW ist.

# Programmierung: Tabellen

| Status Bit |       | Multifunktio         | onsausgänge             |

|------------|-------|----------------------|-------------------------|

| MFO 1      | MFO 2 | MFO 1<br>(push-pull) | MFO 2<br>(open drain N) |

| 0          | 0     | FRN                  | FVN                     |

| 0          | 1     | ØVN                  | ØR                      |

| 1          | 0     | PRT 1                | PRT 2                   |

| 1          | 1     | PRT 1                | STROM*                  |

<sup>\*</sup> Input

| Statu      | PD-Ausgangs-<br>strom |           |

|------------|-----------------------|-----------|

| PD-Strom 1 | PD-Strom 2            | typ. (mA) |

| 0          | 0                     | 0,25      |

| 1          | 0                     | 0,5       |

| 0          | 1                     | 1,0       |

| 1          | 1                     | 2,0       |

| Status Bit          |   | Spannungs-<br>verdoppler-<br>frequenz |

|---------------------|---|---------------------------------------|

| Spannungsverdoppler |   | t <sub>int</sub>                      |

| 1                   | 2 | 7,11                                  |

| 0                   | 0 | Off                                   |

| 1                   | 0 | R <sub>I</sub> : 1                    |

| 0                   | 1 | R <sub>I</sub> : 2                    |

| 11                  | 1 | R <sub>I</sub> : 4                    |

# Programmierung: Übertragungsprotokoll

MFO 1 MFO2 PD-Polarität Modulus-Ausgang

### STATUS 1

### STATUS 2\*

|    | Vorverstärker (Stand by) |   |  |

|----|--------------------------|---|--|

|    | Anti-Backlash Impuls     |   |  |

|    | Spannungsverdoppler 1    |   |  |

|    | Spannungsverdoppler 2    |   |  |

| 1  | PORT 1                   |   |  |

| 2  | PORT 2                   |   |  |

| 3  | Teiler (Stand by)        |   |  |

| 4  | PD-Strom 1               |   |  |

| 5  | PD-Strom 2               |   |  |

| 6  | 0 0                      | _ |  |

| 7  | 0 Zieladresse 1          |   |  |

| 8  | 1 0                      |   |  |

| EN |                          |   |  |

| 1  |

|----|

| 2  |

| 3  |

| 4  |

| 5  |

| 6  |

| 7  |

| 8  |

| 9  |

| 10 |

| 11 |

| 12 |

| 13 |

| 14 |

| 15 |

| 16 |

| EN |

|    |

| 0         | 1          |

|-----------|------------|

|           | s. Tabelle |

| neg.      | pos.       |

| push pull | open drain |

| Stand by  | aktiv      |

| 20 ns     | 40 ns      |

|           | s. Tabelle |

| 0**       | 1**        |

| 0**       | 1**        |

| Stand by  | aktiv      |

|           | s. Tabelle |

### STATUS 3: LOCK-Detekt Abfrage

| 1  |

|----|

| 2  |

| 3  |

| EN |

|    |

0 1 Zieladresse 1

1 EN

Zustand Lock-Detekt: IN-Lock = LOW \*\*\*

Zur Initialisierung muß immer STATUS 2 verwendet werden.

(Bit 1-8 von Status 2 haben keine Default-Werte)

<sup>\*\*</sup> Nur gültig, wenn Multifunktionsausgänge (s. Blatt K) in Status PORT, sonst don't care.

<sup>\*\*\*</sup> DA des TBB 206 kann nur "LOW" erzeugen (open-drain output).

### N/A-Teiler

### N-Teiler

### **Dual Betrieb**

# Single Betrieb

Adresse 111: Dual Betrieb Adresse 110: Single Betrieb

# R-Teiler

Adresse 101: synchrone Übernahme \* Adresse 100: asynchrone Übernahme \*

<sup>\*</sup> bestimmt auch Übernahmeart bei N-, N/A-Teiler

# Zeitdiagramm 3-Leiter-Bus

|                      |                              | min. | max. | Einheit |

|----------------------|------------------------------|------|------|---------|

| $f_{\sf CL}$         | Taktfrequenz                 |      | 1,3  | MHz     |

| t <sub>HCL</sub>     | H-Impulsbreite (CL)          | 400  | .,-  | ns      |

| t <sub>DS</sub>      | Data Setup                   | 100  |      | ns      |

| $t_{\sf CLE}$        | Setup Time Clock-Enable      | 5    |      | ns      |

| $t_{\sf ECL}$        | Setup Time Enable-Clock      | 100  |      | ns      |

| $t_{WH}$             | H-Impulsbreite (Enable)      | 80   |      | ns      |

| $t_{R^{r}} \; t_{F}$ | Übergangszeiten              |      | 10   | us      |

| $t_{DEP}$            | Verzögerungszeit Enable-PORT |      | 1    | μs      |

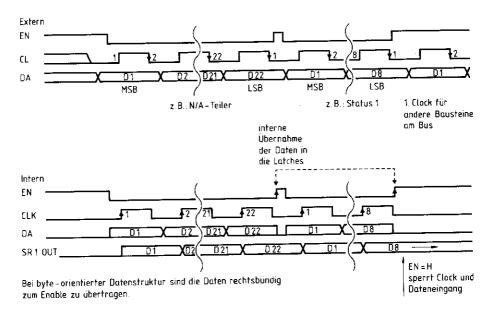

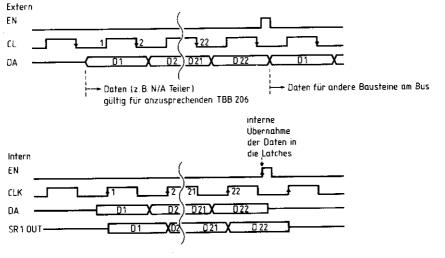

### Impulsdiagramm 3-Leiter-Bus

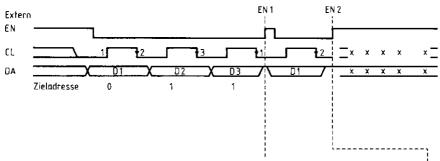

# Impulsdiagramm 3-Leiter-Bus: "Dynamische" EN-Steuerung

# Impulsdiagramm 3-Leiter-Bus Abfrage Lockdetektor

Daten-Leitung des Bus muß hochohmig sein (Pull-Up-Widerstand) EN 1→EN 2.

Der Zustand des Lock-Detekt Ausganges LD zum Zeitpunkt der steigenden Flanke des Enable-Signales EN1 definiert das Ausgangssignal D1 in der Ausgabephase (LD=HiGH→D1=LOW).

Bei byte-orientierter Datenstruktur wird in der Ausgabephase während der Takte 2-8 kein weiteres Signal vom TBB 206 erzeugt, d. h. es stellt sich (Pull-Up-Widerstand) der Zustand HIGH ein.

# Beschreibung einiger wichtiger Anschlüsse

| Anschluß | Symbol | Funktion                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2        | RI     | Eingang für 16-Bit R-Teiler (Referenz-Teiler). Der Eingang hat einen empfindlichen Vorverstärker. Bei kleinen Eingangssignalen ist eine AC-Kopplung vorzusehen, während bei großen Eingangssignalen eine DC-Kopplung möglich ist.                                                                                                                                                                   |  |

| 3        | EN     | 'Enable'-Leitung des 3-Leiter-Bus. Wenn EN = HIGH ist, werde die Eingangssignale CL und DA des 3-Leiter-Bus intern abge schaltet. EN = LOW aktiviert die Bus-Steuerung. Mit der positive Flanke des EN-Signales werden die internen (empfangenen Daten der DA-Leitung in die Latches übernommen.                                                                                                    |  |

| 4        | DA     | Serielle Daten Leitung des 3-Leiter-Bus. Die Anzahl der Daten ist abhängig von der gewünschten Programmierung (siehe Übertragungsprotokolle). Die letzten 3 Bits vor dem EN-Signal definieren, wohin die übertragenen Daten zuzuordnen sind. Bei byte-orientierter Datenstruktur sind die Daten bündig zum EN-Signal zu übertragen, d. h. aufzufüllende (don't care) Bits werden zuerst übertragen. |  |

| 5        | CL     | Clock-Leitung des 3-Leiter-Bus. Mit der positiven Flanke werden die seriellen Daten in die internen Schieberegister übernommen (d. h. erscheinen am Ausgang des Schieberegisters).                                                                                                                                                                                                                  |  |

# Beschreibung einiger wichtiger Anschlüsse (Fortsetzung)

| Anschluß                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Symbol | Funktion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Den Ausgängen können über den Bus ver zugeordnet werden (siehe Programmierung drain N-Kanal Ausgang gebildet und besit nungsfestigkeit als die anderen Ausgänge dist die Möglichkeit gegeben, externen Stußetriebsspannung anzusteuern.  Die Signale ØR und ØVN sind die digitaler Phasen- und Frequenzdetektors und sind Hierdurch können externe aktive Stromquell direkt angesteuert werden. $f_V < f_R$ oder $f_V$ nacheilend: Ø <sub>R</sub> LOW aktiv $f_V > f_R$ oder $f_V$ voreilend: Ø <sub>VN</sub> HIGH aktiv $f_V = f_R$ und PLL eingerastet: Ø <sub>R</sub> hochohmig Die Signale FRN und FVN sind die herunt RI und FI. Die LOW-Zeit entspricht dabei de Der Anschluß MFO2 kann gleichzeitig als einstellung des PD-Ausganges geschaltet positiver Strom einzuspeisen. Die Bus-Stebleibt weiterhin erhalten.  Über Status 2 Bit 3 (PD-Polarity) kann di gangssignale FVN, FRN bzw. ØVN, ØR zu FI, RI vertauscht werden.  In der Funktion PORT wird den Ausgäng Status Programmierung zugeordnet. Die Ausganges gegennet. |        | Die Signale ØR und ØVN sind die digitalen Ausgangssignale des Phasen- und Frequenzdetektors und sind zueinander invertiert. Hierdurch können externe aktive Stromquellen (für größere Ströme) direkt angesteuert werden. $f_{V} < f_{R} \text{ oder } f_{V} \text{ nacheilend: } \emptyset_{R} \text{ LOW aktiv}$ $f_{V} > f_{R} \text{ oder } f_{V} \text{ voreilend: } \emptyset_{VN} \text{ HIGH aktiv}$ $f_{V} = f_{R} \text{ und PLL eingerastet: } \emptyset_{R} \text{ hochohmig, } \emptyset_{VN} \text{ LOW}$ Die Signale FRN und FVN sind die heruntergeteilten Signale von RI und FI. Die LOW-Zeit entspricht dabei der Zeit $1/f_{RI}$ bzw. $1/f_{FI}$ . Der Anschluß MFO2 kann gleichzeitig als Eingang für die Stromeinstellung des PD-Ausganges geschaltet werden. Hierzu ist ein positiver Strom einzuspeisen. Die Bus-Steuerung zur Abstufung bleibt weiterhin erhalten. Über Status 2 Bit 3 (PD-Polarity) kann die Zuordnung der Ausgangssignale FVN, FRN bzw. ØVN, ØR zu den Eingangssignalen |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Im Standby-Mode stellen sich folgende Zustände ein:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Status MFO1 push-pull MFO2 open drain FRN/FVN LOW hochohmig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | ØVN/ØR LOW hochohmig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MOD    | Modulus Control Ausgang für externen Dual Modulus Prescaler. Der Modulus Ausgang ist zu Beginn des Zyklus LOW. Wenn der A-Teiler seinen eingestellten Wert erreicht hat, geht MOD auf HIGH. Wenn der N-Teiler seinen eingestellten Wert erreicht hat, geht MOD wieder auf LOW, und der Zyklus beginnt von neuem. Wenn der Prescaler die Teilerfaktoren P bzw. P +1 hat (P für MOD = H, P +1 für MOD = L), dann ist der Gesamtteilungsfaktor: N · P + A. Der Wert des A-Teilers muß kleiner sein als der Wert des N-Teilers. Im Single-Modulus Betrieb und bei Standby Operation in Dual Mode Betrieb ist der Ausgang bei open-drain-Betrieb hochohmig und im push-pull-Betrieb "Tri-State".                                                                                                                                                                                                                                                                                                                      |  |

# Beschreibung einiger wichtiger Anschlüsse (Fortsetzung)

| Anschluß | Symbol | Funktion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8        | FI     | Eingang mit hochempfindlichem Vorverstärker für 12-bit-N-Teiler<br>und 7-bit-A-Teiler. Bei kleinen Eingangssignalen ist eine AC-Kopp-<br>lung vorzusehen, während bei großen Eingangssignalen eine<br>DC-Kopplung möglich ist.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 9        | GND2   | Masse des internen empfindlichen Vorverstärkers des Eingangs Fl. Wird extern mit GND1 verbunden.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 12       | PD     | Tri-State Charge Pump Ausgang. Die integrierten positiven und negativen Stromquellen können über den Bus bezüglich der Stromdichte programmiert werden. Die Aktivierung bzw. Deaktivierung hängt von der Phasenbeziehung der heruntergeteilten Eingangssignale FI:N, RI:R, ab. (siehe Impulsdiagramm Phasendetektor). $f_V < f_R$ oder $f_V$ nacheilend: P-Kanal Stromquelle aktiv $f_V > f_R$ oder $f_V$ voreilend: N-Kanal Stromquelle aktiv $f_V = f_R$ und PLL eingerastet: Stromquellen abgeschaltet, Ausgang ist hochohmig (Tristate) Im Standby-Mode wird der Tri-State Zustand eingestellt. Über Status 2 Bit 3 (Polarity) kann die Zuordnung der Stromquellen zu den Ausgangssignalen des Phasendetektors vertauscht werden, d. h. das Vorzeichen der Phasendetektorkonstante ist steuerbar. |  |

| 13       | С      | Spannungsverdoppler-Ausgang. Der interne kapazitive Spannungsverdoppler arbeitet auf eine externe Kapazität an Anschluß 13 (C: + an Anschluß 11, — an Anschluß 13). Ein typischer Kapazitätswert ist 110 μF. Der Kondensator sollte geringe Leckströme haben. Wird der Spannungsverdoppler nicht benötigt, so ist Anschluß C mit GND1 zu verbinden. Anschluß 13 ist gleichzeitig Fußpunkt der N-Kanal Stromquelle des PD-Ausganges. Die Taktfrequenz des Wandlers wird über einen programmierbaren Teiler (:1, :2, :4) aus dem Signal an RI abgeleitet. Die interne Taktfrequenz sollte größer 2 MHz sein.                                                                                                                                                                                            |  |

| 14       | LD     | Lock-Detekt Ausgang (open-drain). Unipolarer Ausgang des Phasendetektors in Form eines pulsweiten modulierten Signales. Im eingerasteten Zustand entspricht die LOW-Pulsweite dem Antibacklash-Impuls. Im Standby-Mode ist der Ausgang hochohmig. Der Zustand ist über den Bus (Status 3) abfragbar. Eine Abfrage während des Standby-Modes ist nicht sinnvoll.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

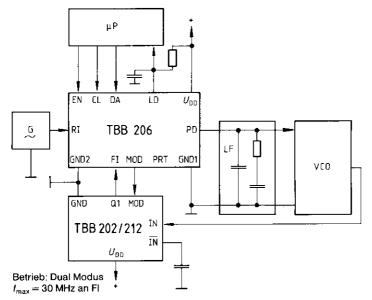

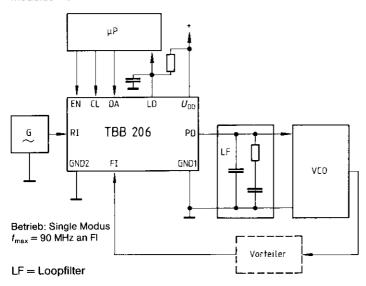

### Anwendungsschaltung

Entsprechend der Referenzfrequenz sind die geeigneten Teilerverhältnisse des Dual-Modulus-Vorteilers 128/129 bzw. 64/65 zu wählen.

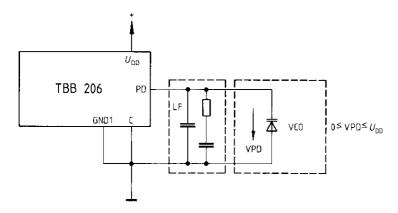

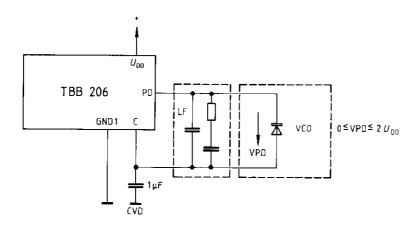

# **Anwendungsschaltung VCO-Ankopplung**

Betrieb ohne Spannungsverdoppler (Status-Bit = s. Tabelle K)

Betrieb mit Spannungsverdoppler/Status-Bit = siehe Tabelle K)

LF = Loopfilter

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com