# TC5299J FAST ETHERNET PCMCIA LAN CONTROLLER

4FL No. 106 Hsin-Tai Wu Road,

Sec. 1, Hsichih,

Taipei Hsien, Taiwan R.O.C. TEL: 886-2-2696-1669 FAX: 886-2-2696-2220 http://www.tmi.com.tw

Ver. 0.1 07/04/01

# **TABLE OF CONTENTS**

| 1.1   General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 | Introduction                                          | 3  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------|----|--|--|--|--|

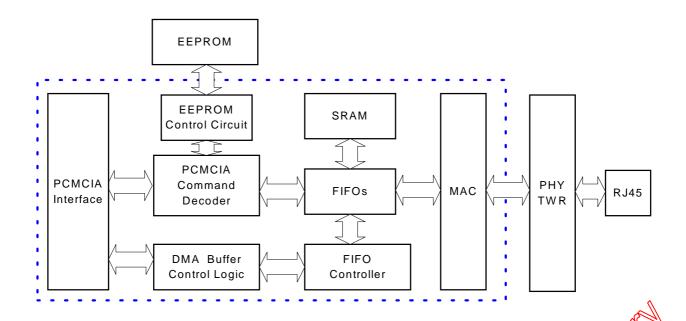

| 2   Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                       |    |  |  |  |  |

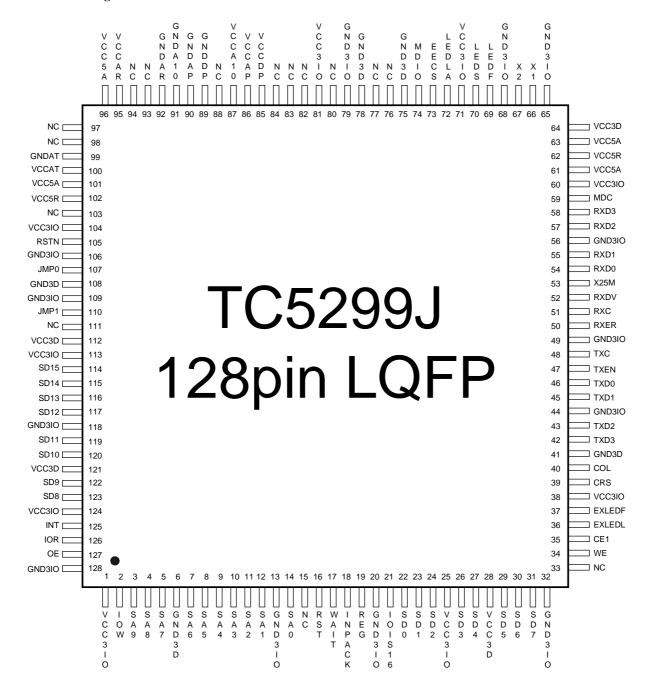

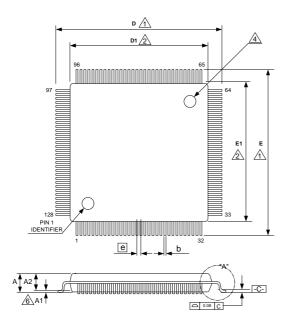

| 3.1 Pin Out Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 1.2 Features                                          | 3  |  |  |  |  |

| 3.1 Pin Out Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 | Block Diagram                                         | 3  |  |  |  |  |

| 3.1 Pin Out Diagram       2.         3.2 Signal Description       5.         3.3 Power On Configuration       8.         4 I/O and Mapping       10         4.1 I/O Port Address Mapping       11         4.2 EEPROM/SRAM Memory Mapping       11         4.3 Attribute Memory Mapping       11         4.3.1 Attribute Memory Map       11         5 Configuration Register S       12         5.1 Configuration Register A       12         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MII/PHY Control Register       15         5.6 TCS2991 Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configuration Register (CR) 00H(Write)       18         5.7.3 Transmit status Register (TCR) 00H(Write)       15         5.7.3 Transmit Status Register (TCR) 00H(Write)       15         5.7.5 Receive Configuration Register (CR) 0CH(Write)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RCR) 0CH(Write)       22         5.7.7 Interrupt Mask Register (RCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | •                                                     |    |  |  |  |  |

| 3.2 Signal Description       5.         3.3 Power On Configuration       8.         4 I/O and Mapping       10.         4.1 I/O Port Address Mapping       10.         4.2 EEPROM/SRAM Memory Mapping       11.         4.3 Attribute Memory Mapping       11.         4.3 Attribute Memory Mapping       11.         5 Configuration Register S       12.         5.1 Configuration Register A       15.         5.2 Configuration Register B       15.         5.3 Configuration Register C       14.         5.4 Hardware Configuration       14.         5.5 MII/PHY Control Register Assignment       15.         5.6 TCS2991 Core Registers Assignment       15.         5.7 Register Descriptions       18.         5.7.1 Command Register (CR) 00H (Read/Write)       18.         5.7.2 Data Configure register (DCR) 0EH(Write)       15.         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15.         5.7.4 Transmit Status Register (TSR) 0H(Write)       15.         5.7.5 Receive Configuration Register (RCR) 0CH(Read)       20.         5.7.6 Receive Status Register (RR) 0CH(Read)       20.         5.7.8 Interrupt Mask Register (RR) 0FH(Write)       22.         5.7.8 Interrupt Mask Register (RCR) 0CH(Read)       22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | <b>-</b>                                              |    |  |  |  |  |

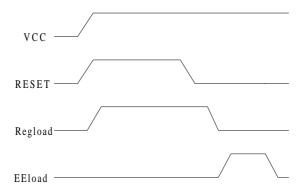

| 3.3 Power On Configuration   Statistics   Statistics |   |                                                       |    |  |  |  |  |

| 41 I/O and Mapping       10         4.1 I/O Port Address Mapping       10         4.2 EEPROM/SRAM Memory Mapping       11         4.3 Attribute Memory Mapping       11         4.3.1 Attribute Memory Map       11         5 Configuration Registers       12         5.1 Configuration Register A       15         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MIJPHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       18         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       22         5.7.7 Interrupt Mask Register (RSR) 0TH(Read/Write)       22         5.7.8 Interrupt Status Register (RSR) 0TH(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.10 Physical Address Registers (MARO-MART)       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                       |    |  |  |  |  |

| 4.1 I/O Port Address Mapping       10         4.2 EEPROM/SRAM Memory Mapping       11         4.3 Attribute Memory Mapping       11         4.3.1 Attribute Memory Map       11         5 Configuration Registers       12         5.1 Configuration Register A       15         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MII/PHY Control Register       15         5.6 TCS2991 Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configuration Register (TCR) 0DH(Write)       15         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TCR) 0H(Read)       20         5.7.5 Receive Configuration Register (NCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (RSR) 0CH(Read)       22         5.7.8 Interrupt Mask Register (RSR) 0CH(Write)       22         5.7.8 Interrupt Status Register (RSR) 0CH(Read/Write)       22         5.7.8 Interrupt Status Register (RSR) 0CH(Read/Write)       22         5.10 Physical Address Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4 | · · · · · · · · · · · · · · · · · · ·                 |    |  |  |  |  |

| 4.2 EEPROM/SRAM Memory Mapping       16         4.3 Attribute Memory Mapping       11         4.3 I Attribute Memory Map       11         5 Configuration Registers       12         5.1 Configuration Register A       15         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MIVPHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       18         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (MR) 0FH(Write)       22         5.7.8 Interrupt Mask Register (MR) 0FH(Write)       22         5.7.8 Interrupt Status Register (NTR)       22         5.7.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NTR)       22         5.10 Physical Address Register (MAR0-MAR7)       22         5.12 DMA Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ |                                                       |    |  |  |  |  |

| 4.3 Attribute Memory Mapping       11         4.3.1 Attribute Memory Map       17         5 Configuration Registers       12         5.1 Configuration Register A       13         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MIl/PHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       18         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       26         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       22         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (MAR0-MAR7)       22         5.12 DMA Registers       22         5.14 REMOTE DMA REGISTERS       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                       |    |  |  |  |  |

| 4.3.1 Attribute Memory Map       1.1         5 Configuration Registers       1.3         5.1 Configuration Register A       1.5         5.2 Configuration Register B       1.3         5.3 Configuration Register C       1.4         5.4 Hardware Configuration       1.4         5.5 MII/PHY Control Register       1.5         5.6 TC52991 Core Registers Assignment       1.5         5.7 Register Descriptions       1.8         5.7.1 Command Register (CR) 00H (Read/Write)       1.8         5.7.2 Data Configure register (DCR) 0EH(Write)       1.5         5.7.3 Transmit configuration Register (TCR) 0DHWrite)       1.5         5.7.4 Transmit Status Register (TSR) 04H(Read)       2.6         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       2.1         5.7.6 Receive Status Register (RSR) 0CH(Read)       2.1         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       2.1         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       2.2         5.7.8 Network Tally Counter Registers (CNTR)       2.2         5.9 Number of Collisions Register (NCR)       2.2         5.10 Physical Address Register (PAR0-PAR5)       2.2         5.11 Multicast Address Registers       2.2         5.12 DMA Registers       2.2         5.15 (i) Local                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                                       |    |  |  |  |  |

| 5 Configuration Registers       13         5.1 Configuration Register A       15         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MII/PHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       19         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       26         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       20         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (MARO-MAR7)       22         5.12 DMA Registers       22         5.13 LOCAL DMA RECEIVE REGISTERS       22         5.15 (i) Local DMA Transmit Registers       22         5.16 (ii) Local DMA Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                       |    |  |  |  |  |

| 5.1 Configuration Register A       12         5.2 Configuration Register B       15         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MII/PHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       15         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       20         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.7.8 Interrupt Status Register (NCR)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       25         5.15 (i) Local DMA Transmit Registers       25         5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 |                                                       |    |  |  |  |  |

| 5.2 Configuration Register B       12         5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MII/PHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       18         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       19         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IRR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       25         5.15 (i) Local DMA RECEIVE REGISTERS       25         5.15 (ii) Local DMA Transmit Registers       25         5.17 (iii) Remote DMA registers       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | J |                                                       |    |  |  |  |  |

| 5.3 Configuration Register C       14         5.4 Hardware Configuration       14         5.5 MII/PHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       15         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       26         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       26         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IRR) 0FH(Write)       22         5.7.8 Interrupt Status Register (IRR) 0FH(Write)       22         5.7.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       25         5.15 (i) Local DMA REGISTERS       25         5.15 (i) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28         7 Ph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                       |    |  |  |  |  |

| 5.4 Hardware Configuration       14         5.5 MIVPHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       15         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (ISR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.9 Number of Collisions Register (CNTR)       25         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       25         5.15 (i) Local DMA REGISTERS       25         5.15 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28 <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |                                                       |    |  |  |  |  |

| 5.5 MII/PHY Control Register       15         5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       18         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       19         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         5.17 (iii) Remote DMA registers       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                       |    |  |  |  |  |

| 5.6 TC5299J Core Registers Assignment       15         5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       18         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                       |    |  |  |  |  |

| 5.7 Register Descriptions       18         5.7.1 Command Register (CR) 00H (Read/Write)       18         5.7.2 Data Configure register (DCR) 0EH(Write)       19         5.7.3 Transmit configuration Register (TCR) 0DH(Write)       19         5.7.4 Transmit Status Register (TSR) 04H(Read)       20         5.7.5 Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6 Receive Status Register (RSR) 0CH(Read)       21         5.7.7 Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8 Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       22         5.10 Physical Address Register (PAR0-PAR5)       22         5.11 Multicast Address Registers (MAR0-MAR7)       22         5.12 DMA Registers       22         5.14 REMOTE DMA RECEIVE REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         5.18 (iii) Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                       |    |  |  |  |  |

| 5.7.1       Command Register (CR) 00H (Read/Write)       18         5.7.2       Data Configure register (DCR) 0EH(Write)       19         5.7.3       Transmit configuration Register (TCR) 0DH(Write)       19         5.7.4       Transmit Status Register (TSR) 04H(Read)       20         5.7.5       Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6       Receive Status Register (RSR) 0CH(Read)       21         5.7.7       Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8       Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8       Network Tally Counter Registers (CNTR)       22         5.9       Number of Collisions Register (NCR)       22         5.9       Number of Collisions Register (NCR)       22         5.10       Physical Address Register (PAR0-PAR5)       22         5.11       Multicast Address Registers (MAR0-MAR7)       22         5.12       DMA Registers       22         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.16       (ii) Local DMA Transmit Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                       |    |  |  |  |  |

| 5.7.2       Data Configure register (DCR) 0EH(Write)       15         5.7.3       Transmit configuration Register (TCR) 0DH(Write)       15         5.7.4       Transmit Status Register (TSR) 04H(Read)       26         5.7.5       Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6       Receive Status Register (RSR) 0CH(Read)       21         5.7.7       Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8       Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8       Network Tally Counter Registers (CNTR)       22         5.9       Number of Collisions Register (NCR)       22         5.10       Physical Address Register (PAR0-PAR5)       22         5.11       Multicast Address Registers (MAR0-MAR7)       22         5.12       DMA Registers       22         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.14       REMOTE DMA REGISTERS       25         5.16       (ii) Local DMA Transmit Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                                       |    |  |  |  |  |

| 5.7.3       Transmit configuration Register (TCR) 0DH(Write)       19         5.7.4       Transmit Status Register (TSR) 04H(Read)       26         5.7.5       Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6       Receive Status Register (RSR) 0CH(Read)       21         5.7.7       Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8       Interrupt Status Register (ISR) 07H(Read/Write)       22         5.8       Network Tally Counter Registers (CNTR)       23         5.9       Number of Collisions Register (NCR)       24         5.10       Physical Address Register (PAR0-PAR5)       24         5.11       Multicast Address Registers (MAR0-MAR7)       24         5.12       DMA Registers       25         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.15       (i) Local DMA Transmit Registers       25         5.16       (ii) Local DMA Receive Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                       |    |  |  |  |  |

| 5.7.4       Transmit Status Register (TSR) 04H(Read)       26         5.7.5       Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6       Receive Status Register (RSR) 0CH(Read)       21         5.7.7       Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8       Interrupt Status Register (ISR) 07H(Read/Write)       23         5.8       Network Tally Counter Registers (CNTR)       23         5.9       Number of Collisions Register (NCR)       24         5.10       Physical Address Register (PAR0-PAR5)       24         5.11       Multicast Address Registers (MAR0-MAR7)       24         5.12       DMA Registers       25         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.14       REMOTE DMA REGISTERS       25         5.15       (i) Local DMA Transmit Registers       25         5.16       (ii) Local DMA Receive Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                       |    |  |  |  |  |

| 5.7.5       Receive Configuration Register (RCR) 0CH(Write)       21         5.7.6       Receive Status Register (RSR) 0CH(Read)       22         5.7.7       Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8       Interrupt Status Register (ISR) 07H(Read/Write)       23         5.8       Network Tally Counter Registers (CNTR)       22         5.9       Number of Collisions Register (NCR)       22         5.10       Physical Address Register (PAR0-PAR5)       22         5.11       Multicast Address Registers (MAR0-MAR7)       22         5.12       DMA Registers       25         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.14       REMOTE DMA REGISTERS       25         5.15       (i) Local DMA Transmit Registers       25         5.16       (ii) Local DMA Receive Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                       |    |  |  |  |  |

| 5.7.6       Receive Status Register (RSR) OCH(Read)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 5.7.5 Receive Configuration Register (RCR) OCH(Write) | 20 |  |  |  |  |

| 5.7.7       Interrupt Mask Register (IMR) 0FH(Write)       22         5.7.8       Interrupt Status Register (ISR) 07H(Read/Write)       23         5.8       Network Tally Counter Registers (CNTR)       23         5.9       Number of Collisions Register (NCR)       24         5.10       Physical Address Register (PAR0-PAR5)       22         5.11       Multicast Address Registers (MAR0-MAR7)       22         5.12       DMA Registers       25         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.14       REMOTE DMA REGISTERS       25         5.15       (i) Local DMA Transmit Registers       25         5.16       (ii) Local DMA Receive Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                                       |    |  |  |  |  |

| 5.7.8       Interrupt Status Register (ISR) 07H(Read/Write).       23         5.8       Network Tally Counter Registers (CNTR).       23         5.9       Number of Collisions Register (NCR)       24         5.10       Physical Address Register (PAR0-PAR5)       24         5.11       Multicast Address Registers (MAR0-MAR7)       24         5.12       DMA Registers       25         5.13       LOCAL DMA RECEIVE REGISTERS       25         5.14       REMOTE DMA REGISTERS       25         5.15       (i) Local DMA Transmit Registers       25         5.16       (ii) Local DMA Receive Registers       26         5.17       (iii) Remote DMA registers       26         6       Electrical Specification and Timing       28         7       Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 0 ( , ,                                               |    |  |  |  |  |

| 5.8 Network Tally Counter Registers (CNTR)       22         5.9 Number of Collisions Register (NCR)       24         5.10 Physical Address Register (PAR0-PAR5)       24         5.11 Multicast Address Registers (MAR0-MAR7)       24         5.12 DMA Registers       25         5.13 LOCAL DMA RECEIVE REGISTERS       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                       |    |  |  |  |  |

| 5.9 Number of Collisions Register (NCR)       24         5.10 Physical Address Register (PAR0-PAR5)       24         5.11 Multicast Address Registers (MAR0-MAR7)       24         5.12 DMA Registers       25         5.13 LOCAL DMA RECEIVE REGISTERS       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                       |    |  |  |  |  |

| 5.10 Physical Address Register (PAR0-PAR5)       24         5.11 Multicast Address Registers (MAR0-MAR7)       24         5.12 DMA Registers       25         5.13 LOCAL DMA RECEIVE REGISTERS       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                                       |    |  |  |  |  |

| 5.11 Multicast Address Registers (MAR0-MAR7)       24         5.12 DMA Registers       25         5.13 LOCAL DMA RECEIVE REGISTERS       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         6 Electrical Specification and Timing       28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                       |    |  |  |  |  |

| 5.12 DMA Registers       25         5.13 LOCAL DMA RECEIVE REGISTERS       25         5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26         Flectrical Specification and Timing       28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                       |    |  |  |  |  |

| 5.14 REMOTE DMA REGISTERS       25         5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26 <b>Electrical Specification and Timing</b> 28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 5.12 DMA Registers                                    | 25 |  |  |  |  |

| 5.15 (i) Local DMA Transmit Registers       25         5.16 (ii) Local DMA Receive Registers       26         5.17 (iii) Remote DMA registers       26 <b>Electrical Specification and Timing</b> 28         7 Physical Dimension       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.13 LOCAL DMA RECEIVE REGISTERS                      | 25 |  |  |  |  |

| 5.16 (ii) Local DMA Receive Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 5.14 REMOTE DMA REGISTERS                             | 25 |  |  |  |  |

| 5.17 (iii) Remote DMA registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                       |    |  |  |  |  |