**TOSHIBA** TC9235P/F

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9235P, TC9235F

# **ELECTRONIC VOLUME**

The TC9235P and TC9235F are an optimum CMOS IC which has been designed for electronization of volume control of audio equipment, etc.

## **FEATURES**

- Attenuation can be controlled from 0dB to -78dB by up, down input.

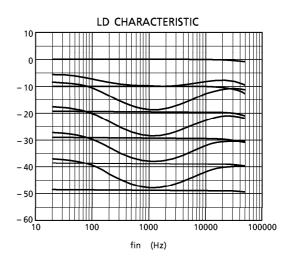

- This IC have 20dB tap for loudness circuit.

- This IC features a built-in DC output circuit (7 level) for volume level meter.

- Polysilicon resistors enables low-distortion, highperformance volume systems.

- Volume level remains in backup mode with low current consumption.

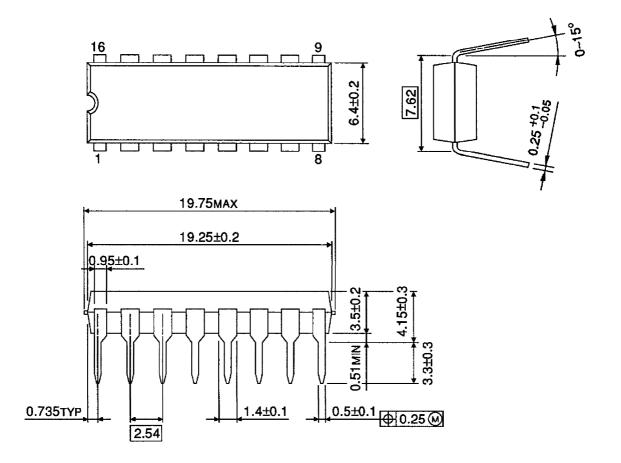

- Package is DIP16 and SOP16.

Weight

DIP16-P-300-2.54A SOP16-P-300-1.27

: 1.0g (Typ.) : 0.16g (Typ.)

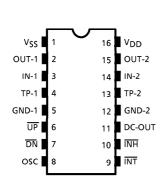

### PIN CONNECTION

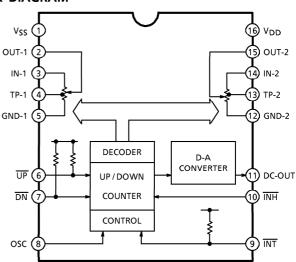

#### **BLOCK DIAGRAM**

980508EBA2

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

## **PIN FUNCTION**

| PIN<br>No. | SYMBOL   | PIN NAME                         | FUNCTION AND OPERATION                                                                                                         | NOTE                            |  |

|------------|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| 1          | $v_{SS}$ | Negative power supply pin        | Power supply terminal                                                                                                          |                                 |  |

| 16         | $V_{DD}$ | Positive power supply pin        | Power supply terminal                                                                                                          |                                 |  |

| 2          | OUT-1    | Volume output pins               |                                                                                                                                |                                 |  |

| 15         | OUT-2    | Volume output pins               | Volume circuit                                                                                                                 |                                 |  |

| 3          | IN-1     | Valuma input pins                |                                                                                                                                |                                 |  |

| 14         | IN-2     | Volume input pins                | OUT                                                                                                                            |                                 |  |

| 4          | TP-1     | Tap output pins for              | TP S                                                                                                                           | _                               |  |

| 13         | TP-2     | loudness                         |                                                                                                                                |                                 |  |

| 5          | GND-1    | Analan anaund nine               |                                                                                                                                |                                 |  |

| 12         | GND-2    | Analog ground pins               |                                                                                                                                |                                 |  |

| 6          | ŪP       | Volume up input pin              | Volume up, down control input pin. The 1 step/1 push volume is controlled by pushing the Up or Down key. If the key            | Built-in<br>pull-up             |  |

| 7          | DΝ       | Volume down input pin            | has been pushed continuously, the continuous volume control.                                                                   | resistor                        |  |

| 8          | osc      | Oscillation pin                  | Oscillation pin. Oscillator circuit consist of C·R connection. Oscillation is executed while key is pushed.                    | _                               |  |

| 9          | ĪNT      | Initializing pin                 | Input pin for setting initial volume level volume level set to 46dB by "L" input.                                              | Built-in<br>pull-up<br>resistor |  |

| 10         | ĪNH      | Inhibit terminal                 | Back up mode input pin. Internal all operation is stopped by "L" input, and volume level remains with low current consumption. | _                               |  |

| 11         | DC-OUT   | DC output pin for level<br>meter | DC output pin for volume level meter. DC voltage which is corresponded to volume step is generated.                            | _                               |  |

980508EBA2'

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

#### **OPERATION**

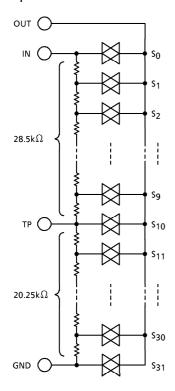

#### 1. Volume circuit

Volume circuit consist of ladder resistor and analog switch.

Tap for loudness is connected to step 10 (20dB).

Attenuation is as follows when resistor (3.9k $\Omega$ ) is connected between TP pin and GND pin.

## • Equivalence circuit

• Volume step and attenuation (Attenuation is as follows when resistor (3.9k $\Omega$ ) is connected between TP pin and GND pin.)

| connected between in pin and and pin., |              |      |             |  |  |  |

|----------------------------------------|--------------|------|-------------|--|--|--|

| STEP                                   | ATTENUATION  | STEP | ATTENUATION |  |  |  |

| 0                                      | 0 (dB)       | 16   | 32 (dB)     |  |  |  |

| 1                                      | 2            | 17   | 34          |  |  |  |

| 2                                      | 4            | 18   | 36          |  |  |  |

| 3                                      | 6            | 19   | 38          |  |  |  |

| 4                                      | 8            | 20   | 40          |  |  |  |

| 5                                      | 10           | 21   | 42          |  |  |  |

| 6                                      | 6 12<br>7 14 |      | 46          |  |  |  |

| 7                                      |              |      | 50          |  |  |  |

| 8                                      | 16           | 24   | 54          |  |  |  |

| 9                                      | 18           | 25   | 58          |  |  |  |

| 10                                     | 20           | 26   | 62          |  |  |  |

| 11                                     | 22           | 27   | 66          |  |  |  |

| 12                                     | 24           | 28   | 70          |  |  |  |

| 13                                     | 26           | 29   | 74          |  |  |  |

| 14                                     | 28           | 30   | 78          |  |  |  |

| 15                                     | 30           | 31   | $\infty$    |  |  |  |

<sup>\*</sup> Step 22 (46dB) initial value.

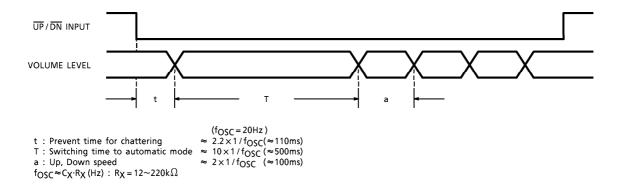

2. Volume up, down control circuit

Volume up, down control is executed by UP, DN key input.

- The 1 step/1 push volume is controlled by "L" level of  $\overline{UP}$ ,  $\overline{DN}$  key.

- If  $\overline{UP}$ ,  $\overline{DN}$  key is input "L" continuously, volume level is changed continuously.

- Timing of key input

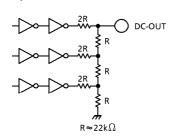

## 3. DC output circuit for volume level

DC output for volume level meter is internally connected to D-A converter (R/2R type).

8 stage output voltage which is corresponded to volume level is generated.

Because output impedance  $\approx$  22k $\Omega$  (typ.) is high, If input impedance of next setting level meter IC is low, set to Buffer.

# • Equivalence circuit

# • Volume step and Output voltage

| STEP  | ATTENUATION (dB) | OUTPUT VOLTAGE<br>(V) |  |  |

|-------|------------------|-----------------------|--|--|

| 0~ 3  | 0~ 6             | 7/8 V <sub>DD</sub>   |  |  |

| 4~ 7  | 8~14             | 6/8 V <sub>DD</sub>   |  |  |

| 8~11  | 16~22            | 5/8 V <sub>DD</sub>   |  |  |

| 12~15 | 24~30            | 4/8 V <sub>DD</sub>   |  |  |

| 16~19 | 32~38            | 3/8 V <sub>DD</sub>   |  |  |

| 20~23 | 40~50            | 2/8 V <sub>DD</sub>   |  |  |

| 24~27 | 54~66            | 1/8 V <sub>DD</sub>   |  |  |

| 28~31 | 70~∞             | 0                     |  |  |

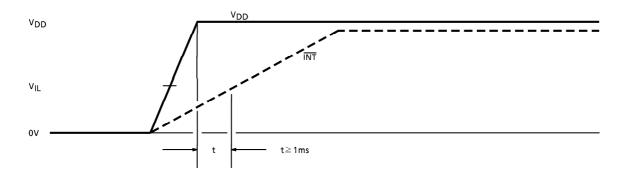

# 4. Initialization and Backup operation

## (1) Initialization operation

When power on, volume level is set to initial value (46dB) by setting  $\overline{INT}$  pin to "L" level for a while.

Adjust condenser value which is set  $\overline{\text{INT}}$  pin to the period while  $\overline{\text{INT}}$  pin is "L" level is longer than 1ms when power on.

## (2) Backup operation

Internal operation is all stopped when  $\overline{\text{INH}}$  pin is "L" level, and prohibit input and output. Volume data is remains while Backup mode with low current consumption.

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                    | UNIT     |

|-----------------------|------------------|---------------------------|----------|

| Supply Voltage        | V <sub>DD</sub>  | -0.3~15                   | V        |

| Input Voltage         | VIN              | -0.3~V <sub>DD</sub> +0.3 | <b>V</b> |

| Power Dissipation     | PD               | 300                       | mW       |

| Operating Temperature | T <sub>opr</sub> | <b>- 40∼85</b>            | °C       |

| Storage Temperature   | t <sub>stg</sub> | <b>-</b> 55∼150           | °C       |

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, Ta = 25°C, V<sub>DD</sub> = 9V)

| CHARACTERISTIC                    |                  | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                                                                                     |                      | MIN.                    | TYP. | MAX.                  | UNIT             |

|-----------------------------------|------------------|------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|------|-----------------------|------------------|

| Operating Supply<br>Voltage       |                  | V <sub>DD</sub>  | _                    | Ta = −40~85°C                                                                                                                                                      |                      | 4.5                     | 9.0  | 12                    | V                |

| Operating Supply<br>Current       |                  | I <sub>DD</sub>  | 1                    | No load, f <sub>OSC</sub> = 20Hz                                                                                                                                   |                      | 1                       | 0.3  | 1.0                   | mA               |

| Backup Volt                       | age              | $V_{QD}$         | _                    | · <del>INH</del> = "L"                                                                                                                                             |                      | 2.0                     | ~    | 12                    | V                |

| Backup Current                    |                  | lQD              | 1                    | IINH = L                                                                                                                                                           |                      |                         | 0.01 | 1.0                   | $\mu$ A          |

| Input<br>Voltage                  | "H" Level        | V <sub>IH</sub>  |                      | All in must min                                                                                                                                                    |                      | ∨ <sub>DD</sub><br>×0.7 | ~    | V <sub>DD</sub>       | V                |

|                                   | "L" Level        | V <sub>IL</sub>  | _                    | All input pin                                                                                                                                                      |                      | 0                       | ~    | V <sub>DD</sub> × 0.3 |                  |

| Input                             | "H" Level        | ΊΗ               |                      | INH input pin                                                                                                                                                      | $V_{IH} = V_{DD}$    | - 1                     | _    | 1                     | μΑ               |

| Current                           | "L" Level        | IJL              | _                    |                                                                                                                                                                    | V <sub>IL</sub> = 0V | <b>– 1</b>              |      | 1                     |                  |

| Pull Up Resi                      | Pull Up Resistor |                  | _                    | UP, DN, INT input pin                                                                                                                                              |                      | 23                      | 47   | 71                    | kΩ               |

| Volume Resi                       | stor             | R <sub>VR</sub>  | _                    | Between IN→GND resistor                                                                                                                                            |                      | 31                      | 44   | 58                    | kΩ               |

| Analog Switch ON<br>Resistor      |                  | RON              | _                    | Analog switch ON resistor                                                                                                                                          |                      | -                       | 500  | 800                   | Ω                |

| Attenuation                       | Error            | ∆ATT             | _                    | _                                                                                                                                                                  |                      | _                       | 0    | ± 2.0                 | dB               |

| Balance Between Left<br>And Right |                  | ⊿R <sub>VR</sub> | _                    | Volume resistor error between left and right                                                                                                                       |                      |                         | 0    | ± 3.0                 | %                |

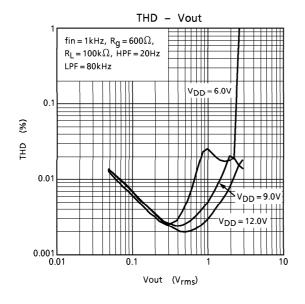

| Total Harmonic Distortion         |                  | THD              |                      | f <sub>IN</sub> = 1kHz                                                                                                                                             | 0dB                  | _                       | 0.01 | _                     | %                |

| Maximum Attenuation               |                  | ATTMAX           | 1                    | $\begin{aligned} &\text{V}_{\text{IN}} = 1 \text{V}_{\text{rms}} \\ &\text{R}_{\text{L}} = 100 \text{k} \Omega \\ &\text{R}_{\text{g}} = 600 \Omega \end{aligned}$ | ∞dB                  | _                       | 100  | _                     | dB               |

| Cross Talk                        |                  | C∙T              | 1                    |                                                                                                                                                                    | 0dB                  | _                       | 100  | _                     | dB               |

| Output Noise Voltage              |                  | ٧N               | 1                    |                                                                                                                                                                    |                      | _                       | 2.0  | _                     | $\mu$ V $_{rms}$ |

| OSC Frequency                     |                  | fosc             | 1                    | $C_X = 2.2 \mu F$ , RX = 33ks                                                                                                                                      | )                    | _                       | 20   | _                     | Hz               |

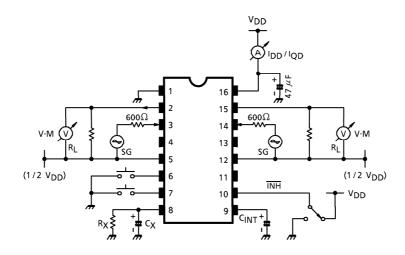

## **TEST CIRCUIT 1**

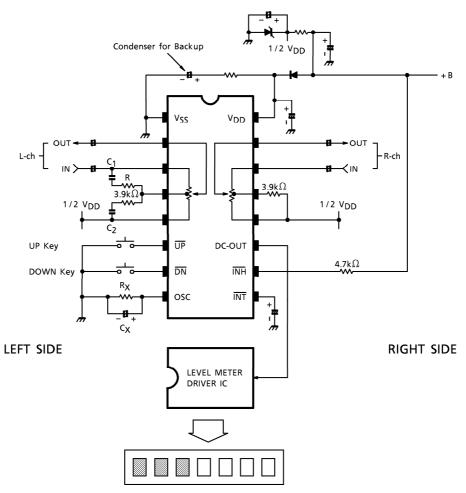

## **EXAMPLE OF APPLICATION CIRCUIT**

TOSHIBA TC9235P/F

## OUTLINE DRAWING DIP16-P-300-2.54A

Unit: mm

Weight: 1.0g (Typ.)

TOSHIBA TC9235P/F

#

Weight: 0.16g (Typ.)

Copyright Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com