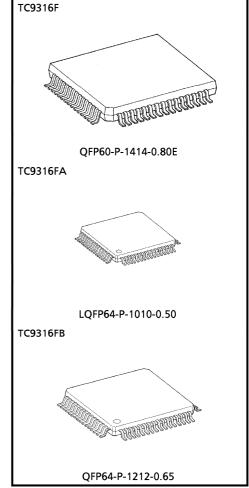

**TOSHIBA** TC9316F/FA/FB

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9316F, TC9316FA, TC9316FB

## DTS MICRO CONTROLLER CONTAINING PLL, LCD DRIVER (DTS-11)

TC9316F/FA/FB are a 4bit CMOS microcontroller for digital tuning system capable of making 3V low voltage operation, and containing PLL circuit, LCD driver. CPU has 4bit parallel addition and substruction (AI/SI instructions, etc.), logical operation (OR and AN instructions, etc.), plural bit judge, comparison instructions (TM, SL instructions, etc.) and time base function.

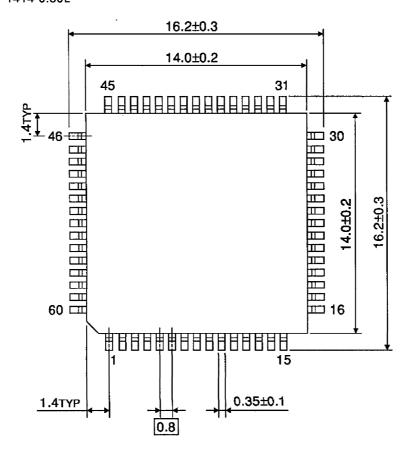

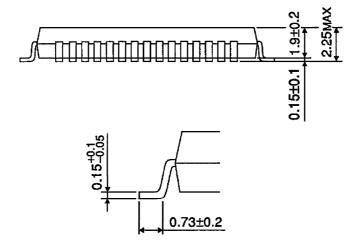

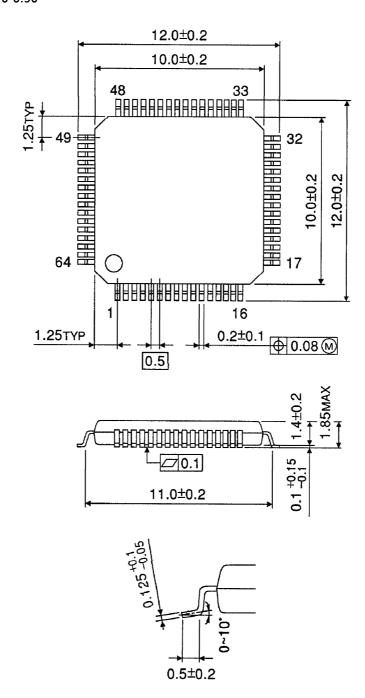

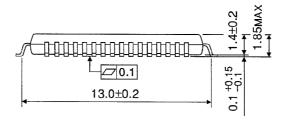

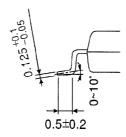

The package is 60 pin mini-flat type (TC9316F), 64 pin mini-flat type (TC9316FA, TC9316FB) and has abundant I/O ports and exclusive key-input ports controlled by the powerful input/output instructions (IO, KEY instructions), besides containing PLL circuit.

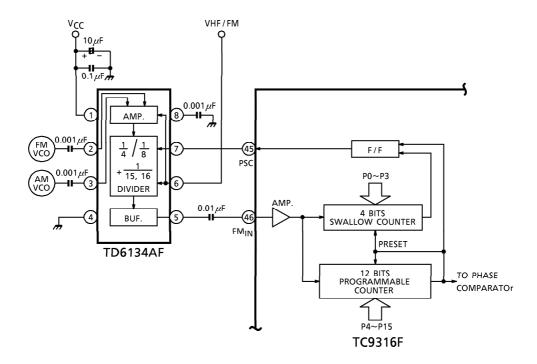

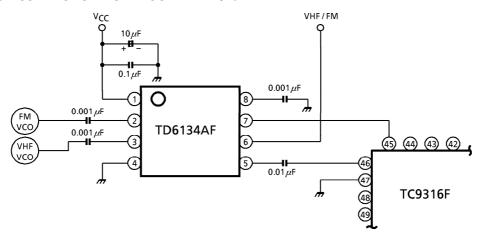

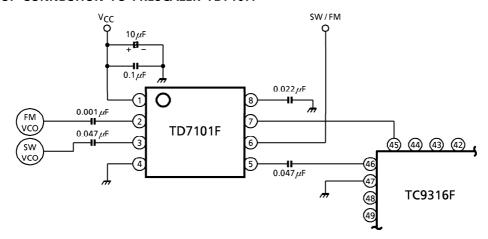

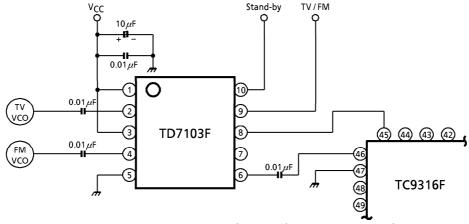

By combining with the prescaler TD6134AF or TD7101F or TD7103F, it permits the configuration of DTS that receives FM/AM and TV (VHF) bands.

#### **FEATURES**

- 4bit micro controller for digital tuning system use

- It is operated with 3V single power supply.  $(V_{DD} = 1.8 \sim 3.6 V)$

- Back-up of data memory (RAM) and each port are easily made. (by INH terminal)

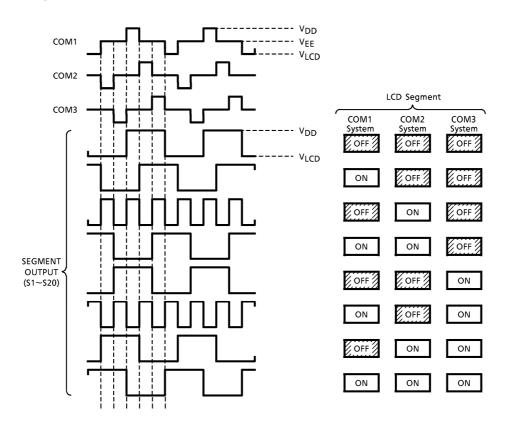

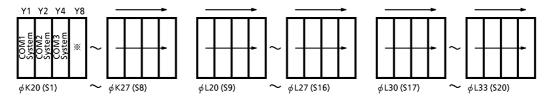

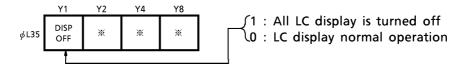

- Built-in LCD driver (1/3 duty, 1/2 bias driving, driving frequency: 52Hz), and boosting circuit for display

- Program memory (ROM): 16bit × 2048 steps

- Data memory (RAM): 4bit × 128 words

- Powerful instruction set of 65 kinds. (all single word instruction)

Weight

QFP60-P-1414-0.80E : 0.85g (Typ.) LQFP64-P-1010-0.50 : 0.32g (Typ.) QFP64-P-1212-0.65 : 0.45g (Typ.)

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

- Instruction executing time  $80 \mu s$ . (75kHz crystal connection)

- Abundant addition and substruction instructions.

(addition instructions 12 kinds, substraction instructions 12 kinds)

- Powerful compound judge instructions. (TMTR, TMFR, TMT, TMF, TMTN, TMFN instructions)

- Data transfer in same low address is possible.

- Indirect transfer of register is possible. (MVRD, MVRS, MVGD, MVGS instructions)

- 16 powerful general registers. (arranged in RAM)

- Stack level: 1 level

- Program memory (ROM) has no conception of page, field, and JUMP and CAL instruction can be freely made among 2048 steps.

- At the FM or TV band, swallow counter is composed by combining with prescaler TD6134AF or TD7103F, and is able to receive TV VHF band. At the AM or FM band, swallow counter is composed by combining with prescaler TD7101F, and is able to receive SW, AM, FM band.

- It is possible to freely refer to the content, 16 bits, of optional address within 1024 steps in program memory (ROM). (DAL instruction)

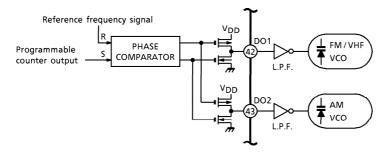

- Independent frequency input terminal at FM and AM (FM<sub>IN</sub>, AM<sub>IN</sub>), and two phase-comparator outputs. (DO1, DO2)

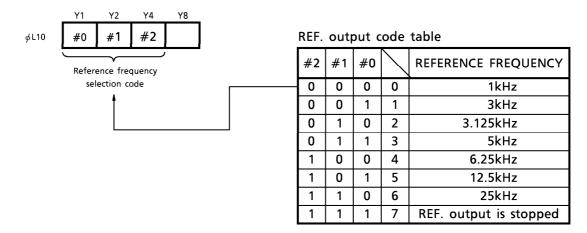

- 7 kinds of reference frequency can be selected with program.

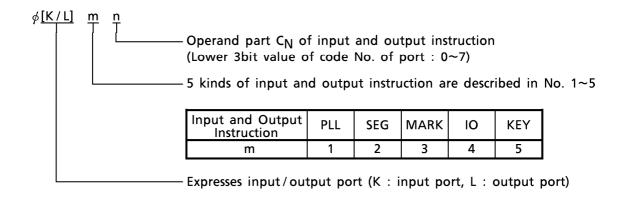

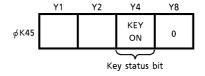

- Powerful input / output instructions, (IO, KEY instructions)

- Exclusive input port (K0~K3) for key input use and abundant 23 exclusive LCD driving terminals.

- Abundant 15 I/O ports (ports for which input and output can be assigned for each bit: 8, exclusive output ports: 7)

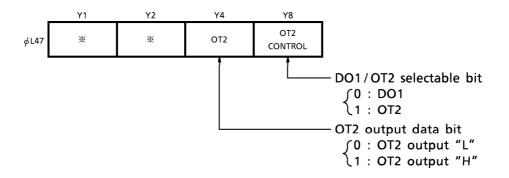

- $IF_{\mbox{\footnotesize{IN}}}$  port and DO1 port are able to use IN port (exclusive input port) and OT2 port (exclusive output port) by changing instruction.

- 3 kinds of back-up mode (only CPU operating, crystal oscillation and clock stop) are possible by instructions.

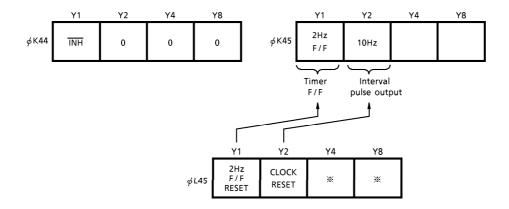

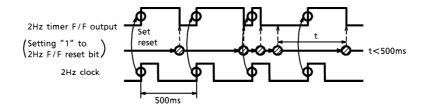

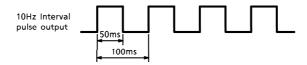

- 2Hz timer F/F and 10Hz interval pulse output are contained. (Internal port for time base use)

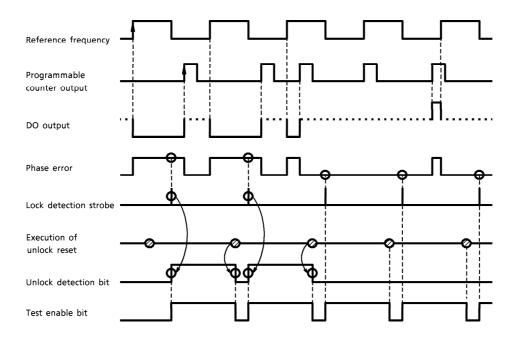

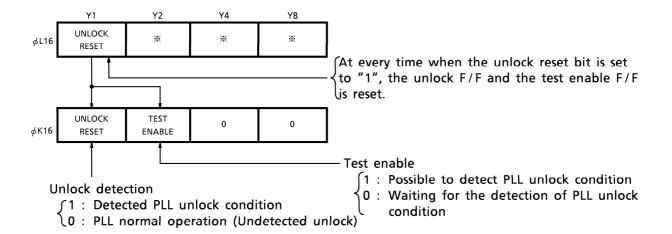

- Locked condition of PLL can be detected.

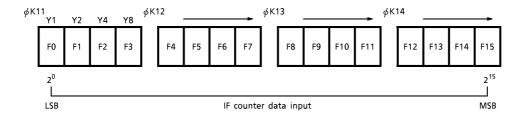

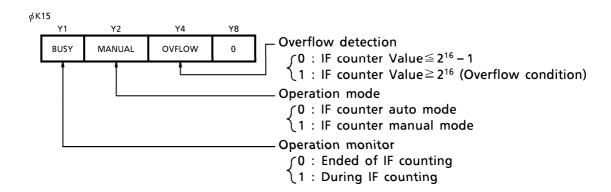

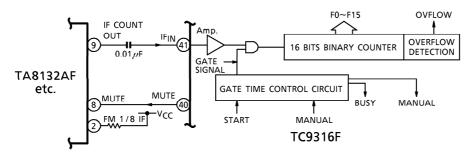

- Universal-type IF counter is built in.

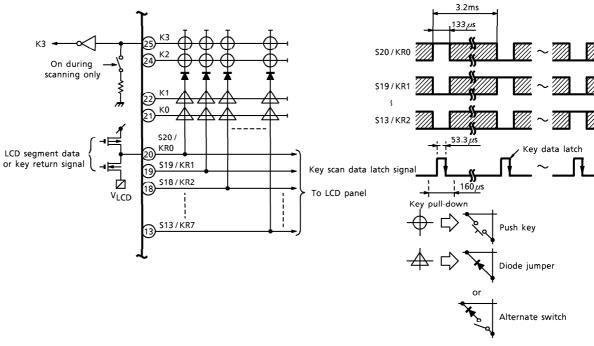

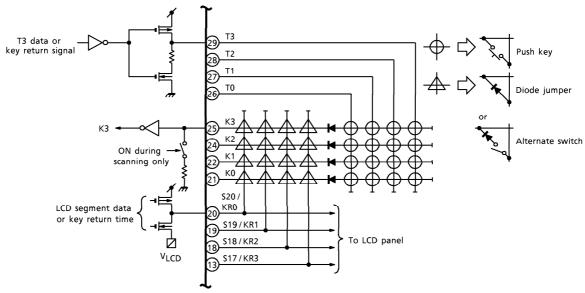

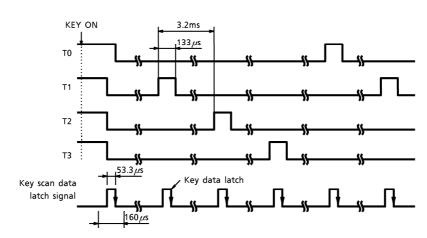

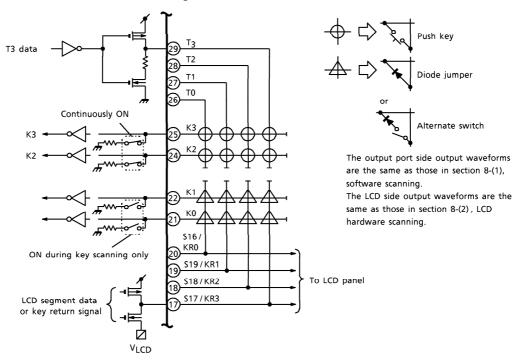

- 8 output ports in LCD segment ports (\$13~\$20) are able to use as Key Return Timing output ports. Exclusive output ports are not only use Key Return Timing output ports but use the others.

- 16bit universal-type IF counter is built in, it is able to detect the auto stop signal at auto-tuning mode with counting intermediate frequency of each band.

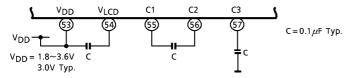

- Built-in 3V voltage regulation circuit for driving LCD.

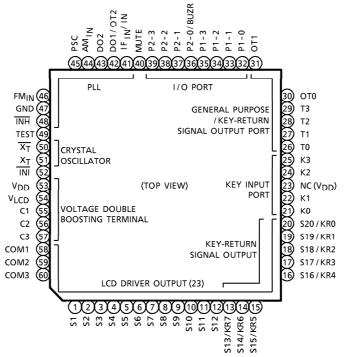

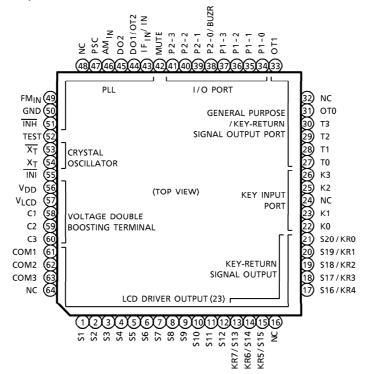

#### **PIN CONNECTION**

(TC9316F)

(TC9316FA, TC9316FB)

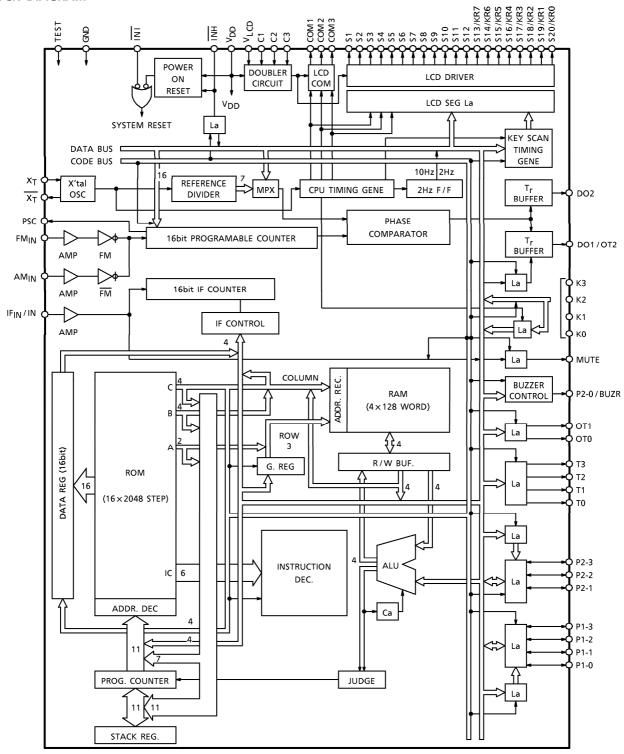

#### **BLOCK DIAGRAM**

**PIN FUNCTION** (Data in parenthesises are for TC9316FA, TC9316FB)

| PIN No.                                  | SYMBOL                    | PIN NAME                                     | EXPLANATION OF FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                   | REMARKS          |

|------------------------------------------|---------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 58<br>(61)                               | COM1                      |                                              | This is a common signal output terminal to LCD.                                                                                                                                                                                                                                                                                         | V <sub>DD</sub>  |

| 59<br>(62)                               | COM2                      | LCD Common<br>Output                         | Indication of maximum 60 segments is possible with matrix made with \$1~\$20. To this terminal, three value levels of                                                                                                                                                                                                                   | V <sub>EE</sub>  |

| 60<br>(63)                               | сомз                      |                                              | V <sub>DD</sub> , V <sub>EE</sub> , V <sub>LCD</sub> are output with 3.2ms interval and 52Hz cycle.                                                                                                                                                                                                                                     | VLCD             |

| 1~12                                     | \$1~\$12                  | LCD Segment<br>Output                        | This is a segment signal output terminal to LCD. Indication of maximum 60 segments is possible with matrix made with COM1, COM2 and COM3. The data for these terminals are output by the execution of SEG instruction and MARK instruction.                                                                                             |                  |

| 13~20<br>(13~15)<br>(17~21)              | \$13 / KR7<br>~\$20 / KR0 | LCD Segment<br>Output / Key<br>Return Output | S13 / KR7~S20 / KR0 are able to output LCD segment signal and Key Return Timing signal at same time by program. Maximum 32 (=8×4) Key input be able to combine with matrix made with Key input ports K0~K3 without the other output port.                                                                                               | V <sub>LCD</sub> |

| 21, 22<br>24, 25<br>(22, 23)<br>(25, 26) | K0~K3                     | Key Input Port                               | This is a 4bit input port for key matrix input.  It is able to input data of maximum total 56 key, maximum 24 key (= 6 × 4) with matrix made with Key Return Timing output port, besides maximum 32 key (8 × 4) with matrix made with LCD Segment Output \$13 / KR7~\$20 / KR0. All these terminals are built in pull down resistances. | VDD<br>RIN1      |

| PIN No.            | SYMBOL                | PIN NAME                                       | EXPLANATION OF FUNCTION AND OPERATION                                                                                                                                                                                                  | REMARKS                                    |

|--------------------|-----------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 26~29<br>(27~30)   | T0~T3                 | General Purpose<br>/ Key Return                | This is a 6bit output port for General Purpose / Key Return Timing output. Besides use for general purpose output port, it is able to output the timing                                                                                |                                            |

| 30, 31<br>(31, 33) | OT0, OT1              | Timing Output<br>Port                          | signal for key matrix by program. For making the key matrix, it is built in load resistance at N-ch FET side, useless the diode when uses Push key.                                                                                    | RON                                        |

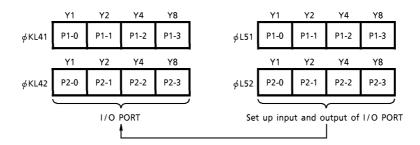

| 32~35<br>(34~37)   | P1-0~P1-3             | I/O Port                                       | This is a 8bit general purpose I/O Port. It is possible to assign input and output                                                                                                                                                     | V <sub>DD</sub> V <sub>DD</sub>            |

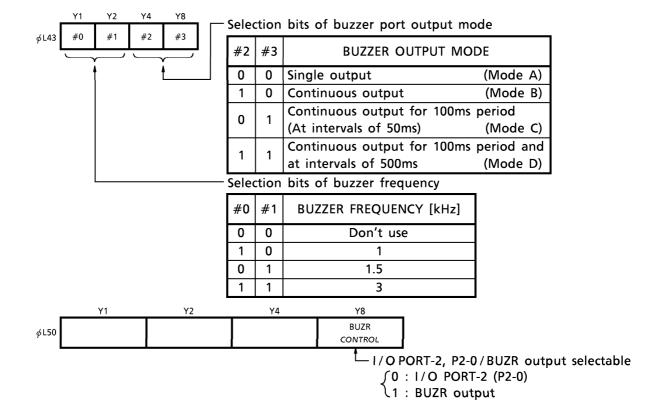

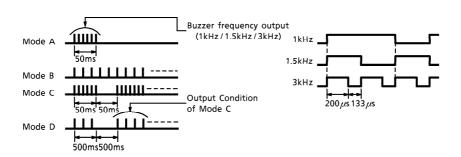

| 36<br>(38)         | P2-0/BUZR             | I/O Port/Buzzer<br>Pulse Output<br>Port        | for each bit by program. P2-0 is able to use as the beep sound pulse output port by program.                                                                                                                                           |                                            |

| 37~39<br>(34~41)   | P2-1~P2-3             | I/O Port                                       | It is able to output 3 kinds of the beep sound pulse signal by program.                                                                                                                                                                |                                            |

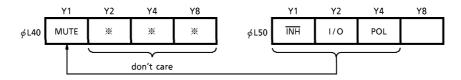

| 40<br>(42)         | MUTE                  | Muting Output<br>Port                          | This is a 1bit output port. This is usually used as muting control signal output.                                                                                                                                                      | VD THE |

| 41<br>(43)         | IF <sub>IN</sub> / IN | If Counter Input<br>Port/Input Port            | This is an If signal input terminal of 16bit general purpose IF counter. This terminal has built-in amplifiers, and operates with C-connection and small amplitude. It is able to use as a 1bit general purpose input port by program. | Rfin                                       |

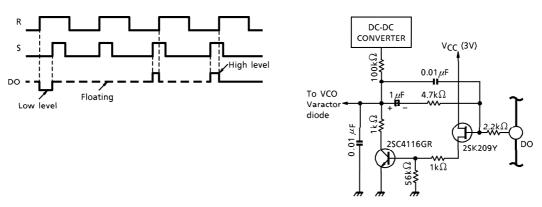

| 42<br>(44)         | DO1/OT2               | Phase<br>Comparator<br>Output / Output<br>port | This is a phase comparator output terminal of PLL. DO1 and DO2 are parallel outputs. Therefore, optimum filter constant can                                                                                                            | VD ↓ ↓ ↓ ↓                                 |

| 43<br>(45)         | DO2                   | Phase I<br>Comparator I                        | be set for each band of FM/AM.  DO1 is able to use as a 1bit general purpose output port by program.                                                                                                                                   |                                            |

| PIN No.    | SYMBOL           | PIN NAME                            | EXPLANATION OF FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                 | REMARKS                                 |

|------------|------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

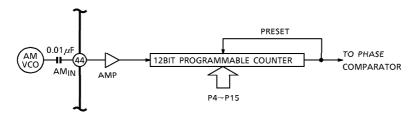

| 44<br>(46) | AM <sub>IN</sub> | AM<br>Programmable<br>Counter Input | This is a programmable counter input terminal at 12bit direct frequency-divider mode. Usually the local oscillator signal at AM band is input to this terminal. This terminal has built-in amplifiers, and operated with C-connection and small amplitude.                                                                                                            | Rfin                                    |

| 45<br>(47) | PSC              | Prescaler Control<br>Output         | This is an output terminal which controls 1/15 or 1/16 frequency-dividing mode of two modulus prescaler. This output signal controls two frequency-dividing mode of external prescaler as using programmable counter for pluse-swallow counter. "H": 1/16, "L": 1/15                                                                                                  | V D D D D D D D D D D D D D D D D D D D |

| 46<br>(49) | FMIN             | FM Programable<br>Counter Input     | This is an input terminal of programmable counter at 16bit swallow-counter mode. This terminal is input the divided frequency output signal of external prescaler, and has built-in input amplifiers and operates with C-connection and small amplitude.                                                                                                              | REGIN                                   |

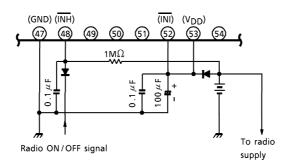

| 48<br>(51) | ĪNH              | Inhibit Input                       | This is a signal input terminal for selecting radio mode. "H": radio ON, "L": radio OFF                                                                                                                                                                                                                                                                               |                                         |

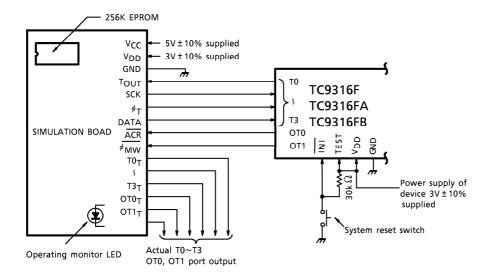

| 49<br>(52) | TEST             | Test Input                          | This is an input terminal for controlling test mode control. At "H" level, test mode is made, and at "L" level, normal operation is carried out. In the test mode, the device operates as evaluator chip, and program evaluation is made possible on EPROM base through combination with external simulation board. This terminal is built in a pull-down resistance. | V <sub>DD</sub>                         |

| PIN No.            | SYMBOL                 | PIN NAME                                                    | EXPLANATION OF FUNCTION AND OPERATION                                                                                                                                  | REMARKS           |

|--------------------|------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

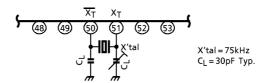

| 50<br>(53)         | $\overline{x_T}$       | Crystal<br>Oscillation                                      | This is a connecting terminal of crystal resonator. Reference crystal of 75kHz is connected.                                                                           | Nout Refer to VDD |

| 51<br>(54)         | Χ <sub>T</sub>         | Terminal                                                    | During the execution of CKSTP instruction, oscillation is automatically stopped.                                                                                       | X <sub>T</sub>    |

| 52<br>(55)         | ĪNĪ                    | Initializing Input                                          | This is a system reset signal input terminal of the device.  During INT is at "L" level, reset is applied, and when it becomes "H" level, it is normal operation mode. | V <sub>DD</sub>   |

| 54 (57)            | V <sub>LCD</sub>       | Voltage Double                                              | These are voltage double boosting                                                                                                                                      |                   |

| 55 (58)            | <b>C</b> 1             | Boosting                                                    | terminal for driving LCD.                                                                                                                                              | _                 |

| 56 (59)            | C2                     | Terminal                                                    | Boosting capacitiors are connected to these terminals. (Typ. $0.1\mu\text{F}\sim3.3\mu\text{F}$ )                                                                      |                   |

| 57<br>(60)         | C3                     | Reference Voltage Stabilizing Capacitor Connecting Terminal | The stabilizing capacitor of Reference Voltage is connected to this terminal for LCD driving. (Typ. $0.01\mu F\sim 0.1\mu F$ )                                         | _                 |

| 53 (56)<br>47 (50) | V <sub>DD</sub><br>GND | Power Supply<br>Terminal                                    | Power supply voltage is applied.  VDD = 1.8~3.6V (Typ. 3.0V)                                                                                                           | _                 |

#### **EXPLANATION OF OPERATION**

#### ○ CPU

CPU is composed of program counter, stack register, ALU, program memory, data memory, Gregister, carry F/F and judging circuit.

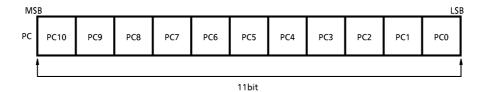

#### 1. Program counter (PC)

Program Counter is a block to designate the address of program memory (ROM), and is composed of 11 bits binary up counter. This is cleared by system reset, and the program starts from zero address.

Usually, it's increment is made one by one everytime the one instruction is executed, but when JUMP instruction or CAL instruction is executed, the address designated at operand part of that instruction is loaded.

Further, when the instruction (AIS, SLT, TMT, RNS instructions, etc.) having skip function is executed, two increments of program counter is made if the result is the condition to be skipped, and the succeeding instruction is skipped.

## 2. Stack register (STACK)

This is a register composed of  $1 \times 11$  bits during the execution of subroutine call instruction, the value obtained by adding +1 to the content of program counter, namely return address, is housed. The content of stack register is loaded on the program counter by the execution of return instruction. (RN, RNS instructions)

This stack level is 1 level, and nesting is 1 level.

## 3. ALU

ALU has binary 4 bits parallel addition and subtraction, logical operation, comparison and plural bit judge functions.

This CPU has no accumulator, and all operations directly treat the contents of data memory.

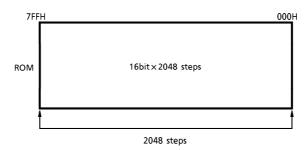

#### 4. Program memory (ROM)

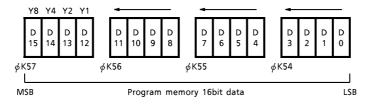

Program memory is composed of 16bit × 2048 steps and is the address of 000H~7FFH.

Program memory has no concept of page or field, so JUMP instruction and CAL instruction can be freely used among 2048 steps.

Further, it is possible to use optional address of program memory as data area, and its content, 16 bits, can be loaded to the data register by executing DAL instruction.

(Note) Provide the data area at the address outside the program loop in the program memory.

(Note) In DAL instruction, the address of program memory can be designated as the data area becomes 1024 steps of 000H~3FFH.

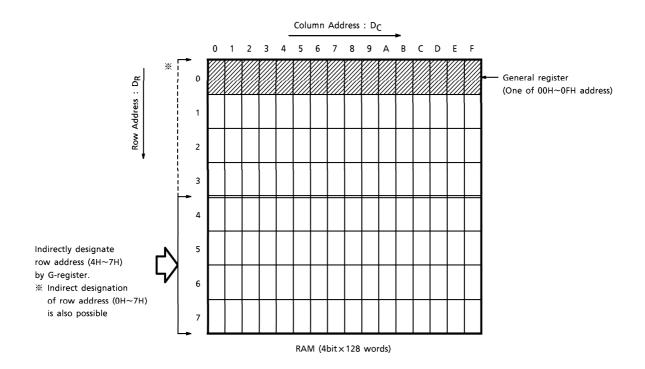

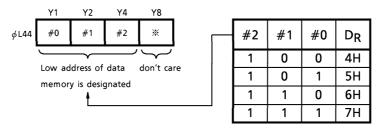

#### 5. Data memory (RAM)

Data memory is composed of 4bit x 128 words and used for storing data.

This 128 words are expressed with row address (3 bits) and column address (4 bits). 64 words (row address = 4H~7H) among the data memory are indirect addressing by G-register. For this reason, when carrying out data processing within this territory, it is necessary to designate row address by G-register beforehand Area of 00H~0FH address in data memory is called general register, and can be used only by designating column address (4 bits). These 16 general registers can be used for operation and transfer between data memories. Further, it can also be used as ordinary data memory.

- (Note) The column address (4 bits) to designate general register becomes register number of the general register.

- (Note) It is also possible to indirectly designate all of row address (=0H~7H) by G-register.

#### 6. G-register (G-REG.)

G-register is a 3 bits register for addressing row address ( $D_R = 4H \sim 7H$ ) of 64 words in data memory.

Content of this register is effective during executing MVGD instruction, MVGS instruction, and is not related with the execution of other instructions.

This register is treated as one of the port, and its content is set by the execution of IO instruction among input and output instructions.

(refer to register port item 1 page 39)

#### 7. Data register (DATA REG.)

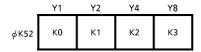

This is a register composed of  $1 \times 16$  bits. In this register, 16 bits data of optional address among the program memory is loaded during executing of DAL instruction. This register is treated as one of the port, and when KEY instruction among input and output instruction is executed, it's content is read in the data memory in 4 bits unit.

(refer to register port item 2 page 39)

## 8. Carry F/F (C·F/F)

This is set when carry or borrow is produced as a result of executing operational instruction, and is reset when it is not produced. Content of carry F/F changes only when addition and subtraction instruction is executed, and does not change during the execution of other instructions.

## 9. Judging circuit (J)

When a instruction with skip function is executed, this circuit judges it's skip condition. When skip condition is satisfied, this circuit makes two increments of program counter, and skips the succeeding instruction.

It is provided with 31 kinds of instructions having abundant skip function. (refer to Item 11, explanation list of function and operation of instructions, % marked instruction page 13~19)

## 10. List of instruction set

65 kinds of instruction set are included, all of which consisting of one word instruction. These instructions are expressed with 6 bits instruction code.

|             | Rank<br>2 bits | 00                     | 01        | 10                                   | 11                        |

|-------------|----------------|------------------------|-----------|--------------------------------------|---------------------------|

| Rank 4 bits |                | 0                      | 1         | 2                                    | 3                         |

| 0000        | 0              | Al M, I                | AD r, M   | LD r, M                              | SLTI M, I                 |

| 0001        | 1              | AIS M, I               | ADS r, M  | ST M, r                              | SGEI M, I                 |

| 0010        | 2              | AIN M, I               | ADN r, M  | MVRD r, M                            | SEQI M, I                 |

| 0011        | 3              | SI M, I                | SU r, M   | MVRS M, r                            | SNEI M, I                 |

| 0100        | 4              | SIS M, I               | SUS r, M  | MVSR M <sub>1</sub> , M <sub>2</sub> | SLT r, M                  |

| 0101        | 5              | SIN M, I               | SUN r, M  | MVIM M, I                            | SGE r, M                  |

| 0110        | 6              | CAL ADDR               | ORR r, M  | MVGD r, M                            | SEQ r, M                  |

| 0111        | 7              | CAL ADDR <sub>1</sub>  | ANDR r, M | MVGS M, r                            | SNE r, M                  |

| 1000        | 8              | AIC M, I               | AC r, M   | PLL M, C                             | TMTR r, M                 |

| 1001        | 9              | AICS M, I              | ACS r, M  | SEG M, C                             | TMFR r, M                 |

| 1010        | Α              | AICN M, I              | ACN r, M  | MARK M, C                            | TMT M, N                  |

| 1011        | В              | SIB M, I               | SB r, M   | IO M, C                              | TMF M, N                  |

| 1100        | С              | SIBS M, I              | SBS r, M  | KEY M, C                             | TMTN M, N                 |

| 1101        | D              | SIBN M, I              | SBN r, M  | WAIT P                               | TMFN M, N                 |

| 1110        | Е              | IIIMD ADDD             | ORIM M, I | XORIM M, I                           | DAL ADDR <sub>2</sub> , r |

| 1111        | F              | JUMP ADDR <sub>1</sub> | ANIM M, I | XORR r, M                            | RN, RNS, CKSTP, NOOP      |

TOSHIBA TC9316F/FA/FB

11. Explanation list of function and operation of instructions (Explanation of symbols)

M : Data memory address

Normally, one of 00H~3FH address of data memory.

r : General register

One of 00H~0FH address of data memory.

PC : Program counter (11bit)

STACK : Stack register (11bit)

G : G-register (3bit)

DATA : Data register (16bit)

I : Immediate data (4bit)

N : Bit position (4bit)

— : All "0"

C : Code No. of port (4bit)

C<sub>N</sub>: Lower rank 3bit of port code No.

R<sub>N</sub> : General register No. (4bit)

ADDR<sub>1</sub>: Program memory address in page 0 or 1 (10bit)

ADDR<sub>2</sub>: Higher rank 6bit of program memory address in page 0

Ca : Carry b : Borrow

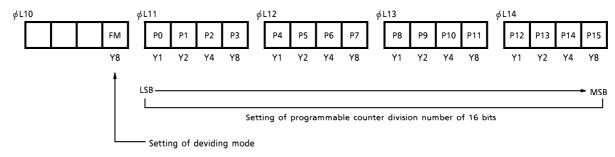

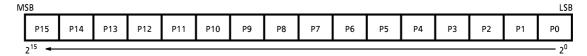

PLL : Port treated during the execution of PLL instruction

SEG : Port treated during the execution of SEG instruction

MARK : Port treated during the execution of MARK instruction

IO : Port treated during the execution of IO instruction

KEY : Port treated during the execution of KEY instruction

( ) : Register or data memory content

[ ]C : Content of port indicated by code No. C (4bit)

[ ] : Content of data memory indicated by the content of register or data memory

[ ]p : Content of program memory (16bit)

IC : Instruction code (6bit)

: Instruction having skip function

DC

: Data memory column address (4bit)

DR

: Data memory row address (2bit)

P : Wait condition select bit at WAIT instruction

(Note) Address 000H~3FFH of program memory address: Page 0 area Address 400H~7FFH of program memory address: Page 1 area

| -            | . MNEMONIC |               | EXPLANATION OF EXPLANATION OF                                         |                                       |              | NE LAN         | IE LANGUAGE (16b |                |  |  |

|--------------|------------|---------------|-----------------------------------------------------------------------|---------------------------------------|--------------|----------------|------------------|----------------|--|--|

| INST.<br>GR. | MNEMONIC   | SKIP<br>FUNCT | FUNCTION                                                              | OPERATION                             | IC<br>(6bit) | A<br>(2bit)    | B<br>(4bit)      | C<br>(4bit)    |  |  |

|              | Al M, I    |               | Add immediate data to memory                                          | M←(M) + I                             | 000000       | D <sub>R</sub> | DC               | -              |  |  |

|              | AIS M, I   | *             | Add immediate data to memory, then skip if carry                      | M←(M) + I<br>Skip if carry            | 000001       | D <sub>R</sub> | DC               | 1              |  |  |

|              | AIN M, I   | *             | Add immediate data to memory, then skip if not carry                  | M←(M) + I<br>Skip if not carry        | 000010       | D <sub>R</sub> | DC               | -              |  |  |

|              | AIC M, I   |               | Add immediate data to memory with carry                               | M←(M) + I + ca                        | 001000       | D <sub>R</sub> | DC               | _              |  |  |

| TION         | AICS M, I  | *             | Add immediate data to memory with carry, then skip if carry           | M←(M) + I + ca<br>Skip if carry       | 001001       | D <sub>R</sub> | D <sub>C</sub>   | _              |  |  |

| NSTRUCTION   | AICN M, I  | *             | Add immediate data<br>to memory with carry,<br>then skip if not carry | M←(M) + I + ca<br>Skip if not carry   | 001010       | D <sub>R</sub> | DC               | I              |  |  |

| N - N        | AD r, M    |               | Add memory to general register                                        | r←(r) + (M)                           | 010000       | D <sub>R</sub> | DC               | R <sub>N</sub> |  |  |

| ADDITION     | ADS r, M   | *             | Add memory to<br>general register, then<br>skip if carry              | r←(r) + (M)<br>Skip if carry          | 010001       | D <sub>R</sub> | DC               | R <sub>N</sub> |  |  |

| ₹            | ADN r, M   | *             | Add memory to general register, then skip if not carry                | r←(r) + (M)<br>Skip if not carry      | 010010       | D <sub>R</sub> | DC               | R <sub>N</sub> |  |  |

|              | AC r, M    |               | Add memory to general register with carry                             | r←(r) + (M) + ca                      | 011000       | D <sub>R</sub> | DC               | R <sub>N</sub> |  |  |

|              | ACS r, M   | *             | Add memory to general register with carry, then skip if carry         | r←(r) + (M) + ca<br>Skip if carry     | 011001       | D <sub>R</sub> | DC               | R <sub>N</sub> |  |  |

|              | ACN r, M   | *             | Add memory to general register with carry, then skip if not carry     | r←(r) + (M) + ca<br>Skip if not carry | 011010       | D <sub>R</sub> | DC               | R <sub>N</sub> |  |  |

| . <del>.</del> . | NANIENA ONUC | NO L            | EXPLANATION OF                                                                      | EXPLANATION OF                        | MACHI        | NE LAN         | GUAGE       | JAGE (16bit)   |  |

|------------------|--------------|-----------------|-------------------------------------------------------------------------------------|---------------------------------------|--------------|----------------|-------------|----------------|--|

| INST.<br>GR.     | MNEMONIC     | SK I P<br>FUNCT | FUNCTION                                                                            | OPERATION                             | IC<br>(6bit) | A<br>(2bit)    | B<br>(4bit) | C<br>(4bit)    |  |

|                  | SI M, I      |                 | Subtract immediate data from memory                                                 | M←(M) – I                             | 000011       | D <sub>R</sub> | DC          | I              |  |

|                  | SIS M, I     | *               | Subtract immediate data from memory, then skip if borrow                            | M←(M) – I<br>Skip if borrow           | 000100       | D <sub>R</sub> | DC          | l              |  |

|                  | SIN M, I     | *               | Subtract immediate data from memory, then skip if not borrow                        | M←(M) – I<br>Skip if not borrow       | 000101       | D <sub>R</sub> | DC          | I              |  |

| z                | SIB M, I     |                 | Subtract immediate data from memory, with borrow                                    | M←(M) – I – b                         | 001011       | D <sub>R</sub> | DC          | I              |  |

| STRUCTION        | SIBS M, I    | *               | Subtract immediate data from memory with borrow, then skip if borrow                | M←(M) – I – b<br>Skip if borrow       | 001100       | D <sub>R</sub> | DC          | -              |  |

| Z<br> -          | SIBN M, I    | *               | Subtract immediate data from memory with borrow, then skip if not borrow            | M←(M) – I – b<br>Skip if not borrow   | 001101       | D <sub>R</sub> | DC          | I              |  |

| ACTI             | SU r, M      |                 | Subtract memory from general register                                               | r←(r) – (M)                           | 010011       | D <sub>R</sub> | Dc          | R <sub>N</sub> |  |

| SUBTRACTION      | SUS r, M     | *               | Subtract memory from<br>general register, then<br>skip if borrow                    | r←(r) – (M)<br>Skip if borrow         | 010100       | D <sub>R</sub> | DC          | R <sub>N</sub> |  |

|                  | SUN r, M     | *               | Subtract memory from<br>general register, then<br>skip if not borrow                | r←(r) – (M)<br>Skip if not borrow     | 010101       | D <sub>R</sub> | DC          | R <sub>N</sub> |  |

|                  | SB r, M      |                 | Subtract memory from general register with borrow                                   | r←(r) – (M) – b                       | 011011       | D <sub>R</sub> | DC          | R <sub>N</sub> |  |

|                  | SBS r, M     | *               | Subtract memory from<br>general register with<br>borrow, then skip if<br>borrow     | r←(r) – (M) – b<br>Skip if borrow     | 011100       | D <sub>R</sub> | DC          | R <sub>N</sub> |  |

|                  | SBN r, M     | *               | Subtract memory from<br>general register with<br>borrow, then skip if<br>not borrow | r←(r) – (M) – b<br>Skip if not borrow | 011101       | D <sub>R</sub> | DC          | R <sub>N</sub> |  |

| ·            | MNEMONIC |      | NOIL            | EXPLANATION OF EXPLANATION OF                                                   |                                                                                       |              | NE LAN         | GUAGE       | (16bit)        |

|--------------|----------|------|-----------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|----------------|-------------|----------------|

| INST.<br>GR. | MNEM     | ONIC | SK I P<br>FUNCT | FUNCTION                                                                        | OPERATION                                                                             | IC<br>(6bit) | A<br>(2bit)    | B<br>(4bit) | C<br>(4bit)    |

|              | SLTI     | М, І | *               | Skip if memory is less than immediate data                                      | Skip if (M) <i< td=""><td>110000</td><td>D<sub>R</sub></td><td>DC</td><td>I</td></i<> | 110000       | D <sub>R</sub> | DC          | I              |

|              | SGEI     | M, I | *               | Skip if memory is greater than or equal to immediate data                       | Skip if (M)≥I                                                                         | 110001       | D <sub>R</sub> | DC          | I              |

| NOIT         | SEQI     | M, I | *               | Skip if memory is equal to immediate data                                       | Skip if (M) = I                                                                       | 110010       | D <sub>R</sub> | DC          | I              |

| INSTRUCTION  | SNEI     | M, I | *               | Skip if memory is not equal to immediate data                                   | Skip if (M)≠I                                                                         | 110011       | D <sub>R</sub> | DC          | 1              |

|              | SLT      | r, M | *               | Skip if general register is less than memory                                    | Skip if (r)<(M)                                                                       | 110100       | D <sub>R</sub> | DC          | R <sub>N</sub> |

| COMPARISON   | SGE      | r, M | *               | Skip if general register is greater than or equal to memory                     | Skip if (r)≥(M)                                                                       | 110101       | D <sub>R</sub> | DC          | R <sub>N</sub> |

|              | SEQ      | r, M | *               | Skip if general register is equal to memory                                     | Skip if (r) = (M)                                                                     | 110110       | D <sub>R</sub> | DC          | R <sub>N</sub> |

|              | SNE      | r, M | *               | Skip if general register is not equal to memory                                 | Skip if (r)≠(M)                                                                       | 110111       | D <sub>R</sub> | DC          | R <sub>N</sub> |

| Z            | LD       | r, M |                 | Load memory to general register                                                 | r←(M)                                                                                 | 100000       | D <sub>R</sub> | DC          | R <sub>N</sub> |

| RUCTION      | ST       | M, r |                 | Store general register to memory                                                | M←(r)                                                                                 | 100001       | D <sub>R</sub> | DC          | R <sub>N</sub> |

| ER INST      | MVRD     | r, M |                 | Move memory to destination memory referring to general register in the same row | $[D_R, (r)] \leftarrow (M)$                                                           | 100010       | D <sub>R</sub> | Dc          | R <sub>N</sub> |

| TRANSF       | MVRS     | M, r |                 | Move source memory referring to general register to memory in the same row      | M←[D <sub>R</sub> , (r)]                                                              | 100011       | D <sub>R</sub> | Dc          | R <sub>N</sub> |

| ST.         | MNEMONIC    |                   | EXPLANATION OF                                                                     | EXPLANATION OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MACHI          | NE LAN         | GUAGE           | (16            | bit)           |

|-------------|-------------|-------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----------------|----------------|----------------|

| INS<br>GR.  | MINEMONIC   | SK I P<br>FUNCT I | FUNCTION                                                                           | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IC<br>(6bit)   | A<br>(2bit)    | B<br>(4bit)     | (4             | C<br>lbit)     |

| STRUCTION   | MVSR M1, M2 |                   | Move memory to memory in the same row                                              | $(D_R, D_{C1}) \leftarrow (D_R, D_{C2})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100100         | D <sub>R</sub> | D <sub>C1</sub> | [              | PC2            |

| RUC         | MVIM M, I   |                   | Move immediate data to memory                                                      | M←I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100101         | $D_{R}$        | DC              |                | _              |

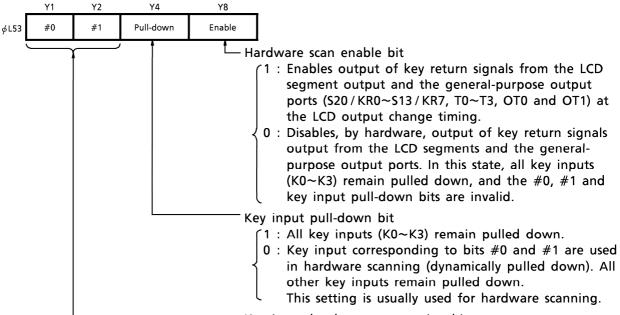

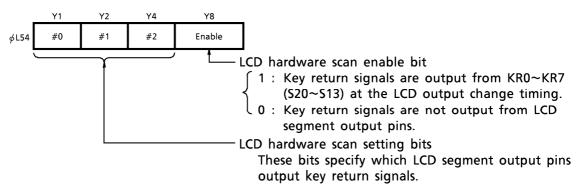

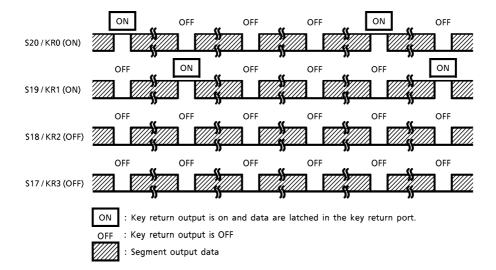

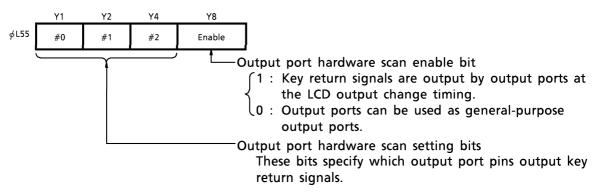

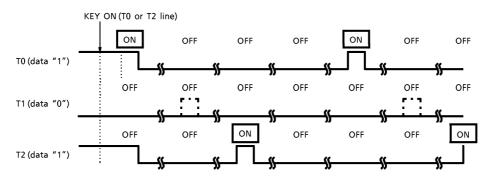

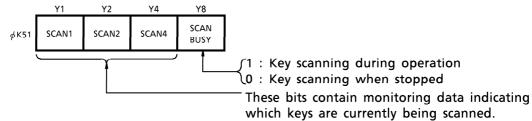

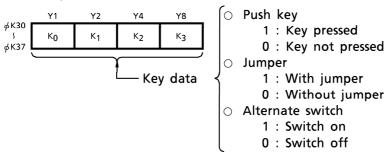

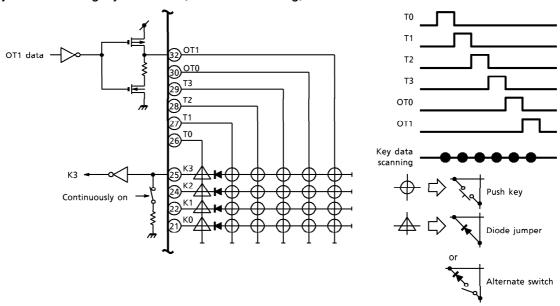

| ER IN       | MVGD r, M   |                   | Move memory to destination memory referring to G-register and general register     | 100110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D <sub>R</sub> | DC             |                 | R <sub>N</sub> |                |