**TENTATIVE**

TOSHIBA BIPOLAR DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

### TD7624AFN

# 3-WIRE AND I<sup>2</sup>C BUS SYSTEM, 1.3 GHz DIRECT TWO MODULUS-TYPE FREQUENCY SYNTHESIZER FOR TV AND CATV

The TD7624AFN can be combined with a micro CPU to create a highly functional frequency synthesizer. The control data conforms to 3-wire bus and standard I<sup>2</sup>C bus formats. BUS-SW can be used to easily switch for easy tuner system set-up.

#### **FEATURES**

- Direct two modulus-type frequency synthesizer

- Standard I<sup>2</sup>C bus format control with built-in read mode

- 3-wire bus format control

- 18-bit and 19-bit automatic discrimination circuit (when 3-wire bus selected)

- High voltage tuning amplifier Not built-in (built-in type available)

- 4-bit bandswitch drive transistor

- 5-level A/D converter (when I<sup>2</sup>C bus selected)

- Frequency Step: 31.25 kHz, 50 kHz and 62.5kHz (at 4 MHz X'tal used)

- Phase lock detector

- Various function settings via program data

- Four address settings via address selector (when I<sup>2</sup>C bus selected)

- Power on reset circuit

f.dzsc.com

- Flat, compact package: SSOP16 (0.65 mm pitch)

- Power on reset operation condition

Bandswitch register 1 to 4 : OFF

Tuning amplifier : ON

Charge-pump output current :  $\pm 60 \mu A$

Phase comparator reference frequency divider ratio : 1/64

(Note) These devices are easy to be damaged by high static voltage or electric fields. In regards to this, please handle with care.

0000105041

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

Weight: 0.07 g (Typ.)

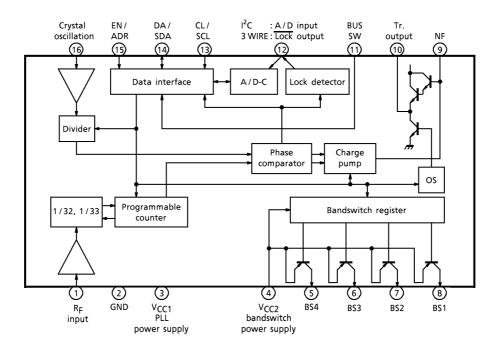

#### **BLOCK DIAGRAM**

#### MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| Supply Voltage 1      | V <sub>CC1</sub> | 6.0             | V    |

| Supply Voltage 2      | V <sub>CC2</sub> | 12              | V    |

| Power Dissipation     | PD               | 560             | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>- 20∼85</b>  | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>- 55∼150</b> | °C   |

- (Note 1) When using the device at above Ta = 25°C, decrease the power dissipation by 4.5 mW for each increase of 1°C.

- (Note 2) These devices are easy to be damaged by high static voltage or electric fields. In regards to this, please handle with care.

#### **RECOMMENDED SUPPLY VOLTAGE**

| PIN<br>No. | PIN NAME                                    | MIN              | TYP. | MAX | UNIT |

|------------|---------------------------------------------|------------------|------|-----|------|

| 3          | V <sub>CC1</sub> : PLL Power Supply         | 4.5              | 5.0  | 5.5 | V    |

| 4          | V <sub>CC2</sub> : Band Switch Power Supply | V <sub>CC1</sub> |      | 9.9 | V    |

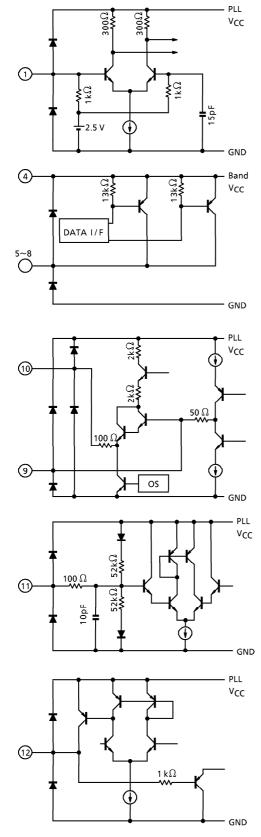

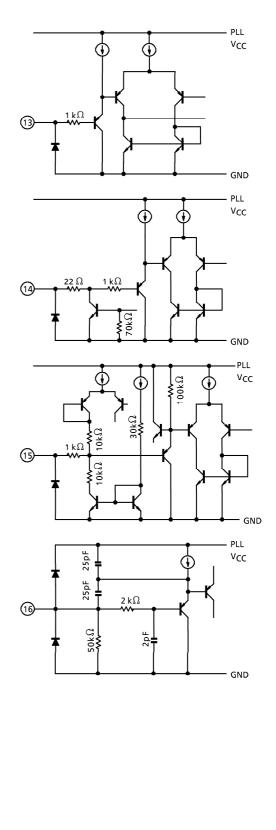

#### PIN INTERFACE

### **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, $V_{CC1} = 5 \text{ V}$ , $V_{CC2} = 9 \text{ V}$ , $Ta = 25^{\circ}\text{C}$ )

| CHARACTERISTIC                   | SYMBOL                 | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                 | MIN              | TYP. | MAX                       | UNIT       |  |

|----------------------------------|------------------------|----------------------|----------------------------------------------------------------|------------------|------|---------------------------|------------|--|

| Supply Voltage 1                 | V <sub>CC1</sub>       | _                    | _                                                              | 4.5              | 5.0  | 5.5                       | V          |  |

| Supply Current 1                 | lCC1                   | 1                    | Bandswitch : OFF<br>V <sub>t</sub> : OFF                       | 13               | 16   | 21                        | mA         |  |

| Supply Voltage 2                 | V <sub>CC2</sub>       | _                    | _                                                              | V <sub>CC1</sub> | _    | 9.9                       | V          |  |

| Supply Current 2                 | I <sub>CC2</sub> -1    | 1                    | Bandswitch : 1 Band ON IBD = 30 mA (LOAD)                      |                  | 35   | 39                        | mA         |  |

|                                  | I <sub>CC2</sub> -2    | •                    | Bandswitch : 2 Band ON<br>I <sub>BD</sub> = 40 mA (TOTAL LOAD) | -                | 50   | 58                        |            |  |

| Bandswitch Drive<br>Current      | I <sub>BD</sub>        | 3                    | Maximum Drive Current /<br>1 port                              | 1                | -    | 30                        | mA         |  |

| Bandswitch Drive<br>Maximum LOAD | IBDMAX                 | 3                    | Maximum Total Drive Current                                    | _                | _    | 50                        | mA         |  |

| Bandswitch Drive<br>Voltage Drop | V <sub>BD</sub><br>Sat | 3                    | I <sub>BD</sub> = 30 mA                                        |                  | 0.2  | 0.4                       | V          |  |

| X'tal Operating Range            | OSCf <sub>in</sub>     | _                    | _                                                              | 3.2              | _    | 4.5                       | MHz        |  |

| X'tal Negative<br>Resistance     | osc <sub>R</sub>       | 1                    | _                                                              | 1.0              | 1.5  | _                         | kΩ         |  |

| X'tal External Input<br>Level    | osc <sub>in</sub>      | _                    | 3.2 MHz $\sim$ 4.5 MHz, Rx = 91 k $\Omega$                     | 250              | -    | 1000                      | mVp-p      |  |

| Datia Catting Dange              | N14                    |                      | 15-bit counter                                                 | 1024             | _    | 32767                     | Ratio      |  |

| Ratio Setting Range              | N13                    | -                    | 14-bit counter                                                 | 1024             | _    | 16384                     | Ratio      |  |

| Prescaler Input                  | V <sub>in1</sub>       | 2                    | f = 80~150 MHz                                                 | - 25             |      | + 5                       | dBmW       |  |

| Sensitivity                      | V <sub>in2</sub>       | ]                    | f = 150~1300 MHz                                               | - 30             | _    | + 5                       | GEIIIVV    |  |

| Lock Output Low<br>Voltage       | $V_{LkL}$              | 1                    | (lock mode, 3-wire bus mode)                                   |                  | -    | 0.4                       | V          |  |

| Lock Output High<br>Voltage      | $V_{LkH}$              | 1                    | (unlock mode, 3-wire bus mode)                                 | 4.6              |      |                           | V          |  |

| Logic Input Low<br>Voltage       | V <sub>BsL</sub>       | 1                    | Pins 13 to 15                                                  | - 0.3            | 1    | 1.5                       | >          |  |

| Logic Input High<br>Voltage      | V <sub>BsH</sub>       | 1                    | Pins 13 to 15                                                  | 3.0              |      | V <sub>CC1</sub><br>+ 0.3 | V          |  |

| Logic Input Current<br>(low)     | I <sub>BsL</sub>       | 1                    | Pins 13 to 15                                                  | - 20             | _    | 10                        | μΑ         |  |

| Logic Input Current (high)       | I <sub>BsH</sub>       | 1                    | Pins 13 to 15                                                  | - 10             | _    | 20                        | μ <b>Α</b> |  |

| BUS-SW Low Input<br>Voltage      | V <sub>BIL</sub>       | 1                    | _                                                              | 0.0              | _    | 0.8                       | v          |  |

| BUS-SW High Input<br>Voltage     | V <sub>BIH</sub>       | 1                    | _                                                              | 4.2              | _    | V <sub>CC1</sub>          |            |  |

|                                                        |                     | TEST         |                                                      |               |               |                  |                |     |   |  |  |

|--------------------------------------------------------|---------------------|--------------|------------------------------------------------------|---------------|---------------|------------------|----------------|-----|---|--|--|

| CHARACTERISTIC                                         | SYMBOL              | CIR-<br>CUIT | TEST CONDITION                                       | MIN           | TYP.          | MAX              | UNIT           |     |   |  |  |

| BUS-SW Low Current<br>(low)                            | I <sub>BIL</sub>    | 1            | _                                                    | - 200         | l             | I                | ^              |     |   |  |  |

| BUS-SW Low Current (high)                              | Івін                | 1            | _                                                    |               | ı             | 200              | μΑ             |     |   |  |  |

| Charge Pump Output<br>Current                          | I <sub>chg</sub>    | 2            | CP = [ 0 ]<br>CP = [ 1 ]                             | ± 50<br>± 230 | ± 60<br>± 280 | ± 90<br>± 420    | $\mu$ <b>A</b> |     |   |  |  |

| ACK Output Voltage                                     | V <sub>ACK</sub>    | 1            | I <sub>SINK</sub> = 3 mA (I <sup>2</sup> C-bus mode) | _             | _             | 0.4              | V              |     |   |  |  |

| A/D Converter Input<br>Voltage                         | V <sub>ADC</sub>    | _            |                                                      | 0.0           | _             | V <sub>CC1</sub> | V              |     |   |  |  |

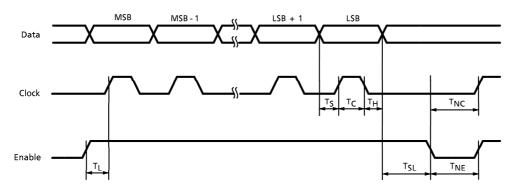

| Set-up Time                                            | T <sub>S</sub>      |              |                                                      | 2             | _             | _                |                |     |   |  |  |

| Enable Hold Time                                       | $T_{SL}$            |              |                                                      | 2             |               |                  |                |     |   |  |  |

| Next Enable Stop Time                                  | T <sub>NE</sub>     |              | (2 veins hus made)                                   | 6             | _             |                  |                |     |   |  |  |

| Next Clock Stop Time                                   | T <sub>NC</sub>     |              | (3-wire bus mode) Refer to data timing chart         | 6             | _             | _                | $\mu$ s        |     |   |  |  |

| Clock Width                                            | T <sub>C</sub>      |              | Refer to data tilling chart                          | 2             | _             |                  |                |     |   |  |  |

| Enable Set-up Time                                     | TL                  |              |                                                      | 10            |               |                  |                |     |   |  |  |

| Data Hold Time                                         | TH                  |              |                                                      | 2             |               |                  |                |     |   |  |  |

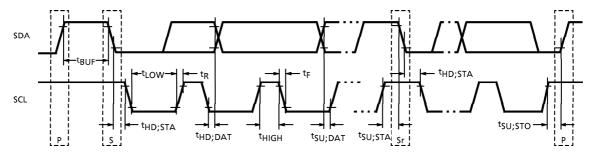

| SCL Clock Frequency                                    | fscl                | 1            |                                                      | 0             |               | 100              | kHz            |     |   |  |  |

| Bus Free Time Between<br>a STOP and START<br>Condition | t <sub>BUF</sub>    |              |                                                      |               |               |                  |                | 4.7 | _ |  |  |

| Hold Time (Repeated) START Condition                   | t <sub>HD;STA</sub> |              |                                                      | 4.0           |               |                  |                |     |   |  |  |

| Low Period of the SCL<br>Clock                         | tLOW                | _            |                                                      | 4.7           | _             | _                | μs             |     |   |  |  |

| High Period of the SCL<br>Clock                        | <sup>t</sup> HIGH   |              | (I <sup>2</sup> C bus mode)                          | 4.0           | _             | 1                |                |     |   |  |  |

| Set-up Time for a<br>Repeated START<br>Condition       | <sup>t</sup> SU;STA |              | Refer to data timing chart                           | 4.7           | -             |                  |                |     |   |  |  |

| Data Hold Time                                         | tHD;DAT             |              |                                                      | 0             | _             | _                |                |     |   |  |  |

| Data Set-up Time                                       | tsu;dat             | ]            |                                                      | 250           | _             | _                |                |     |   |  |  |

| Rise Time of both SDA and SCL Signals                  | t <sub>R</sub>      |              |                                                      | _             | _             | 1000             | ns             |     |   |  |  |

| Fall Time of both SDA and SCL Signals                  | t <sub>F</sub>      |              |                                                      | _             | _             | 300              |                |     |   |  |  |

| Set-up Time for STOP<br>Condition                      | <sup>t</sup> su;sTO |              |                                                      | 4.0           | _             | _                | μ\$            |     |   |  |  |

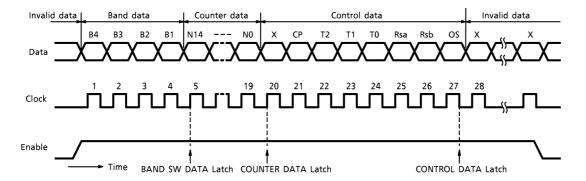

Fig.1 3-wire bus data timing chart (Falling edge timing)

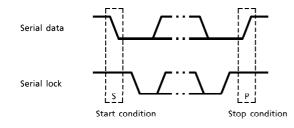

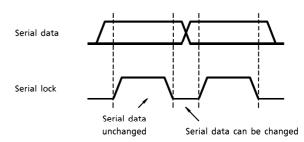

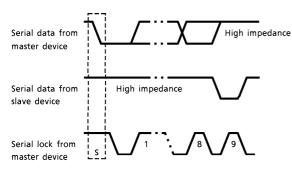

Fig.2 I<sup>2</sup>C bus data timing chart (Falling edge timing)

#### **OPERATION INSTRUCTIONS**

TD7624AFN can be controlled with either the 3-wire bus or standard I2C bus.

The 3-wire bus mode is equipped with an 18-bit/19-bit automatic selection circuit.

Frequency steps can be switched, depending on the voltage applied to the BUS-SW pin.

The I<sup>2</sup>C bus conforms to the standard I<sup>2</sup>C bus format. The bus supports two-way bus communications control, consisting of WRITE mode where data are received and READ mode where data are transmitted. In READ mode, the voltage applied on the A/D converter input pin can be transmitted and output with 5-level resolution.

(This function is only valid when the  $I^2C$  bus is selected. When the 3-wire bus is selected, the A/D converter input pin function as the  $\overline{LOCK}$  output pin.)

Addresses can be set using the hardware bits. Three programmable addresses are supported. 3-wire bus and standard I<sup>2</sup>C bus are switches by the voltage applied on the BUS-SW pin.

When the supply voltage ( $V_{CC1}$ ) is applied, the power-on reset circuit operates. Before data are input, counter data are all initialized to  $\llbracket 0 \rrbracket$ : band switches are all initialized to off.

#### **FUNCTION CHART**

| NAME       | 3-WIRE BUS MODE              | I <sup>2</sup> C BUS MODE |

|------------|------------------------------|---------------------------|

| BUS-SW     | 「OPEN」 or 「V <sub>CC</sub> 」 | 「 GND 」                   |

| CL/SCL     | CLOCK INPUT                  | SCL INPUT                 |

| DA / SDA   | DATA INPUT                   | SDA IN/OUTPUT             |

| EN/ADR     | ENABLE INPUT                 | ADDRESS                   |

| LOCK / ADC | <u> LOCK</u>                 | ADC                       |

#### — 3-WIRE BUS COMMUNICATIONS CONTROL —

The 3-wire bus used normal 18-bit and 19-bit data (bandswitch information and programmable counter information) and 27-bit test data (charge pump current setting, reference frequency divider ratio setting, and testing item functions) are available.

The program frequency can be calculated together with normal data and test data.

$fosc = f_r \times N$

fosc: Program frequency

f<sub>r</sub> : Phase comparator reference frequency (Step frequency)

N : Counter total ratio

#### (1) Normal data

Depending on the voltage (OPEN, V<sub>CC</sub>) applied on the BUS-SW pin and the transfer DATA bit length, the X'tal divider ratio setting, phase comparator reference frequency, and step frequency of the normal data are as shown in the table below.

#### NORMAL DATA FUNCTION TABLE

| BUS-SW<br>INPUT     | TRANSFER<br>DATA | X'TAL RATIO   | REFERENCE<br>FREQUENCY | STEP<br>FREQUENCY |

|---------------------|------------------|---------------|------------------------|-------------------|

| [ V <sub>CC</sub> ] | 18-bit           | Cannot be set | ←                      | ←                 |

| 「v <sub>CC</sub> 」  | 19-bit           | 1/80          | 50 kHz                 | 50 kHz            |

| 「 OPEN 」            | 18-bit           | 1 / 64        | 62.5 kHz               | 62.5 kHz          |

| 「 OPEN 」            | 19-bit           | 1 / 128       | 31.25 kHz              | 31.25 kHz         |

(Note 1) The step frequency at 4 MHz X'tal used

(Note 2) During "OPEN", automatically set with transmitted bit length (18↔19 possible)

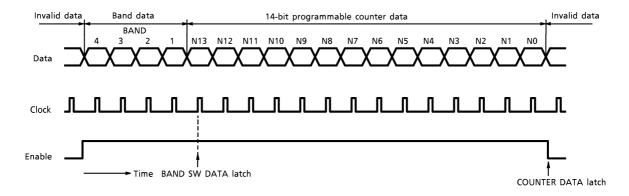

Fig.3 Normal data format (18-bit transmission)

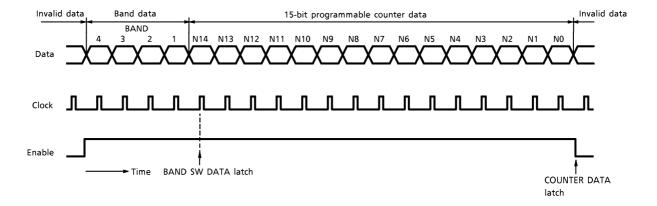

Fig.4 Normal data format (19-bit transmission)

#### • 18-bit DATA TRANSMISSION:

During a high level of the enable signal, the data is clocked into the register on the falling edge of the clock.

The clock number during a high level of the enable signal must be set to 18-bit for the latch condition. (The number of clock rising edges is 18).

For latch timing, the first four bits, which control the bandswitch buffers, are loaded at the fifth rising edge of the clock, and the data is updated.

The programmed counter data transmits the 18-bit data, latched on the falling edge of the enable signal.

During 18-bit data transmission, "N14" programmable counter data is constantly set to  $\lceil 0 \rceil$ , and the phase comparator reference frequency divider ratio is automatically set to "1/64".

Details of the data timing, see the data timing chart (Figure 1)

#### • 19-bit DATA TRANSMISSION:

During a high level of the enable signal, the data is clocked into the register on the falling edge of the clock.

The clock number during a high level of the enable signal must be set to 19-bit for the latch condition. (The number of clock rising edge is 19).

For latch timing, the first four bits, which control the bandswitch buffers, are loaded at the fifth rising edge of the clock, and the data is updated.

The programmed counter data transmits the 19-bit data, latched on the falling edge of the enable signal.

During 19-bit data transmission, the phase comparator reference frequency divider ratio is automatically set to "1/80" or "1/128" in BUS-SW mode.

Details of the data timing, see the data timing chart (Figure 1)

#### (2) TEST MODE

In the test mode, the settings can be changed and the functions can be checked.

Change from the normal mode to the test mode with a 27-bit or more of clock and data transmission during a high level of the enable signal.

The data are latched at the 27th falling edge of the clock signal, validating the previous 27-bit data. The latch timing is the same as normal data.

The 4-bit bandswitch data are latched at the 5th bit rising edge of the clock signal, and the data is updated.

The programmable counter data are latched at the 20th bit rising edge of the clock signal, and the data is updated.

The test data are latched at the 27th bit falling edge of the clock signal, and the data is updated.

When the mode is changed from test to normal, RSa changes depending on the data bit length (18 or 19 bits, automatic discrimination). The data set in RSb in test mode are retained (see the table below).

| REFERENCE FREQUENCY<br>DIVIDER RATIO SETTING<br>VIA TEST MODE | DATA<br>TRANSMISSION<br>LENGTH | SET REFERENCE<br>FREQUENCY DIVIDER<br>RATIO |

|---------------------------------------------------------------|--------------------------------|---------------------------------------------|

| 1/64                                                          | 18-bit                         | 1 / 64                                      |

| 1764                                                          | 19-bit                         | 1 / 128                                     |

| 1 / 90                                                        | 18-bit                         | 1 / 80                                      |

| 1 / 80                                                        | 19-bit                         | 1 / 80                                      |

| 1 / 128                                                       | 18-bit                         | 1 / 64                                      |

| 17 128                                                        | 19-bit                         | 1 / 128                                     |

Fig.5 Test data format

(Note) The data timing is the same as normal data.

#### **TEST DATA SPECIFICATIONS**

• B4~B1 : Band drive data

[ 0 ] : OFF [ 1 ] : ON

• N14~N0 : Programmable divider data

• CP : Charge pump output current

• T2, T1, T0 : Test mode setting bits

| CHARACTERISTIC             | T2 | T1 | ТО | NOTE                                                                          |

|----------------------------|----|----|----|-------------------------------------------------------------------------------|

| Normal operation           | 0  | 0  | 1  | _                                                                             |

| Reference signal output    | 1  | 0  | 0  | Reference signal output : B4, Counter output : B2                             |

| 1/2 counter divider output | 1  | 0  | 1  | Reference signal output: B4, 1/2 counter output: B2                           |

| Phase comparator test      | 0  | 0  | 0  | Comparative signal input : DA Reference signal input : CL (check output : NF) |

X : Don't care

(Note) When testing the counter divider output, programmable counter data input is necessary.

• Rsa, Rsb : X'tal Reference frequency divider ratio select bits

| RSa | RSb | DIVIDER RATIO | STEP FREQUENCY |

|-----|-----|---------------|----------------|

| 1   | 1   | 1 / 64        | 62.5 k         |

| 0   | 1   | 1 / 128       | 31.25 k        |

| Х   | 0   | 1/80          | 50.0 k         |

X : Don't care

(Note) When the mode is changed from test to normal, RSa changes depending on the data bit length (18 or 19 bits, automatic discrimination). The data set in RSb in test mode are retained.

• OS : Tuning amplifier control bit

**『0』: Tuning amp ON (Normal operation)**

[1]: Tuning amp OFF (Tr. Output is Low Level)

• X : Don't care

#### — I<sup>2</sup>C BUS COMMUNICATIONS CONTROL—

The TD7624AFN conform to standard I<sup>2</sup>C bus format.

The I<sup>2</sup>C bus mode enables two-way bus communications with the WRITE mode, which receives data, and READ mode, which status data.

WRITE and READ mode are set using the last bit (R/W bit) of the address byte.

If the last address bit is set to \[ 0 \], WRITE mode is set; if set to \[ 1 \] READ mode is set.

Address can be set using the hardware bits. Three programmable address can be programmed.

With this setting, multiple frequency synthesizers can be used in the same I<sup>2</sup>C bus line.

The address for the hardware bit setting can be selected by applying voltage to the address setting pin (ADR: Pin 15). An address is selected according to the set bits.

When the correct address byte is received, during acknowledgment, serial data (SDA) line is "Low".

If WRITE mode is set at this time, when the data byte is programmed, the serial data (SDA) line is "Low" during the next acknowledgment.

#### a) WRITE mode (setting command)

When WRITE mode is set, byte 1 segment the address data; bytes 2 and 3 segment the frequency data; byte 4 segment the divider ratio setting and function setting data; and byte 5 segment the output port data.

Data are latched and transferred at the end of byte 3, byte 4 and byte 5.

Byte 2 and byte 3 are latched and transferred is done with a two byte set (byte 2 + byte 3). Once a correct address is received and acknowledged, the data type is determined according to  $\lceil 0 \rceil$  or  $\lceil 1 \rceil$  set in the first bit of the next byte. That is, if the first bit is  $\lceil 0 \rceil$ , the data are frequency data; if  $\lceil 1 \rceil$ , function setting or output port data.

Until the I<sup>2</sup>C bus STOP CONDITION is detected, the additional data can be input without transmitting the address again. (Ex : Frequency sweep is possible with additional frequency data.)

If data transmission is aborted, data programmed before the abort are valid.

Byte 1 can set the hardware bit with address data.

The hardware bit is set with voltage applied to the address setting pin (ADR: Pin 15).

Bytes 2 and 3 are stored in the 15-bit shift register with counter data for the frequency setting, and control the 15-bit programmable counter ratio.

The program frequency can be calculated in the following formula:

$fosc = f_r \times N$

fosc: Program frequency

f<sub>r</sub>: Phase comparator reference frequency (Step frequency)

N : Counter total ratio

$f_r$  is calculated using the crystal oscillator frequency and the reference frequency divider ratio set in byte 4 (control byte). ( $f_r = X'$ tal oscillator frequency/reference frequency divider ratio)

The reference frequency divider ratio can be set to 1/64, 1/128 and 1/80.

When using a 4 MHz crystal oscillator,  $f_r = 62.5 \text{ kHz}$ , 31.25 kHz and 50 kHz.

The step frequency are 62.5kHz, 31.25kHz, and 50kHz.

Byte 4 is a control byte used to set function. Bit 2 (CP) controls the output current of the charge-pump circuit. When bit 2 is set to  $\ 0 \$ : the output current is set to  $\ \pm \ 60 \ \mu A$ ; when set to  $\ 1 \$ ,  $\ \pm \ 280 \ \mu A$ .

Bit 3 (T<sub>2</sub>), bit 4 (T<sub>1</sub>) and bit 5 (T<sub>0</sub>) are used to set test mode. They are used to set the phase comparator reference signal output, and counter divider output.

For details of test mode, see the test mode setting table.

Bit 6 (RSa) and bit 7 (RSb) are used to set the X'tal reference frequency divider ratio.

For details of the X'tal reference frequency divider ratios, see the table for X'tal reference frequency divider ratios.

Bit 8 (OS) is used to set the charge-pump drive amplifier output setting. When bit 8 is set to [0] the output is ON (Normal Use); when set to [1] the output is OFF (Tr. Output is Low Level).

Byte 5 is used to set and control the output port (Bands 1~4).

When an output port set to  $\lceil 0 \rceil$  is OFF; when set to  $\lceil 1 \rceil$  is ON.

Two output ports can be operation turned on, but be sure to keep the total output current under 50mA.

#### b) READ mode (status request)

When READ mode is set, power-on reset operation status, phase comparator lock detector output status, and 5-level A/D converter pin input voltage status are output to the master device.

Bit 1 (POR) indicates the power-on reset operation status. When the power supply of  $V_{CC1}$  stops, bit 1 is set to  $\llbracket 1 \rrbracket$ . The condition for reset to  $\llbracket 0 \rrbracket$ , voltage supplied to  $V_{CC1}$  is 3 V or higher, transmission is requested in READ mode, and the status is output. (when  $V_{CC1}$  is turned on, bit 1 is also set to  $\llbracket 1 \rrbracket$ .)

Bit 2 (FL) indicates the phase comparator lock status. When locked, [1] is output; when unlocked, [0] is output.

Bits 6, 7 and 8 ( $A_2$ ,  $A_1$ ,  $A_0$ ) indicate the 5-level A/D converter status. The voltage applied to the A/D converter input pin (pin 12) is output through a 5-level resolution.

For the voltage applied on the A/D converter input pin, 5-level resolution, and the output bits, see the table.

(Ex : The AFT output voltage data can be given to the master device.)

#### **DATA FORMAT**

#### a) WRITE MODE

|   | ВҮТЕ          | MSB |     |     |     |     |     |     | LSB     |                   |

|---|---------------|-----|-----|-----|-----|-----|-----|-----|---------|-------------------|

| 1 | Address Byte  | 1   | 1   | 0   | 0   | 0   | MA1 | MA0 | R/W = 0 | ACK               |

| 2 | Divider Byte① | 0   | N14 | N13 | N12 | N11 | N10 | N9  | N8      | ACK               |

| 3 | Divider Byte② | N7  | N6  | N5  | N4  | N3  | N2  | N1  | N0      | ACK(L)            |

| 4 | Control Byte  | 1   | СР  | T2  | T1  | T0  | RSa | RSb | OS      | ACK <sup>()</sup> |

| 5 | Band SW Byte  | ×   | ×   | ×   | ×   | B4  | В3  | B2  | B1      | ACK(L)            |

x : DON'T Care

ACK: Acknowledged

① : Latch and transfer timing

#### b) READ MODE

|   |   | ВҮТЕ         | MSB |    |   |   |   |     |     | LSB     |     |

|---|---|--------------|-----|----|---|---|---|-----|-----|---------|-----|

| ſ | 1 | Address Byte | 1   | 1  | 0 | 0 | 0 | MA1 | MA0 | R/W = 1 | ACK |

| ſ | 2 | Status Byte  | POR | FL | 1 | 1 | 1 | A2  | A1  | A0      |     |

ACK : Acknowledged

#### **DATA SPECIFICATIONS**

• MA1, MA0 : Programmable hardware address bits

| ADDRESS PIN APPLIED VOLTAGE                 | MA1 | MA0 |

|---------------------------------------------|-----|-----|

| 0~0.1 V <sub>CC</sub> 1                     | 0   | 0   |

| 0.4 V <sub>CC</sub> 1~0.6 V <sub>CC</sub> 1 | 1   | 0   |

| 0~V <sub>CC</sub> 1                         | 0   | 1   |

| 0.9 V <sub>CC</sub> 1~V <sub>CC</sub> 1     | 1   | 1   |

• CP : Charge-pump output current setting

#### • T2, T1, T0 : Test mode setting

| CHARACTERISTIC             | T2 | T1 | ТО | NOTE                                                                            |

|----------------------------|----|----|----|---------------------------------------------------------------------------------|

| Normal operation           | 0  | 0  | 1  | _                                                                               |

| Reference signal output    | 1  | 0  | 0  | Reference signal output: B4, Counter output: B2                                 |

| 1/2 counter divider output | 1  | 0  | 1  | Reference signal output: B4, 1/2 counter output: B2                             |

| Phase comparator test      | 0  | 0  | 0  | Comparative signal input : SDA Reference signal input : SCL (check output : NF) |

X : Don't care

(Note) When testing the counter divider output, programmable counter data input is necessary.

#### • RSa, RSb: X'tal reference frequency divider ratio select bits

| RSa | RSb | DIVIDER RATIO | STEP FREQUENCY |  |  |

|-----|-----|---------------|----------------|--|--|

| 1   | 1   | 1 / 64        | 62.5 k         |  |  |

| 0   | 1   | 1 / 128       | 31.25 k        |  |  |

| Х   | 0   | 1 / 80        | 50.0 k         |  |  |

X : Don't care

• OS : Tuning amplifier control setting

**■ 0 ■ : Tuning amp ON (Normal operation)**

[1]: Tuning amp OFF (Tr. Output is Low Level)

• POR : Power-on reset flag

0 : Normal operation1 : Reset operation

• FL : Lock detect flag

[0]: Unlocked

[1]: Locked

#### • A2, A1, A0 : 5-level A/D converter status.

| ADC PIN APPLIED VOLTAGE                       | A2 | A1 | A0 |

|-----------------------------------------------|----|----|----|

| 0.60 V <sub>CC</sub> 1~V <sub>CC</sub> 1      | 1  | 0  | 0  |

| 0.45 V <sub>CC</sub> 1~0.60 V <sub>CC</sub> 1 | 0  | 1  | 1  |

| 0.30 V <sub>CC</sub> 1~0.45 V <sub>CC</sub> 1 | 0  | 1  | 0  |

| 0.15 V <sub>CC</sub> 1~0.30 V <sub>CC</sub> 1 | 0  | 0  | 1  |

| 0~0.15 V <sub>CC</sub> 1                      | 0  | 0  | 0  |

(\*) Accuracy is  $\pm 0.03 \times V_{CC}1$

• X : DON'T Care

#### I<sup>2</sup>C BUS CONTROL SUMMARY

The bus control format of TD7624AFN conforms to the Philips I<sup>2</sup>C bus control format.

# Data transmission format S Slave address 0 A Data A Data A P 7-bit MSB 8-bit MSB 8-bit

S : Start condition P : Stop condition

A: Acknowledge

#### (1) Start/Stop condition

#### (2) Bit transfer

#### (3) Acknowledge

#### (4) Slave address

| A <sub>6</sub> | A <sub>5</sub> | Α4 | Α3 | A <sub>2</sub> | Α1 | A <sub>0</sub> | R/W |

|----------------|----------------|----|----|----------------|----|----------------|-----|

| 1              | 1              | 0  | 0  | 0              | *  | *              | 0   |

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Tights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

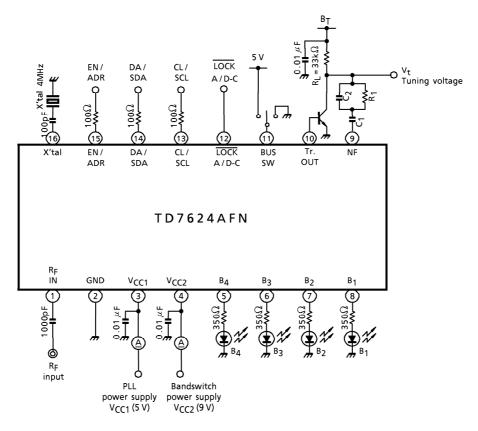

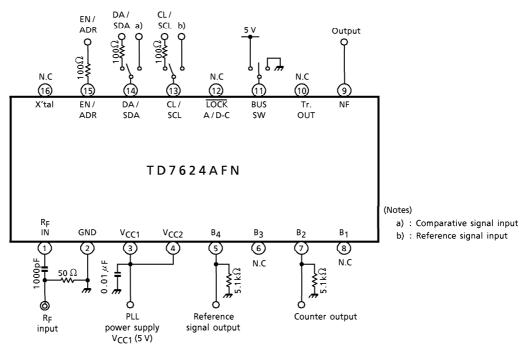

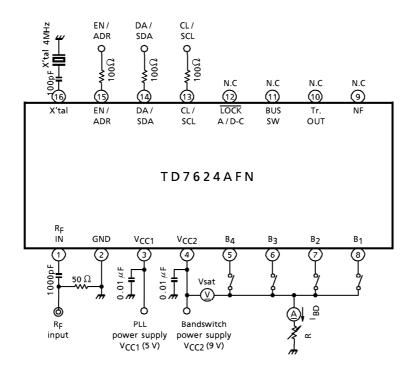

**TEST CIRCUIT 1** Evaluation circuit board

TEST CIRCUIT 2 Input sensitivity test circuit

Test mode circuit

TEST CIRCUIT 3

Bandswitch drive test circuit

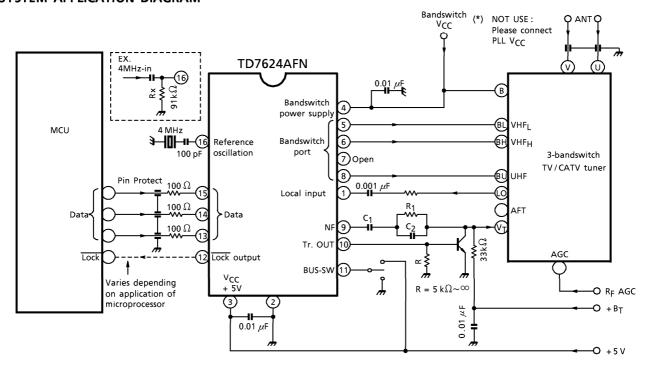

#### SYSTEM APPLICATION DIAGRAM

**TOSHIBA**

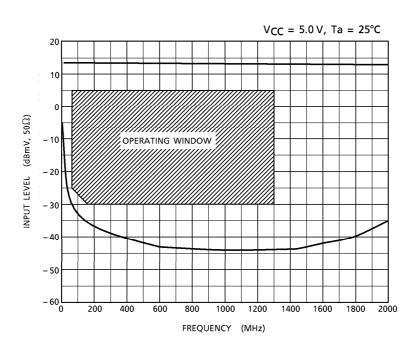

#### TYPICAL INPUT SENSITIVITY CURVE

#### FILTER COMPONENT EXPRESSION

C1 =  $[Kv * Icomp / (2\pi)] / (\omega n^2 * N)$

R1 =  $[2 * \varepsilon]/(\omega n * C1)$

C2 =  $1/(2\pi * fc * R1)$

with:

Kv = Oscillator control sensitivity (radian/Second/Volts)

lcomp = Charge-pump current (A)

$\omega n$  = Natural radian frequency (radian/Second)

N = Total counter ratio

$\varepsilon$  = Dumping-factor (generaly : dumping-factor is about 0.5~1.0)

fc = filter cut-off frequency with combination resistor R1.

(generally: fc is about fr (reference frequency)/20)

##

Weight: 0.07 g (Typ.)

1999-05-17 20/20