# TIR2000 Data Manual

High-Speed Serial Infrared Controller With 64-Byte FIFO

> SLLS248A June 1998

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

# **Contents**

| 1-11-21-31-42-12-12-82-92-11                         |

|------------------------------------------------------|

| 2–1 2–2 2–5 2–8 2–9                                  |

| 2–13<br>2–17                                         |

|                                                      |

| 4-1<br>4-1<br>4-1<br>4-2<br>4-4<br>4-5<br>4-6<br>4-6 |

|                                                      |

|    |       | 4.9.2 Low-Power Mode                                                   | . 4–7 |

|----|-------|------------------------------------------------------------------------|-------|

|    |       | Configuration Control Register (CCR) – (write only)                    |       |

|    | 4.11  | Bank 0 Registers                                                       | . 4–7 |

|    |       | 4.11.1 Transmit Frame-Length Register Low (TXFLL) – (write only)       |       |

|    |       | 4.11.2 Transmit Frame-Length Register High (TXFLH) – (write only)      |       |

|    |       | 4.11.3 Received Frame-Length Register Low(RXFLL) – (write only)        |       |

|    |       | 4.11.4 Received Frame-Length Register High (RXFLH) – (write only)      |       |

|    |       | 4.11.5 Preamble Length Register (PLR) – (write only)                   |       |

|    |       | 4.11.6 Auxiliary Control Register (ACREG) – (read and write only)      |       |

|    |       | 4.11.7 Status FIFO Line Status Register (SFLSR) – (read only)          |       |

|    |       | 4.11.8 Status FIFO Register Low (SFREGL) – (read only)                 | 4–10  |

|    |       | 4.11.9 Status FIFO Register High (SFREGH) – (read only)                |       |

|    | 4.12  | Bank 1 Registers                                                       | 4–10  |

|    |       | 4.12.1 TV Configuration Register (TVCFG)                               |       |

|    |       | 4.12.2 TV Demodulation Configuration Register (TVDMCFG)                |       |

|    |       | 4.12.3 TV Modulation Configuration Register (TVMDCFG)                  |       |

|    | 4.13  | Bank 2 Registers                                                       |       |

|    |       | 4.13.1 Prescaler Register (PRESC)                                      |       |

|    |       | 4.13.2 Interrupt Configuration Register (ICR) – (write only)           |       |

|    |       | 4.13.3 DMA Channel Select Register (DCSR) – (write only)               |       |

|    | 4.14  | Bank 3 Registers                                                       |       |

|    |       | 4.14.1 General Purpose I/O Direction Register (GPIODIR) – (write only) |       |

|    |       | 4.14.2 General Purpose I/O Data Register (GPIODAT) – (read and write)  |       |

|    |       | 4.14.3 General Purpose Function Select Register (GPFSR) – (write only) |       |

|    |       | 4.14.4 Ir Mode Configuration Register 1 (IRCFG) – (read and write)     | 4–15  |

| 5. | Elec  | trical Characteristics                                                 | . 5–1 |

|    | 5.1   | Absolute Maximum Ratings                                               | . 5–1 |

|    | 5.2   | Recommended Operating Conditions                                       |       |

|    |       | Low voltage (3.3 V nominal)                                            |       |

|    |       | Standard voltage (5 V nominal)                                         |       |

|    | 5.3   | Timing Requirements                                                    |       |

|    | 5.4   | Operating Characteristics                                              |       |

|    | 5.5   | Switching Characteristics                                              | . 5–2 |

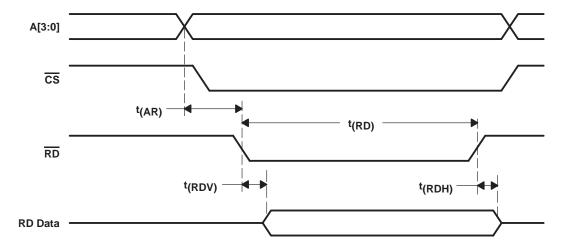

|    | 5.6   | Timing Diagrams                                                        |       |

| 6. | Δnn   | lication Information                                                   | 6_1   |

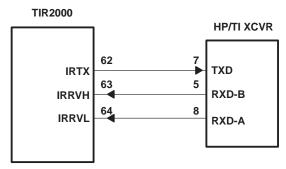

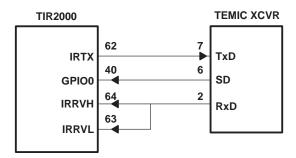

| ٥. |       | Transceiver Connections                                                |       |

|    |       | Operating Modes                                                        |       |

|    | 0.2   | operating modes                                                        | . 0–3 |

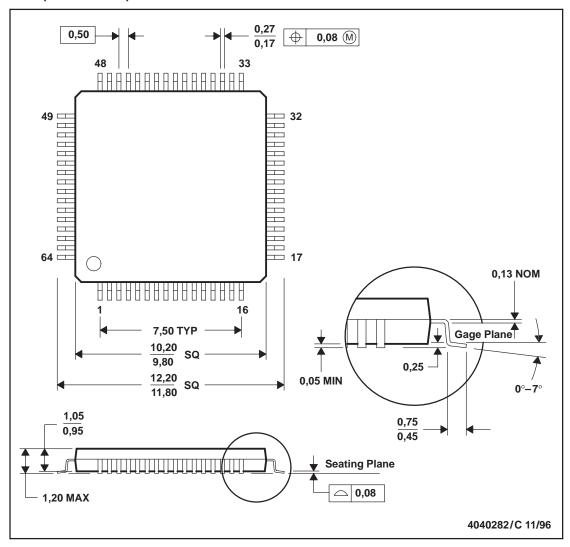

| Αp | pendi | ix A Mechanical Data                                                   | A-1   |

# **List of Illustrations**

| Figu | ure Title                                           | Page       |

|------|-----------------------------------------------------|------------|

| 1–1  | Functional Block Diagram                            | <br>1–2    |

| 1–2  | Terminal Assignments                                | <br>1–3    |

| 2–1  | Basic Configuration for Ir Communication            | <br>2-1    |

|      | SIR Encoding                                        |            |

| 2–3  | SHARP Ir Encoding                                   | <br>2–9    |

| 2–4  | Example of Auto-flow Contol (Auto-RTS and Auto-CTS) | <br>. 2-14 |

| 2–5  | CTS Functional Timing Diagram                       | <br>. 2-15 |

| 2–6  | RTS Functional Timing, RCV-FIFO Trigger             | <br>. 2-15 |

| 5–1  | Standard ISA Write-Cycle Timing Diagram             | <br>5–3    |

| 5–2  | Standard ISA Read-Cycle Timing Diagram              | <br>5–3    |

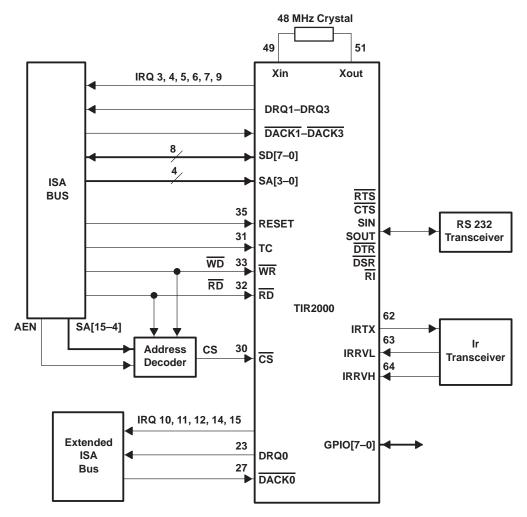

|      | Typical TIR2000 Configuration                       |            |

| 6–2  | HP/TI Transceiver Connection                        | <br>6–2    |

| 6–3  | Temic Transceivers                                  | <br>6-2    |

# **List of Tables**

| Table                                     | Title                      | Page |

|-------------------------------------------|----------------------------|------|

| 4-1 RX Demodulation Carrier Frequency (lo | w range TVCFG[4] bit = 0)  | 4-11 |

| 4-2 RX Demodulation Carrier Frequency (hi | gh range TVCFG[4] bit = 1) | 4-12 |

| 4–3 TX Modulation Carrier Frequency       |                            | 4-12 |

| 4–4 TX Modulation Carrier Pulse Duration  |                            | 4-12 |

### 1 Introduction

The TIR2000 is a serial communication controller with full infrared support which is also compatible to the TL16C550C and the TL16C750 UART devices. This device also supports the Sharp-IR, HPSIR, MIR, FIR and TV modes. The controller has a 64-byte FIFO which reduces the CPU of excessive software overhead. Also a 64-byte FIFO meets the minimum frame size requirements simplifying the software driver design. DMA and interrupt support for all operations have been included in this architecture. The TIR2000 offers programmable registers for routing interrupt DMA handshake signals. While in UART mode, the 64-byte FIFO and selectable auto-flow control for RTS and CTS increases system efficiency and baud rate.

- IrDA 1.0 mode with a data rate up to 115.2 Kbps

- IrDA 1.1 mode with a data rate up to 1.15 Mbps

- IrDA 1.1 mode with a data rate up to 4 Mbps

- Sharp ASK infrared mode

- Consumer television remote control mode (RC5, RC5 extended, NEC, RC6, and RECS80)

#### 1.1 Features

- Full infrared support

- Infrared Data Association (IrDA™) 1.0 supports up to 115.2 kbps

- IrDA 1.1 supports 1.15 Mbps and 4 Mbps

- Sharp Amplitude Shift Keying (ASK)

- TV remote control mode

- Industry Standard Architecture (ISA) compatible bus interface

- Selectable 16- or 64-byte FIFO

- Full duplex infrared transmission and reception

- Controlled transmit start

- Supports back-to-back transactions

- Supports multiple optical transceivers

- Controlled Serial Interaction Pulse (SIP) generation

- Supports 11 IRQ options and 3 DMA configurations

- Power management support

- 8 general purpose I/O terminals

- Fully compatible with TL16C450, TL16C550C, TL16C750 UARTs

- Automatic fallback to TL16C550C mode

- UART baud rate up to 1 Mbps

- Auto-flow control in UART mode

- 3.3-V or 5-V operation

- Available in 64-pin TQFP package

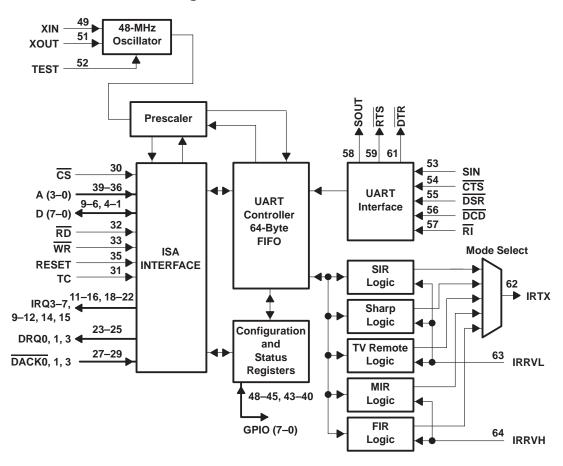

# 1.2 Functional Block Diagram

Figure 1–1. Functional Block Diagram

# 1.3 Terminal Assignments

# PAG PACKAGE (TOP VIEW)

Figure 1–2. Terminal Assignments

# 1.4 Ordering Information

|             | PACKAGE                 |

|-------------|-------------------------|

| TA          | QUAD FLAT PACK<br>(PAG) |

| 0°C to 70°C | TIR2000PAG              |

## 1.5 Terminal Functions

| 1.5 Terminal Functions                    |                         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------------------------------------|-------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TERMINALS                                 |                         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NAME                                      | NO.                     |     | DEGGINIF HON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

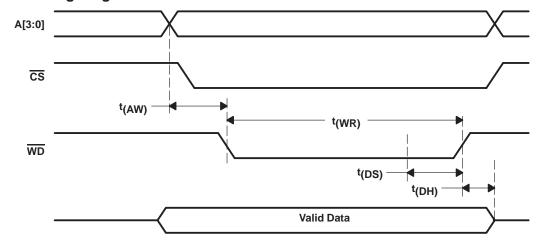

| A0 – A3                                   | 36–39                   | I   | Address bus. The CPU uses A0 -A3 and the CS signal to select the internal register of the TIR2000. A0 -A3 are decoded to select a particular register.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CS                                        | 30                      | ı   | Chip select. The CPU uses CS to select the TIR2000 for read/write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| стѕ                                       | 54                      | I   | Clear to send. $\overline{\text{CTS}}$ is a modem-status signal. Its condition can be checked by reading bit 4 $\underline{\text{(CTS)}}$ of the modem-status register (MSR). Bit 0 ( $\underline{\Delta}\text{CTS}$ ) of the MSR indicates that $\overline{\text{CTS}}$ has changed states since the last read from the MSR. When modem-status interrupt is enabled, $\overline{\text{CTS}}$ changes states, and the auto- $\overline{\text{CTS}}$ mode is not enabled, an interrupt is generated. $\overline{\text{CTS}}$ is also used in the auto- $\overline{\text{CTS}}$ mode to control the transmitter. |  |  |

| D0-D7                                     | 1–4,<br>6–9             | I/O | Data bus. These bidirectional data lines are connected to the CPU for data transfer between the TIR2000 and the CPU. D0 is the LSB and D7 is the MSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| DACKO,<br>DACK1,<br>DACK3                 | 27–29                   | I   | DMA acknowledge. DACK0, DACK1, and DACK3 are DMA active low signals that are the corresponding acknowledge signals, for the DMA request signals which are DRQ0, DRQ1 and DRQ3.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DCD                                       | 56                      | I   | Data carrier detect. $\overline{DCD}$ is a modem-status signal. Its condition can be checked by reading bit 7 (DCD) of the MSR. Bit 3 ( $\Delta DCD$ ) of the MSR indicates that $\overline{DCD}$ has changed states since the last read from the MSR. When the modem-status interrupt is enabled and $\overline{DCD}$ changes state, an interrupt is generated.                                                                                                                                                                                                                                               |  |  |

| DRQ0, DRQ1,<br>DRQ3                       | 23–25                   | 0   | DMA requests. DRQ0, DRQ1 and DRQ3 are used for DMA requests that are active high and are used to signal the DMA controller that data transfer between the TIR2000 and memory is required. When the DMA is enabled, one of the three channels configurable through the DMA channel select register (DCSR) can be selected.                                                                                                                                                                                                                                                                                      |  |  |

| DSR                                       | 55                      | I   | Data set ready. $\overline{\text{DSR}}$ is a modem-status signal. Its condition can be checked by reading bit 5 (DSR) of the MSR. Bit 1 ( $\Delta$ DSR) of the MSR indicates the $\overline{\text{DSR}}$ has changed states since the last read from the MSR. When the modem-status interrupt is enabled and the $\overline{\text{DSR}}$ changes states, an interrupt is generated.                                                                                                                                                                                                                            |  |  |

| DTR                                       | 61                      | 0   | Data terminal ready. When low, $\overline{\text{DTR}}$ informs a modem or data set that the UART is ready to establish communication. $\overline{\text{DTR}}$ is placed in the active state by setting the DTR bit of the modem-control register to one. $\overline{\text{DTR}}$ is placed in the inactive condition as a result of a master reset, during loop mode operation, or clearing of the DTR bit.                                                                                                                                                                                                    |  |  |

| GND                                       | 5, 10,<br>26, 34,<br>50 |     | Ground (0 V). GND terminals must be tied to ground for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| GPIO0-GPIO3,<br>GPIO4-GPIO7               | 40–43,<br>45–48         | I/O | General purpose I/O terminals. GPIO0–GPIO7 terminals are programmable general-purpose input/output terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| IRQ3–IRQ7,<br>IRQ9–IRQ12,<br>IRQ14, IRQ15 | 11–16,<br>18–22         | 0   | Interrupt signals. These active-high interrupts are activated based on the IRQ configuration register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| IRRVH                                     | 64                      | I   | Infrared receive. IRRVH is an input connected to the IR transceiver module that receives data in the high-speed modes (1.15 Mbps and 4 Mbps mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

# 1.5 Terminal Functions (Continued)

| IRRVL     | 63            | I   | Infrared receive. IRRVL is connected to the IR transceiver module and receives data in the slow-speed mode such as the SIR, Sharp Ir, and TV remote-control modes.                                                                                                                                                                                                            |  |  |

|-----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IRTX      | 62            | 0   | nfrared transmit. IRTX is an output terminal connected to the IR transceiver mode and transmits data out from the TIR2000.                                                                                                                                                                                                                                                    |  |  |

| RD        | 32            | I   | Read. RD is an active-low signal that indicates when the CPU reads data from the TIR2000.                                                                                                                                                                                                                                                                                     |  |  |

| RESET     | 35            | Ι   | Reset. When active (high), RESET is used for system reset operation.                                                                                                                                                                                                                                                                                                          |  |  |

| RI        | 57            | I   | Ring indicator. $\overline{RI}$ is a modem-status signal. Its condition can be checked by reading bit 6 (RI) of the MSR. Bit 2 (TERI) of the MSR indicates that $\overline{RI}$ has transitioned from a low to a high level since the last read from the MSR. If the modem-status interrupt is enabled when this transition occurs, an interrupt is generated.                |  |  |

| RTS       | 59            | 0   | Request to send. When low, RTS informs the modem or data set that the ACE is ready to receive data. RTS is set low by setting the RTS MCR bit and is set to its inactive (high) level either as a result of a master reset, during loop mode operations, or by clearing bit 1 (RTS) of the MCR. In the auto-RTS mode, RTS is set low by the receiver threshold control logic. |  |  |

| SIN       | 53            | Ι   | Serial data. SIN is the input from a connected communications device.                                                                                                                                                                                                                                                                                                         |  |  |

| SOUT      | 58            | 0   | Composite serial data output. SOUT is connected to a communication device. SOUT is set to the marking (high) level as a result of master reset.                                                                                                                                                                                                                               |  |  |

| TC        | 31            | I   | Terminal count. TC comes from the DMA controller and indicates the end of the block transfer.                                                                                                                                                                                                                                                                                 |  |  |

| TEST      | 52            | I   | Test terminal. TEST is used for test purposes only and should be tied low in normal operation.                                                                                                                                                                                                                                                                                |  |  |

| VCC       | 17, 44,<br>60 |     | 5-V or 3-V supply voltage.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| WR        | 33            | I   | Write. WR is an active low signal that indicates that the CPU is writing data to the TIR2000.                                                                                                                                                                                                                                                                                 |  |  |

| Xin, Xout | 49, 51        | I/O | Crystal connectors. A 48-MHz crystal should be connected across these terminals.                                                                                                                                                                                                                                                                                              |  |  |

(This page has been left blank intentionally.)

# 2 Functional Description

## 2.1 Modes of Operation

The TIR2000 operates in six different modes. For proper operation, the device must be programmed correctly for each mode. The various modes of operation include:

- Fast-speed infrared (IrDA FIR) mode

- Medium-speed infrared (IrDA MIR) mode

- Slow-speed infrared (IrDA SIR) mode

- SHARP Infrared (IR) mode

- TV mode

- Universal asynchronous receiver transmitter (UART) mode

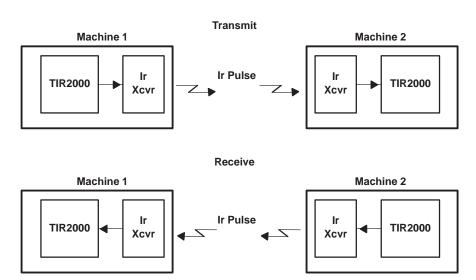

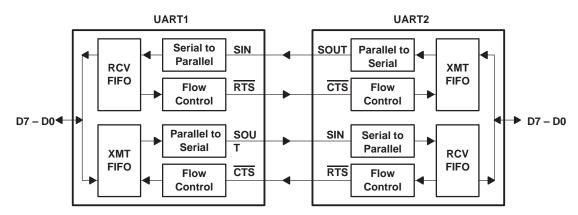

Basic data communication involves at least two devices. During the data transmit mode, the first device transmits data and the second device receives the transmitted data. During the receive mode, the second device transmits the data and the first device receives the data. When the device is configured for the UART mode, both data transmission and data receive can occur simultaneously, but during the infrared (IR) modes either the data transmit or data receive is possible at any time but not simultaneously. A basic configuration for two communicating devices in the infrared mode is shown in Figure 2–1.

Figure 2-1. Basic Configuration for Ir Communication

The TIR2000 has internal programmable registers. Some of the registers are common to all modes of operation and some are specific to a particular mode of operation. The device is accessed with the industry standard architecture (ISA) address bus SA[15–0]. An outside address decoder uses ISA signals (SA[15–4], AEN) and generates the chip select (CS) signal for the TIR2000 device. The lower address bits SA[3–0] are directly connected to the device. The internal address decoder decodes SA[3–0] lower address bits to access the different registers.

## 2.1.1 Fast-Speed Infrared (FIR) mode (IrDA 1.1)

During the FIR mode, data transfer takes place between the CPU and peripheral devices at the baud-rate speed of 4 Mbps. An FIR transmit frame starts with the Preamble, followed by a Start Flag, Frame Data, CRC-32, and Stop Flag. The details of the frame format can be found in the Infrared Data Association (IrDA) document physical layer link specification

| Preamble | Start Flag | Frame Data | CRC-32 | Stop Flag |

|----------|------------|------------|--------|-----------|

|----------|------------|------------|--------|-----------|

The peripheral device that is in the data-transmission mode attaches the Preamble, Start Flag, CRC-32, and the Stop Flag. It also encodes the transmit data into the 4PPM format. During data receive, the peripheral device in the data-receive mode recovers the data-receive clock, removes the Start Flag, decodes the 4PPM incoming data and determines the frame boundary with the reception of a Stop Flag. It also checks for errors such as illegal pulse-position-modulation (4PPM) symbols, cyclic reduncy check (CRC) errors and frame-length errors. At the end of a frame reception, the CPU reads the LSR-status register to find the errors, if any, of the received frame.

Data cannot be transmitted and received by the same device at the same time. When the CPU wants to send data, the peripheral device needs to be programmed for data transmission. When the CPU receives data from the peripheral device, the peripheral device needs to be programmed for data receive. Some registers are common to both data transmit and data receive and need to be programmed only once. Use the following programming sequence for these registers:

- 1. Program the interrupt configuration register (ICR) in order to:

- Select the IRQ channel

- Select either totem-pole or open-drain output

- Select an active high or an active low for an interrupt when the totem-pole configuration is selected.

- 2. Write a 6 to the PRESC register. This divides a 48-MHz input clock by 6 and generates a 8-MHz internal clock for the FIR mode of operation.

## 2.1.1.1 FIR Data-Transmission Mode

The following register programming steps should be performed for transmission in the FIR mode:

- 1. Program the mode definition register (MDR) in order to :

- · Select the FIR mode

- Enable/disable the low-power mode. For normal operation, enable the low-power mode.

- Enable/disable the sleep mode. For normal operation, disable the sleep mode.

- Enable/disable the store-and-controlled transmission (SCT). For normal operation, disable the SCT.

- Enable/disable the software control on a 2-μs infrared pulse. For normal operation, disable the software control.

- Select the frame closing method (frame-length method or set-EOT bit method).

- 2. Program the preamble length register (PLR) in order to:

- Select the number of preambles. The default value is 16.

- Select the TX FIFO trigger level

- When the frame-length method is selected for frame termination, program the TXFLL and the TXFLH registers for the frame length value.

- 4. Reset the TX FIFO. This includes:

- Write to the LCR register so that the LCR[7] bit is a 1. The LCR[7] bit must be a 1 to be able to

write to the FCR[5] bit.

- Program the FCR register to select 64-/16-bytes of the TX FIFO, the non-DMA/DMA mode of operation, select the TX FIFO trigger level and to clear the TX FIFO.

- Write the LCR register to set the LCR[7] bit to a 0 for normal operation.

- 5. Program the IER register to enable only the transmitter related interrupts and disable the remaining interrupts. Enable the following:

For programmed I/O mode

- Transmitter FIFO below threshold level interrupt enable (IER[1])

- Transmitter underrun interrupt enable (IER[7])

For DMA mode

- Status FIFO time-out interrupt enable (IER[2])

- Status FIFO threshold interrupt enable (IER[4])

- Transmitter underrun interrupt enable (IER[6])

- 6. Write a 1 to the ACREG[7] bit to enable data transmission

- 7. Write a 1 to the MCR[3] bit. This enables the selected IRQ channel.

#### 2.1.1.1.1 Frame-Closing Methods

There are two ways a transmission frame can be properly terminated: frame-length method and set-EOT bit method. The two methods are described as follows:

- Frame-Length method: This method is selected when the MDR[7] bit equals 0. The CPU writes

the frame-length value to the TXFLH and TXFLL registers. The device automatically attaches an

end flag to the frame when the number of bytes transmitted becomes equal to the TXFLH and

TXFLL value.

- Set-EOT bit method: This method is selected when the MDR[7] bit equals 1. The CPU writes a

1 to the EOT bit of the ACREG[0] register just before it writes the last byte to the TX FIFO. When

the CPU writes the last byte to the TX FIFO, the device internally sets the tag bit for that particular

byte in the TX FIFO. As the peripheral device in the transmit mode reads bytes from the TX FIFO,

the flag-bit information is used to attach an end flag and properly terminate the frame.

### 2.1.1.1.2 Store and Controlled Data Transmission

In the store and controlled transmission (SCT), the CPU initially writes (stores) the data in the TX FIFO. After the CPU writes a part of the frame (for a bigger frame) or the whole frame (a small frame such as a supervisory frame), it enables another bit (ACREG[2] in this case) to start transmission. The SCT is effective when the CPU writes a 1 to the MDR[5] bit. This method of transmission is different from the normal mode of transmission (MDR[5] = 0) where transmission of data starts right after the CPU writes the first byte to the TX FIFO. The SCT sends short frames without a TX underrun.

## 2.1.1.1.3 1.6-μs Infrared (IR)-Pulse Select Method

During the MIR and FIR mode of operation, the transmitter sends a 1.6- $\mu$ s pulse at least once every 500 ms. The purpose of this special pulse is to inform the slow device (in SIR mode) that the high-speed device involved in data transaction is currently occupied. When the MDR[6] bit is a 0 (the default value), the peripheral device in the transmit mode always sends a 1.6- $\mu$ s pulse at the end of a transmission frame. However, when bit MDR[6] is a 1, the transmission of a 1.6- $\mu$ s pulse depends on the ACREG[3] bit value. The CPU keeps a timer and sets the ACREG[3] bit at least once in every 500 ms. When the MDR[6] bit is a 1, the peripheral device in the transmit mode sends a 1.6- $\mu$ s pulse only if the ACREG[3] bit is a 1. The advantage to this approach over the default value sent-always-1.6- $\mu$ s pulse-at-the-end approach is that the peripheral device in the transmit mode need not send the special 1.6- $\mu$ s pulse at the end of every frame. Sending a 1.6- $\mu$ s pulse at the end of every frame may increase overhead, mainly in the MIR mode.

#### 2.1.1.1.4 Data-Transmission Underrun

An underrun during data transmission occurs when the CPU fails to supply the data to the TX FIFO and the TX FIFO becomes empty before the end of the frame is transmitted. When an underrun occurs, the device closes the frame with an end-flag but attaches an incorrect CRC value. The receiving device detects the CRC error and discards the frame. The device sets an internal flag and further transmission of data is disabled. The CPU must reset the TX FIFO and read the RESUME register. This read operation clears the internal flag.

#### 2.1.1.2 FIR Data-Receive Mode

The following register programming steps are required to receive data in FIR mode:

- 1. Program the mode definition register (MDR) to:

- Select the FIR mode

- Enable the low-power mode

- Disable the sleep mode

- Program the RXFLL and RXFLH registers for the receive-frame length value. The maximum length of a frame is 2048 bytes. The RXFLL register stores the lower eight bits and the RXFLH register stores the remaining bits. When the intended maximum receive-frame length is n, program the RXFLH and RXFLL registers to be n + 5.

- 3. Reset the RX FIFO. This includes:

- Write to the LCR register that the LCR[7] bit is a 1. The LCR[7] bit must be a 1 to be able to write to the FCR[5] bit.

- Program the FCR register to select 64-/16-bytes of the RX FIFO, the non-DMA/DMA mode of operation, select the RX FIFO trigger level and to clear the RX FIFO.

- Write the LCR register to set the LCR[7] bit to a 0 for normal operation.

- 4. Program the IER register to enable only the receive related interrupts and disable the remaining interrupts. Enable the following:

- RX threshold interrupt (IER[0] bit)

- The last byte from the RX FIFO interrupt (IER[2] bit)

- The RX FIFO overrun interrupt (IER[3] bit)

- The received end of the frame interrupt (IER[7] bit)

- 5. Write a 1 to the ACREG[6] to enable data receive.

- 6. Write a 1 to the MCR[3] bit. This enables the selected IRQ channel.

This completes the programming of the registers for data receive and now the device is ready to receive data. The device decodes the serial data, converts it from serial data to parallel data and stores the data bytes in the RX FIFO. When the stored data in the RX FIFO reaches the set threshold level, the device interrupts the CPU. When the CPU is interrupted, it reads the IIR to identify the source of the interrupt. When the source of the interrupt is the IIR[0] bit and not the IIR[7] bit, the CPU goes to the threshold mode.

#### 2.1.1.2.1 Threshold Mode

During threshold mode, the CPU reads a number of bytes (determined by the RX FIFO threshold level) from the RX FIFO. An example: When the RX threshold value is set to be 16, the CPU can perform 16 consecutive read operations from the RX FIFO. When the source of interrupts is the IIR[7] bit, the CPU goes to the byte mode.

## 2.1.1.2.2 Byte Mode

The CPU will read the majority of the frame in the threshold mode. However, the last bits of data may not fall on the exact threshold boundary and will not be able to interrupt the CPU with the IIR[0] bit. The device interrupts the CPU with the IIR[7] bit when the machine in the data-receive mode detects the end of a frame. The CPU disables the IER[0] bit and reads one byte from the RX FIFO each time and checks for the interrupt (IIR[2]) bit. When the CPU reads the last byte of a frame from the RX FIFO, the device interrupts the CPU with the IIR[2] bit. Once the CPU receives the IIR[2] bit, it should not read further from the RX FIFO and that is the end of the frame. The last four bytes that the CPU read from the RX FIFO are the CRC value and not the actual data. The CPU enables the IER[0] bit. After the CPU reads the last byte of a frame from the RX FIFO, it reads the LSR register to determine the sources or errors, if any, for that frame. When the source of the interrupt is the IIR[3] bit, there has been an overrun while receiving data and the CPU will service the overrun.

#### 2.1.1.2.3 Data-Receive Overrun

An overrun occurs during data receive if the CPU cannot timely read out data from the RX FIFO and the RX FIFO is overwritten. When an overrun occurs, the device interrupts the CPU with the IIR[3] bit and discards the remaining portion of the frame. When an overrun occurs, the device sets an internal flag and the receive operation of the next frame is disabled. Before the next frame can be received, the CPU must reset the RX FIFO and read the RESUME register. This read operation clears the internal flag.

#### 2.1.2 Medium-Speed Infrared (MIR) mode (IrDA 1.1)

During the medium speed infrared (MIR) mode, data transfer takes place between the CPU and peripheral devices at a speed of 1.15 Mbs. A MIR transmit frame starts with a minimum of two Start Flags followed by the Frame Data, CRC–16 and ends with a Stop Flag.

| Start Flag | Frame Data | CRC-16 | Stop Flag |

|------------|------------|--------|-----------|

|------------|------------|--------|-----------|

The peripheral device in the data transmission mode of operation attaches the Start Flags, CRC-16, and a Stop Flag. It also looks for five consecutive ones in the frame data and automatically inserts a zero after five consecutive ones. This operation is known as bit stuffing. On a receive operation, the machine in the data receive mode recovers the receive clock, removes the Start Flag, de-stuffs the incoming data and determines frame boundary with the reception of the Stop Flag. It also checks for errors such as frame abort, CRC error and frame-length error. At the end of a frame reception, the CPU reads the LSR status register to find out if any errors occurred with the received frame.

The device can both transmit and receive data, but cannot do both at the same time. When the CPU wants to send data, the perpheral device must be programmed for data transmission. When the CPU receives data from the peripheral device, the perpheral device must be programmed for data receive. Some registers are common to both data transmit and data receive and are programmed only once. Use the following programming sequence for these registers:

- 1. Program the interrupt configuration register (ICR) in order to:

- Select the IRQ channel

- Select either totem-pole or open-drain output

- Select an active high or an active low for an interrupt when the totem-pole configuration is selected.

- In the MIR mode, the 48-MHz input clock is automatically divided by 1.5 to generate the 28x MIR clock. However, a 6 should be written to the PRES register which is used as the base clock for the status FIFO timeout interrupt.

#### 2.1.2.1 MIR-Data Transmission Mode

The following register programming steps are performed for transmission in the MIR mode:

- 1. Program the mode-definition register (MDR) to:

- Select the MIR mode

- Enable/disable the low-power mode. The low-power mode is enabled for normal operation.

- Enable/disable the sleep mode. The sleep mode is disabled for normal operation.

- Enable/disable the store and controlled transmission. The SCT is disabled for normal operation.

- Enable/disable the software control on the 1.6-μs infrared pulse. The software control is disabled during normal operation.

- Select the frame closing method (frame-length method or set–EOT bit method)

- 2. Program the PLR to:

- Select the number of Start Flags. The default value is two.

- Select the TX FIFO trigger level.

- When the frame-length method is selected for frame closing, program the TXFLL and the TXFLH registers for the frame length.

- 4. Reset the TX FIFO:

- Write the LCR register so that the LCR[7] bit is a 1. The LCR[7] bit must be a 1 in order to write to the FCR[5] bit.

- Program the FCR to select 64-/16-bytes of TX FIFO, non-DMA/DMA mode of operation, and to clear the TX FIFO.

- Write the LCR register so that the LCR[7] bit is a 0 for normal operation.

- Program the IER register to enable only the transmission related interrupts and disable the remaining interrupts. The TX threshold interrupt and the TX underrun interrupt are enabled.

- 6. Write a 1 to the ACREG[7] bit to enable data transmission.

- 7. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

When the CPU receives an interrupt, it reads the IIR to identify the source of the interrupt. When the source of the interrupt is an IIR[1] bit, the CPU requires the following:

- Disable the IER[1] bit.

- Write data bytes (maximum number limited to the number selected by the TX FIFO trigger level) to the TX FIFO.

- Enable the IER[1] bit.

When the source of the interrupt is the IIR[5] bit, there has been an underrun while transmitting data and the CPU needs to service the underrun. See paragraph 2.1.1.1.4.

#### 2.1.2.2 MIR Data Receive Mode

The following register programming steps are required to receive data in MIR mode:

- 1. Program the mode definition register (MDR) in order to:

- Select the MIR mode

- Disable the low power mode

- Disable the sleep mode

- Program the RXFLL and RXFLH registers for maximum receive-frame length value. The

maximum length of a frame is 2048 bytes. The RXFLL register stores the lower eight bits and the

RXFLH register stores the remaining upper bits. When the intended maximum receive-frame

length is n, program the RXFLH and RXFLL registers to be n + 3.

- 3. Reset the RX FIFO. This includes:

- Write to the LCR register so that the LCR[7] bit is a 1. LCR[7] bit must be a 1 to be able to write

to the FCR[5] bit.

- Program the FCR register to select 64-/16- bytes of the RX FIFO, the non-DMA/DMA mode of operation, select the RX FIFO trigger level and to clear the RX FIFO.

- Write the LCR register to set the LCR[7] bit to a 0 for normal operation.

- 4. Program the IER register to enable only the receive related interrupts and disable the remaining interrupts. Enable the following:

- RX threshold interrupt (IER[0] bit)

- The last byte from the RX FIFO interrupt (IER[2] bit)

- The RX FIFO overrun interrupt (IER[3] bit)

- The received end of the frame interrupt (IER[7] bit)

- 5. Write a 1 to the ACREG[6] bit to enable data receive.

- 6. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

This completes the programming of the registers for data receive and now the device is ready to receive data. When the CPU is interrupted, it reads the IIR to identify the source of the interrupt. When the source of the interrupt is the IIR[7] bit, the CPU goes to the byte mode. See paragragh 2.1.1.2.2. The CRC value is the last two bytes instead of the last four bytes as in the FIR data-transmission mode.

When the source of the interrupt is the IIR[0] bit and not the IIR[7] bit, the CPU goes into the threshold mode. See paragraph 2.1.1.2.1. If the source of the interrupt is the IIR[4] bit, there has been an overrun while receiving data and the CPU will need to service the overrun. See paragraph 2.1.1.2.3.

## 2.1.3 Slow-Speed Infrared (SIR) Mode (IrDA 1.0)

The SIR mode of operation is similar to the UART mode except that data communication takes place in a slow-speed half-duplex manner. The method of data transfer is infrared instead of on a wired path. The modem-control register (MCR) and the Modem Status Register (MSR) are not used.

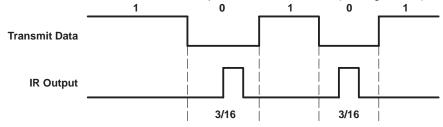

Data transfer occurs with a baud rate of up to 115.2 Kbps. The format of serial data is similar to the UART data format. Each data byte starts with a start bit (0), 1 byte of data, and then ends with at least a stop bit (1). Each serial data bit is encoded before transmission and decoded after being received. A 1 is decoded with no IR pulse and a 0 is decoded by sending 3/16th of one bit time IR pulse. Similarly, the received serial pulse is decoded as a 0 and the absence of an IR pulse is decoded as a 1 (see Figure 2–2).

Figure 2-2. SIR Encoding

The following register programming steps are required to receive or transmit data in SIR mode transmissions:

- 1. Program the ICR register.

- Program the prescaler (PRESC) register to ensure the prescaler output is approximately 1.843 MHz. The default PRESC value is used for an input clock frequency of 48-MHz.

- Program the auxiliary baud-rate divisor lower byte (ABDL) and the auxiliary baud-rate divisor higher byte (ABDH) registers to select the desired communication baud rate for the UART mode. The baud rate is given by:

Baud rate =

$$\frac{X_{IN}}{PRESC \times Divisor \times 16}$$

(1)

- 4. Program the mode definition register (MDR) to:

- Select the SIR mode

- Enable/disable the low-power mode. For normal operation, the low-power mode is enabled.

- Enable/disable the sleep mode.

#### 2.1.3.1 SIR Data Transmission Mode

The following register programming steps are required for data transmission in the SIR mode:

- 1. Program the PLR register to select the TX FIFO trigger level.

- 2. Reset the TX FIFO and program the FCR register.

- Program the IER register to enable only the data transmission interrupts.

- · Enable the TX holding-register-empty interrupt

- Enable the TX underrun interrupt

- Disable the RX FIFO over the threshold interrupt

- Disable the RX FIFO overrun error interrupt

- 4. Program the IRCFG[3] bit to select fixed 1.6 μs or 3/16th pulse width

- 5. Write a 1 to the ACREG[7] bit to enable data transmission.

- 6. Write a 1 to the MCR[3] bit to enable the selected IRQ channel

#### 2.1.3.2 SIR Data Receive Mode

The following register programming steps are required to receive data in SIR mode:

- Reset the RX FIFO. This includes:

- Write the LCR register to set the LCR[7] bit to a 1. The LCR[7] bit must be a 1 in order to be able to write to the FCR(5) bit.

- Program the FCR to select 64-/16-bytes RX FIFO register, non-DMA mode of operation, select the RX FIFO trigger level and to clear the RX FIFO.

- Write the LCR register so that the LCR[7] bit = 0 (for normal operation).

- 2. Program the IER register to enable the receive related interrupts which include:

- RX threshold interrupt (IER[0]) bit

- Modem-Status interrupt enable (IER[3])

- Disable the TX related interrupts (TX FIFO below threshold interrupt and the TX underrun interrupt).

- 3. Write a 1 to the ACREG[6] bit to enable data receive.

## 2.1.4 SHARP Infrared (IR) mode

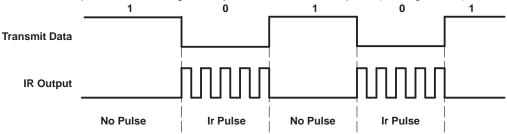

The SHARP IR mode of operation is similar to the SIR mode except the modulation/demodulation of the serial data is different. The SHARP IR mode uses amplitude shift keying (ASK) modulation/demodulation. Data transfer can take place up to a 38.4K baud rate. In the ASK modulation, a 0 is signaled by sending a 500-kHz continuous pulse and a 1 is signaled by the absence of an IR pulse (see Figure 2–3).

Figure 2-3. SHARP Ir Encoding

The following register programming steps are required for encoding in the SHARP Ir mode:

- 1. Program the ICR register

- 2. Program the prescaler (PRESC) register to insure the prescaler output is approximately 1.43 MHz. The default PRESC value is used for an input clock frequency of 48 MHz.

- Program the auxiliary baud rate divisor lower byte (ABDL) and the auxiliary baud rate divisor higher byte (ABDH) registers to select the desired communication baud rate for the UART mode. The baud rate is given by:

Baud rate =

$$\frac{X_{IN}}{PRESC \times Divisor \times 16}$$

(2)

- 4. Program the mode-definition register (MDR) in order to:

- Select the SHARP Ir mode

- Enable/disable the low-power mode. For normal operation, the low-power mode is enabled.

- Enable/disable the sleep mode. For normal operation, the sleep mode is disabled.

- 5. Program the TV configuration (TVCFG) register in order to:

- Enable/disable the receiver internal demodulation.

- Select the transmission carrier-frequency range.

- Select the receiver carrier-frequency range.

#### 2.1.4.1 SHARP IR Data-Transmission Mode

The following register programming steps are required for data transmission in the SHARP IR mode:

- 1. Program the PLR to select the TX FIFO trigger level.

- 2. Reset the TX FIFO. This includes the following:

- Write to the LCR register to set the LCR[7] bit to a 1. The LCR[7] bit must be a 1 to be able to

write to the FCR(5) bit.

- Program the FCR register to select 64-/16-bytes TX FIFO, non-DMA mode of operation, select the RX FIFO trigger level and to clear the TX FIFO.

- Write the LCR register so that the LCR[7] bit = 0 (for normal operation).

- 3. Program the IER register to enable only the data-transmission related interrupts.

- Enable the transmit threshold interrupt.

- Enable the transmit underrun interrupt.

- Disable the RX FIFO over threshold interrupt.

- Disable the RX FIFO overrun error interrupt.

- 4. Program the transmit modulation carrier-frequency register (TVMDCFG) to select the desired carrier frequency and pulse duration.

- 5. Write a 1 to the ACREG[7] bit to enable data transmission.

- 6. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

This completes the programming of registers and now the device is ready for data transmission.

### 2.1.4.2 SHARP Infrared Data-Receive Mode

The following register programming steps are required for data receive in the SHARP infrared mode:

- Program the infrared-configuration register (IRCFG). Select the SHARP infrared data-receive terminal to be either IRRVL (IRCFG[1] = 1) or IRRVH (IRCFG[1] = 0).

- Program the RX demodulation configuration register (TVDMCFG). Select the desired incoming infrared data carrier frequency range.

- 3. Reset the RX FIFO. This includes:

- Write to the LCR register to set the LCR[7] bit to a 1. The LCR[7] bit must be a 1 to be able to write to the FCR(5) bit.

- Program the FCR to select 64-/16-bytes TX FIFO, non-DMA mode of operation, select the RX FIFO trigger level and to clear the TX FIFO.

- Write the LCR register so that bit LCR[7] = 0 (for normal operation).

- 4. Program the IER register to enable only the receive related interrupts.

- 5. Write a 1 to the ACREG[6] bit to enable data receive.

- 6. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

This completes the programming of registers for data receive and now the device is ready to receive data. The CPU receives an interrupt and reads the IIR to identify the source of the interrupt. If the source of the interrupt is IIR[0] the CPU goes into the threshold mode. See paragraph 2.1.1.2.1. If the source of the interrupt is IIR[4] there has been an overrun while data receiving and the CPU needs to service the overrun. See paragraph 2.1.1.2.3.

#### 2.1.5 TV mode

The consumer TV remote-control (TV) mode supports data transmission between devices at a speed of up to 166.7 Kbps. Data can be transferred in a half-duplex mode. The following registers need to be programmed:

- 1. Program the interrupt configuration register (ICR) in order to:

- Select the IRQ channel.

- Select either totem-pole or open-drain output.

- Select an active high or an active low for an interrupt when the totem-pole configuration is selected.

- Program the prescaler (PRESC) register. The PRESC register can be programmed to a value so that:

$$\frac{X_{IN}}{PRESC} \le 5 \text{ MHz} \tag{3}$$

Where

For a 48-MHz input clock, a PRESC register value of larger than 0A (hex) is recommended. The default hex value is 1A. This default value is retained if the desired baud rate is under 115.2 Kbps.

Program the auxiliary baud-rate divisor lower byte (ABDL) and the auxiliary baud-rate divisor higher byte (ABDH) registers to select the desired communication baud rate for TV mode. The baud rate is determined by:

Baud rate =

$$\frac{X_{IN}}{PRESC \times Divisor \times 16}$$

(4)

$$\Longrightarrow$$

$$\mathsf{Divisor} = \frac{\mathsf{X}_{\mathsf{IN}}}{\mathsf{PRESC} \times \mathsf{BaudRate} \times \mathsf{16}}$$

The two 8-bit auxiliary baud-rate divisor registers store the divisor in a 16-bit binary format.

- 4. Program the mode-definition register (MDR) in order to:

- Select the TV mode

- Enable/disable the low-power mode. For normal operation, the low-power mode is enabled.

- Enable/disable the sleep mode. For normal operation, the sleep mode is disabled.

- Enable/disable the store and controlled data transmission. For normal operation, disable the SCT.

- Select the frame-closing method to set-EOT-bit (MDR[7]) to 1.

- Program the TV configuration register (TVCFG) to:

- Select the modulation mode (C\_PLS, 6\_PLS OR 8\_PLS).

- Enable/disable the receiver internal demodulation.

- Select programmed T-period mode or over-sampling mode. For normal operation select programmed T-period mode.

- Enable/disable the run-length coding mode.

- Select the TX carrier-frequency range.

- Select the RX carrier-frequency range.

- Write a 0 to the RX-active bit (TVCFG[7]). When set to a 1, this bit sets the device to sample

the infrared data even if the carrier frequency is out of range. This bit is normally used to

disable the RX when required. The RX automatically enables when infrared is detected and

the carrier frequency is in the programmed range.

## 2.1.5.1 TV Data-Transmission Mode

The following register programming steps are required for data transmission in the TV mode:

- 1. Program the PLR to select the TX FIFO trigger level

- 2. Reset the TX FIFO. This includes the following:

- Write to the LCR register to set the LCR[7] bit to a 1. The LCR[7] bit must be a 1 to be able to write to the FCR(5) bit.

- Program the FCR register to select 64-/16-bytes TX FIFO, non-DMA mode of operation, select the RX FIFO trigger level and to clear the TX FIFO.

- Write the LCR register so that the LCR[7] bit = 0 (for normal operation).

- Program the IER register to enable only the data-transmission related interrupts. This includes the following:

- Enable the TX threshold interrupt.

- Enable the TX underrun interrupt.

- Disable the RX FIFO over threshold interrupt.

- Disable the RX FIFO overrun error interrupt.

- 4. Program the TX modulation carrier-frequency register (TVMDCFG) to select the desired carrier frequency and its pulse duration.

- 5. Write a 1 to the ACREG[7] bit to enable data transmission.

- 6. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

This completes the programming of registers and the device is ready for data transmission. The TV data transmission only supports the set-EOT-bit method, thus the CPU must write a 1 to the ACREG[0] bit prior to writing the last byte of a frame to the TX FIFO. The CPU receives an interrupt and reads the IIR to identify

the source of the interrupt. If the source of the interrupt is IIR[1] (TX FIFO below the threshold interrupt), the CPU must:

- Disable the IER[1] bit

- Write data bytes to the TX FIFO. The maximum number of data bytes is limited to the number selected by the TX FIFO trigger level.

- Enable the IER[1] bit

If the source of the interrupt is a IIR[5] bit, an underrun has occurred while transmitting and the CPU must service the underrun. See paragraph 2.1.1.1.4.

#### 2.1.5.2 TV Receive Mode

The following register programming steps are required for data receive in the TV mode:

- Program the infrared configuration register (IRCFG). Select the TV infrared receive terminal to be either IRRVL (IRCFG[1] = 1) or IRRVH (IRCFG[1] = 0).

- Program the RX demodulation configuration register (TVDMCFG). Select the desired incoming infrared data carrier frequency range.

- 3. Reset the RX FIFO. This includes the following:

- Write to the LCR register to set the LCR[7] bit to a 1. The LCR[7] bit must be a 1 in order to be

able to write to the FCR(5) bit.

- Program the FCR to select 64-/16-bytes TX FIFO, non-DMA mode of operation, select the RX FIFO trigger level and to clear the TX FIFO.

- Write the LCR register so that bit LCR[7] = 0 (for normal operation).

- 4. Program the IER register to enable only the receive related interrupts which include:

- RX threshold interrupt (IER[0].

- RX FIFO overrun (IER[3]).

- Disable the TX related interrupts (TX FIFO below threshold interrupt and the TX underrun interrupt).

- 5. Write a 1 to the ACREG[6] bit to enable data receive.

- 6. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

This completes the programming of the registers for data receive and now the device is ready to receive data. The CPU receives an interrupt and reads the IIR to identify the source of the interrupt. If the source of the interrupt is IIR[0], the CPU goes to the threshold mode. See paragraph 2.1.1.2.1. If the source of the interrupt is IIR[4], an overrun has occurred while receiving data and the CPU needs to service the overrun. See paragraph 2.1.1.2.3.

7. To stop data receive after the End-Of-Frame flag (EOF) is detected by the CPU, write a 0 to the TVCFG[7] bit.

### 2.1.6 Universal Asynchronous Receiver Transmitter (UART) mode

The UART mode is the default mode of operation after power up and system reset. This mode uses a wired interface for serial communication with a remote device or a modem. The TIR2000 can operate in a full-duplex mode, i.e. data transmission and reception can take place simultaneously.

The TIR2000 in the UART mode works as a regular serial asynchronous communication controller that converts the parallel data received from the CPU or the DMA controller to serial data. It also converts the serial data received on the serial input terminal to parallel data.

## 2.1.6.1 Auto-flow Control (See Figure 2-4)

Auto-flow control is composed of auto-CTS and auto-RTS. With auto-CTS, CTS must be low before the transmit FIFO register can emit data (see Figure 2–4). With auto-RTS, RTS becomes high when the receiver is empty or the threshold has not been reached. When RTS is connected to the CTS, data transmission does not occur unless the receiver FIFO register has empty space. Overrun errors are eliminated when UART1 and UART2 are TIR2000 or other autoflow control devices with enabled flow control. When UART1 and UART2 are not autoflow control devices with enabled flow control an overrun error occurs if the transmit data exceeds the data receive FIFO-read capacity.

Figure 2–4. Example of Auto-flow Contol (Auto-RTS and Auto-CTS)

## 2.1.6.2 Auto-RTS (See Figure 2-4)

Auto-RTS data-flow control originates in the receiver timing and control block and is linked to the programmed RCV-FIFO trigger level. When the receiver FIFO trigger level reaches a trigger level of 1, 4, 8, or 14 in the 16-byte mode or 1, 16, 32, or 56 in the 64-byte mode, RTS is de-asserted. The sending UART may send an additional byte after the trigger level is reached (assuming the sending device has another byte to send) because it may not recognize the de-assertion of RTS until after it begins to send the additional byte. RTS is automatically reasserted when the RX FIFO register is emptied by reading the receiver-buffer register (RBR). The reassertion signals the sending UART to continue transmitting data.

## 2.1.6.3 Auto-CTS (See Figure 2–4)

The transmitter circuitry checks CTS before sending the next data byte. If CTS is low, the transmitter sends the next byte. To stop the transmitter from sending the following byte, CTS must be released before the middle of the last stop bit that is currently being sent. The auto-CTS function reduces interrupts to the host system. When the flow control is enabled, the CTS level changes and does not trigger host interrupts because the device automatically controls its own transmitter. Without auto-CTS, the transmitter sends any data present in the transmit FIFO register and a receiver overrun error can result.

To enable the auto-RTS and auto-CTS modes of operation bit 5 of the modem-control register must be set to a 1.

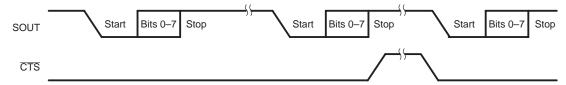

NOTES: A. When CTS is a low, the transmitter keeps sending serial data out.

- B. When CTS transitions to a high before the middle of the last stop bit of the current byte, the transmitter finishes sending the current byte but it does not send the next byte.

- C. When CTS transitions from a high to a low, the transmitter begins sending data again.

## Figure 2–5. CTS Functional Timing Diagram

# 2.1.6.4 Enabling Auto-RTS and Auto-CTS

The receiver FIFO trigger level can be set to 1, 4, 8, or 14 bytes for the 16-byte mode and 1, 16, 32, or 56 bytes for the 64-byte mode.

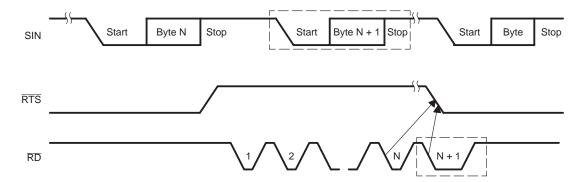

NOTES: A. N = receiver FIFO trigger level

B. The two blocks in dashed lines cover the case when an additional byte is sent as described in auto-CTS.

Figure 2–6. RTS Functional Timing, RCV-FIFO Trigger

## 2.1.6.4.1 Programming UART Related Registers

All UART related registers must be programmed for proper data communication. The following register programming steps are required for data communication:

- 1. Program the interrupt configuration register (ICR) in order to:

- Select the IRQ channel.

- Select either totem-pole or open-drain output.

- Select an active high or an active low for an interrupt when the totem-pole configuration is selected.

Program the baud-rate divisor lower byte (DLL) register and the baud-rate divisor higher byte (DLM) register to select the desired communication baud rate for the UART mode. The baud rate is given by:

Baud rate =

$$\frac{X_{IN}}{PRESC \times Divisor \times 16}$$

(5)

so the formula for the Divisor is:

$$Divisor = \frac{X_{IN}}{PRESC \times BaudRate \times 16}$$

Where

$X_{1N}$  = Input clock frequency to the chip

PRESC = PRESC register value

Baud Rate = Desired baud rate

The two 8-bit baud-rate divisor registers (DLL and DLM) store the divisor in a 16-bit binary format. The device can be changed to the UART mode from any other mode of operation by writing to the DLL or the DLM registers. This changes the MDR register MDR[2–0] bits to the UART mode automatically (known as the fall-back mechanism). The PRESC register also automatically changes to the default value.

- 3. Program the prescaler (PRESC) register so that the prescaler output is approximately 1.843 MHz. For an input frequency of 48 MHz, use the default PRESC value (26).

- 4. Program the mode-definition register (MDR) in order to:

- Select the UART mode.

- Enable/disable the low-power mode. For normal operation, the low-power mode is enabled.

- Enable/disable the sleep mode. For normal operation, the sleep mode is disabled.

- 5. Program the line-control register (LCR) in order to:

- Select the word length.

- Select the number of stop bits.

- Enable/disable parity generation.

- Select even/odd parity.

- Enable/disable stick parity.

- Enable/disable the break control.

- 6. Program the LCR to select the TX FIFO trigger level.

- 7. Reset the TX FIFO. This includes the following:

- Write to the LCR register to set the LCR[7] bit to a 1. The LCR[7] bit must be a 1 in order to be

able to write to the FCR(5) bit.

- Program the FCR register to select 64-/16-bytes TX FIFO register, non-DMA mode of operation, select the RX FIFO trigger level and to clear the TX FIFO.

- Write the LCR register so that the LCR[7] bit = 0 (for normal operation).

- Program the IER register to enable interrupts.

- 9. Write a 1 to the MCR[3] bit to enable the selected IRQ channel.

## 2.1.7 DMA Operation

The DMA mode of data transfer is used to achieve faster data transfer when the device is operating in the FIR or in the MIR modes. In a multi-application environment, where multiple applications are running at the same time, the DMA mode should be used to keep up with the high rate of data transfer without having underrun during data transmission or overrun during data receive. Frames can be transmitted and received back-to-back. The device must be programmed for data transmission and data receive. The DCSR register is programmed to select and enable the DMA channel for data transmit and data receive.

#### 2.1.7.1 DMA Data-Transmit Mode

Packets of various sizes can be transmitted. Packets, smaller than 2k bytes, can be properly terminated through the TC signal from the DMA controller or through the (TXFLH, TXFLL) registers value. Packets, larger than 2k bytes, can be automatically fragmented into equal-sized smaller frames (decided by the TXFLH and TXFLL registers value) and properly transmitted. The last portion of the packet, which may be smaller than the (TXFLH, TXFLL) register value, is terminated by the TC signal. The DMA controller asserts the TC signal when it sends the last byte of that packet. When the DMA asserts the TC signal, an interrupt IIR[6] bit is generated to inform the CPU that the DMA data transmission is complete.

The DMA controller uses the Demand Transfer mode to transfer data from memory to the TXFIFO. The peripheral device asserts the DRQ signal when the number of bytes in the TXFIFO falls below the set threshold level and de-asserts the DRQ when the TXFIFO becomes almost full.

#### 2.1.7.2 DMA Data-Receive Mode

The DMA controller controls the data reception of back-to-back frames. The back-to-back frames are transferred to memory and the status of each received frame is stored in the Status FIFO which can hold up to 8 entries. Each entry in the Status FIFO corresponds to one received frame. Each entry stores the length of each received frame and the error-status of that frame. The CPU reads the Status FIFO entries to locate the frame boundaries and status of individual frames inside memory.

The Status FIFO has 4 interrupt levels, which are 1, 4, 7, and 8. In a data receive transaction, the receiver peripheral expects to receive 1 to 7 frames. When the number of received frames becomes equal or greater than the set threshold value in the Status FIFO, the peripheral device generates an interrupt IIR[4] bit. After the CPU receives the Status FIFO interrupt (IIR[4] bit), it reads the Status FIFO Register High (SFREGH) and then the Status FIFO Register Low (SFREGL) to determine the length of the frame. The SFLSR register is then read to determine the error-status of that frame. The CPU checks the content of the SFLSR[4] bit which is set to a 1 when the Status FIFO becomes empty. If this bit is found to be a 1, the CPU should stop reading the SFREFH, SFREGL, and SFLSR registers.

The time-out interrupt is set at 1 ms. This is useful when the number of frames in a data receive transaction is less than the set Status FIFO threshold level. A time-out interrupt (IIR[2] bit) will be generated when the inter-frame gap between back-to-back frames is 1 ms. When the CPU receives a Status FIFO time-out interrupt, it should read the LSR register (LSR[1] bit) to find out the empty status of the Status FIFO. If the Status FIFO is empty, the CPU disregards the interrupt. If the Status FIFO is not empty, the CPU reacts the same as it does after receiving a Status FIFO threshold interrupt.

The DMA controller uses the demand transfer mode to transfer data from the RXFIFO to memory. The peripheral device asserts the DRQ signal when the number of bytes in the RXFIFO is equal to or greater than the set threshold level or when the end of a receive frame is detected by the RX state machine. The DRQ is de-asserted when the RXFIFO becomes empty. An overrun in the RXFIFO in the DMA mode is handled differently than in the programmed I/O mode. When an overrun occurs in the RXFIFO, during any frame, data reception is terminated and the RX state machine waits for the next frame. It continues to receive the further frames. The overrun error (OE bit) is set to a 1 in the SFLSR register for the frame in which a RXFIFO overrun has occurred.

(This page has been left blank intentionally.)

# 3 Register Definitions for the UART, SIR and SHARP Modes

# 3.1 Receiver-Buffer Register (RBR) – (read only)

The receiver buffer register is used to access the receiver-holding register when the RX FIFO register is disabled, or the RX FIFO when the RX FIFO is enabled. Address: 0 (hex) – LCR[7] bit should be a 0.

## 3.2 Transmitter Holding Register (THR) – (write only)

The transmitter holding register is used to access the transmitter (TX) holding register when the TX FIFO is disabled, or the TX FIFO when the TX FIFO is enabled. Address: 0 (hex) – LCR[7] bit should be a 0.

# 3.3 Interrupt Enable Register (IER) – (read and write)

Address: 1 (hex) - LCR[7] bit should be a 0.

Bit definitions are as follows:

| BIT NO. | DEFAULT | DESCRIPTIONS                                                                                                                                                             |  |  |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0       | 0       | Receiveddata-available interrupt enable (1 = enable, 0 = disable). When set, bit 0 enables an interrupt when the receiver FIFO is equal to or above its threshold level. |  |  |

| 1       | 0       | Transmitter holding-register-empty interrupt enable.                                                                                                                     |  |  |

| 2       | 0       | Receiver line-status interrupt enable.                                                                                                                                   |  |  |

| 3       | 0       | Modem-status interrupt enable.                                                                                                                                           |  |  |

| 4       | 0       | Not used                                                                                                                                                                 |  |  |

| 5       | 0       | Transmitter underrun interrupt enable                                                                                                                                    |  |  |

| 6       | 0       | 0                                                                                                                                                                        |  |  |

| 7       | 0       | 0                                                                                                                                                                        |  |  |

# 3.4 Interrupt Identification Register (IIR) - (read only)

Address: 2 (Hex) Bit Definitions:

| BIT NO. | DEFAULT | DESCRIPTION                                                                                        |  |  |  |

|---------|---------|----------------------------------------------------------------------------------------------------|--|--|--|

| 0       | 1       | Interrupt pending                                                                                  |  |  |  |

| 1       | 0       | Interrupt ID0                                                                                      |  |  |  |

| 2       | 0       | Interrupt ID1                                                                                      |  |  |  |

| 3       | 0       | Interrupt ID2                                                                                      |  |  |  |

| 4       | 0       | Reserved (always 0)                                                                                |  |  |  |

| 5       | 0       | FIFO enabled 1                                                                                     |  |  |  |

| 6       | 0       | FIFO enabled 2                                                                                     |  |  |  |

| 7       | 0       | FIFO enabled 3 (bit 7 bit 6 bit 5) = 000 FIFO disabled<br>= 110 16-byte FIFO<br>= 111 64-byte FIFO |  |  |  |

| INTER | INTERRUPT ID REGISTER |       |       | PRIORITY INTERRUPT | INTERRUPT SOURCE                         | INTERRUPT RESET                                                                                                                                                 |                                                                                          |

|-------|-----------------------|-------|-------|--------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| BIT 3 | BIT 2                 | BIT 1 | BIT 0 | LEVEL              | TYPE                                     |                                                                                                                                                                 | METHOD                                                                                   |