# TELECOMMUNICATION SYSTEM SECONDARY PROTECTION

Ion-Implanted Breakdown Region Precise and Stable Voltage Low Voltage Overshoot under Surge

| DEVICE | V <sub>(Z)</sub> | V <sub>(BO)</sub> |  |  |

|--------|------------------|-------------------|--|--|

| DEVIOL | - V V            |                   |  |  |

| '3180  | 145              | 180               |  |  |

- Planar Passivated Junctions Low Off-State Current < 10 μA</li>

- Rated for International Surge Wave Shapes

| WAVE SHAPE | STANDARD         | I <sub>TSP</sub> |

|------------|------------------|------------------|

| 8/20 µs    | ANSI C62.41      | 150              |

| 10/160 µs  | FCC Part 68      | 60               |

| 10/560 µs  | FCC Part 68      | 45               |

| 0.2/310 µs | RLM 88           | 38               |

|            | FTZ R12          | 50               |

| 10/700 μs  | VDE 0433         | 50               |

|            | CCITT IX K17/K20 | 50               |

| 10/1000 µs | REA PE-60        | 50               |

# UL Recognized, E132482

# description

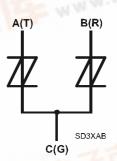

The TISP3180 is designed specifically for telephone equipment protection against lightning and transients induced by a.c. power lines. These devices consist of two bidirectional suppressor elements connected to a Common (C) terminal. They will supress voltage transients between terminals A and C, B and C, and A and B.

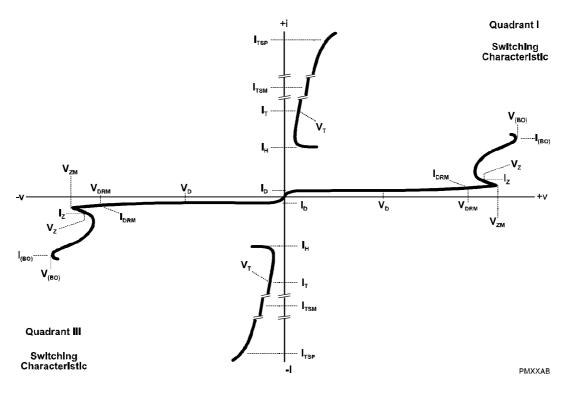

Transients are initially clipped by zener action until the voltage rises to the breakover level, which causes the device to crowbar. The high crowbar holding current prevents d.c. latchup as the transient subsides.

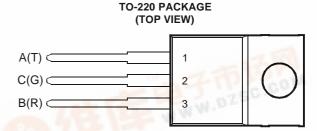

Pin 2 is in electrical contact with the mounting base.

MDXXANA

# device symbol

These monolithic protection devices are fabricated in ion-implanted planar structures to ensure precise and matched breakover control and are virtually transparent to the system in normal operation.

# TISP3180 DUAL SYMMETRICAL TRANSIENT VOLTAGE SUPPRESSORS

NOVEMBER 1986 - REVISED SEPTEMBER 1997

# absolute maximum ratings at 25°C case temperature (unless otherwise noted)

| RATING                                                                                   | SYMBOL              | VALUE       | UNIT  |

|------------------------------------------------------------------------------------------|---------------------|-------------|-------|

| Non-repetitive peak on-state pulse current (see Notes 1, 2 and 3)                        |                     |             |       |

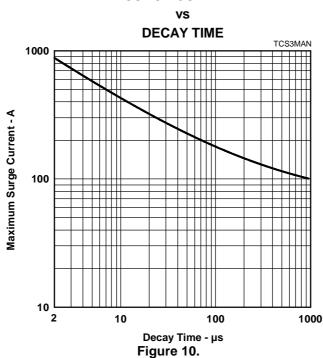

| 8/20 μs (ANSI C62.41, open-circuit voltage wave shape 1.2/50 μs)                         |                     | 150         |       |

| 10/160 μs (FCC Part 68, open-circuit voltage wave shape 10/160 μs)                       |                     | 60          |       |

| 5/200 μs (VDE 0433, open-circuit voltage wave shape 2 kV, 10/700 μs)                     |                     | 50          |       |

| 0.2/310 μs (RLM 88, open-circuit voltage wave shape 1.5 kV, 0.5/700 μs)                  | I <sub>TSP</sub>    | 38          | Α     |

| 5/310 μs (CCITT IX K17/K20, open-circuit voltage wave shape 2 kV, 10/700 μs)             |                     | 50          |       |

| 5/310 μs (FTZ R12, open-circuit voltage wave shape 2 kV, 10/700 μs)                      |                     | 50          |       |

| 10/560 μs (FCC Part 68, open-circuit voltage wave shape 10/560 μs)                       |                     | 45          |       |

| 10/1000 μs (REA PE-60, open-circuit voltage wave shape 10/1000 μs)                       |                     | 50          |       |

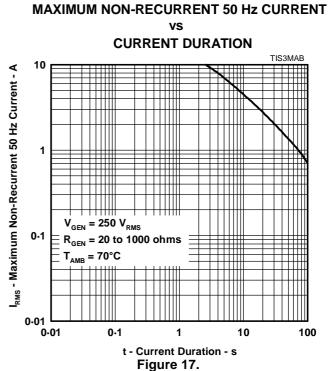

| Non-repetitive peak on-state current, 50 Hz, 2.5 s (see Notes 1 and 2)                   | I <sub>TSM</sub>    | 10          | A rms |

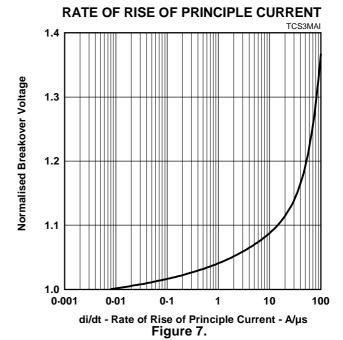

| Initial rate of rise of on-state current, Linear current ramp, Maximum ramp value < 38 A | di <sub>T</sub> /dt | 250         | A/µs  |

| Junction temperature                                                                     | TJ                  | 150         | °C    |

| Operating free - air temperature range                                                   |                     | 0 to 70     | °C    |

| Storage temperature range                                                                | T <sub>stg</sub>    | -40 to +150 | °C    |

| Lead temperature 1.5 mm from case for 10 s                                               | T <sub>lead</sub>   | 260         | °C    |

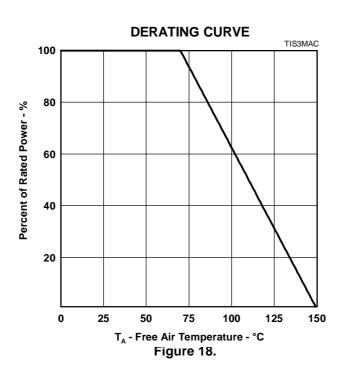

- NOTES: 1. Above 70°C, derate linearly to zero at 150°C case temperature

- 2. This value applies when the initial case temperature is at (or below) 70°C. The surge may be repeated after the device has returned to thermal equilibrium.

- 3. Most PTT's quote an unloaded voltage waveform. In operation the TISP essentially shorts the generator output. The resulting loaded current waveform is specified.

# electrical characteristics for the A and B terminals, $T_J = 25$ °C

|                  | PARAMETER             |                         | TEST CONDITI | ONS          | MIN   | TYP | MAX  | UNIT |

|------------------|-----------------------|-------------------------|--------------|--------------|-------|-----|------|------|

| Vz               | Reference zener       | $I_Z = \pm 1 \text{mA}$ |              |              | ± 290 |     |      | V    |

| ٧Z               | voltage               | 1Z = ± 11117            |              |              | 1 230 |     |      | ·    |

| 1                | Off-state leakage     | V <sub>D</sub> = ± 50 V |              |              |       |     | ± 10 | μA   |

| l <sub>D</sub>   | current               | VD = ± 30 V             |              |              |       |     | ± 10 | μΑ   |

| C <sub>off</sub> | Off-state capacitance | $V_D = 0$               | f = 1 kHz    | (see Note 4) |       | 0.5 | 5    | pF   |

NOTE 4: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is connected to the guard terminal of the bridge.

# electrical characteristics for the A and C or the B and C terminals, $T_J = 25$ °C

|                   | PARAMETER                |                         | TEST CONDITIONS     |              | MIN    | TYP   | MAX   | UNIT  |

|-------------------|--------------------------|-------------------------|---------------------|--------------|--------|-------|-------|-------|

| Vz                | Reference zener          | $I_Z = \pm 1 \text{mA}$ |                     |              | ± 145  |       |       | V     |

| VZ                | voltage                  | 1Z - T 1111Q            |                     |              | 143    | 1     |       | V     |

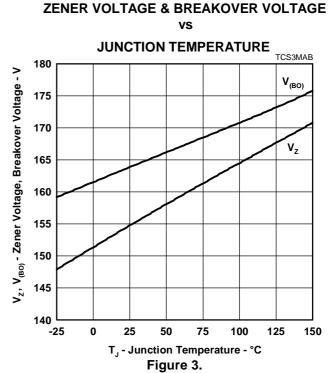

| ∝V <sub>Z</sub>   | Temperature coefficient  |                         |                     |              |        | 0.1   |       | %/°C  |

| ٧Z                | of reference voltage     |                         |                     |              |        | 0.1   |       | 76/ C |

| V <sub>(BO)</sub> | Breakover voltage        | (see Notes 5 and 6)     |                     |              |        |       | ± 180 | V     |

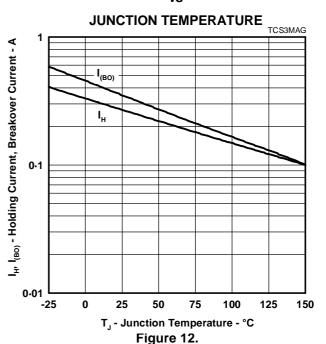

| I <sub>(BO)</sub> | Breakover current        | (see Note 5)            |                     |              | ± 0.15 |       | ± 0.6 | Α     |

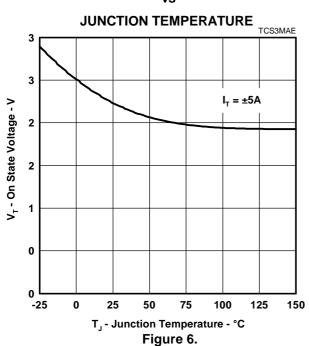

| V <sub>TM</sub>   | Peak on-state voltage    | I <sub>T</sub> = ± 5 A  | (see Notes 5 and 6) |              |        | ± 2.2 | ± 3   | V     |

| I <sub>H</sub>    | Holding current          | (see Note 5)            |                     |              | ± 150  |       |       | mA    |

| dv/dt             | Critical rate of rise of | (see Note 7)            |                     |              |        |       | ± 5   | kV/μs |

| uv/ut             | off-state voltage        | (See Note 1)            |                     |              |        |       |       | κν/μο |

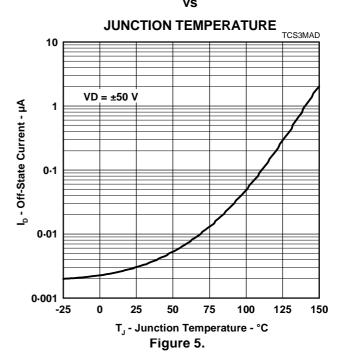

| I_                | Off-state leakage        | V <sub>D</sub> = ± 50 V |                     |              |        |       | ± 10  | μА    |

| I <sub>D</sub>    | current                  | ^D - ± 30 v             |                     |              |        |       | ± 10  | μΑ    |

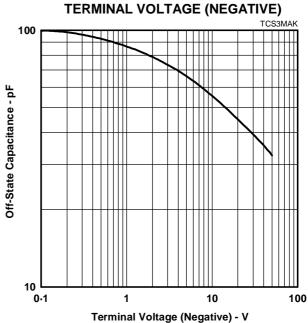

| C <sub>off</sub>  | Off-state capacitance    | $V_D = 0$               | f = 1 kHz           | (see Note 4) |        | 110   | 200   | pF    |

- NOTES: 5. These parameters must be measured using pulse techniques,  $t_w = 100 \mu s$ , duty cycle  $\leq 2\%$ .

- 6. These parameters are measured with voltage sensing contacts seperate from the current carrying contacts located within 3.2 mm (0.125 inch) from the device body.

- 7. Linear rate of rise, maximum voltage limited to 80 %  $\rm V_{\rm Z}$  (minimum)..

NOVEMBER 1986 - REVISED SEPTEMBER 1997

# PARAMETER MEASUREMENT INFORMATION

Figure 1. VOLTAGE-CURRENT CHARACTERISTIC FOR ANY PAIR OF TERMINALS

# thermal characteristics

| PARAMETER                                                |  | TYP | MAX  | UNIT |

|----------------------------------------------------------|--|-----|------|------|

| R <sub>0JA</sub> Junction to free air thermal resistance |  |     | 62.5 | °C/W |

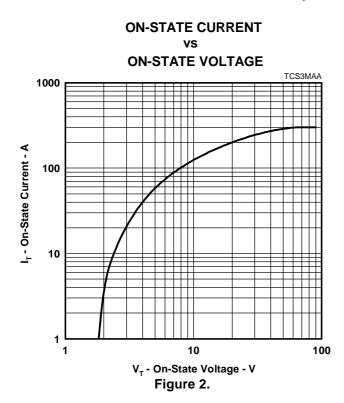

# TYPICAL CHARACTERISTICS A and C, or B and C terminals

# TYPICAL CHARACTERISTICS A and C, or B and C terminals

# HOLDING CURRENT & BREAKOVER CURRENT vs

# JUNCTION TEMPERATURE TCS3MAC TCS3MAC TCS3MAC TCS3MAC TCS3MAC TCS3MAC TCS3MAC TCS3MAC TCS3MAC TGS3MAC TGS3MAC

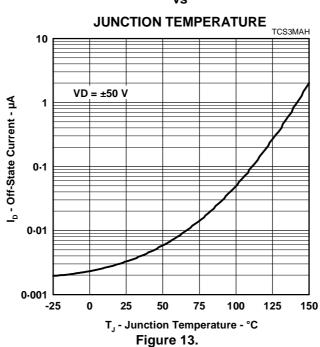

# OFF-STATE CURRENT

# ON-STATE VOLTAGE vs

# NORMALISED BREAKOVER VOLTAGE vs

100

Off-State Capacitance - pF

10

0-1

# TYPICAL CHARACTERISTICS A and C, or B and C terminals

# TERMINAL VOLTAGE (POSITIVE) TCS3MAJ

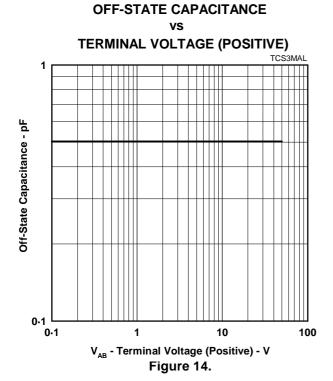

**OFF-STATE CAPACITANCE**

SMAJ

100

Terminal Voltage (Positive) - V

Figure 8.

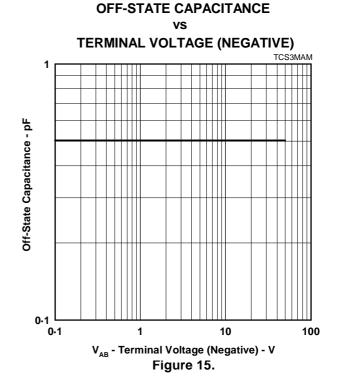

# OFF-STATE CAPACITANCE vs RMINAL VOLTAGE (NEGATI)

Figure 9.

# **SURGE CURRENT**

# TYPICAL CHARACTERISTICS A and B terminals

# ZENER VOLTAGE & BREAKOVER VOLTAGE

# **JUNCTION TEMPERATURE** TCS3MAF 360 $V_z, V_{(BO)}$ - Zener Voltage, Breakover Voltage - V **V**<sub>(BO)</sub> 350 340 330 320 310 300 290 280 -25 0 125 150 $T_J$ - Junction Temperature - °C Figure 11.

# HOLDING CURRENT & BREAKOVER CURRENT

# OFF-STATE CURRENT vs

# TYPICAL CHARACTERISTICS A and B terminals

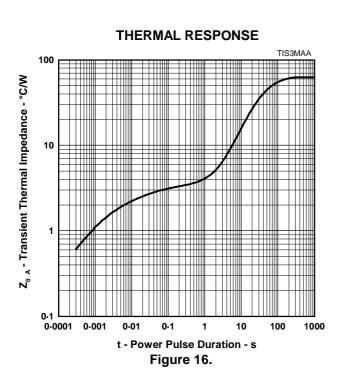

# THERMAL INFORMATION

# FREE AIR TEMPERATURE

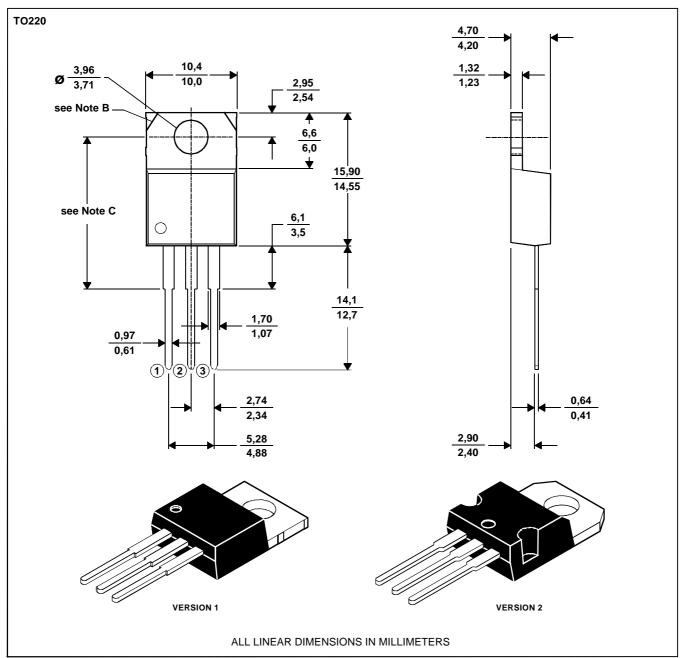

# **MECHANICAL DATA**

### **TO-220**

# 3-pin plastic flange-mount package

This single-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

NOTES: A. The centre pin is in electrical contact with the mounting tab.

- B. Mounting tab corner profile according to package version.

- C. Typical fixing hole centre stand off height according to package version. Version 1, 18.0 mm. Version 2, 17.6 mm.

**MDXXBE**

# TISP3180 DUAL SYMMETRICAL TRANSIENT VOLTAGE SUPPRESSORS

NOVEMBER 1986 - REVISED SEPTEMBER 1997

## **IMPORTANT NOTICE**

Power Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the information being relied on is current.

PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with PI's standard warranty. Testing and other quality control techniques are utilized to the extent PI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except as mandated by government requirements.

PI accepts no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor is any license, either express or implied, granted under any patent right, copyright, design right, or other intellectual property right of PI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS.

Copyright © 1997, Power Innovations Limited