## TL855

## Professional Digital TV Decoder

All Format video/graphics solution for studio or professional quality equipment

### GLOBAL AND SCALABLE ARCHITECTURE

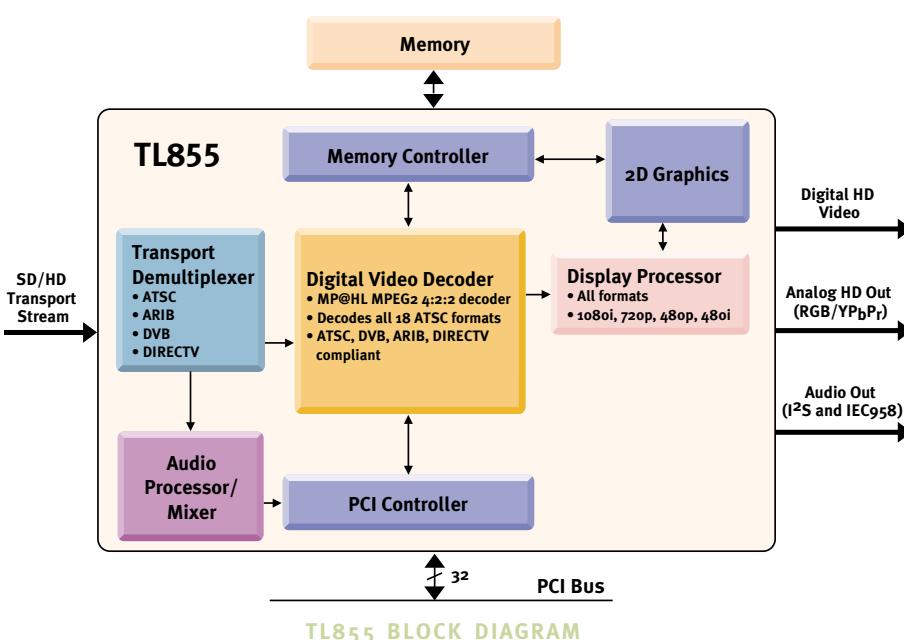

The TL855 is an integrated MPEG-2 MP@HL 4:2:2 video decoder, display processor and graphics accelerator for professional advanced Digital Television. It complies with all ATSC/ARIB/DVB-HD/DIRECTV®-HD recommended performance metrics and supports direct video output to a variety of display types. It performs professional quality decoding (4:2:2) of a single HD program (MP@HL). An integrated graphics accelerator renders text and graphics to an independent on-screen display (OSD) bitmap. The IC buffers the audio data, allowing the use of a standard Dolby Digital (AC-3) decoder chip or software on a host CPU for audio decoding.

The TL855 accepts MPEG compressed data encoded in the 4:2:2 format. Four Y, two Cb and two Cr values are generated for every four pixels decoded. Compared to 4:2:0 decoding, 4:2:2 decoding generates two extra chroma components requiring a considerable increase in performance over 4:2:0 consumer decoders. Therefore the TL855 memory interface, the MPEG decoder core engine and the display controller must be highly tuned for 4:2:2 processing. The memory interface has twice the buffering of conventional 4:2:0 decoders to handle the extra amount of chroma component during writes and reads. The MPEG decoder engine decodes the extra chroma values. The display controller accepts 4:2:2 data from the SDRAM as decoded by the MPEG decoder engine, then displays this higher quality video on the screen.

The TL855 is able to process all ATSC, DVB-HD and ARIB formats (and other worldwide and proprietary decoding such as DIRECTV) in high quality 4:2:2 video and then display the resultant video at this quality. In addition to the MPEG-2 4:2:2 decode, the TL850 performs format conversion from any ATSC format to any other ATSC format (including many non-standard resolutions). An on-chip 2D graphics accelerator provides TV-centric graphics and OSD to complement the video quality. A PCI interface allows ease of interfacing to a variety of common off-the-shelf components suitable for professional systems. In addition to these functions the TL855 can be programmed into a 4:2:0 mode of operation.

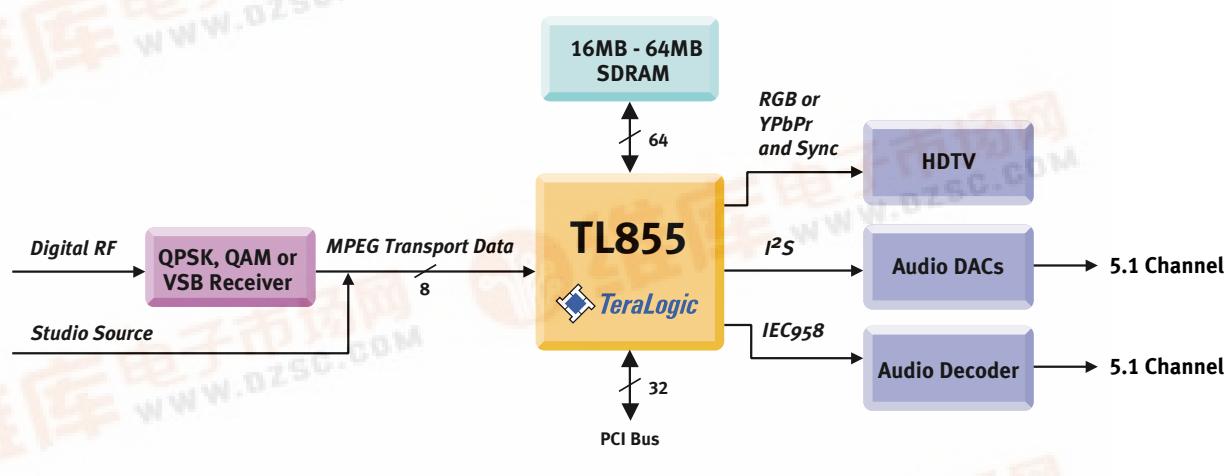

TL855 SYSTEM DIAGRAM

# TL855 Professional Digital TV Decoder

## APPLICATIONS

- Professional/Broadcast STB

- Professional video decoding/editing systems

- Ad Insertion Systems

- Digital Cinema

## SUPPORTING TERALOGIC PRODUCTS

- Cougar Pro Development Platform

- TL81x STB/PVR Controller ICs

## PROGRAMMABLE TRANSPORT

### DEMULTIPLEXER

- ATSC/DVB-HD/DIRECTV-HD compliant

- Glueless interface to most front-end ICs

- Maximum input bit rate of 135 Mbits/sec supported

## HIGH-PERFORMANCE 4:2:2 DIGITAL

### VIDEO DECODER

- MP@HL MPEG2 4:2:2 decoder

- All ATSC/ARIB/DVB/DIRECTV compliant decode formats

- Decodes one 4:2:2 HD (MP@HL) stream at a time

- Decodes and displays HD content in 4:2:2 mode for professional applications

## HIGH-PERFORMANCE DISPLAY

### PROCESSOR

- Multiple output display formats supported, including 1920x1080i, 1280x720p, 704x480p and 704x480i

- Many nonstandard input and output formats supported

- Up/down conversion of source to selected display format

- Graphics overlay plane with up to 8-bits per pixel and global alpha blending

- Analog RGB or YCrCb output for HDTV display

- Support for SMPTE 274M-, SMPTE 296M-, SMPTE 293M-, and EIA 770-compatible tri-level sync on analog output

- 16- or 24-bit digital video output in YCrCb or RGB mode

## AUDIO PROCESSING

- Audio stream play from memory

- Audio mix, cross-fade and attenuate between sources

- Six-channel audio output

- IEC-958 formatted output supported

- Provides audio rate buffer

- Supports audio and video PTS synchronization

## ACCELERATED 2-D GRAPHICS

- Full alpha blend support

- Up to 32 bpp graphics in RGB

## MEMORY CONTROLLER

- 64-bit wide SDRAM interface

- Programmable clock generator

- Up to 64 Mbytes addressing range

## PCI BUS INTERFACE

- 32-bit interface

- 66 MHz or 33 MHz bus clock

- PCI slave capability supported

- DMA master capability over PCI bus supported (4:2:0 mode only)

## VIDEO DECODE AND DISPLAY

### OF 4:2:0 CONTENT

- Supports video decode and display of 4:2:0 content as specified in the TL850 specification.

- Extra features are enabled in this mode such as extra graphics modes. See the TL850 product brief for the full list of features enabled.

## TECHNOLOGY

- 2.5-V core, 3.3-V I/O, 0.25-m CMOS

- 348-pin ball grid array package

**TeraLogic, Inc.** 1240 Villa Street Mountain View CA 94041

tel 650.526.2000 fax 650.526.2006 [www.teralogic.tv](http://www.teralogic.tv)

Copyright 2000, TeraLogic, Inc. All rights reserved worldwide. TeraLogic and the TeraLogic logo are registered trademarks of TeraLogic, Inc. Janus is a trademark of TeraLogic, Inc. All other trademarks are properties of their respective owners and are acknowledged.

11/00 - 5K