# **TLK3114SC**10-Gbps XAUI Transceiver

# Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                                       |                                                                            | Applications                                                                             |                                                                                                                                                                         |

|------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amplifiers                                     | amplifier.ti.com                                                           | Audio                                                                                    | www.ti.com/audio                                                                                                                                                        |

| Data Converters                                | dataconverter.ti.com                                                       | Automotive                                                                               | www.ti.com/automotive                                                                                                                                                   |

| DSP                                            | dsp.ti.com                                                                 | Broadband                                                                                | www.ti.com/broadband                                                                                                                                                    |

| Interface                                      | interface.ti.com                                                           | Digital Control                                                                          | www.ti.com/digitalcontrol                                                                                                                                               |

| Logic                                          | logic.ti.com                                                               | Military                                                                                 | www.ti.com/military                                                                                                                                                     |

| Power Mgmt                                     | power.ti.com                                                               | Optical Networking                                                                       | www.ti.com/opticalnetwork                                                                                                                                               |

| Microcontrollers                               | microcontroller.ti.com                                                     | Security                                                                                 | www.ti.com/security                                                                                                                                                     |

|                                                |                                                                            | Telephony                                                                                | www.ti.com/telephony                                                                                                                                                    |

|                                                |                                                                            | Video & Imaging                                                                          | www.ti.com/video                                                                                                                                                        |

|                                                |                                                                            | Wireless                                                                                 | www.ti.com/wireless                                                                                                                                                     |

| Data Converters DSP Interface Logic Power Mgmt | dataconverter.ti.com dsp.ti.com interface.ti.com logic.ti.com power.ti.com | Broadband Digital Control Military Optical Networking Security Telephony Video & Imaging | www.ti.com/broadband<br>www.ti.com/digitalcontrol<br>www.ti.com/military<br>www.ti.com/opticalnetwor<br>www.ti.com/security<br>www.ti.com/telephony<br>www.ti.com/video |

Mailing Address: Texas Instruments

Post Office Box 655303, Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated

## **Contents**

| Se | ection | Title                                                  | Page   |

|----|--------|--------------------------------------------------------|--------|

| 1  | Descr  | ription                                                | . 1–1  |

|    | 1.1    | Features                                               | 1–5    |

|    | 1.2    | Ordering Information                                   | 1–6    |

| 2  | Termi  | nal Descriptions                                       | 2–1    |

| 3  | Detail | led Description                                        | 3–1    |

|    | 3.1    | Serdes Modes                                           | 3–1    |

|    | 3.2    | 10-Gbps Ethernet Transceiver Modes                     |        |

|    | 3.3    | Parallel Interface Clocking                            |        |

|    | 3.4    | Parallel Interface Data                                | 3–1    |

|    | 3.5    | Transmit Data Bus Timing                               | 3–2    |

|    | 3.6    | Transmission Latency                                   |        |

|    | 3.7    | Channel Clock to Serial Transmit Clock Synchronization | 3–3    |

|    | 3.8    | Receive Data Bus Timing                                | 3–4    |

|    | 3.9    | Data Reception Latency                                 |        |

|    | 3.10   | Auto Detectable HSTL/SSTL_2 Class 1 I/O                |        |

|    | 3.11   | 8-b/10-b Encoder                                       |        |

|    | 3.12   | Comma Detect and 8-b/10-b Decoding                     |        |

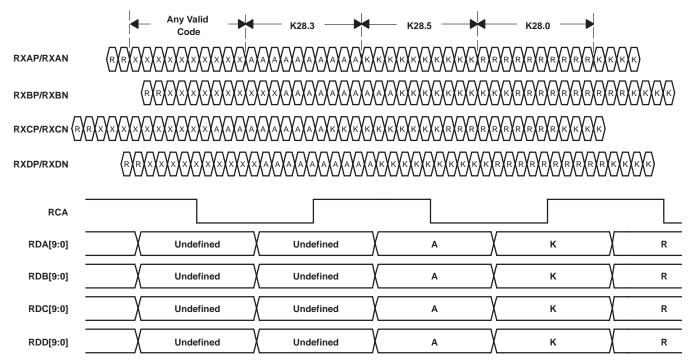

|    | 3.13   | Channel Initialization and Synchronization             |        |

|    |        | 3.13.1 Channel State Descriptions                      |        |

|    | 3.14   | End-of-Packet Error Detection                          |        |

|    | 3.15   | Fault Detection and Reporting                          |        |

|    | 3.16   | Receive Synchronization and Skew Compensation          |        |

|    |        | 3.16.1 Column State Descriptions                       |        |

|    | 3.17   | Independent Channel Mode                               |        |

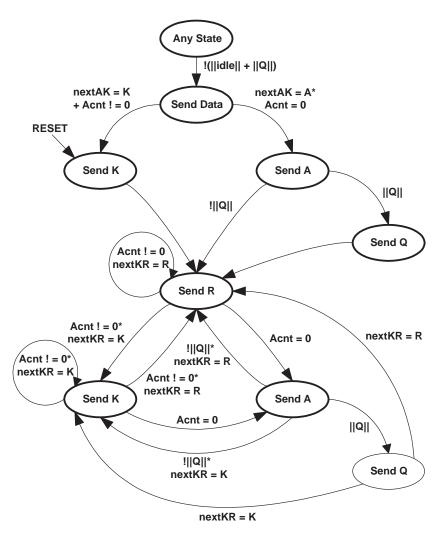

|    | 3.18   | Inter-Packet Gap Management                            |        |

|    | 3.19   | Clock Tolerance Compensation (CTC)                     |        |

|    | 3.20   | Parallel-to-Serial Shift Register                      |        |

|    | 3.21   | Serial-to-Parallel Shift Register                      |        |

|    | 3.22   | High-Speed VML Output Driver                           |        |

|    | 3.23   | Device Configuration                                   |        |

|    | 3.24   | PRBS Generator                                         |        |

|    | 3.25   | MDIO Management Interface                              |        |

|    | 3.26   | Operating Frequency Range                              |        |

|    | 3.27   | Power-Down Mode                                        |        |

|    | 3.28   | Loopback Testing                                       |        |

|    | 3.29   | Power-On Reset                                         |        |

|    | 3.30   | Differences From the TLK3104SA Device                  | . 3–37 |

| 4  | Elect                                     | rical Specifications                                               | 4–1    |  |  |  |  |

|----|-------------------------------------------|--------------------------------------------------------------------|--------|--|--|--|--|

|    | 4.1                                       | Absolute Maximum Ratings Over Operating Free-Air Temperature Range | 4–1    |  |  |  |  |

|    | 4.2                                       | Recommended Operating Conditions                                   |        |  |  |  |  |

|    | 4.3                                       | Reference Clock Timing Requirements (RFCP/N)                       |        |  |  |  |  |

|    | 4.4                                       | Reference Clock Electrical Characteristics (RFCP/N)                | 4–2    |  |  |  |  |

|    | 4.5                                       | LVTTL Electrical Characteristics                                   |        |  |  |  |  |

|    | 4.6                                       | SSTL_2 Class 1 Signals                                             |        |  |  |  |  |

|    | 4.7                                       | HSTL Signals                                                       |        |  |  |  |  |

|    | 4.8                                       | Serial Transmitter/Receiver Characteristics                        |        |  |  |  |  |

|    | 4.9                                       | SSTL_2 Class 1/HSTL Junut Timing Programments                      |        |  |  |  |  |

|    | 4.10<br>4.11                              | SSTL_2 Class 1/HSTL Input Timing Requirements                      |        |  |  |  |  |

|    | 4.11                                      | Package Dissipation Rating                                         |        |  |  |  |  |

| 5  |                                           | anical Data                                                        |        |  |  |  |  |

|    | Moon                                      |                                                                    | 0 .    |  |  |  |  |

|    |                                           | list of Illustrations                                              |        |  |  |  |  |

|    |                                           | List of Illustrations                                              | _      |  |  |  |  |

| •  | gure                                      | Title                                                              | Page   |  |  |  |  |

|    | -                                         | em Block Diagram (Chip-to-Chip Implementation)                     |        |  |  |  |  |

|    | •                                         | em Block Diagram (PCS Implementation)                              |        |  |  |  |  |

|    | -                                         | em Block Diagram (Backplane Interconnect Implementation)           |        |  |  |  |  |

| 1– | 4 TLK                                     | 3114SC Block Diagram                                               | 1–4    |  |  |  |  |

| 1– | 5 Bloc                                    | k Diagram of Individual Channel                                    | 1–5    |  |  |  |  |

| 2- | 1 TLK                                     | 3114SC GNT/GPV-Package Terminal Diagram                            | 2–1    |  |  |  |  |

| 3– | 1 Tran                                    | smit Interface Timing                                              | 3–2    |  |  |  |  |

| 3– | 2 Tran                                    | smitter Latency                                                    | 3–3    |  |  |  |  |

| 3– | 3 Tran                                    | smit and Reference Clock Relationship (Channel Sync Mode)          | 3–3    |  |  |  |  |

|    |                                           | smit and Reference Clock Relationship                              |        |  |  |  |  |

|    |                                           | ndependent Channel Mode)                                           | 3–4    |  |  |  |  |

| 3– | 5 Rece                                    | eive Interface Timing                                              | 3–4    |  |  |  |  |

| 3– | 6 Rece                                    | eiver Latency                                                      | 3–5    |  |  |  |  |

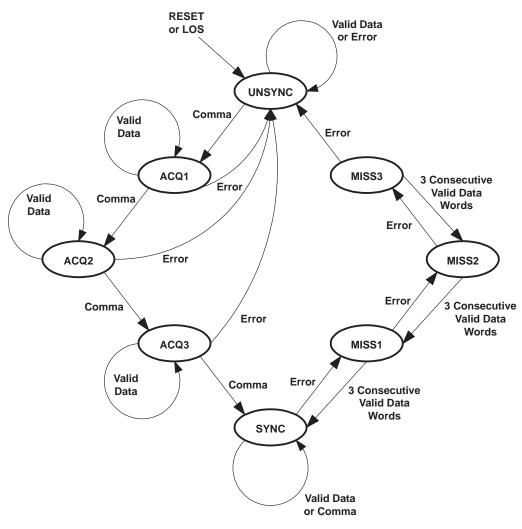

|    | 3–7 Channel Synchronization State Machine |                                                                    |        |  |  |  |  |

|    |                                           | of-Packet Error Detection                                          |        |  |  |  |  |

|    |                                           | eive and Reference Clock Relationship                              |        |  |  |  |  |

|    |                                           | Synchronized Channel Modes)                                        | . 3–10 |  |  |  |  |

| 3– | 10 Col                                    | lumn De-skew State Machine                                         | . 3–11 |  |  |  |  |

|    |                                           | ceive and Reference Clock Relationship                             |        |  |  |  |  |

|    |                                           | ndependent Channel Modes)                                          | . 3–12 |  |  |  |  |

| 3– | 12 Inte                                   | er-Packet Gap Management                                           | . 3–13 |  |  |  |  |

|    |                                           | Management State Machine                                           |        |  |  |  |  |

|    |                                           | -                                                                  |        |  |  |  |  |

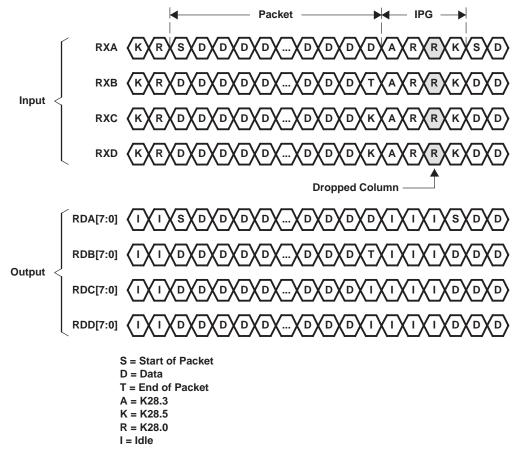

| 3–14 Channel Synchronization Using Alignment Code                  | 3–15 |

|--------------------------------------------------------------------|------|

| 3–15 Clock Tolerance Compensation: Add                             | 3–16 |

| 3–16 Clock Tolerance Compensation: Drop                            | 3–17 |

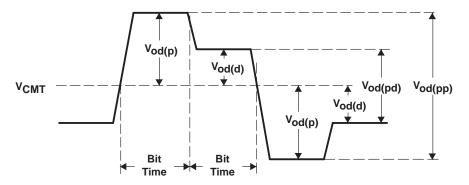

| 3–17 Output Differential Voltage Under Preemphasis                 | 3–18 |

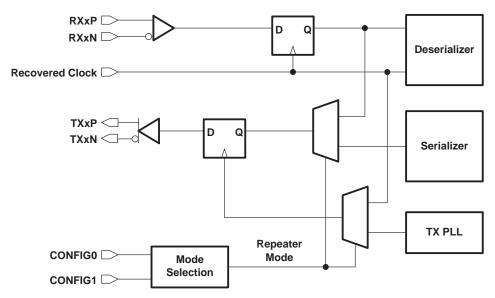

| 3–18 Repeater-Mode Block Diagram                                   |      |

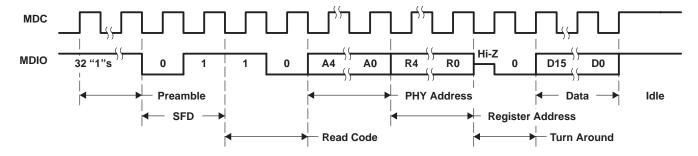

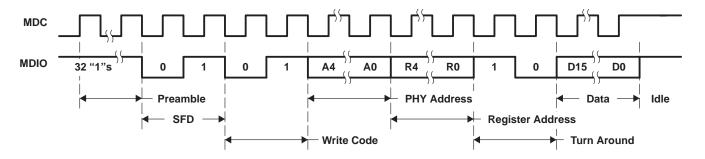

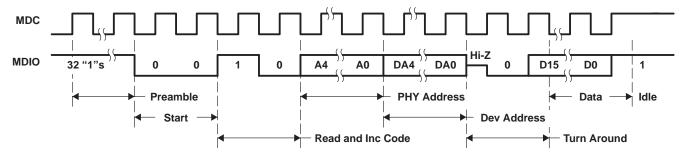

| 3–19 Management Interface Read Timing                              | 3–20 |

| 3–20 Management Interface Write Timing                             |      |

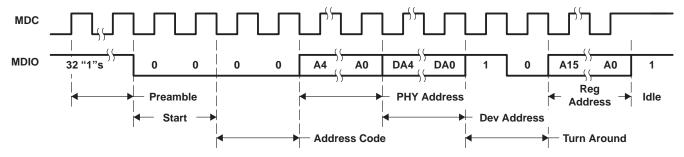

| 3–21 Management Interface Extended Space Address Timing            | 3–21 |

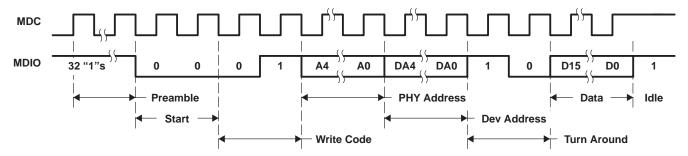

| 3–22 Management Interface Extended Space Write Timing              |      |

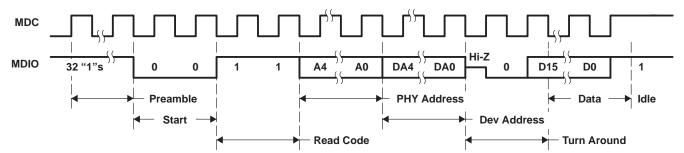

| 3–23 Management Interface Extended Space Read Timing               |      |

| 3–24 Management Interface Extended Space Read and Increment Timing |      |

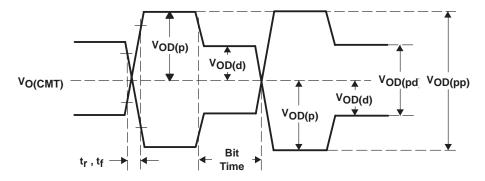

| 4–1 Differential and Common-Mode Output Voltage Definitions        |      |

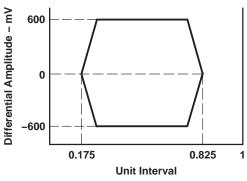

| 4–2 Transmit Template                                              |      |

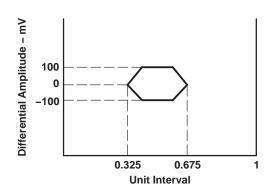

| 4–3 Receive Template                                               | 4–4  |

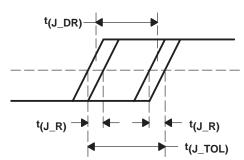

| 4–4 Input Jitter                                                   | 4–4  |

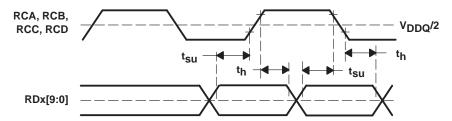

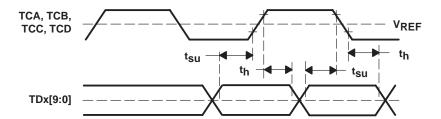

| 4–5 SSTL_2 Class 1/HSTL Output Timing Requirements                 |      |

| 4–6 SSTL_2 Class 1/HSTL Data Input Timing Requirements             |      |

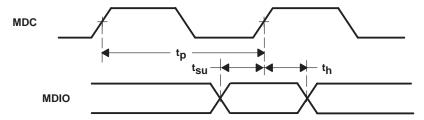

| 4–7 MDIO Read/Write Timing                                         |      |

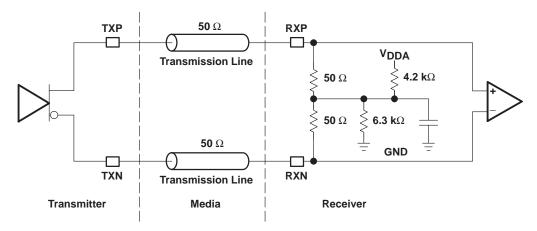

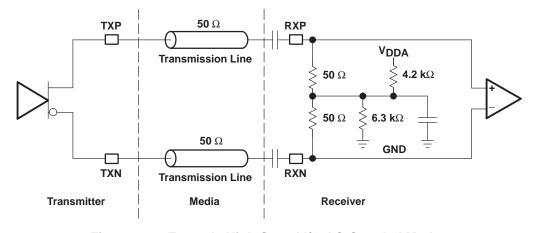

| 4–8 High-Speed I/O Direct-Coupled Mode                             |      |

| 4–9 Example High-Speed I/O AC-Coupled Mode                         |      |

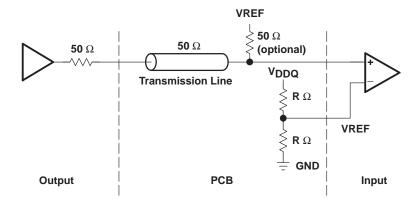

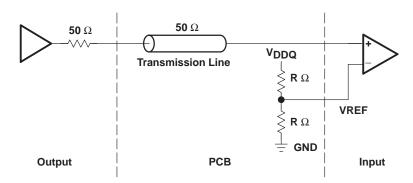

| 4–10 SSTL_2 Class 1 I/O                                            |      |

| 4–11 HSTL I/O                                                      |      |

|                                                                    |      |

| •••••                                                              |      |

| List of Tables                                                     |      |

| Table Title                                                        | Page |

| 2-1 Clock Terminals                                                | 2–2  |

| 2–2 Serial Side Data Terminals                                     |      |

| 2–3 Parallel Data Terminals                                        | 2–3  |

| 2–4 JTAG Test Port Interface                                       |      |

| 2–5 Management Data Interface                                      |      |

| 2–7 Voltage Supply and Reference Terminals                         |      |

| 3–1 Operational Interface Modes                                    |      |

| 3–2 Parallel Interface Clocking Modes                              |      |

| 3–3 Parallel Data Modes                                            | 3–2  |

| 3–4 Valid K-Codes                                                  |      |

| 3–5 Valid XGMII Channel Encodings                                  |      |

| 3–6 Receive Data Controls                                          |      |

| 3–7 Local and Remote Fault Sequences                               | 3-9  |

| 3-8 I | PG Management State Machine Notation                            | 3–14 |

|-------|-----------------------------------------------------------------|------|

| 3-9 F | Programmable Preemphasis                                        | 3–18 |

| 3–10  | Device Configuration                                            | 3–19 |

| 3–11  | MDIO Device Address                                             | 3-20 |

|       | MDIO Registers                                                  |      |

| 3–13  | Control Register Bit Definitions (Register 0)                   | 3-23 |

|       | Status Register Bit Definitions (Register 1)                    |      |

| 3–15  | PHY Identifier Bit Definitions (Register 2)                     | 3–24 |

|       | PHY Identifier Bit Definitions (Register 3)                     |      |

| 3–17  | Extended Status Register Bit Definitions (Register 15)          | 3–24 |

| 3–18  | Global Configuration Register Bit Definitions (Register 16)     | 3–25 |

| 3–19  | Channel A Configuration Registers Bit Definitions (Register 17) | 3-26 |

| 3–20  | Channel B Configuration Registers Bit Definitions (Register 18) | 3–27 |

|       | Channel C Configuration Registers Bit Definitions (Register 19) |      |

| 3–22  | Channel D Configuration Registers Bit Definitions (Register 20) | 3–29 |

|       | Channel Status Register (Register 22)                           |      |

| 3–24  | Channel Synchronization Status Register (Register 23)           | 3–31 |

| 3–25  | Clock Tolerance Compensation Status (Register 24)               | 3–32 |

| 3–26  | Error Counter Control Register (Register 25)                    | 3-33 |

| 3–27  | Channel A Error Count (Register 26)                             | 3–33 |

| 3–28  | Channel B Error Count (Register 27)                             | 3–33 |

| 3–29  | Channel C Error Count (Register 28)                             | 3–33 |

|       | Channel D Error Count (Register 29)                             |      |

| 3–31  | PHY XS Control 1 Register (Register 40)                         | 3-33 |

| 3–32  | PHY XS Status 1 Register (Register 41)                          | 3-34 |

| 3–33  | PHY XS Speed Ability Register (Register 44)                     | 3-34 |

| 3-34  | Devices in Package Register (Register 45)                       | 3-34 |

|       | 10G PHY XS Status 2 Register (Register 48)                      |      |

| 3-36  | 10G PHY XGXS Lane Status Register (Register 424)                | 3-34 |

| 3-37  | PHY XS Register Cross Reference (Registers 432768–432776)       | 3-35 |

| 3–38  | DTE XS Control 1 Register (Register 50)                         | 3-35 |

|       | DTE XS Status 1 Register (Register 51)                          |      |

| 3-40  | DTE XS Speed Ability Register (Register 54)                     | 3-35 |

| 3–41  | Devices in Package Register (Register 55)                       | 3-35 |

| 3-42  | 10G DTE XS Status 2 Register (Register 58)                      | 3-36 |

| 3-43  | 10G DTE XGXS Lane Status Register (Register 524)                | 3-36 |

| 3-44  | DTE XS Register Cross Reference (Registers 532768–532776)       | 3-36 |

| 3-45  | Comparison of TLK3104SA and TLK3114SC Devices                   | 3-37 |

#### 1 Description

The TLK3114SC device is a flexible quad serial transceiver, delivering high-speed, bidirectional, point-to-point data transmissions to provide up to 10 Gbps of data transmission capacity. The TLK3114SC device is terminal compatible with the TLK3104SA quad serial transceiver and supports an operating range of serial data rates from 2.5 Gbps to 3.125 Gbps. The primary application of this device is to provide building blocks for developing point-to-point baseband data transmission over controlled-impedance media of approximately 50  $\Omega$ . The transmission media can be printed-circuit board (PCB) traces, copper cables, or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling into the lines.

The TLK3114SC device performs the parallel-to-serial, serial-to-parallel conversion, and clock extraction functions for a physical layer interface. The TLK3114SC device also provides a selectable 8-b/10-b encode/decode function. The serial transmitter is implemented using differential pseudoemitter controlled logic (PECL) compatible signaling called voltage mode logic (VML) that eliminates the need for external components. The serial receiver employs an equalization circuit to maximize receive capabilities.

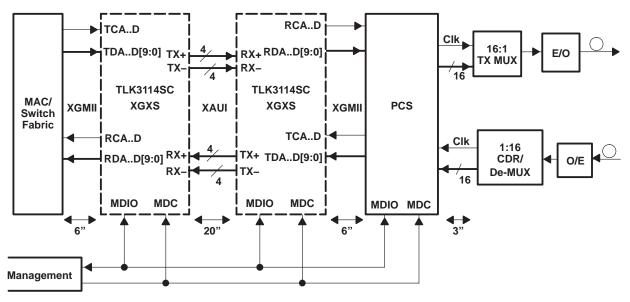

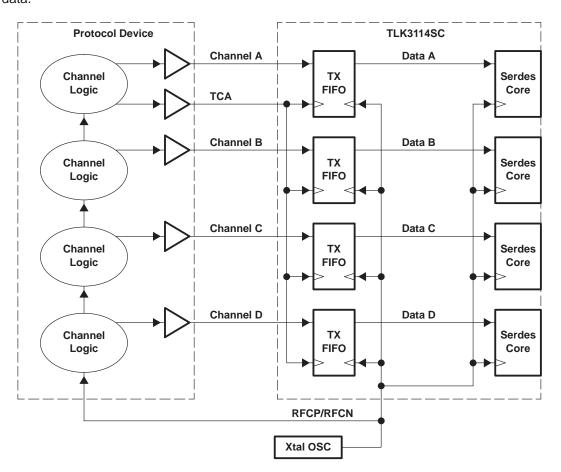

The four transceivers in the TLK3114SC device can be configured as either four separate links or synchronized together as a single data path. The TLK3114SC device supports both the 32-bit data path, 4-bit control, 10-gigabit media independent interface (XGMII), and the extended auxiliary unit interface (XAUI) specified in the IEEE 802.3ae 10-Gigabit Ethernet standard. Figure 1–1 shows an example system block diagram for the TLK3114SC device used as an XGMII extended sublayer (XGXS) device to provide an additional trace distance on PCB for data being transferred between the switching fabric and optical transceiver modules.

Figure 1-1. System Block Diagram (Chip-to-Chip Implementation)

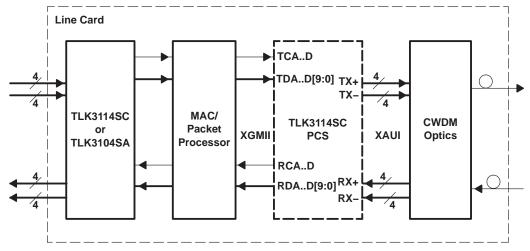

Figure 1–2 shows an example system block diagram for TLK3114SC device used to provide the 10-Gbps Ethernet physical coding sublayer (as defined in IEEE802.3ae Clause 48) to coarse wavelength division multiplexed optical transceiver.

Figure 1–2. System Block Diagram (PCS Implementation)

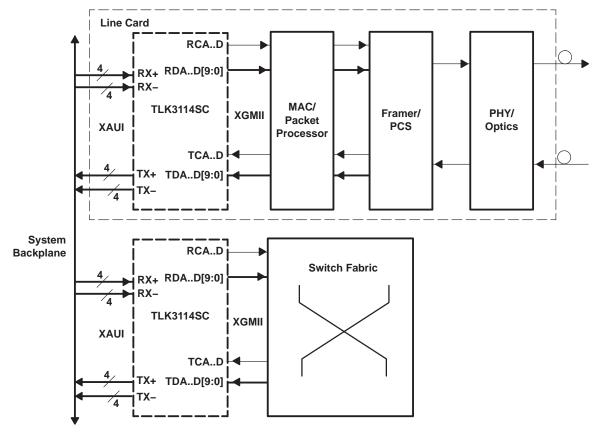

Figure 1–3 shows an example system block diagram for the TLK3114SC device used to provide the system backplane interconnect.

Figure 1-3. System Block Diagram (Backplane Interconnect Implementation)

The TLK3114SC device supports the IEEE 802.3 defined management data input/output (MDIO) interface to allow ease in configuration and status monitoring of the link.

The TLK3114SC device supports the IEEE 1149.1 defined JTAG test port for ease in board manufacturing test. It also supports a comprehensive series of built-in tests for self-test purposes including internal serial loopback and pseudorandom bit stream (PRBS) generation and verification.

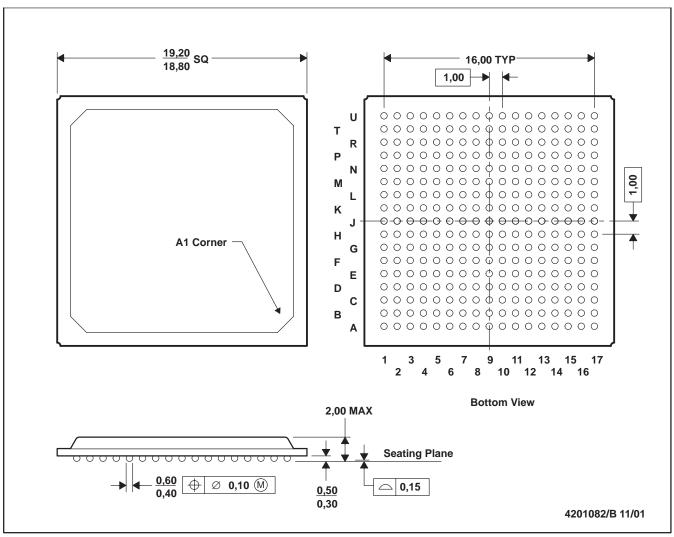

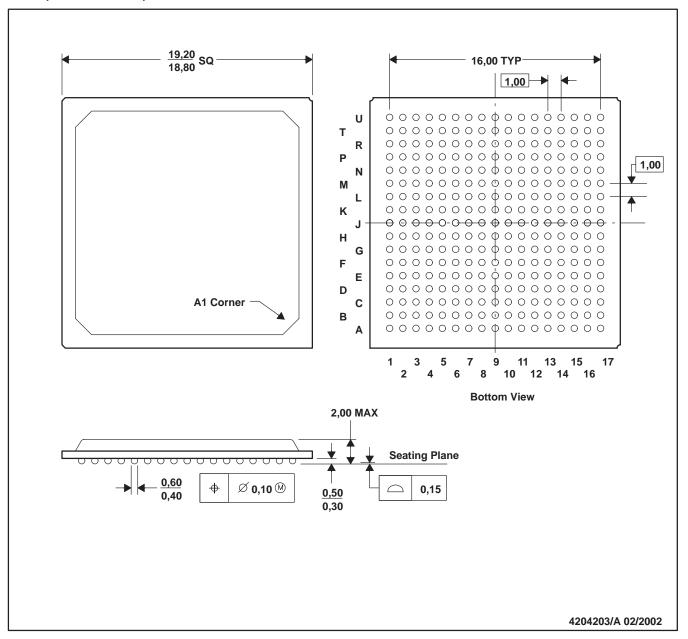

The TLK3114SC device operates with a single 2.5-V supply and dissipates less than 3 W. The device is packaged in a 19-mm  $\times$ 19-mm, 289-terminal plastic ball grid array (PBGA) package and is characterized for operation from 0°C to 70°C.

The TLK3114SC device is a member of a family of CMOS multi-gigabit transceivers, intended for use in high-speed bidirectional point-to-point data transmission systems.

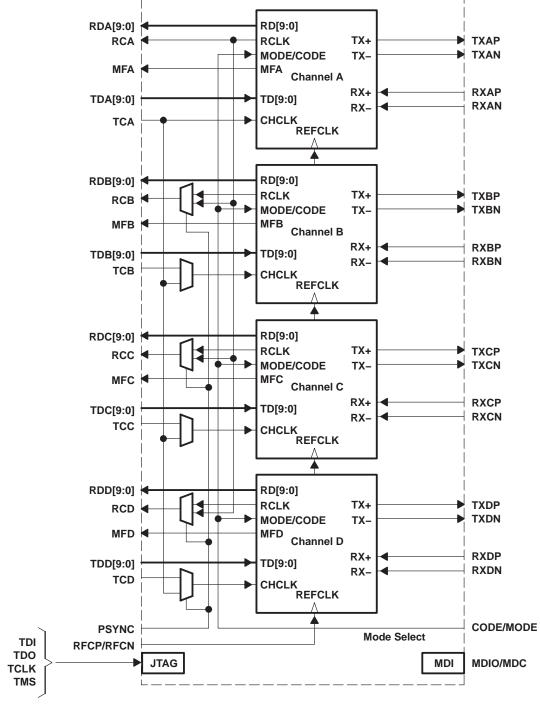

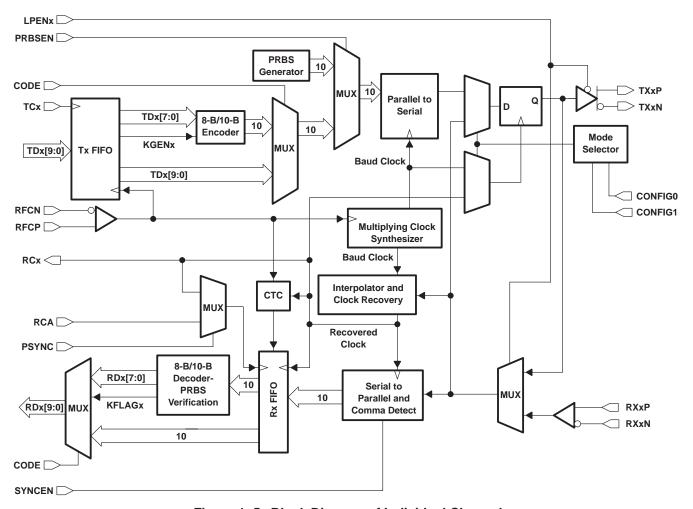

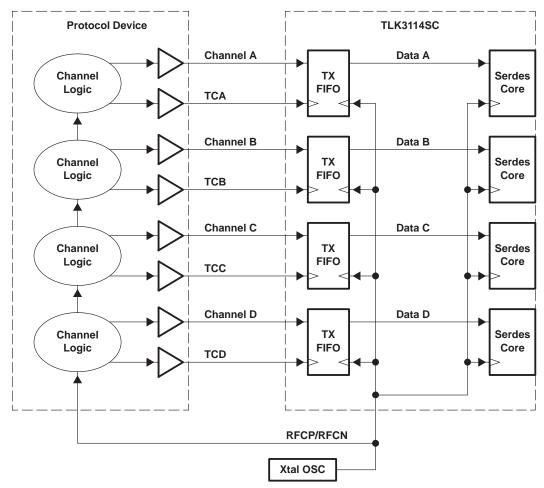

Figure 1–4 provides a high–level description of the TLK3114SC device. For a detailed diagram of the individual channels, see Figure 1–5.

Figure 1-4. TLK3114SC Block Diagram

Figure 1–5 is a more detailed block diagram description of each channel core.

Figure 1-5. Block Diagram of Individual Channel

#### 1.1 Features

- Quad 3.125 Gbps per channel transceiver providing 10-Gbps data throughput

- IEEE 802.3 10-Gbps Ethernet XGXS compliant including:

- XGMII parallel interface to MAC and XAUI serial interfaces

- Clock tolerance compensation with column add/drop

- XAUI interpacket gap /A/, /K/, and /R/ code generation and stripping

- Remote and local fault reporting on the XGMII as defined

- MDIO interface

- Selectable synchronized or independent channel operation

- Selectable transmit-only, receiver-only, transceiver, and repeater functions

- Selectable on-chip 8-b/10-b ENDEC

- On-chip receive equalization

- Receiver differential input thresholds 200 mV<sub>P-P</sub>

- On-chip  $100-\Omega$  differential receiver termination

- · No external filter capacitors required

- VML serial driver providing PECL-compatible differential signaling with no external components

- Auto-selects between HSTL or SSTL\_2 Class 1 I/O with on-chip 50-Ω series termination on outputs

- Able to operate with a single 2.5-V power supply

- On-chip PRBS generation and verification controlled from external terminal

- IEEE 1149.1 JTAG test interface

- Hot-plug protection

- Mainstream 250-nm CMOS technology

- Small-footprint, 19-mm × 19-mm, 289-ball PBGA package

#### 1.2 Ordering Information

|             | PACKAGE                           |        |

|-------------|-----------------------------------|--------|

| TA          | PLASTIC BALL GRID ARRAY<br>(PBGA) | SYMBOL |

|             | TLK3114SCGNT                      |        |

| 0°C to 70°C | TLK3114SCGPV                      |        |

|             | TLK3114SCZPV                      | ECAT   |

NOTE: For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

### **2 Terminal Descriptions**

The TLK3114SC device is available in a 289-terminal MicroStar BGA<sup>™</sup> package (GNT/GPV). The terminal layout for the GNT and GPV packages is shown in Figure 2–1. The TLK3114SC pinout is compatible with TLK3104SA board designs.

Pin Out

(Top View) В С D F F G н J ĸ 1 М N Р R т U VDDQ 17 **VDDQ GND** RDB3 **VDDQ** GND **RCB VDDQ** GND VREF GND **VDDQ** RCC GND **VDDQ** RDC3 GND 17 MFD 16 MFA MFB RDB6 TDB5 TDB8 **VDDQ** TDC5 RDC6 16 VDDQ TDB4 TDC7 TDC4 TDC2 RDC5 RDC1 VDDQ 15 15 **GND** RDB1 RDB5 RDB8 TDB2 TDB7 TDC9 RDC8 **GND** 14 RDA9 RDA8 RDB0 VDDQ TDB1 VDDQ GND VDDQ GND VDDQ TDC1 VDDQ RDD8 RDD9 14 RDA6 RDA5 RDB4 RDB7 TDB3 TDB9 TDC6 TDC3 TDC0 RDC7 RDC4 RDD5 RDD6 RDD7 13 RDA7 TDB0 TDB6 13 T-GND T-GND T-GND 12 VDDQ RDA4 RDA3 T-GND T-GND T-GND 12 RDA1 RDA0 VDDQ GND T-GND T-GND T-GND T-GND T-GND T-GND T-GND GND VDDQ RDD0 RDD1 RCD 11 RCA 11 TCA TDA9 TDA8 TDA7 TDA6 T-GND T-GND T-GND T-GND T-GND T-GND T-GND TDD6 TDD7 TDD8 TDD9 TCD 10 10 VDDQ GND TDA5 TDA4 TDA3 T-GND T-GND T-GND T-GND T-GND T-GND T-GND TDD3 TDD4 TDD5 GND VDDQ 9 TDA2 TDA1 TDA0 VDDQ GND T-GND T-GND T-GND T-GND T-GND T-GND T-GND GND VDDQ TDD0 TDD1 TDD2 8 8 VDDA GNDA **GNDA** VDD GND T-GND T-GND T-GND T-GND T-GND T-GND T-GND GND VDD GNDA GNDA VDDA 7 VDDA VDDA GND T-GND T-GND T-GND T-GND T-GND T-GND GND TXDN VDDA RXDN VDDA **RXAN** TXAN T-GND 6 6 5 VDDA RXAP VDDA TXAP GND GNDA **GNDA** GND GND GND GNDA **GNDA** GND TXDP VDDA **RXDP** VDDA 5 GNDA GNDA GNDA VDD VDD **TXBP** TXBN VDD VDD VDD TXCN TXCP VDD VDD GNDA GNDA GNDA TCLK LPENA LPENB GNDA VDDA VDDA GND RFCP GND VDDA VDDA GNDA LPENC LPEND PADR2 MDIO 3 3 TDO TMS CONFIG0 CONFIG1 **GNDA RXBP** RXBN GND RFCN GND **RXCN** RXCP GNDA TESTEN PADR4 PADR3 MDC 2 2 ENABLE **RSTN PSYNC** SYNCEN GNDA VDDA VDDA VDD PRBSEN VDD VDDA VDDA GNDA CODE PADR0 PADR1 DADR0 Α

Figure 2-1. TLK3114SC GNT/GPV-Package Terminal Diagram

The terminals are grouped in tables by functionality, such as clocks, serial side data, parallel data, etc. The terminal numbers are also listed for convenient reference.

Table 2-1. Clock Terminals

| TERM              | IINAL             | XGMII  | TVDE                                                                                                               | DECORPORA                                                                                                                                                                                                                                                                                  |

|-------------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NUMBER            | NAME   | TYPE                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                                                |

| RCA A11           | A11               | RX CLK | HSTL/SSTL_2 output                                                                                                 | Receive data clock, channel A. The data on RDA(0–9) is output on the rising and falling edges of RCA. When PSYNC is high, RCA acts as the receive clock for all channels.                                                                                                                  |

|                   |                   |        |                                                                                                                    | This terminal has internal series termination to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                            |

| RCB<br>RCC        | F17<br>M17        | N/A    | HSTL/SSTL_2                                                                                                        | Receive data clock, channels B–D. When PSYNC is low, the data on RDx(0–9) is output on the rising and falling edges of the receive clocks. When PSYNC is high, these terminals are duplicates of RCA.                                                                                      |

| RCD U11           |                   | output | These terminals have internal series termination to provide direct connection to a 50- $\Omega$ transmission line. |                                                                                                                                                                                                                                                                                            |

| RFCP<br>RFCN      | J3<br>J2          | N/A    | PECL<br>compatible or<br>LVDS input                                                                                | Differential reference input clock. This differential pair accepts LVDS- or PECL-compatible signals. When interfacing with 3.3-V PECL, ac-coupling is required. An on-chip $100-\Omega$ termination resistor is placed differentially between the terminals. Internal biasing is provided. |

| TCA               | A10               | TX_CLK | HSTL/SSTL_2<br>input                                                                                               | Transmit data clock, channel A. The data on TDA(0–9) is latched on the rising and falling edges of TCA. When PSYNC is high, TCA acts as the transmit clock for all channels.                                                                                                               |

| TCB<br>TCC<br>TCD | F16<br>M16<br>U10 | N/A    | HSTL/SSTL_2<br>input                                                                                               | Transmit data clock, channels B–D. When PSYNC is low, the data on TDx(0–9) is latched on the rising and falling edges of the transmit clocks. When PSYNC is high, these terminals are undefined.                                                                                           |

Table 2-2. Serial Side Data Terminals

| TERMINAL                                             |                                      | TVDE                   | DECODIDE                                                                                                                                                                                                                                                                             |  |

|------------------------------------------------------|--------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                 | NUMBER                               | TYPE                   | DESCRIPTION                                                                                                                                                                                                                                                                          |  |

| RXAP, RXAN<br>RXBP, RXBN<br>RXCP, RXCN<br>RXDP, RXDN | B5, B6<br>F2, G2<br>M2, L2<br>T5, T6 | PECL-compatible input  | Receive differential pairs, channels A–D. High-speed serial inputs with on-chip $100-\Omega$ differential termination. Each input pair is terminated differentially across an on-chip $100-\Omega$ resistor (see Figure 4–9 and Figure 4–10). These terminals have internal biasing. |  |

| TXAP, TXAN<br>TXBP, TXBN<br>TXCP, TXCN<br>TXDP, TXDN | D5, D6<br>F4, G4<br>M4, L4<br>P5, P6 | PECL-compatible output | Transmit differential pairs, channels A–D. High-speed serial outputs.                                                                                                                                                                                                                |  |

Table 2–3. Parallel Data Terminals

| TER                  | MINAL                                           | XGMII                 |                        |                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|-------------------------------------------------|-----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NUMBER                                          | NAME                  | TYPE                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

| RDA[0:7]             | C11, B11,<br>E12, D12,                          | RXD[0:7]              | HSTL/SST               | Receive data terminals, channel A. Parallel data on this bus is valid on the rising and falling edges of RCA.                                                                                                                                                                                                                                                         |

| NDA[0.1]             | C12, C13,<br>B13, A13                           | NXD[0.7]              | L_2 output             | These terminals have internal series termination to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                    |

| RDA8                 | B14                                             | RXC0                  | HSTL/SST<br>L_2 output | Receive data/K-flag, channel A. When CODE is low, this terminal is the ninth bit of a received 8-b/10-b encoded byte. When CODE is high, this terminal acts as the K-character flag. When this terminal is high, it indicates the data on RDA(0–7) is a valid K-character. Data on this terminal is valid on the rising and falling edges of RCA.                     |

|                      |                                                 |                       |                        | This terminals has internal series termination to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                      |

| RDA9                 | A14                                             | N/A                   | HSTL/SST<br>L_2 output | Receive data terminal/error detect, channel A. When CODE is low, this terminal is the tenth bit of a 8-b/10-b encoded byte. When CODE is high, this terminal goes high to signify the occurrence of either a disparity error or an invalid code word during the decoding of the received data. Data on this terminal is valid on the rising and falling edges of RCA. |

|                      |                                                 |                       |                        | This terminal has internal series termination to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                       |

| RDB[0:7]             | C14, C15,<br>C16, C17,<br>D13, D15,<br>D16, E13 | RXD[8:15]             | HSTL/SST<br>L_2 output | Receive data terminals, channels B–D. When PSYNC is low, parallel data on these                                                                                                                                                                                                                                                                                       |

| RDC[0:7]             | R14, R15,<br>R16, R17,<br>P13, P15,<br>P16, N13 | RXD[16:23]            |                        | buses is valid on the rising and falling edges of the recovered data clock (RCB, RCC, or RCD). When PSYNC is high, data on each bus is valid on the rising and falling edges of RCA. These terminals are series terminated to provide direct connection to a $50-\Omega$                                                                                              |

| RDD[0:7]             | R11, T11,<br>N12, P12,<br>R12, R13,<br>T13, U13 | RXD[24:31]            |                        | transmission line.                                                                                                                                                                                                                                                                                                                                                    |

| RDB8                 | E15                                             | RXC1                  |                        | Receive data/K-flag, channels B–D. When PSYNC is low, data on these terminals is valid on the rising and falling edges of the recovered clock (RCB, RCC, or RCD). When PSYNC is high, data on these terminals is valid on the rising and falling edges of RCA.                                                                                                        |

| RDC8<br>RDD8         | N15<br>T14                                      | RXC2<br>RXC3          | C2 HSTL/SST            | When CODE is low, these terminals are the ninth bit of a received 8-b/10-b encoded byte. When CODE is high, these terminals act as the K-character flag. When asserted high, this indicates the data on RDx[0:7] is a valid K-character.                                                                                                                              |

|                      |                                                 |                       |                        | These terminals are series terminated to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                               |

| RDB9<br>RDC9<br>RDD9 | F40                                             | E16<br>N16 N/A<br>U14 | HSTL/SST<br>L_2 output | Receive data terminal/error detect, channels B–D. When PSYNC is low, data on these terminals is valid on the rising and falling edges of recovered channel clock (RCB, RCC, RCD). When PSYNC is high, data on these terminals is valid on the rising and falling edges of RCA.                                                                                        |

|                      | N16                                             |                       |                        | When CODE is low, these terminals are the tenth bit of a 8-b/10-b encoded byte. When CODE is high, these terminals provide an error detection flag. The error detect is asserted high to signify the occurrence of either a disparity error or an invalid code word during the decoding of the received data.                                                         |

|                      |                                                 |                       |                        | These terminals have internal series termination to provide direct connection to a 50- $\Omega$ transmission line.                                                                                                                                                                                                                                                    |

Table 2-3. Parallel Data Terminals (Continued)

| TERMINAL             |                                                 | XGMII        | XGMII                 | DECORPORA                                                                                                                                                                                                                                                                                                 |  |

|----------------------|-------------------------------------------------|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                 | NUMBER                                          | NAME         | TYPE                  | DESCRIPTION                                                                                                                                                                                                                                                                                               |  |

| TDA[0:7]             | C8, B8, A8,<br>E9, D9, C9,<br>E10, D10          | TXD[0:7]     | HSTL/SST<br>L_2 input | Transmit data terminals, channel A. Parallel data on this bus is clocked on the rising and falling edges of TCA.                                                                                                                                                                                          |  |

| TDA8                 | C10                                             | TXC0         | HSTL/SST<br>L_2 input | Transmit data/KGEN, channel A. When CODE is low, this terminal is the ninth bit of an 8-b/10-b encoded byte to be transmitted. When CODE is high, this terminal acts as the K-character generator indicator. When this terminal is high, it causes the data on TDA(0–7) to be encoded into a K-character. |  |

| TDA9                 | B10                                             | N/A          | HSTL/SST<br>L_2 input | Transmit data terminal, channel A. When CODE is low, this terminal is the tenth bit of an 8-b/10-b encoded byte. When CODE is high, this terminal is ignored.                                                                                                                                             |  |

| TDB[0:7]             | F13, F14,<br>F15, G13,<br>G15, G16,<br>H13, H15 | TXD[8:15]    | HSTL/SST L_2 input    |                                                                                                                                                                                                                                                                                                           |  |

| TDC[0:7]             | M13, M14,<br>M15, L13,<br>L15, L16, K13,<br>K15 | TXD[16:23]   |                       | ansmit data terminals, channels B–D. When PSYNC is low, parallel data on this is clocked on the rising and falling edges of the transmit channel clock (TCB, CC, TCD). When PSYNC is high, data on these buses is clocked on the rising and lling edges of TCA.                                           |  |

| TDD[0:7]             | R8, T8, U8,<br>N9, P9, R9,<br>N10, P10          | TXD[24:31]   |                       |                                                                                                                                                                                                                                                                                                           |  |

| TDB8<br>TDC8         | H16<br>K16                                      | TXC1<br>TXC2 | HSTL/SST              | Transmit data/KGEN, channels B–D. When PSYNC is low, data on these terminals is clocked on the rising and falling edges of the transmit channel clock (TCB, TCC, or TCD). When PSYNC is high, data on these terminals is clocked on the rising and falling edges of TCA.                                  |  |

| TDD8                 | R10                                             | TXC3         | L_2 input             | When CODE is low, these terminals are the ninth bit of an 8-b/10-b encoded byte to be transmitted. When CODE is high, these terminals act as the K-character generator indicator. When driven high, these terminals cause the data on $TDx(0-7)$ to be encoded into a K-character.                        |  |

| TDB9<br>TDC9<br>TDD9 | J13<br>J15<br>T10                               | N/A          | HSTL/SST<br>L_2 input | Transmit data terminal, channels B–D. When PSYNC is low, data on these terminals is clocked on the rising and falling edges of the transmit channel clock (TCB, TCC, TCD). When PSYNC is high, data on these terminals is clocked on the rising and falling edges of TCA.                                 |  |

| פטטו                 | 110                                             |              |                       | When CODE is low, these terminals are the tenth bit of an 8-b/10-b encoded byte. When CODE is high, these terminals are ignored.                                                                                                                                                                          |  |

Table 2-4. JTAG Test Port Interface

| TERM | TERMINAL |                          | PECCEIPTION                                                                                                                                                                                    |  |

|------|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NUMBER   | TYPE                     | DESCRIPTION                                                                                                                                                                                    |  |

| TCLK | А3       | LVTTL input              | JTAG clock. TCLK clocks state information and test data into and out of the device during the operation of the test port.                                                                      |  |

| TDI  | В3       | LVTTL input <sup>†</sup> | JTAG input data. TDI serially shifts test data and test instructions into the device during the operation of the test port.                                                                    |  |

| TDO  | A2       | LVTTL output             | JTAG output data. TDO serially shifts test data and test instructions out of the device during operation of the test port. When the JTAG port is not in use, TDO is in a high-impedance state. |  |

| TMS  | B2       | LVTTL input <sup>†</sup> | JTAG mode select. TMS controls the state of the internal test-port controller.                                                                                                                 |  |

<sup>†</sup> With an internal pullup resistor

Table 2-5. Management Data Interface

| TERM      | INAL                  | TYPE        | DESCRIPTION                                                                                                                                               |  |

|-----------|-----------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NUMBER                | TYPE        |                                                                                                                                                           |  |

| DADR0     | U1                    | LVTTL input | Management MMD address. DADR0 is the externally set device address, which configures PHY XS or DTE XS according to Table 3–11.                            |  |

| MDC       | U2                    | LVTTL input | Management data clock. MDC is the clock reference for the transfer of management data to and from the protocol device.                                    |  |

| MDIO      | U3                    | LVTTL I/O   | Management data I/O. MDIO is the bidirectional serial data path for the transfer of management data to and from the protocol device.                      |  |

| PADR(0-4) | R1, T1,<br>T3, T2, R2 | LVTTL input | Management PHY address. Device address PADR(0-4) is the externally set physical address given to this device used to distinguish one device from another. |  |

Table 2-6. Miscellaneous Terminals

| TERMINAL           |                       |                          |                                                                                                                                                                                                                                                                                                                                                                             |  |

|--------------------|-----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME               | NUMBER                | TYPE                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |

| CODE               | P1                    | LVTTL input†             | Encode enable. When CODE is high, the 8-b/10-b encoder and decoder is enabled.                                                                                                                                                                                                                                                                                              |  |

| CONFIG0<br>CONFIG1 | C2, D2                | LVTTL input <sup>‡</sup> | Configuration terminals. These terminals put the device under one of the three operation modes:  00 = Transceiver mode 01 = Transmit-only mode 10 = Receive-only mode 11 = Repeater mode                                                                                                                                                                                    |  |

| ENABLE             | A1                    | LVTTL input†             | Standby enable. When this terminal is held low, the device is in a low-power state. When high, the device operates normally.                                                                                                                                                                                                                                                |  |

| LPEN(A-D)          | C3, D3,<br>P3, R3     | LVTTL input‡             | Internal loop enable, channels A–D. When high, the serial output for each channel is internally looped back to its serial input.                                                                                                                                                                                                                                            |  |

| MF(A-D)            | A16, B16,<br>T16, U16 | LVTTL output             | Multifunction outputs, channels A–D. The functions of these terminals are enabled via the MDIO. Currently defined functions are:  Terminal indicates 1 for HSTL, 0 for SSTL_2 signaling (default),  LOS (loss of signal) for each channel,  COMMA_DET (K28.5 character detected) for each channel, and  PRBS_STATUS (pseudorandom bit stream test status) for each channel. |  |

| PRBSEN             | J1                    | LVTTL input <sup>‡</sup> | PRBS enable. When this terminal is asserted high, the PRBS generator and comparator circuits are inserted into the transmit and receive data paths on all channels. PRBS_PASS is indicated on the MFx terminals once they are enabled using MDIO.                                                                                                                           |  |

| PSYNC              | C1                    | LVTTL input‡             | Channel synchronization enable. When PSYNC is high, all transmit data is latched on the rising and falling edges of TCA and all receive data is valid on the rising and falling edges of RCA.                                                                                                                                                                               |  |

| RSTN               | B1                    | LVTTL input†             | Chip reset (FIFO clear). Pulling this terminal low recenters the transmit skew buffers, receive channel synchronization FIFOs, and resets MDIO flags.                                                                                                                                                                                                                       |  |

| SYNCEN             | D1                    | LVTTL input†             | Comma detect enable. When this terminal is high, comma detection and byte alignment for all channels are enabled.                                                                                                                                                                                                                                                           |  |

| TESTEN             | P2                    | LVTTL input <sup>‡</sup> | Test mode enable. This terminal is used for manufacturing test. This terminal must be left unconnected or tied low.                                                                                                                                                                                                                                                         |  |

<sup>†</sup> With an internal pullup resistor ‡ With an internal pulldown resistor

Table 2–7. Voltage Supply and Reference Terminals

| TERMINAL         |                                                                                                                                                                   | TVDE                                                                          | DECORPORTION                                                                                                 |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| NAME             | NUMBER                                                                                                                                                            | TYPE                                                                          | DESCRIPTION                                                                                                  |  |

| GND              | B9, B12, B15, B17, E5, E6,<br>E7, E8, E11, E14, E17, H2,<br>H3, H5, H14, H17, J5, K2,<br>K3, K5, K14, K17, N5, N6,<br>N7, N8, N11, N14, N17, T9,<br>T12, T15, T17 | Ground Digital logic ground. Supply reference for core logic and SSTL_2 Class |                                                                                                              |  |

| GNDA             | A4, B4, B7, C4, C7, E1, E2,<br>E3, F5, G5, L5, M5, N1, N2,<br>N3, R4, R7, T4, T7, U4                                                                              | Ground                                                                        | Analog ground. Supply reference for analog circuitry.                                                        |  |

| T-GND            | F6–F12, G6–G12, H6–H12,<br>J6–J12, K6–K12, L6–L12,<br>M6–M12                                                                                                      | Ground                                                                        | Thermal grounds. Electrically connected to GND, these terminals provide a thermal path for heat dissipation. |  |

| V <sub>DD</sub>  | D4, D7, E4, H1, H4, J4, K1,<br>K4, N4, P4, P7                                                                                                                     | Supply                                                                        | Core supply (2.5 V). Digital logic power. Provides power for all digital circuitry.                          |  |

| V <sub>DDA</sub> | A5, A6, A7, C5, C6, F1, F3,<br>G1, G3, L1, L3, M1, M3,<br>R5, R6, U5, U6, U7                                                                                      | Supply                                                                        | Analog voltage supply (2.5 V). Provides power for all analog circuitry.                                      |  |

| V <sub>DDQ</sub> | A9, A12, A15, A17, D8,<br>D11, D14, D17, G14, G17,<br>J14, J16, L14, L17, P8,<br>P11, P14, P17, U9, U12,<br>U15, U17                                              | Supply                                                                        | HSTL/SSTL_2 Class 1 supply voltage. Nominally 1.5 V for HSTL or 2.5 V for SSTL_2 Class 1.                    |  |

| VREF             | J17                                                                                                                                                               | Input                                                                         | Input voltage reference for HSTL/SSTL_2 Class 1 I/O                                                          |  |

#### 3 Detailed Description

The TLK3114SC device has four operational interface modes controlled by the states of terminals CODE and PSYNC. These operational interface modes are listed in Table 3–1.

CODE PSYNC DESCRIPTION

Low Low Four independent serializer/deserializers (serdes)

Low High Four synchronized serdes

High Low Four independent transceivers with on-chip 8-b/10-b encode/decode

High High 10-gigabit ethernet XGMII extended sublayer (XGXS) transceiver

Table 3–1. Operational Interface Modes

#### 3.1 Serdes Modes

When CODE is deasserted, the TLK3114SC device performs serialization and deserialization of encoded data across four ten-bit interfaces (TBI) similar to that done in fibre channel and 802.3z gigabit ethernet serdes devices. The channels can be synchronized to allow use of one transmit data clock and one receive data clock.

#### 3.2 10-Gbps Ethernet Transceiver Modes

When CODE and PSYNC are asserted, the TLK3114SC device supports the 32-bit data path, 4-bit control, 10-gigabit media independent interface (XGMII), and full encoding scheme specified in the IEEE 802.3ae 10-Gigabit Ethernet standard. In these modes, the TLK3114SC device performs the serialization/deserialization and channel synchronization function of an extended auxiliary unit interface (XAUI), also specified in the IEEE 802.3ae 10-Gigabit Ethernet standard.

#### 3.3 Parallel Interface Clocking

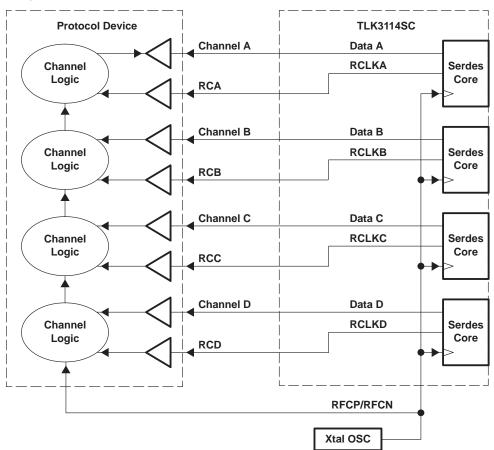

Two clocking choices are selectable via the PSYNC terminal detailed in Table 3–2. Under channel sync mode (PSYNC is high), TCA is used as the transmit data clock for all four channels. Under independent channel mode (PSYNC is low), each channel uses its own transmit data clock (TCA–TCD) to latch data into the TLK3114SC device. A data FIFO is placed in the transmit data path to resolve any phase difference between the transmit data clocks and differential reference clock, RFCP/N.

Table 3-2. Parallel Interface Clocking Modes

|                                                                                    | PSYNC | PARALLEL INTERFACE CLOCKING OPERATION                                          |  |  |

|------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------|--|--|

| Low Independent channel mode. TC[A-D]/RC[A-D] clock in/out each individual channel |       | Independent channel mode. TC[A-D]/RC[A-D] clock in/out each individual channel |  |  |

|                                                                                    | High  | Channel sync mode. TCA/RCA clock in/out all channels of data                   |  |  |

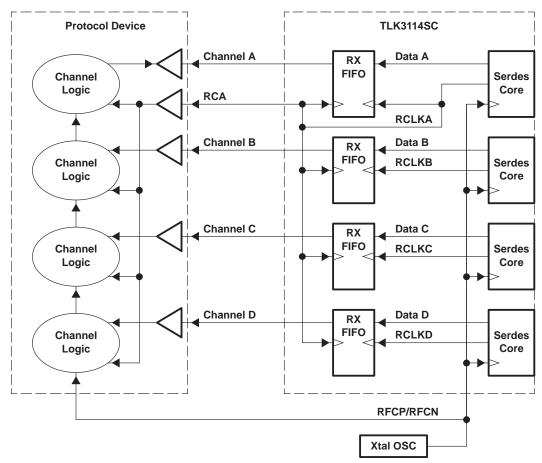

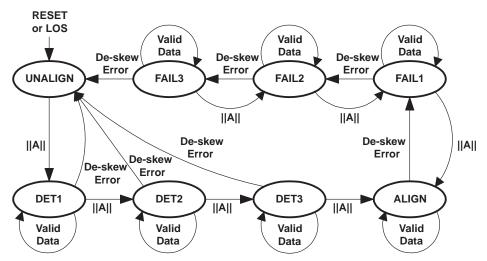

On the receive data path, in independent channel mode, the data for each channel is output referenced to each channel's extracted receive clock. In channel sync mode, the data on all channels are synchronized and output referenced to the extracted receive clock for channel A, RCA. A FIFO is enabled in the parallel receive data path on each channel to compensate for channel skew and clock phase tolerance differences between the received clocks for each channel and the receive output clock, RCA. This FIFO has a total depth of 11 bytes.

#### 3.4 Parallel Interface Data

Two data mode choices are selectable via the CODE terminal detailed in Table 3–3. In serdes mode, the transmit data bus for each channel accepts 10-bit wide 8-b/10-b encoded data at the TDx[0:9] terminals. Data is latched on the rising and falling edge of the transmit data clock. The 8-b/10-b encoded data is then phase aligned to the reference clock (RFCP/RFCN), serialized, then transmitted sequentially beginning with bit 0 (TDx0) over the differential high-speed serial transmit terminals.

In serdes mode, the receive data bus for each channel outputs 10-bit wide 8-b/10-b encoded data on RDx[0:9]. The 8-b/10-b encoded data input to the differential high-speed serial receive terminals is deserialized with the first bit (bit 0) output on RDx0 and the last bit (bit 9) output on RDx9. Data is output relative to both the rising and falling edges of the receive clock.

Table 3-3. Parallel Data Modes

| CODE | PARALLEL INTERFACE DATA OPERATION                                                                                                                                                                                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low  | Serdes mode. On-chip 8-b/10-b encoder/decoder is disabled. Data on TDx[0:9] and RDx[0:9] is treated as 8-b/10-b encoded data.                                                                                                                                                                                    |

| High | Transceiver mode. Enables 8-b/10-b encode/decode for each channel. Data TDx[0:7] and RDx[0:7] are treated as uncoded data. TDx8 is used as the K-character generator control. RDx8 is the K-character indicator to the host device. Data on TDx9 is ignored. RDx9 goes high on either a disparity or code error. |

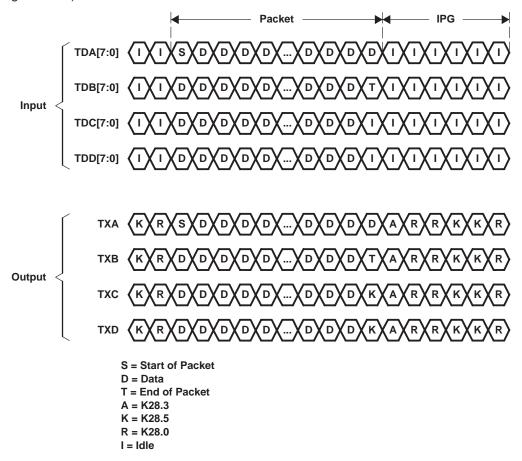

In transceiver mode, the transmit data bus for each channel accepts 8-bit wide parallel data at the TDx[0:7] terminals. Data is sampled on the rising and falling edges of the transmit clock as shown in Figure 3–1. The data is first aligned to the reference clock (RFCP/RFCN), then 8-b/10-b encoded and passed to the serializer. The generation of K-characters on each channel is controlled by TDx8 (KGEN). When KGEN is asserted along with the 8 bits of data TDx[0:7], the appropriate 8-b/10-b K-character is transmitted.

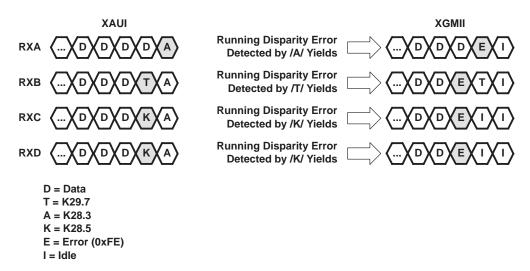

In transceiver mode, the receive data bus for each channel outputs an 8-bit wide parallel data on RDx[0:7]. Reception of K-characters is reported on RDx8 (KFLAG). When KFLAG is asserted, the 8 bits of data on RDx[0:7] must be interpreted as a K-character. If an error is uncovered in decoding the data, KFLAG and RDx9 (RX\_ER) are asserted and 0xFE is placed on the receive data bus for that channel.

#### 3.5 Transmit Data Bus Timing

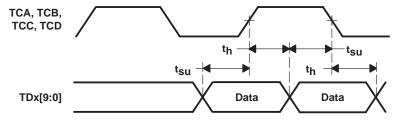

For each channel, the transmitter portion of the TLK3114SC device latches the data on transmit data bus TDx[0:9] on both the rising and falling edges of the transmit data clock, as shown in Figure 3–1. Depending on the state of the PSYNC terminal, the transmit data clock is either TCA (channel sync mode) or the individual transmit channel clocks, TCA–TCD (independent channel mode). When in the channel sync mode, signals on TCB, TCC, and TCD are ignored.

Figure 3-1. Transmit Interface Timing

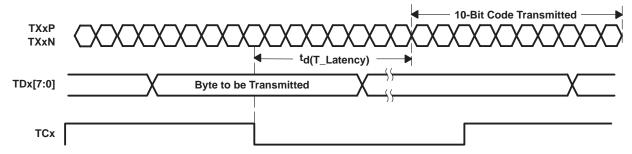

#### 3.6 Transmission Latency

For each channel, the data transmission latency of the TLK3114SC device is defined as the delay from the rising or falling edge of the selected transmit clock when valid data is on the transmit data terminals to the serial transmission of bit 0, as shown in Figure 3–2. The minimum latency (T<sub>LATENCY</sub>) is 71 bit times; the maximum is 120 bit times. There are approximately 20 bit times required for the 8-b/10-b encoder.

Figure 3-2. Transmitter Latency

#### 3.7 Channel Clock to Serial Transmit Clock Synchronization

The TLK3114SC device requires an external differential reference clock, RFCP/N, for the on-chip phase-locked loop (PLL) and the clock/data recovery loop. To compensate for arbitrary clock phase tolerance differences between the reference clock and the data aligned to the transmit clock, a small FIFO in the parallel transmit data path on each channel is employed. This FIFO has a depth of four bytes.

The reference clock and the transmit data clock(s) are assumed to be from a common source and only phase misaligned due to different path delays as shown in Figure 3–3 and Figure 3–4. The reference clock is multiplied in frequency 10x to produce the internal serialization clock. The internal serialization clock is used to clock out the serial transmit data.

Figure 3-3. Transmit and Reference Clock Relationship (Channel Sync Mode)

Figure 3-4. Transmit and Reference Clock Relationship (Independent Channel Mode)

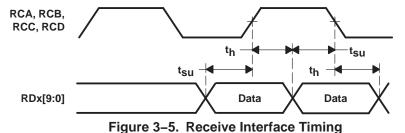

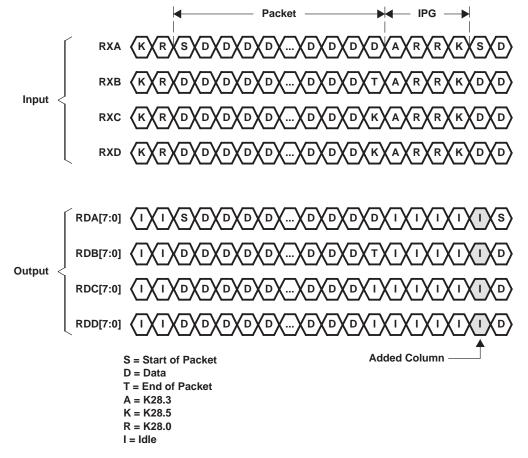

#### 3.8 Receive Data Bus Timing

For each channel, the receiver portion of the TLK3114SC device outputs the recovered deserialized data on the receive data bus TDx[0:9] on both the rising and falling edges of the receive data clock, as shown in Figure 3–5. Depending on the state of PSYNC terminal the receive data clock is either RCA (channel sync mode) or the individual receive channel clocks, RCA–RCD (independent channel mode). Terminals RCB, RCC, and RCD are also strobed to match RCA in channel sync mode.

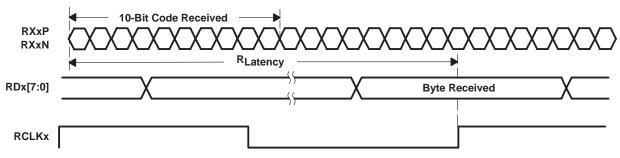

#### 3.9 Data Reception Latency

For each channel, the serial-to-parallel data latency is the time from when the first bit arrives at the receiver input until it is output in the aligned parallel word with RDx0 received as first bit, as shown in Figure 3–6. The minimum latency (R<sub>LATENCY</sub>) is 84 bit times; the maximum is 225 bit times. The 8-b/10-b encoder, channel de-skew, and CTC all contribute to the maximum latency.

Figure 3-6. Receiver Latency

#### 3.10 Auto Detectable HSTL/SSTL\_2 Class 1 I/O

The transmit and receive data buses of the TLK3114SC device are compatible with both high-speed transfer logic (HSTL) supply and stub series terminated logic 2 (SSTL\_2) Class 1 buffers. The TLK3114SC device determines which buffer technology to use by sensing the voltage level on the  $V_{DDQ}$  supply terminals at power up. If the voltage on the  $V_{DDQ}$  supply is between 2.3 V and 2.7 V, the TLK3114SC device provides the necessary drive current to meet SSTL\_2 Class 1 requirements. If the voltage on the  $V_{DDQ}$  supply is between 1.4 V and 2 V, the TLK3114SC device provides HSTL compatible signaling. During normal operation, the voltage level on the  $V_{DDQ}$  terminals must not change.

All HSTL/SSTL\_2 Class 1 outputs are series terminated to provide direct connection to a  $50-\Omega$  transmission line signaling environment (see Figure 4–10 and Figure 4–11).

#### 3.11 8-b/10-b Encoder

All true serial interfaces require a method of encoding to ensure sufficient transition density for the receiving PLL to acquire and maintain lock. The encoding scheme also maintains the signal dc balance by keeping the number of 1s and 0s the same, which allows for ac-coupled data transmission. The TLK3114SC device uses the 8-b/10-b encoding algorithm that is used by fibre channel and gigabit ethernet. This provides good transition density for clock recovery and improves error checking. The 8-b/10-b encoder/decoder function is enabled for all four channels by the assertion of the CODE terminal. When enabled, the TLK3114SC device internally encodes and decodes the data such that the user reads and writes actual 8-bit data on each channel.

When enabled, the 8-b/10-b encoder converts 8-bit wide data to a 10-bit wide encoded data character to improve its transition density. This transmission code includes D-characters, used for transmitting data, and K-characters, used for transmitting protocol information. Each K- or D-character code word can also have both a positive and a negative disparity version. The disparity of a code word is selected by the encoder to balance the running disparity of the serialized data stream.

The generation of K-characters to be transmitted on each channel is controlled by TDx8 (KGEN). When KGEN is asserted along with the 8 bits of data TDx[0:7], an 8-b/10-b K-character is transmitted. Similarly, reception of K-characters is reported by RDx8 (KFLAG). When KFLAG is asserted, the 8 bits of data on RDx[0:7] must be interpreted as a K-character. The TLK3114SC device transmits and receives all 12 valid K-characters defined in Table 3–4. Table 3–5 provides additional transmit data control coding and descriptions that have been proposed for 10 gigabits per second ethernet. Data patterns put on TDx[0:7], other than those defined in Table 3–4 when TDx8 is asserted, result in an invalid K-character being transmitted, which results in a code error at the receiver.

Table 3-4. Valid K-Codes

|                    |              | DATA BUS                  | ENCODED K-CODE                   |                                  |                                |

|--------------------|--------------|---------------------------|----------------------------------|----------------------------------|--------------------------------|

| K-CODE             | TDX8 OR RDX8 | (RDX[7:0] OR<br>TDX[7:0]) | NEGATIVE<br>RUNNING<br>DISPARITY | POSITIVE<br>RUNNING<br>DISPARITY | K-CODE DESCRIPTION             |

| 00 through FF      | 0            | ddddddd                   | ddddddddd                        | ddddddddd                        | Normal data                    |