#### www.ti.com

# **Dual XAUI Transceiver**

#### **FEATURES**

- Eight Channel 3.125 Gbps Transceiver

- Contains Two Complete IEEE P802.3ae-2002 10 Gbps Ethernet XGXS<sup>(1)</sup> (XAUI) Compliant Cores

- XAUI (Serial side) Channel Redundancy Mode Support: Fast Switching from Primary to Secondary XAUI/Channel with Provisionable Error Character or Local Fault Code Insertion at Switch Time

- XGMII (Parallel side) Channel Redundancy Mode Support: Fast Switching from Primary to Secondary XGMII/Channel with Provisionable Error Character or Local Fault Code Insertion at Switch Time

- Serial Side Transmit Pre-emphasis and Receive Adaptive Equalization to Allow Extended Backplane Reach

- Selectable Full Duplex Serial Side Retimer Mode

- Full Datapath Loopback Capability (Serial/Parallel Side)

- Support PRBS 2<sup>7</sup>-1 and 2<sup>23</sup>-1 Generate/Verify.

Support Standard Defined CJPAT, CRPAT,

High Frequency, Low Frequency, and Mixed

Frequency Testing

- XGMII: HSTL Class 1 I/O with On-chip 50- $\Omega$  Termination on Inputs/Outputs (1.5-V Power Supply)

- XGMII: Support Receive (Output)

Aligned/Centered Timing Modes, and Transmit (Input) Source Centered Mode

- Supports Jumbo Packet (9600 byte maximum)

Operation

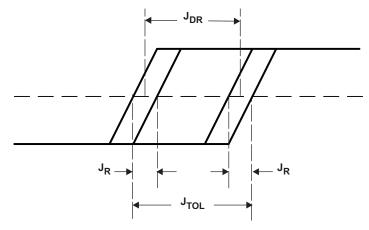

- Align Character Skew Support of 30 bit Times at Chip Pins

- Dual MDIO: IEEE 802.3ae Clause 45 Compliant Management Data Input / Output Interface (1.2-V and 2.5-V I/O)

- 1.2-V Core, 1.5-V HSTL I/O Supply, and 2.5-V LVCMOS and Bias Supply

- JTAG: IEEE 1149.1 Test Interface

- ±200 ppm Clock Tolerance in XAUI Transmit and Receive Datapaths

- Diagnostic LED Output Interface

- 130-nm CMOS Technology

- Package: PBGA 484, 23×23mm, 484 ball, 1mm Pitch

- 2.42 W Typical Power Dissipation (Dual XAUI Mode, Input HSTL Termination Disabled)

- Commercial Ambient Operating Temp (0°C to 70°C)

- (1) XGMII Extender Sublayer

#### **APPLICATIONS**

• 10 Gigabit Ethernet Servers and Routers

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **DESCRIPTION**

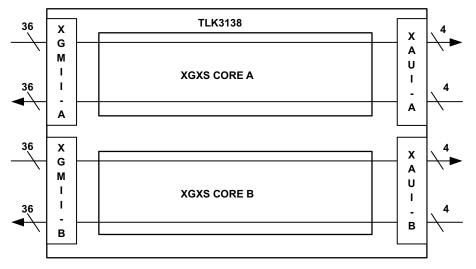

The TLK3138 is an eight channel serial transceiver. It is compliant with the 10Gbps Ethernet XAUI specification. The TLK3138 provides 10 Gbps high-speed bi-directional point-to-point data transmission. The primary application of this device is in backplanes and front panel connections requiring dual/redundant 10Gbps connections over controlled impedance media of approximately  $50\Omega$ . The transmission media can be printed circuit board (PCB) traces, copper cables or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling into the lines.

The TLK3138 performs the parallel-to-serial, serial-to-parallel conversion, and clock extraction functions for a physical layer interface. The TLK3138 provides two complete XGXS/PCS functions defined in Clause 47/48 of the IEEE P802.3ae 10Gbps Ethernet standard. The serial transmitter is implemented using differential Current Mode Logic (CML) with integrated termination resistors.

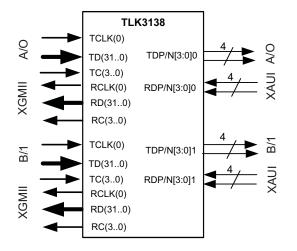

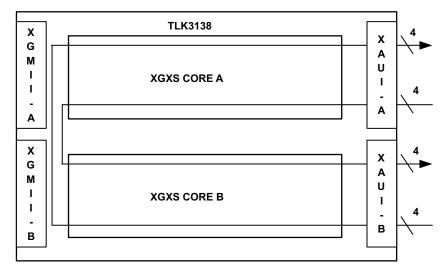

The TLK3138 can be configured as a dual XAUI transceiver. TLK3138 supports two 32-bit data path, 4-bit control, 10 Gigabit Media Independent Interfaces (XGMII) to the protocol device(s). Figure 1 shows an example system block diagram for TLK3138 used to provide the 10Gbps Ethernet Physical Coding Sublayer to Coarse Wave-length Division Multiplexed optical transceiver or parallel optics.

Figure 1. System Block Diagram - PCS

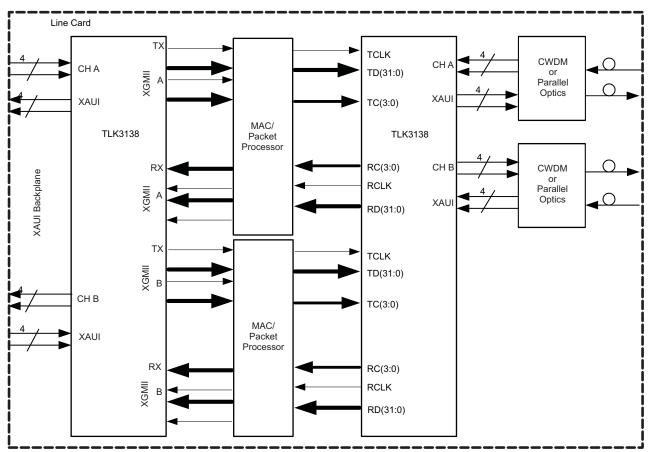

Figure 2 shows an example system block diagram for TLK3138 used to provide the system backplane interconnect.

Figure 2. System Block Diagram - XAUI Backplane

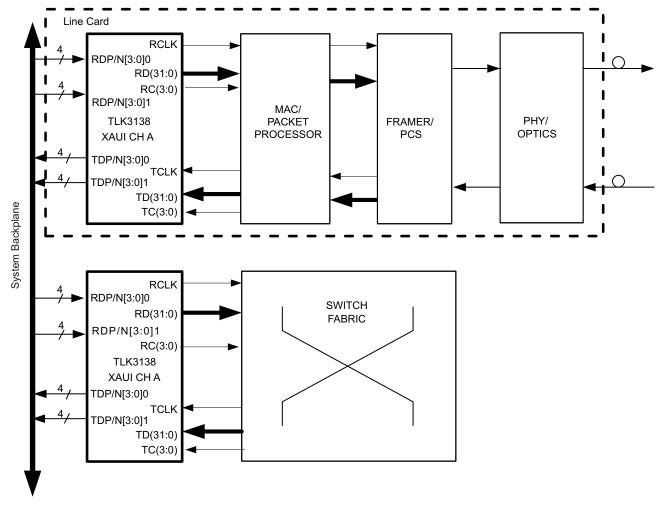

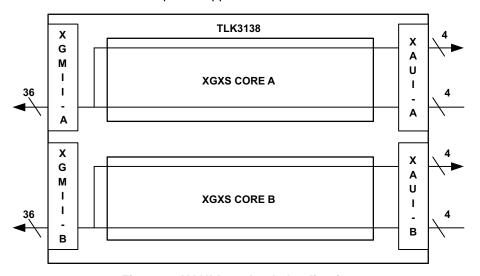

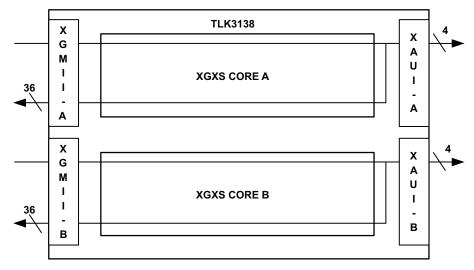

Figure 3 shows the TLK3138 in a Dual XAUI Application:

Figure 3. DUAL XAUI Application

Figure 4 shows the TLK3138 in a XAUI Retimer Application

Figure 4. XAUI Retimer Application

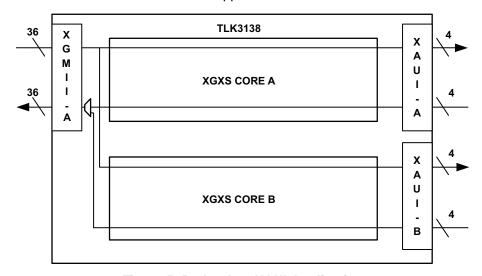

Figure 5 shows the TLK3138 in a Redundant XAUI Application.

Figure 5. Redundant XAUI Application

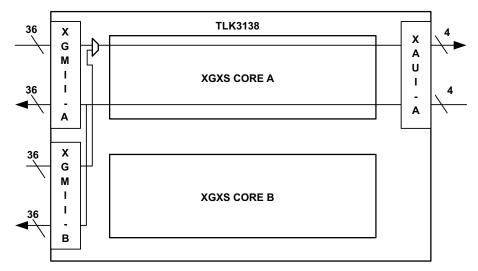

Figure 6 shows the TLK3138 in a Redundant XAUI Application.

Figure 6. Redundant XGMII Application

Figure 7 shows the TLK3138 in a XAUI Loopback Application.

Figure 7. XAUI Loopback Application

Figure 8 shows the TLK3138 in a XGMII Loopback application.

Figure 8. XGMII Loopback Application

It is possible to select non-conflicting modes of operation based on the following bits:

XAUI\_RETIME (See Register Bit 4/5. 32907.2 for definition)

REDUNDANT XAUI (See Register Bit 4/5.32907.6 for definition)

REDUNDANT\_XGMII (See Register Bit 4/5.32907.7 for definition)

XGMII LOOPBACK (See Register Bit 4/5.32792. 0 for definition (1 bit for each XGXS Core))

XAUI LOOPBACK (See Register Bit 4/5.32792. 1 for definition (1 bit for each XGXS Core))

The TLK3138 supports the IEEE 802.3 defined Management Data Input/Output (MDIO) Interface to allow ease in configuration and status monitoring of the link. The bi-directional data pin (MDIO) should be externally pulled up to 1.2V or 2.5V per the standard for both MDIO0 and MDIO1.

The TLK3138 supports the IEEE 1149.1 defined JTAG test port for ease in board manufacturing test. It also supports a comprehensive series of built-in tests for self-test purposes including PRBS generation and verification, CRPAT, CJPAT, Mixed/High/Low Frequency testing.

The TLK3138 operates with a 1.2V core voltage supply, a 1.5V HSTL I/O voltage supply and a 2.5V bias supply.

The TLK3138 is packaged in a 23×23mm, 484-ball, 1mm ball pitch Plastic Ball Grid Array (PBGA) package and is characterized for operation from 0°C to 70°C Ambient, 115°C Junction, and 5% power supply variation unless noted otherwise. Note that the junction temperature must be kept below 115°C to meet TI C035 process reliability.

### **BLOCK DIAGRAMS**

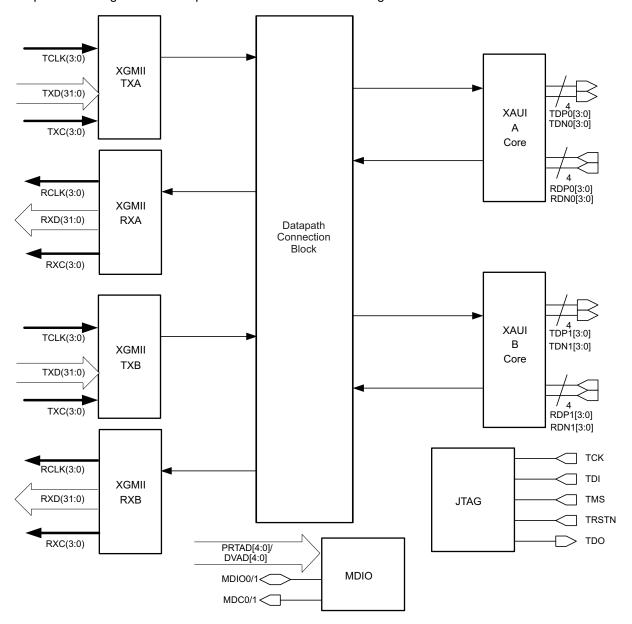

Figure 9 provides a high level description of the TLK3138 block diagram.

Figure 9. TLK3138 Block Diagram

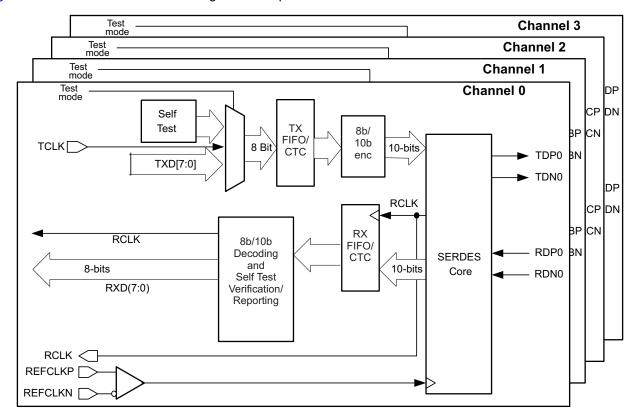

Figure 10 is a more detailed block diagram description of XAUI core.

Figure 10. Detailed XAUI Core Block Diagram

Figure 11. Block Diagram of SERDES Core

#### **DETAILED DESCRIPTION**

The TLK3138 has several operational interface modes controlled by register bits A/B and XAUI\_RETIME, REDUNDANT\_XAUI, and REDUNDANT\_XGMII. The major modes of application are discussed below.

#### **REDUNDANT XAUI OPERATION**

The TLK3138 can operate as a redundant XAUI transceiver.

In Redundant XAUI MODE (4/5.32907.6), only the A side XGMII interface is active, and both serial interfaces XAUI A and XAUI B are active. It is possible for B side XGMII to receive B side serial data, but the transmit XGMII B interface is ignored. The transmit datapath either duplicates the transmit XGMII data to both serial side data streams, or if the IDLE mode is selected, send only valid A/K/R (idle) sequences on the deselected side. The receive datapath selects one of the two aggregated input serial streams controlled by the A\_B (4/5.32907.3) register bit.

While communication is occurring on the primary selected channel, the secondary channel is fully functional capable of transmitting and receiving data. All registers are accessible and valid. The only difference between the primary and secondary channels is the primary channel is routed to the A side XGMII receive bus.

A completely active secondary channel allows transition from primary to secondary channels within a few clock cycles. During the transition, the data on each byte of the bus is 0xFE (code violation), which is the ERROR indication, or local fault indication (based on a provisioned register value).

#### **REDUNDANT XGMII OPERATION**

The TLK3138 can operate as a redundant XGMII transceiver.

In Redundant XGMII MODE (4/5.32907.7), only the A side Serial interface is active, and both Parallel interfaces XGMII A and XGMII B are active. It is possible for B side XAUI to transmit B side parallel data, but the receive XAUI B interface is processed but not used. The receive datapath either duplicates the receive XAUI data to both parallel side data streams, or if the IDLE mode is selected, send only valid (idle) sequences on the deselected side. The transmit datapath selects one of the two aggregated input parallel streams controlled by the A\_B (4/5.32907.3) register bit.

While communication is occurring on the primary selected channel, the secondary channel is fully functional capable of transmitting data (if desired). All B side transmit related registers are accessible and valid.

During the transition, the data on each byte of the bus is 0xFE (code violation), which is the ERROR indication, or local fault indication (based on a provisioned register value).

#### **RETIMER OPERATION**

The TLK3138 can operate as a full duplex serial side re-timer. All the functions of transceiver operations are performed except for the XGMII input interfaces, and optionally the XGMII output interfaces. The recovered data on each XAUI channel is de-serialized, de-skewed, aligned to the reference clock, and re-serialized. In the re-timer mode inputs from the XGMII inputs are ignored. XGMII outputs can provisionally be left on to snoop received data, or turned off to save power.

Note that when RETIM is high, the serial side A receive data is routed out to the serial side B transmit serial lines. Similarly, the serial side B receive data is routed out to the serial side A transmit serial lines.

If A/B is toggled when in re-timer monitor mode, the data on each byte of the XGMII receive output bus (if not in 3-state) is 0xFE (code violation) for several XGMII clock cycles, or local fault (based on the provisioned register value).

#### **PARALLEL CLOCKING MODES**

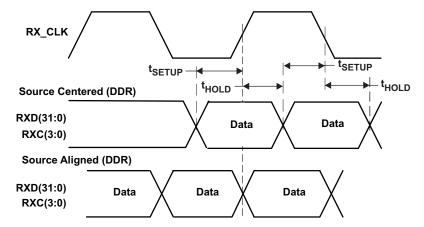

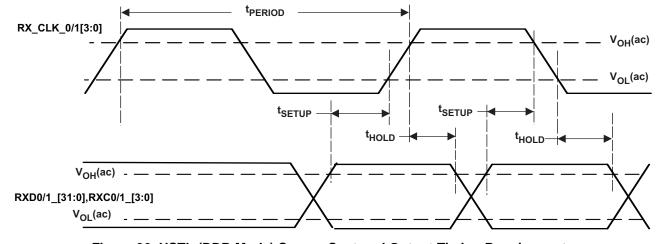

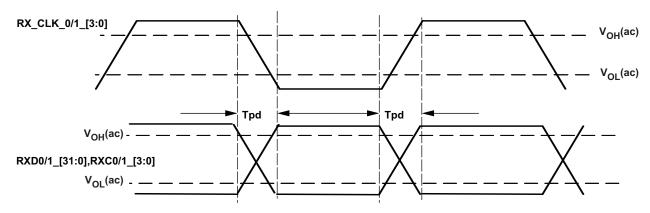

The TLK3138 supports source-centered timing and source-aligned timing on the XGMII receive output bus. The source-centered timing supported is the timing defined in P802.3ae Clause 46, with the RX\_CLK centered within the receive output data bit timing, as shown in Figure 12. Also shown is source-aligned timing.

Figure 12. Receive Interface Timing – Source Centered/Aligned

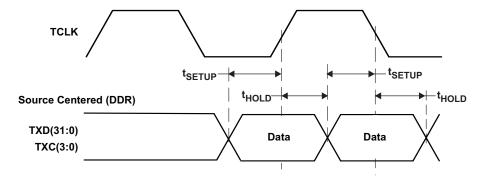

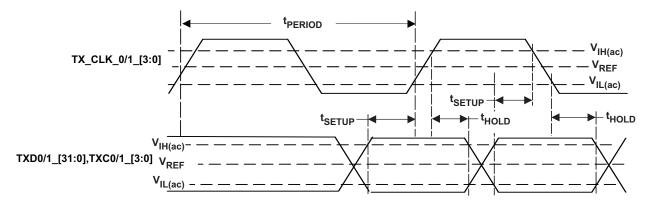

On the transmit data path, the data is sampled on the rising edge and falling edge of TCLK as shown in Figure 13.

In the receive datapath A FIFO, placed on the output of the serial to parallel conversion logic for each serial link, compensates for channel skew, clock phase and frequency tolerance differences between the received clocks for each serial links and the received output clock, RX\_CLK. This FIFO has a total depth of sixteen ten bit entries, giving 30 bit time deskew (channel to channel skew) alignment capability in standard mode. See HSTL Output Switching Characteristics (DDR) table in the Electrical Characteristics section for more details on XGMII timing.

Figure 13. Transmit Interface Timing

#### PARALLEL INTERFACE DATA

Data placed on the XGMII transmit input bus is latched and then phase aligned to the internal version of the transmit reference clock, 8b/10b encoded, serialized, then transmitted sequentially beginning with the LSB of the encoded data byte over the differential high speed serial transmit pins.

The XGMII receive data bus outputs four bytes on RXD(31:0). Control character (K-characters) reporting for each byte is done by asserting the corresponding control pin, RXC(3:0). When RXC is asserted, the 8 bits of data corresponding to the control pin is to be interpreted as a K-character. If an error is uncovered in decoding the data, the control pin is asserted and 0xFE is output for the corresponding byte.

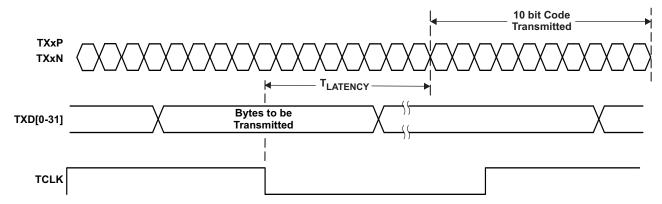

### TRANSMISSION LATENCY

For each channel, the data transmission latency of the TLK3138 is defined as the delay from the rising or falling edge of the selected transmit clock when valid data is on the transmit data pins to the serial transmission of bit 0, as shown in Figure 14. The maximum transmit latency  $(T_{LATENCY})$  is 650 bit times; the standard allows a combined latency (TX + RX) of 2048 bit times.

Figure 14. Transmission Latency

#### CHANNEL CLOCK TO SERIAL TRANSMIT CLOCK SYNCHRONIZATION

In XAUI mode, the TLK3138 allows  $\pm 200$  ppm difference between the serdes transmit reference on the XAUI side, versus the input TCLK on the XGMII side. There exists a FIFO capable of CTC operations, and has a depth of 32 locations (32 bits wide per location).

The reference clock and the transmit data clock(s) may be from a common source, but the design allows for up to  $\pm 200$  ppm of frequency difference should the application require it.

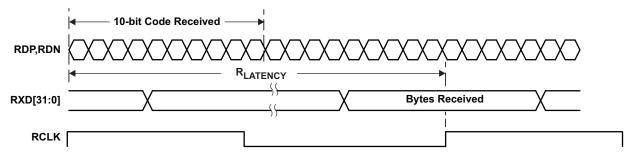

#### **DATA RECEPTION LATENCY**

For each serial link, the serial-to-parallel data latency is the time from when the first bit arrives at the serial receiver input until it is output in the aligned parallel word on the XGMII, as shown in Figure 15. The maximum receive latency (R<sub>LATENCY</sub>) is 950 bit times using standard alignment mode; the standard allows a combined latency (TX + RX) of 2048 bit times.

Figure 15. Receiver Latency

#### **8B/10B ENCODER**

All true serial interfaces require a method of encoding to insure sufficient transition density for the receiving PLL to acquire and maintain lock. The encoding scheme also maintains the signal DC balance by keeping the number of ones and zeros are balanced which allows for AC coupled data transmission. The TLK3138 uses the 8B/10B encoding algorithm that is used by 10Gbps and 1Gbps Ethernet and Fibre Channel standards. This provides good transition density for clock recovery and improves error checking. The 8B/10B encoder/decoder function is enabled for all serial links. The TLK3138 internally encodes and decodes the data such that the user reads and writes actual 8-bit data on each channel. The encoder and decoder functions can optionally be enabled or disabled on a per channel basis.

The 8B/10B encoder converts 8-bit wide data to a 10-bit wide encoded data character to improve its transition density. This transmission code includes D Characters, used for transmitting data, and K Characters, used for transmitting protocol information. Each K or D character code word can also have both a positive and a negative disparity version. The disparity of a code word is selected by the encoder to balance the running disparity of the serialized data stream.

The generation of K-characters to be transmitted on each channel is controlled by transmit control pins, TXC(3:0). When the control pin is asserted along with the 8 bits of data, an 8B/10B K-character is transmitted. Similarly, reception of K-characters is reported by the receive control pins, RXC(3:0). When receive control pin is asserted, the corresponding byte on the receive data bus should be interpreted as a K-character. The TLK3138 transmits and receives all of the twelve valid K-characters as defined in Table 1.

#### Table 1. Valid K-Codes

|               | TVC(2-0)                   | DATA DUC DVICE                              | ENCODE                           | D K-CODE                      |                                |

|---------------|----------------------------|---------------------------------------------|----------------------------------|-------------------------------|--------------------------------|

| K-CODE        | TXC(3:0)<br>or<br>RXC(3:0) | DATA BUS BYTES (RXD[x: x-7] or TXD[x: x-7]) | NEGATIVE<br>RUNNING<br>DISPARITY | POSITIVE RUNNING<br>DISPARITY | K-code Description             |

| 00 through FF | 0                          | DDD DDDDD                                   | dddddd dddd                      | dddddd dddd                   | Normal data                    |

| K28.0         | 1                          | 000 11100                                   | 001111 0100                      | 110000 1011                   | IdleO/busy                     |

| K28.1         | 1                          | 001 11100                                   | 001111 1001                      | 110000 0110                   | IdleE/busy                     |

| K28.2         | 1                          | 010 11100                                   | 001111 0101                      | 110000 1010                   |                                |

| K28.3         | 1                          | 011 11100                                   | 001111 0011                      | 110000 1100                   | Channel Alignment Pre-curser   |

| K28.4         | 1                          | 100 11100                                   | 001111 0010                      | 110000 1101                   |                                |

| K28.5         | 1                          | 101 11100                                   | 001111 1010                      | 110000 0101                   | IdleE/not-busy                 |

| K28.6         | 1                          | 110 11100                                   | 001111 0110                      | 110000 1001                   |                                |

| K28.7         | 1                          | 111 11100                                   | 001111 1000                      | 110000 0111                   | Code Violation or Parity Error |

| K23.7         | 1                          | 111 10111                                   | 111010 1000                      | 000101 0111                   | IdleO/not-busy                 |

| K27.7         | 1                          | 111 11011                                   | 110110 1000                      | 001001 0111                   | SOP(S)                         |

| K29.7         | 1                          | 111 11101                                   | 101110 1000                      | 010001 0111                   | EOP(T)                         |

| K30.7         | 1                          | 111 11110                                   | 011110 100                       | 100001 0111                   |                                |

Table 2 provides additional transmit data control coding and descriptions that have been incorporated into 10 Gigabits per second Ethernet. Data patterns put on XGMII transmit data bus other than those defined in Table 2 when the transmit control pin is asserted results in an invalid K-character being transmitted which results in an code error at the receiver.

Table 2. Valid XGMII Channel Encodings

| DATA BUS<br>(TXD[x: x-7]<br>or RXD[x: x-7]) | TXC(3:0)<br>or<br>RXC(3:0) | DESCRIPTION                        |

|---------------------------------------------|----------------------------|------------------------------------|

| 00 through FF                               | 0                          | Normal Data Transmission           |

| 00 through 06                               | 1                          | Reserved                           |

| 07                                          | 1                          | Idle                               |

| 08 through 9B                               | 1                          | Reserved                           |

| 9C                                          | 1                          | Sequence (only valid in Channel A) |

| 9D through FA                               | 1                          | Reserved                           |

| FB                                          | 1                          | Start (only valid in Channel A)    |

| FC                                          | 1                          | Reserved                           |

| FD                                          | 1                          | Terminate                          |

| FE                                          | 1                          | Transmit error propagation         |

| FF                                          | 1                          | Reserved                           |

#### **COMMA DETECT AND 8B/10B DECODING**

When parallel data is clocked into a parallel to serial converter, the byte boundary that was associated with the parallel data is lost in the serialization of the data. When the serial data is received and converted to parallel format again, a method is needed to be able to recognize the byte boundary again. Generally this is accomplished through the use of a synchronization pattern. This is a unique a pattern of 1s and 0s that either cannot occur as part of valid data or is a pattern that repeats at defined intervals. 8B/10B encoding contains a character called the comma (b'0011111' or b'1100000') which is used by the comma detect circuit to align the received serial data back to its original byte boundary. The channel synchronization block detects the K28.5 comma, generating a synchronization signal aligning the data to their 10-bit boundaries for decoding. It then converts the data back into 8-bit data. It is important to note that the comma can be either a (b'0011111') or the inverse (b'1100000') depending on the running disparity. The TLK3138 decoder detects both patterns.

The reception of K-characters is reported by the assertion of receive control pin, RXC(3:0) for the corresponding byte on the XGMII receive bus. When a code word error or running disparity error is detected in the decoded data received on a serial link, the receive control pin is asserted and an 0xFE is placed on the receive data bus for that channel, as shown in Table 3.

| Table  | 3 E  | Receive | Data | Cont | role |

|--------|------|---------|------|------|------|

| i abie | J. F | teceive | Data | Cont | lois |

| EVENT                                      | RECEIVE DATA BUS RXD[x: 7-x] | RXC(3:0) |

|--------------------------------------------|------------------------------|----------|

| Normal Data                                | XX                           | 0        |

| Normal K-character                         | Valid K-code                 | 1        |

| Code word error or running disparity error | FE                           | 1        |

## **Channel Initialization and Synchronization**

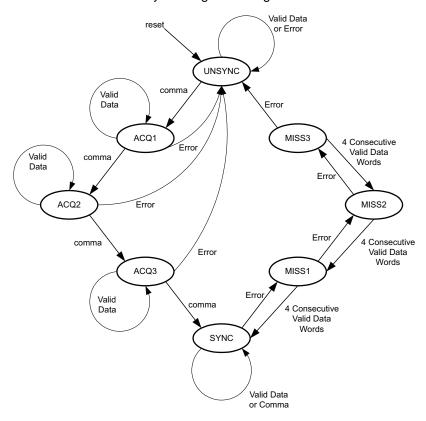

The TLK3138 has a synchronization state machine which is responsible for handling link initialization and synchronization for each channel. The initialization and synchronization state diagram is provided in Figure 16. The status of any channel can be monitored by reading MDIO register 4/5.24.3:0.

Figure 16. Channel Synchronization State Machine

#### CHANNEL STATE DESCRIPTIONS

**UNSYNC** – This is the initial state for each channel upon device power up or reset. In this state, the TLK3138 has the comma detect circuit active and makes code word alignment adjustments based on the position of a comma in the incoming data stream. While in this state the TLK3138 sets the Lane Sync bit to '0' for the particular channel in MDIO register bits 4/5.24.3:0, indicating the lane is not synchronized. (1) The channel state transitions to the ACQ1 state upon the detection of a comma.

(1) The Lane Sync Bit = '0' bit from any/or all channels causes a local fault to be output on the receive data bus.

**ACQ1** – During this state the comma detect circuit is active but code word re-alignment is disabled. The TLK3138 remains in this state until either a comma is detected in the same code word alignment position as found in state UNSYNC or a decode error is encountered. While in this state, the Lane Sync bit for the particular channel remains de-asserted, indicating the lane is not synchronized. (2) A decode or running disparity error returns the channel state to UNSYNC. A detected comma causes the channel state to transition to ACQ2.

**ACQ2** – During this state, the comma detect circuit is active but code word re-alignment is disabled. The TLK3138 remains in this state until either a comma is detected in the same code word alignment position as found in state UNSYNC or a decode error is encountered. While in this state, the Lane Sync bit for the particular channel remains de-asserted, indicating the lane is not synchronized. A decode or running disparity error returns the channel state to UNSYNC. A detected comma causes the channel state to transition to ACQ3.

**ACQ3** –During this state the comma detect circuit is active but code word re-alignment is disabled. The TLK3138 remains in this state until either a comma is detected or a decode error encountered. While in this state, the Lane Sync bit for the particular channel remains de-asserted, indicating the lane is not synchronized. (2) A decode or running disparity error returns the channel state to UNSYNC. A detected comma causes the channel state to transition to SYNC.

**SYNC** –This is the normal state for receiving data. When in this state, the TLK3138 sets the Lane Sync bit to '1' for the particular channel in the MDIO register bits 4/5.24.3:0 indicating the lane has been synchronized. During this state the comma detect circuit is active but code word re-alignment is disabled. A decode or running disparity error causes the channel state to transition to MISS1.

**MISS1** – When entering this state an internal error counter is cleared. If the next four consecutive codes are decoded without error, the channel state reverts back to SYNC. If a decode or running disparity error is detected, the channel state transitions to MISS2.

MISS2 – When entering this state an internal error counter is cleared. If the next four consecutive codes are decoded without error, the channel state reverts back to MISS1. If a decode or running disparity error is detected, the channel state transitions to MISS3.

MISS3 -When entering this state an internal error counter is cleared. If the next four consecutive codes are decoded without error, the channel state reverts back to MISS1. If a decode or running disparity error is detected, the channel state transitions to UNSYNC.

#### **END OF PACKET ERROR DETECTION**

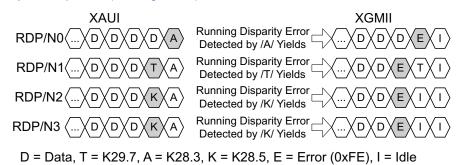

Because of their unique data patterns, /A/ (K28.3), /K/ (K28.5), and /T/ (K29.7) catch running disparity errors that may have propagated undetected from previous codes in a packet. Running disparity errors detected by these control codes at the end of packets cause the previous data codes to be reported as errors (0xFE) to allow the protocol device to reject the packet (see Figure 17).

Figure 17. End of Packet Error Detection

(2) The Lane Sync bit = '0' causes a local fault to be output on the receive data bus.

#### **FAULT DETECTION AND REPORTING**

The TLK3138 detects and reports local faults as well as forward both local and remote faults as defined in the IEEE P802.3ae 10Gbps Ethernet Standard to aid in fault diagnosis. All faults detected by the TLK3138 are reported as local faults to the upper layer protocols. Once a local fault is detected in the TLK3138, MDIO register bit 4/5.1.7 is set. Fault sequences, sequence ordered sets received by the TLK3138, either on the Transmit Data Bus or on the high speed receiver pins, are forwarded without change to the MDIO registers in the TLK3138. Also, note that the TLK3138 is capable of performing CTC operation where only RF and LF or any Q sequences are transported (not generated) in either the transmit or receive direction in XAUI mode.

TLK3138 reports a fault by outputting a K28.4 (0x9C) on RXD(7:0), 0x00 on RXD(15:8) and RXD(23:8) and 0x01 for local faults on RXD(31:24). Forwarding of remote faults is handled as a normal transmission. Note that the TLK3138 does not generate a remote fault indication nor any other type of Q.

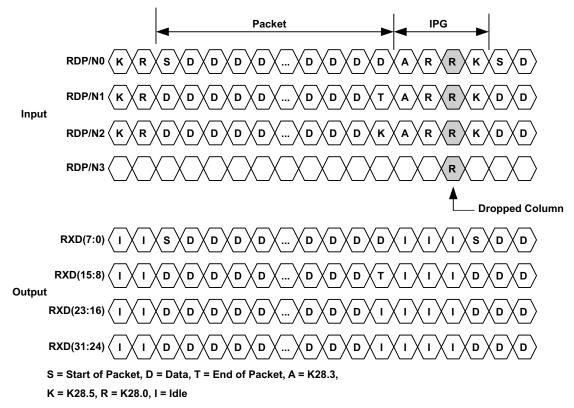

#### RECEIVE SYNCHRONIZATION AND SKEW COMPENSATION

In XAUI mode, the TLK3138 has a FIFO enabled on the receive data path coming from each serial link to compensate for channel skew and clock phase and frequency tolerance differences between the received clocks for each channel and the receive output clock RX\_CLK. This FIFO has a depth of 32 locations (32 bits wide for each location).

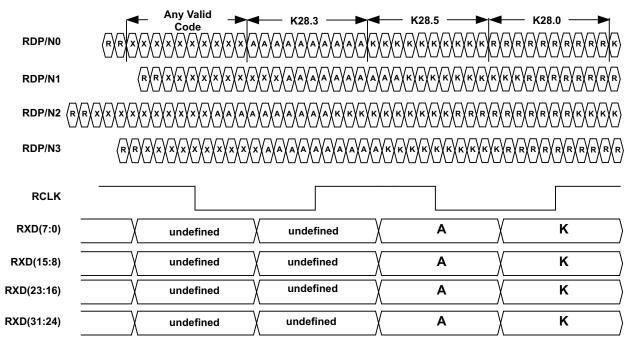

The de-skew of the 4 serial links that make up each XAUI channel into a single 32 bit wide column of data is accomplished by alignment of the receive FIFOs on each serial link to a K28.3 control code sent during the inter-packet gap (IPG) between data packets or during initial link synchronization. The K28.3 code (referred to as the A or alignment code) is transmitted on the first column following the end of the data packet as shown in Table 2.

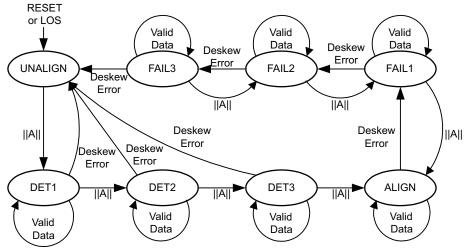

The column de-skew state machine is provided in Figure 18. The status of column alignment can be monitored by reading MDIO registers 4/5.24.12 for global alignment.

Note: Deskew Error is at least one column containing an A character, but not all four simultaneously.

Figure 18. Column De-Skew State Machine

#### **COLUMN STATE DESCRIPTIONS**

**UNALIGN** – This is the initial state for the column state machine upon device power up or reset. If any of the channel state machines are set to UNSYNC, the column state is set to UNALIGN. In this state, the column state machine searches for alignment character codes (K28.3 or /A/) on each channel and align the FIFO pointers on each channel to the /A/ character code. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4/5.24.12, indicating the column is not aligned.<sup>(3)</sup> The column state transitions to the DET1 state upon the detection and alignment of /A/ character codes in all four channels.

**DET1** – During this state, the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. The column state machine remains in this state looking for a column of alignment character codes. If an incomplete alignment column is detected (alignment character codes not found on all channels) or a deskew error is detected, the column state machine transitions to state UNALIGN. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4/5.24.12 indicating the column is not aligned. (4) Detection of a complete alignment column causes the column state machine to transition to state DET2.

**DET2** – During this state, the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. The column state machine remains in this state looking for a column of alignment character codes. If an incomplete alignment column is detected (alignment character codes not found on all channels) or a deskew error is detected, the column state machine transitions to state UNALIGN. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4/5.24.12 indicating the column is not aligned. Detection of a complete alignment column causes the column state machine to transition to state DET3.

**DET3** –During this state, the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. The column state machine remains in this state looking for a column of alignment character codes. If an incomplete alignment column is detected (alignment character codes not found on all channels) or a deskew error is detected, the column state machine transitions to state UNALIGN. While in this state, the Column Alignment Sync bit is set to '0' in MDIO registers 4/5.24.12 indicating the column is not aligned. Detection of a complete alignment column causes the column state machine to transition to state ALIGN.

**ALIGN** – This is the normal state for receiving data. When in this state, the column state machine sets the Column Alignment Sync bit to '1' in MDIO registers 4/5.24.12 indicating all channels are aligned. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If a deskew error is detected in the correct position within the Inter-Packet Gap, the column state machine transitions to state FAIL1.

**FAIL1** – When in this state, the Column Alignment Sync bit is '1' in MDIO registers 4/5.24.12. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If a complete alignment column is not detected in the correct position within the Inter-Packet Gap, the column state machine transitions to state FAIL2.

**FAIL2** – When in this state, the Column Alignment Sync bit is '1' in MDIO registers 4/5.24.12. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If a complete alignment column is not detected in the correct position within the Inter-Packet Gap, the column state machine transitions to state FAIL3.

**FAIL3** – When in this state, the Column Alignment Sync bit is '1' in MDIO registers 4/5.24.12. During this state the alignment character code detect circuit is active on each channel but the column re-alignment is disabled. If complete alignment column is not detected in the correct position within the Inter-Packet Gap, the column state machine transitions to state UNALIGN.

- (3) The XGXS Lane Alignment bit = '0' causes a local fault to be output on the receive data bus.

- (4) The XGXS Lane Alignment bit = '0' causes a local fault to be output on the receive data bus.

Figure 19. Channel De-Skew Using Alignment Code

#### **INTER-PACKET GAP MANAGEMENT**

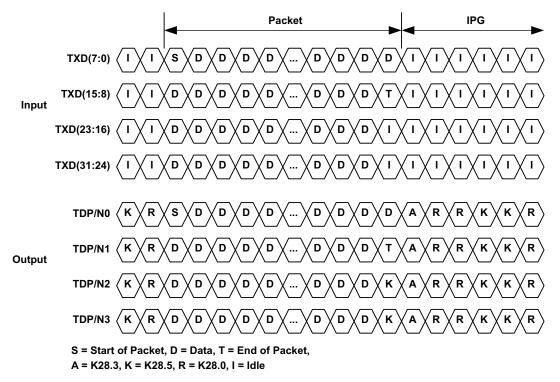

When in transceiver mode, the TLK3138 replaces the idle codes (see Table 2) during the Inter-Packet Gap (IPG) with the necessary codes to perform all channel alignment, byte alignment, and clock tolerance compensation as defined in IEEE 802.3ae 10Gbps Ethernet Standard. According to the Ethernet Standard, a valid packet must begin on TXD(0:7) of the XGMII. However, due to variable packet sizes, the IPG can begin on any channel. The TLK3138 replaces idle codes latched on the same XGMII clock edge as the end of packet code with /K/ codes (as shown in Figure 20).

Figure 20. Inter-Packet Gap Management

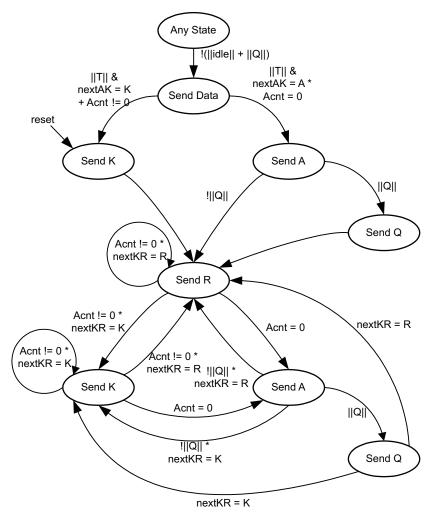

The subsequent idles in the IPG are replaced by *columns* of channel alignment codes (K28.3), byte alignment codes (K28.5), or clock tolerance compensation codes (K28.0). The state machine which governs the IPG replacement procedure is illustrated in Figure 21, with notation defined in Table 2. Note that any IPG management state transitions to send data if the IPG is terminated.

The repetition of the /A/ pattern on each serial channel allows the FIFOs to remove or add the required phase and frequency difference to align the data from all four serial links of a XAUI channel and allow output of the aligned 32 bit wide data on a single edge of the receive clock, RX\_CLK, as shown in Figure 21.

Figure 21. IPG Management State Machine

**Table 4. IPG Management State Machine Notation**

| SYMBOL | DEFINITION                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| idle   | XGMII idle. 0x07 on TXD(x:: :x-7),                                                                                                                                              |

| Q      | Link status message: K28.4, Dx.y, Dx.y, Dx.y.                                                                                                                                   |

| nextAK | A Boolean variable. It takes the value K when an A is sent at the beginning of the IPG and the value A when a K is sent at the beginning of the IPG. Its initial value is K.    |

| Acnt   | When an A character is sent, variable Acnt is loaded with a random number such that $16 \le Acnt \le 31$ . Acnt is decremented each time a column of A characters is generated. |

| nextKR | A randomly-generated Boolean that can assume the value K or R.                                                                                                                  |

| T      | Terminate Character Column (Terminate Character in Any Lane)                                                                                                                    |

## **CLOCK TOLERANCE COMPENSATION (CTC)**

The XAUI interface is defined to allow for separate clock domains on each side of the link. Though the reference clocks for two devices on a XAUI link have the same specified frequencies, there are slight differences that, if not compensated for, leads to over or under run of the FIFOs on the receive/transmit data path. The TLK3138 provides compensation for these differences in clock frequencies via the insertion or the removal of /R/ characters on all channels, as shown in Figure 22 and Figure 23.

Figure 22. Clock Tolerance Compensation: Add

The /R/ code is disparity neutral, allowing its removal or insertion without affecting the current running disparity of each channel's serial stream.

Figure 23. Clock Tolerance Compensation: Drop

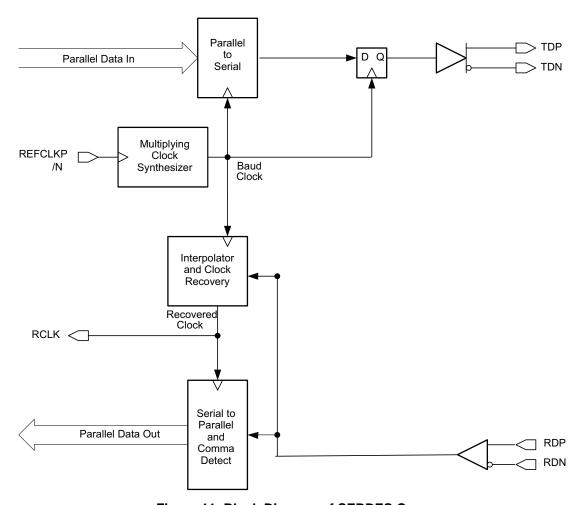

#### PARALLEL TO SERIAL

The parallel-to-serial shift register on each channel takes in data and converts it to a serial stream. The shift register is clocked by the internally generated bit clock, which is 10 times the reference clock (REFCLKP/REFCLKN) frequency. The least significant bit (LSB) for each channel is transmitted first.

#### **SERIAL TO PARALLEL**

For each channel, serial data is received on the RDPx/RDNx pins. The interpolator and clock recovery circuit locks to the data stream if the clock to be recovered is within  $\pm 200$  PPM of the internally generated bit rate clock. The recovered clock is used to retime the input data stream. The serial data is then clocked into the serial-to-parallel shift registers. If enabled, the 10-bit wide parallel data is then fed into 8b/10b decoders.

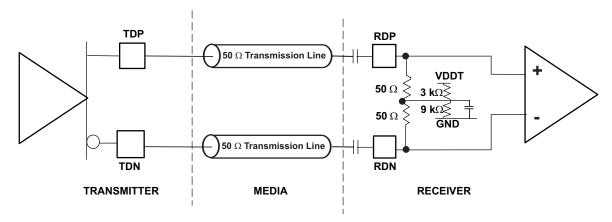

#### HIGH SPEED CML OUTPUT

The high speed data output driver is implemented using Current Mode Logic (CML) with integrated pull up resistors requires no external components. The line can be directly coupled or AC coupled. Under many circumstances, AC couple is desirable.

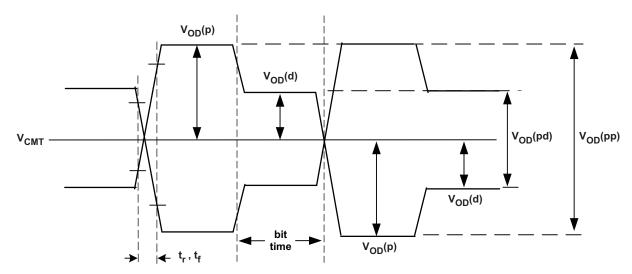

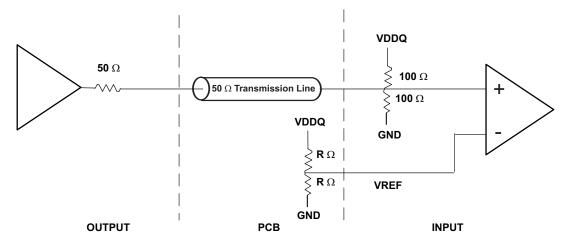

Figure 24. Example High Speed I/O AC Coupled Mode

Standard Current Mode Logic (CML) drivers usually require external components. The disadvantage of the external edge control is a limited edge rate due to package and line parasitic. The CML driver on TLK3138 has on-chip  $50\Omega$  termination resistors terminated to VDDT therefore provides optimum performance for increased speed requirements. The transmitter output driver is highly configurable allowing slew rate, output amplitude and pre-emphasis to be turned to a channel's individual requirements. An internal voltage reference derived from VDDT is also available to provide the target for output amplitude control loop. This reference is enabled by holding register bit 4/5.32900.6 low and results in a nominal output amplitude of ~1400mV differential pk-pk for 100% swing. The receiver input is internally biased to  $2\times VDDT/3$  which is the optimum voltage for input sensitivity. As the input and output references are derived from VDDT, the tolerance of this supply dominates the accuracy of the internal reference. Applications requiring higher tolerance output amplitude are advised to provide a high accuracy external reference.

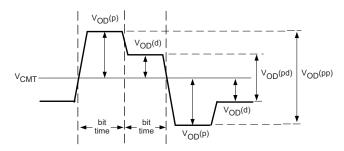

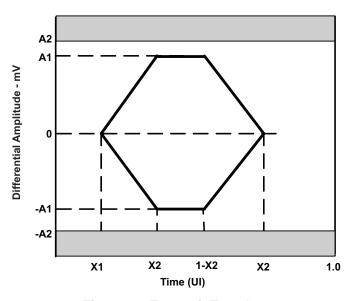

When transmitting data across long lengths of PCB trace or cable, the high frequency content of the signal is attenuated due to the skin effect of the media. This causes a *smearing* of the data eye when viewed on an oscilloscope. The net result is reduced timing margins for the receiver and clock recovery circuits. In order to provide equalization for the high frequency loss, 2-tap finite impulse response (FIR) transmit pre-emphasis is implemented. In a 1-tap FIR pre-emphasis, differential swing is increased or *pre-emphasized* for the bit immediately following a transition and subsequently reduced or *de-emphasized* for run lengths greater than one, as shown in Figure 25. This provides additional high frequency energy to compensate for PCB or cable loss.

Figure 25.

The 2-stage mode operates in a similar manner but considers the logic level of the previous two transmitted bits when determined how much pre-emphasis to apply. The level and mode of the pre-emphasis is programmable via MDIO Register bits 4/5.32900.14:11. Users can control the strength of the pre-emphasis to optimize for a specific system requirement.

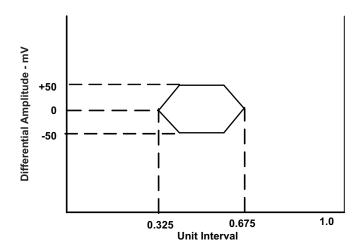

#### **HIGH SPEED RECEIVER**

The high speed receiver conforms to the physical layer requirements of IEEE 802.3ae Clause 47(XAUI). The termination impedances of the receiver is configured as 100 Ohms with the center tap weakly tied to 2×VDDT/3 with a capacitor to create an AC ground. AC coupling is always required on receiver inputs.

All receive channels incorporate an adaptive equalizer. This circuit compensates for channel insertion loss by amplifying the high frequency components of the signal, reducing inter-symbol interference. Setting 4/5.32900.2 enables adaptive equalization. In this mode, both the gain and bandwidth of the equalizer with be controlled by the receiver equalization logic. Bandwidth selection is based on the setting applied to 4/5.32901.14:13 and 4/5.32900.3. Equalization can be disabled by setting 4/5.32900.2 low.

#### **LOOPBACK**

In XAUI Mode, two internal loopback modes are possible for each XAUI Channel Group A and B. One, called XGMII loopback, allows the data input on the XGMII interface to be returned out the corresponding XGMII interface (A->A, B->B). The other, called XAUI loopback, allows serial data on the XAUI interface to be returned out the corresponding XAUI interface (A->A, B->B).

An external loopback (requiring external connection) is also supported, which can be used with the PRBS patterns, as well as the CJPAT, CRPAT, Mixed/High/Low Frequency tests.

#### LINK TEST FUNCTIONS

The TLK3138 has an extensive suite of built in test functions to support system diagnostic requirements. Each channel has built-in link test generator and verification logic. Several patterns can be selected via the MDIO that offer extensive test coverage. The patterns are: 2<sup>7</sup>-1 or 2<sup>23</sup>-1 PRBS (Pseudo Random Bit Stream), CJPAT, CRPAT, high and low and mixed frequency patterns.

#### **MDIO Management Interface**

The TLK3138 supports the Management Data Input/Output (MDIO) Interface as defined in Clause 45 of the IEEE 802.3ae Ethernet specification. The MDIO allows register-based management and control of the serial links. Normal operation of the TLK3138 is possible without use of this interface. However, some additional features are accessible only through the MDIO.

The following registers in the PROGRAMMERS REFERENCE are implemented as global registers (i.e Same physical register is accessed through XAUI-A register access or XAUI-B register access):

16'h8086, 16'h8088, 16'h8089, 16'h808B, 16'h808C, 16'h808E, 16'h8090, 16'h8091, 16'h8092, 16'h8093,16'h80A0, 16'h80A1, 16'h80A2

All other registers are implemented per XAUI channel (unique per channel).

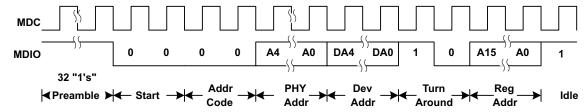

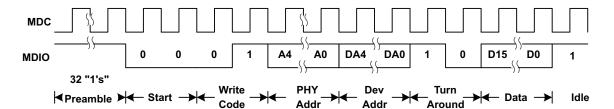

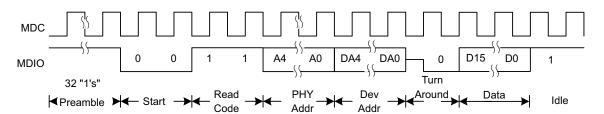

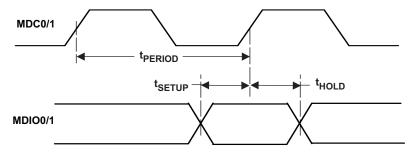

The MDIO Management Interface consists of a bi-directional data path (MDIO) and a clock reference (MDC). The device id and port address are determined by bootstrap pins (see Table 82). In Clause 45, the 5 bootstrap pins determine the port address. Of the port address bits, only the upper four bits are looked at. If the bottom bit of the incoming serial port address is a zero, then XGXS A is addressed. If the bottom bit of the incoming serial port address is a one, then XGXS B is addressed. The device ID is required to be either 4 or 5, so only the bottom device id bit is required. If device id bit 0 is a 0, then a PHY device is selected for both XGXS A and B. If device id bit 0 is a 1, then a DTE device is selected for both XGXS A and B. Note, each register is accessed as either DTE or PHY devices in the TLK3138, although physically there is only one register accessed two different ways. Also note, the XAUI interfaces must either be both DTE devices or both be PHY devices. An even PHY Address (as defined below) indicates an access to XAUI A register space, and an odd PHY Address indicates access to XAUI B register space.

Write transactions which address an invalid register or device, or a read only register are ignored. Read transactions which address an invalid register or device return a 0.

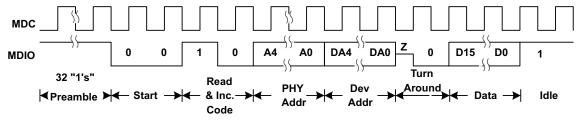

Timing for a Clause 45 address transaction is shown in Figure 26. The Clause 45 timing required to write to the internal registers is shown in Figure 27. The Clause 45 timing required to read from the internal registers is shown in Figure 28. The Clause 45 timing required to read from the internal registers and then increment the active address for the next transaction is shown in Figure 29.

Figure 26. CL45 - Management Interface Extended Space Address Timing

Figure 27. CL45 - Management Interface Extended Space Write Timing

Figure 28. CL45 - Management Interface Extended Space Read Timing

Figure 29. CL45 - Management Interface Extended Space Read And Increment Timing

The IEEE 802.3ae Clause 45 specification defines many of the registers, and additional registers have been implemented for expanded functionality.

### **PROGRAMMERS REFERENCE**

# Table 5. XS<sup>(1)</sup>\_CONTROL\_1

| Address: 0x0000 |                 | x0000 Default: 0x2040                                                                                                                                                                                                                                                                     |                       |

|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Bit(s)          | Name            | Description                                                                                                                                                                                                                                                                               | Access <sup>(2)</sup> |

| 4/5.0.15        | Reset           | 1 = XS reset (including all registers)<br>0 = Normal operation                                                                                                                                                                                                                            | RW<br>SC              |

| 4/5.0.14        | Loop back       | 1 = Enable loop back mode.  If the device is configured as PHY XS (DVAD(0) = 0), then XAUI_LOOPBACK is performed (RX parallel to TX parallel)  If the device is configured as DTE XS (DVAD(0) = 1), then XGMII_LOOPBACK is performed (TX serial to RX serial)  0 = Disable loop back mode |                       |

| 4/5.0.13        | Speed Selection | This bit always reads 1 indicating operation at 10 Gb/s and above.                                                                                                                                                                                                                        | RW                    |

| 4/5.0.11        | Low power       | 1 = Low power mode<br>0 = Normal operation                                                                                                                                                                                                                                                |                       |

| 4/5.0.6         | Speed Selection | This bit always reads 1 indicating operation at 10Gbps and above.                                                                                                                                                                                                                         |                       |

| 4/5.0.5:2       | Speed Selection | These bits always read 0 indicating operation at 10Gbps.                                                                                                                                                                                                                                  |                       |

- (1) In this section XS refers to either PHY or DTE XS device.

- (2) RO: Read-Only, RW: Read-Write, SC: Self-Clearing, LL: Latching-Low, LH: Latching-High, COR: Clear-on-Read

### Table 6. XS\_STATUS\_1

| Address: 0x0001 |                         | Default: 0x0082                                                                                                                            |        |

|-----------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                    | Description                                                                                                                                | Access |

| 4/5.1.7         | Fault                   | 1 = Fault condition detected (either on TX or RX side. This bit is OR ed version of 4/5.8.10 and 4/5.8.11) 0 = No fault condition detected | RO     |

| 4/5.1.2         | XS Transmit Link Status | 1 = XS Transmit link is up.<br>0 = XS Transmit links is down.<br>(This bit is latched low version of 4/5.24.12)                            | RO/LL  |

| 4/5.1.1         | Low Power Ability       | This bit always reads 1 indicating support for low power mode                                                                              | RO     |

# Table 7. XS\_DEVICE\_IDENTIFIER\_1

| Address: 0x0002 |         | Default: 0x4000                     |    |

|-----------------|---------|-------------------------------------|----|

| Bit(s)          | Name    | Description                         |    |

| 4/5.2.15.0      | OUI c:r | Organizationally unique identifier. | RO |

# Table 8. XS\_DEVICE\_IDENTIFIER\_2

| Address: 0x0003         |         | Default: 0x50D0                                           |        |

|-------------------------|---------|-----------------------------------------------------------|--------|

| Bit(s) Name Description |         | Description                                               | Access |

| 4/5.3.15:0              | OUI c:r | Device identifier. Manufacturer model and revision number | RO     |

### Table 9. XS\_SPEED\_ABILITY

| Address: 0x0004 |             | Default: 0x0001                                        |        |

|-----------------|-------------|--------------------------------------------------------|--------|

| Bit(s)          | Name        | Description                                            | Access |

| 4/5.4.0         | 10G Capable | This bit always reads 1 indicating operation at 10Gb/s | RO     |

# Table 10. XS\_DEVICES\_IN\_PACKAGE\_1

| Address: 0x0005 |                             | Default: 0x0010                                                                                                |        |

|-----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                        | Description                                                                                                    | Access |

| 4/5.5.5         | DTE XS Present              | 1 = DTE XS present in the package. 0 = DTE XS not present in the package. Read returns 1, when dvad_in is high |        |

| 4/5.5.4         | PHY XS Present              | 1 = PHY XS present in the package. 0 = PHY XS not present in the package. Read returns 1, when dvad_in is low  | RO     |

| 4/5.5.3         | PCS Present                 | Always reads 0                                                                                                 |        |

| 4/5.5.2         | WIS Present                 | Always reads 0                                                                                                 |        |

| 4/5.5.1         | PMD/PMA Present             | Always reads 0                                                                                                 |        |

| 4/5.5.0         | Clause 22 registers Present | Always reads 0                                                                                                 |        |

# Table 11. XS\_DEVICES\_IN\_PACKAGE\_2

| Address: 0x0006 |                                  | Default: 0x0000                                                                           |        |

|-----------------|----------------------------------|-------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                             | Description                                                                               | Access |

| 4/5.6.15        | Vendor Specific Device 2 Present | This bit always reads 0 indicating that vendor specific device 2 not present in package.  | RO     |

| 4/5.6.14        | Vendor Specific Device 1 Present | This bit always reads 0 indicating that vendor specific device 1 not present in package . | KU     |

# Table 12. XS\_STATUS\_2

| Address: 0x0008 |                | Default: 0x8C00                                                              |        |

|-----------------|----------------|------------------------------------------------------------------------------|--------|

| Bit(s)          | Name           | Description                                                                  | Access |

| 4/5.8.15:14     | Device present | Always read 10 indicating that device responds at this address               | RO     |

| 4/5.8.11        | Transmit fault | 1 = Fault condition on transmit path 0 = No fault condition on transmit path | RO/LH  |

| 4/5.8.10        | Receive fault  | 1 = Fault condition on receive path 0 = No fault condition on receive path   | KO/LH  |

# Table 13. XS\_PACKAGE\_IDENTIFIER\_1

| Address: 0x000E |         | Default: 0x4000                     |        |

|-----------------|---------|-------------------------------------|--------|

| Bit(s)          | Name    | Description                         | Access |

| 4/5.14.15:0     | OUI c:r | Organizationally unique identifier. | RO     |

## Table 14. XS\_PACKAGE\_IDENTIFIER\_2

| Addr        | ess: 0x000F | Default: 0x50D0                                                            |    |

|-------------|-------------|----------------------------------------------------------------------------|----|

| Bit(s)      | Name        | Description                                                                |    |

| 4/5.15.15:0 | OUI c:r     | Organizationally unique identifier Manufacturer model and revision number. | RO |

# Table 15. XS\_LANE\_STATUS

| Address: 0x0018 |                         | Default: 0x0C00                                              |        |

|-----------------|-------------------------|--------------------------------------------------------------|--------|

| Bit(s)          | Name                    | Description                                                  | Access |

| 4/5.24.12       | Align status            | When 1, indicates all lanes are aligned                      |        |

| 4/5.24.11       | Pattern testing ability | Always reads 1. Able to generate test patterns               |        |

| 4/5.24.10       | Loopback ability        | Always read 1. Has the ability to perform loopback function  |        |

| 4/5.24.3        | Lane 3 sync             | 1 = Lane 3 is synchronized<br>0 = Lane 3 is not synchronized |        |

| 4/5.24.2        | Lane 2 sync             | 1 = Lane 2 is synchronized<br>0 = Lane 2 is not synchronized | RO     |

| 4/5.24.1        | Lane 1 sync             | 1 = Lane 1 is synchronized<br>0 = Lane 1 is not synchronized |        |

| 4/5.24.0        | Lane 0 sync             | 1 = Lane 0 is synchronized<br>0 = Lane 0 is not synchronized |        |

# Table 16. XS\_TEST\_CONTROL

| Address: 0x0019 |                             | Default: 0x0000                                                                                                  |        |

|-----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                        | Description                                                                                                      | Access |

| 4/5.25.2        | Receive test-pattern enable | When 1, indicates test pattern function is enabled.                                                              |        |

| 4/5.25.1:0      | Test-pattern select         | 00 = High frequency test pattern 01 = Low frequency test pattern 10 = Mixed frequency test pattern 11 = Reserved | RW     |

# Table 17. TEST\_CONFIG

| Address: 0x8000 |              | 0x8000 Default: 0x0000                                   |        |

|-----------------|--------------|----------------------------------------------------------|--------|

| Bit(s)          | Name         | Description                                              | Access |

| 4/5.32768.1     | CRPAT enable | When set, enables the CRPAT test pattern on all 4 lanes. | RW     |

| 4/5.32768.0     | CJPAT enable | When set, enables the CJPAT test pattern on all 4 lanes. | KVV    |

# Table 18. TEST\_VERIFICATION\_CONTROL

| Address: 0x8001 |                    | Default: 0x0000                                         |        |

|-----------------|--------------------|---------------------------------------------------------|--------|

| Bit(s)          | Name               | Description                                             | Access |

| 4/5.32769.1     | CRPAT check enable | When set, enables the verification of CRPAT test modes. | RW     |

| 4/5.32769.0     | CJPAT check enable | When set, enables the verification of CJPAT test modes. | RVV    |

# Table 19. TX\_FIFO\_STATUS

| Ad          | dress: 0x8002    | Default: 0x0000                                                                   |         |

|-------------|------------------|-----------------------------------------------------------------------------------|---------|

| Bit(s)      | Name             | Description                                                                       | Access  |

| 4/5.32770.9 | Lane 3 overflow  | When high, indicates that transmit FIFO overflow condition occurred for the       |         |

| 4/5.32770.8 | Lane 2 overflow  | corresponding lane.                                                               | DO// 11 |

| 4/5.32770.7 | Lane 1 overflow  |                                                                                   | RO/LH   |

| 4/5.32770.6 | Lane 0 overflow  |                                                                                   |         |

| 4/5.32770.5 | Lane 3 underflow | When high, indicates that transmit FIFO underflow condition occurred for the      |         |

| 4/5.32770.4 | Lane 2 underflow | corresponding lane.                                                               |         |

| 4/5.32770.3 | Lane 1 underflow |                                                                                   |         |

| 4/5.32770.2 | Lane 0 underflow |                                                                                   | RO/LH   |

| 4/5.32770.1 | Overflow         | When high, indicates that transmit FIFO overflow condition occurred in any lane.  |         |

| 4/5.32770.0 | Underflow        | When high, indicates that transmit FIFO underflow condition occurred in any lane. |         |

# Table 20. TX\_FIFO\_DROP\_COUNT

| Address: 0x8003 |            | ss: 0x8003 Default: 0xFFFD                            |        |

|-----------------|------------|-------------------------------------------------------|--------|

| Bit(s)          | Name       | Description                                           | Access |

| 4/5.32771.15:0  | Drop count | Counter for number of idle drops in the transmit FIFO | RO/COR |

# Table 21. TX\_FIFO\_INSERT\_COUNT

| Address: 0x8004 |              | Default: 0xFFFD                                         |        |

|-----------------|--------------|---------------------------------------------------------|--------|

| Bit(s)          | Name         | Description                                             | Access |

| 4/5.32772.15:0  | Insert count | Counter for number of idle inserts in the transmit FIFO | RO/COR |

### Table 22. TX\_CODEGEN\_STATUS

|             | Address: 0x8005                   | Default: 0x0000                                                                                                                                               |        |

|-------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)      | Name                              | Description                                                                                                                                                   | Access |

| 4/5.32773.6 | Invalid XGMII character in lane 3 | When high, indicates invalid XGMII character received in the                                                                                                  |        |

| 4/5.32773.5 | Invalid XGMII character in lane 2 | corresponding lane.                                                                                                                                           | RO/LH  |

| 4/5.32773.4 | Invalid XGMII character in lane 1 |                                                                                                                                                               | KO/LH  |

| 4/5.32773.3 | Invalid XGMII character in lane 0 |                                                                                                                                                               |        |

| 4/5.32773.2 | Invalid XGMII character error     | When high, indicates invalid XGMII character received in any lane                                                                                             |        |

| 4/5.32773.1 | Invalid T column error            | When high, indicates invalid Terminate column (column that contains Terminate character not followed by Idle character(s)) received from the XGMII interface. | RO/LH  |

| 4/5.32773.0 | Invalid S column error            | When high, indicates invalid Start column (column that contains Start character in a lane other than lane 0) received from the XGMII interface.               |        |

### Table 23. LANE\_0\_TEST\_ERROR\_COUNT

| Address: 0x8006 |                                   | Default: 0xFFFD                                                                                                                                                   |        |

|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                              | Description                                                                                                                                                       | Access |

| 4/5.32774.15:0  | Lane 0 test pattern error counter | This counter reflects errors for High, Medium or Low Frequency test patterns for lane 0. This counter increments by 1 for each received character that has error. | RO/COR |

### Table 24. LANE\_1\_ TEST\_ERROR\_COUNT

| Address: 0x8007 |                                   | Default: 0xFFFD                                                                                                                                                   |        |

|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                              | Description                                                                                                                                                       | Access |

| 4/5.32775.15:0  | Lane 1 test pattern error counter | This counter reflects errors for High, Medium or Low Frequency test patterns for lane 1. This counter increments by 1 for each received character that has error. | RO/COR |

# Table 25. LANE\_2\_ TEST\_ERROR\_COUNT

| Address: 0x8008 |                                   | Default: 0xFFFD                                                                                                                                                       |        |

|-----------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                              | Description                                                                                                                                                           | Access |

| 4/5.32776.15:0  | Lane 2 test pattern error counter | This counter reflects errors for High, Medium or Low Frequency test patterns for lane 2. This counter is incremented by 1 for each received character that has error. | RO/COR |

## Table 26. LANE\_3\_ TEST\_ERROR\_COUNT

| Address: 0x8009 |                                   | Default: 0xFFFD                                                                                                                                                     |        |

|-----------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                              | Description                                                                                                                                                         | Access |

| 4/5.32777.15:0  | Lane 3 test pattern error counter | This counter reflects errors for High, Medium or Low Frequency test patterns for lane 3. This counter increments by one for each received character that has error. | RO/COR |

## Table 27. CRPAT\_CJPAT\_TEST\_ERROR\_COUNT\_1<sup>(1)</sup>

| Address: 0x800A |                                | Default: 0xFFFF                                  |        |

|-----------------|--------------------------------|--------------------------------------------------|--------|

| Bit(s)          | Name                           | Description                                      | Access |

| 4/5.32778.15:0  | CRPAT/CJPAT test error counter | MSB of CRPAT/CJPAT error counter for all 4 lanes | RO     |

(1) User has to make sure that register 32778 is read first and then register 32779. If user reads register 32779 without reading register 32778 first, then the count value read through 32779 register may not be correct.

### Table 28. CRPAT\_CJPAT\_TEST\_ERROR\_COUNT\_2<sup>(1)</sup>

| Address: 0x800B |                                | Default: 0xFFFD                                  |        |

|-----------------|--------------------------------|--------------------------------------------------|--------|

| Bit(s)          | Name                           | Description                                      | Access |

| 4/5.32779.15:0  | CRPAT/CJPAT test error counter | LSB of CRPAT/CJPAT error counter for all 4 lanes | RO     |

(1) User has to make sure that register 32778 is read first and then register 32779. If user reads register 32779 without reading register 32778 first, then the count value read through 32779 register may not be correct.

### Table 29. LANE 0 EOP ERROR COUNT<sup>(1)</sup>

| Address: 0x800C |                                    | Default: 0xFFFD                                                                                                                                                                                             |          |

|-----------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Bit(s)          | Name                               | Description                                                                                                                                                                                                 | Access   |

| 4/5.32780.15:0  | Lane 0 end of packet error counter | End of packet termination error counter for lane 0. End of packet error for lane 0 is detected on the RX side. It is detected when Terminate character is in lane 0 and one or both of the following holds: | RO/COR   |

|                 |                                    | Terminate character is not followed by /K/ characters in lanes 1, 2 and 3                                                                                                                                   | 110,0011 |

|                 |                                    | The column following the terminate column is neither   K   or   A  .                                                                                                                                        |          |

(1) Counter is incremented by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter holds on to its value when align\_status goes low or when the counter reaches its maximum value. It is cleared when it is read.

### Table 30. LANE 1 EOP ERROR COUNT<sup>(1)</sup>

| Address: 0x800D |                                    | Default: 0xFFFD                                                                                                                                                                                             |        |

|-----------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                               | Description                                                                                                                                                                                                 | Access |

| 4/5.32781.15:0  | Lane 1 end of packet error counter | End of packet termination error counter for lane 1. End of packet error for lane 1 is detected on the RX side. It is detected when Terminate character is in lane 1 and one or both of the following holds: | RO/COR |

|                 |                                    | Terminate character is not followed by /K/ characters in lanes 2 and 3                                                                                                                                      | ,      |

|                 |                                    | The column following the terminate column is neither   K   or   A  .                                                                                                                                        |        |

(1) Counter is incremented by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter holds on to its value when align\_status goes low or when the counter reaches its maximum value. It is cleared when it is read.

### Table 31. LANE 2 EOP ERROR COUNT<sup>(1)</sup>

| Address: 0x800E |                                    | Default: 0xFFFD                                                                                                                                                                                             |          |

|-----------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Bit(s)          | Name                               | Description                                                                                                                                                                                                 | Access   |

| 4/5.32782.15:0  | Lane 2 end of packet error counter | End of packet termination error counter for lane 2. End of packet error for lane 2 is detected on the RX side. It is detected when Terminate character is in lane 2 and one or both of the following holds: | RO/COR   |

|                 |                                    | Terminate character is not followed by /K/ characters in lane 3                                                                                                                                             | 110,0011 |

|                 |                                    | The column following the terminate column is neither   K   or   A  .                                                                                                                                        |          |

(1) Counter is incremented by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter holds on to its value when align\_status goes low or when the counter reaches its maximum value. It is cleared when it is read.

# Table 32. LANE\_3\_EOP\_ERROR\_COUNT<sup>(1)</sup>

| Address: 0x800F |                                    | Default: 0xFFFD                                                                                                                                                                                                                              |        |

|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                               | Description                                                                                                                                                                                                                                  | Access |

| 4/5.32783.15:0  | Lane 3 end of packet error counter | End of packet termination error counter for lane 3. End of packet error for lane 3 is detected on the RX side. It is detected when Terminate character is in lane 3 and the column following the terminate column is neither   K   or   A  . | RO/COR |

(1) Counter is incremented by 1 when EOP error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter holds on to its value when align\_status goes low or when the counter reaches its maximum value. It is cleared when it is read.

### Table 33. LANE\_0\_CODE\_ERROR\_COUNT<sup>(1)</sup>

| Address: 0x8010 |                           | Default: 0xFFFD                                                                                                                                          |        |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit(s)          | Name                      | Description                                                                                                                                              | Access |

| 4/5.32784.15:0  | Lane 0 code error counter | Output 16-bit counter for invalid code group found in lane 0. Invalid code group is detected when the 8B10B decoder cannot decode the received codeword. | RO/COR |

(1) Counter is incremented by 1 when codeword error is found on the corresponding lane and when all the lanes are aligned (align\_status should be high). Counter holds on to its value when align\_status goes low or when the counter reaches its maximum value. It is cleared when it is read.

# Table 34. LANE\_1\_CODE\_ERROR\_COUNT<sup>(1)</sup>

| Address: 0x8011 |                           | Default: 0xFFFD                                                                                                                                          |        |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|