# TMS320DM643 Digital Signal Processor Silicon Errata

Silicon Revision 2.0, 1.2

*SPRZ231A* March 2005 Revised August 2005

Copyright © 2005, Texas Instruments Incorporated

## **REVISION HISTORY**

This silicon errata revision history highlights the technical changes made to the SPRZ231 revision to make it an SPRZ231A revision.

**Scope:** Applicable updates to the C64x device family, specifically relating to the DM643 device, have been incorporated. Differences between the actual silicon revisions 2.0 and earlier specification values and the data sheet values specified in the *TMS320C643 Video/Imaging Fixed-Point Digital Signal Processor* data manual (literature number SPRS269 or higher) have been documented. Updated values for the A-500 (extended temperature) device have also been incorporated. Added the device-specific information supporting the **TMS**320DM643 silicon revisions 2.0, 1.2, 1.1, and 1.0 devices, which are in the production data (PD) stage of development.

TMS320DM643 silicon revision 2.0 orderables are designated with "A" (e.g., TMS320DM643<u>A</u>GNZ5 for -500 MHz speed).

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6              | Moved "L1P Cache: Incorrect Update of the L1P Tag RAMs (All 64x Devices)" Usage Note to Silicon Revision 2.0 Usage Note section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7–12           | Moved/updated the following advisories to Silicon Revision 2.0 Known Design Exceptions to Functional Specifications section:<br>Advisory 1.2.2 – I2C: Bus Busy Bit Does Not Reflect the State of the I2C Bus When the I2C is in Reset<br>Advisory 1.2.3 – I2C: Addressed-As-Slave (AAS) Bit is not Cleared Correctly<br>Advisory 1.2.4 – EMAC: Multi-Channel Mode Ignores Writes to Interrupt Acknowledgement Register<br>Advisory 1.2.5 – Video Port: Y/C Edge Pixel Bug/Mode Filtering Bug<br>Advisory 1.2.6 – Video Port: Capture Mode Event Pre-Generation Bug<br>Advisory 1.2.7 – EMIF: Data Corruption can Occur in SDRAM When HOLD Feature is Used<br>Advisory 1.2.8 – EMIF: PDT Write Transfers Fail When PDTWL Equals 3<br>Advisory 1.2.13 – EMIF: PDT Transfers Fail When Accessing the Same SDRAM Page as Non–PDT Transfers<br>Advisory 1.2.14 – Video Port: Ancillary Data Header Clipped When Using BT.656 or Y/C Mode |

## Contents

| Introduction     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Device and   | Development-Support Tool Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                        | . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2 Revision Ide | entification                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Silicon Revisior | n 2.0 Known Design Exceptions to Functional Specifications and Usage Notes                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1 Usage Note   | es for Silicon Revision 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •                |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.0.4   | Video Port: Y/C Edge Pixel Bug/Mode Filtering Bug                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.0.5   | Video Port: Capture Mode Event Pre-Generation Bug                                                                                                                                                                                                                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Advisory 2.0.6   | EMIF: Data Corruption can Occur in SDRAM When HOLD Feature is Used                                                                                                                                                                                                                                                                                                                                                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Advisory 2.0.7   | EMIF: PDT Write Transfers Fail When PDTWL Equals 3                                                                                                                                                                                                                                                                                                                                                                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Advisory 2.0.8   | EMIF: PDT Transfers Fail When Acessing the Same SDRAM Page as                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.0.9   | Video Port: Ancillary Data Header Clipped When Using BT.656 or Y/C Mode                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1 Usage Note   | es for Silicon Revision 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2 Silicon Rev  | ision 1.2 Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Advisory 1.2.1   | EMU: Data Corruption With RTDX and Real-Time Emulation Memory Read                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Advisory 1.2.9   | EMIF: Programmable Synchronous Interface AC Timings Differ                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •                |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ,                |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 1.2.12  | L2 Cache: L2 Controller Incorrectly Updates LRU for Accesses in L2 Cache                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | <ul> <li>1.1 Device and</li> <li>1.2 Revision Id</li> <li>Silicon Revision</li> <li>2.1 Usage Note<br/>L1P Cache</li> <li>2.2 Silicon Revision</li> <li>Advisory 2.0.1</li> <li>Advisory 2.0.2</li> <li>Advisory 2.0.3</li> <li>Advisory 2.0.4</li> <li>Advisory 2.0.5</li> <li>Advisory 2.0.6</li> <li>Advisory 2.0.7</li> <li>Advisory 2.0.8</li> <li>Advisory 2.0.9</li> <li>Silicon Revision</li> <li>3.1 Usage Note</li> <li>3.2 Silicon Rev</li> </ul> | 1.2       Revision Identification         Silicon Revision 2.0 Known Design Exceptions to Functional Specifications and Usage Notes          2.1       Usage Notes for Silicon Revision 2.0          L1P Cache: Incorrect Update of the L1P Tag RAMs (All C64x Devices)          2.2       Silicon Revision 2.0 Known Design Exceptions to Functional Specifications          Advisory 2.0.1       I2C: Bus Busy Bit Does Not Reflect the State of the I2C Bus When the I2C is in Reset          Advisory 2.0.2       I2C: Addressed-As-Slave (AAS) Bit is not Cleared Correctly          Advisory 2.0.3       EMAC: Multi-Channel Mode Ignores Writes to Interrupt Acknowledgement Register          Advisory 2.0.4       Video Port: Y/C Edge Pixel Bug/Mode Filtering Bug          Advisory 2.0.5       Video Port: Capture Mode Event Pre-Generation Bug          Advisory 2.0.6       EMIF: Data Corruption can Occur in SDRAM When HOLD Feature is Used          Advisory 2.0.7       EMIF: PDT Write Transfers Fail When PDTWL Equals 3           Advisory 2.0.9       Video Port: Ancillary Data Header Clipped When Using BT.656 or Y/C Mode          Silicon Revision 1.2 Known Design Exceptions to Functional Specifications and Usage Notes           3.1       Usage Notes for Silicon Revision 1.2 |

## 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS320DM643 digital signal processor. [See the *TMS320DM643 Video/Imaging Fixed–Point Digital Signal Processor* data manual (literature number SPRS269).] Throughout this document, TMS320C64x and C64x refer to TMS320DM643.

For additional information, see the latest version of the *TMS320C6000 DSP Peripherals Overview Reference Guide* (literature number SPRU190).

The advisory numbers in this document are not sequential. Some advisory numbers have been moved to the next revision and others have been removed and documented in the user's guide. When items are moved or deleted, the remaining numbers remain the same and are not resequenced.

This document also contains "Usage Notes". Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

## 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (i.e. **TMS**320DM643GDK500). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- TMS Fully qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

- TMDS Fully qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

All trademarks are the property of their respective owners.

## 1.2 Revision Identification

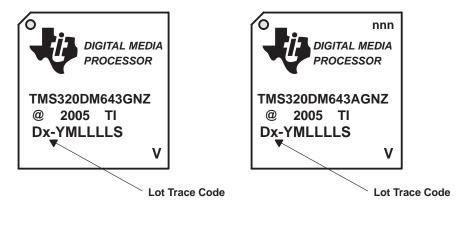

The device revision can be determined by the lot trace code marked on the top of the package. The location of the lot trace code for the GDK and GNZ packages are shown in Figure 1. Figure 1 shows *some* examples of the types of DM643 package symbolization for –500 MHz and –600 MHz devices.

"nnn" represents the device speed for the –500 MHz device **only**. For example: 500 = 1.2 V, 500-MHz Core, 100-MHz EMIF

NOTE: Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

## Figure 1. Example, Lot Trace Codes for TMS320DM643 (GDK and GNZ Packages)

Silicon revision is identified by a code on the chip. The code is of the format Dx-YMLLLLS. *If* x is "B", then the silicon is revision 1.2; if x is "C", then the silicon is revision 2.0, etc.

## Table 1. Lot Trace Codes

| Lot Trace Code<br>(x) | Silicon Revision | Comments     |

|-----------------------|------------------|--------------|

| С                     | 2.0              | TMS320DM643A |

| В                     | 1.2              | TMS320DM643  |

## 2 Silicon Revision 2.0 Known Design Exceptions to Functional Specifications and Usage Notes

## 2.1 Usage Notes for Silicon Revision 2.0

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

## L1P Cache: Incorrect Update of the L1P Tag RAMs (All C64x Devices)

On DM643 silicon revision 2.0, when the CPU is executing non-cacheable code from external memory and there is snoop activity from L2 to L1P occurring at the same time, an incorrect update to the L1P Tag RAM can occur.

Snoop activity from L2 to L1P can be generated two ways:

- 1. EDMA/QDMA activity to L2

- 2. Block cache invalidates initiated in L2

When there is a non-cacheable L1P fetch that is returned from L2 to L1P, **and** there is a snoop from L2 in the very next cycle, then the snoop tag read interferes with the tag/status RAM write for the non-cacheable data. This interference causes the tag RAMs to be incorrectly updated with the tag for that line, rather than discarding the write to the tags. When the NEXT access to that non-cacheable line in L2 occurs, the L1P incorrectly registers this as a hit and transfers data from the L1P rather than the desired external data.

To avoid an incorrect update of the L1P tag RAMs, do the following as best practice:

- 1. While executing code from non-cacheable space, *do not* perform either EDMA/QDMA transfers to L2 *or* block cache invalidates initiated in L2

- 2. Mark program code as cacheable as soon as possible.

6

## 2.2 Silicon Revision 2.0 Known Design Exceptions to Functional Specifications

| Advisory 2.0.1        | I2C: Bus Busy Bit Does Not Reflect the State of the I2C Bus When the I2C is in Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Details:              | The bus busy (BB) bit indicates the status of the I2C bus. The BB bit is set to "1" by a START condition (bus is busy) and set to "0" by a STOP condition (bus is free). The I2C peripheral cannot detect a START or STOP condition when it is in reset (IRS bit set to "0"); therefore, the BB bit will keep the state it was in when the I2C peripheral was placed in reset (when IRS bit is set to "0") instead of reflecting the actual I2C bus status. The BB bit stays in that state until the I2C peripheral is taken out of reset (IRS bit set to "1") and a START or STOP condition is detected on the I2C bus. When the device is powered up, the BB bit stays stuck at the default value of "0" until the IRS bit is set to "1" (taking the I2C peripheral out of reset). After the IRS bit is set to "1", the START or STOP condition can be captured in the BB bit. |  |

| Workaround:           | For multi-master systems, be aware that the BB bit does not reflect the bus status until the I2C peripheral is out of reset (IRS set to "1") and the first START or STOP condition is detected. Before initiating the first data transfer with the I2C peripheral, follow this sequence:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                       | <ol> <li>After taking the I2C peripheral out of reset (IRS bit set to "1"), wait a certain period to<br/>detect the actual bus status before starting the first data transfer. [The period should be<br/>set longer than the total time it takes for the longest data transfer in the application.]<br/>Waiting this amount of time after the I2C comes out of reset should ensure at least one<br/>START or STOP condition occurred on the I2C bus and captured by the BB bit. After this<br/>period, the BB bit will correctly reflect the state of the I2C bus.</li> </ol>                                                                                                                                                                                                                                                                                                    |  |

|                       | 2. Poll the BB bit and verify that BB = 0 (bus not busy) before proceeding to next step.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                       | 3. Begin data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                       | 4. Do not reset the I2C peripheral between transfers so that the BB bit reflects the actual bus status. If the I2C peripheral must be reset between transfers, repeat steps 1 through 3 <i>every</i> time the I2C peripheral is taken out of reset (IRS bit set to "1").                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                       | (Internal reference number: 1474)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Advisory 2.0.2        | I2C: Addressed-As-Slave (AAS) Bit is not Cleared Correctly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Details:              | The addressed-as-slave (AAS) bit indicates that the I2C peripheral has recognized its own slave address on the I2C bus. In normal (proper) operation for both 7- and 10-bit addressing modes, the AAS bit has the capability to know that its own I2C peripheral has been addressed as a slave and is now capable of transferring/receiving. Also, in normal operation for both addressing modes, the AAS bit is subsequently cleared by receiving a STOP condition <i>or</i> by a slave address different from the I2C peripheral's own slave address. |

|                       | Currently, in the 7-bit addressing mode, the AAS bit <i>is</i> cleared when receiving a NACK, a STOP condition, or a repeated START condition. The AAS bit currently is <i>not</i> cleared by receiving a slave address different from the I2C peripheral's own slave address.                                                                                                                                                                                                                                                                          |

|                       | Currently, in the 10-bit addressing mode, the AAS bit <i>is</i> cleared when receiving a NACK, a STOP condition, or by a slave address different from the I2C peripheral's own slave address. The AAS bit, in 10-bit addressing mode, is <i>not</i> cleared by a repeated START condition.                                                                                                                                                                                                                                                              |

|                       | For either address mode, the AAS bit is properly set when addressed as a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       | The only divergence from normal operation is how the AAS bit is cleared in either address modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround:           | None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                       | Note the AAS bit is set correctly when the I2C peripheral is addressed as a slave for both addressing modes. Also, take into account that when the AAS bit is cleared, the I2C peripheral is no longer addressed as a slave, regardless of addressing mode.                                                                                                                                                                                                                                                                                             |

|                       | (Internal reference number: 1483)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Advisory 2.0.3        | EMAC: Multi-Channel Mode Ignores Writes to Interrupt Acknowledgement Register                                                                                                                                                                                                                                                       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.0 and earlier                                                                                                                                                                                                                                                                                                                     |

| Details:              | This bug occurs in both TX and RX, when more than one channel is in use. Under multi-channel conditions, the EMAC can "miss" processor writes to the interrupt acknowledgement registers. The specific writes affected are to the RX[0–7]INTACK registers on multi-channel RX, and the TX[0–7]INTACK registers on multi-channel TX. |

|                       | Use of the EMAC in single-channel mode is not affected. When operating either TX or RX in multi-channel mode (but not the other), only the multi-channel operation is affected.                                                                                                                                                     |

| Workaround:           | One workaround is to use EMAC only in single-channel mode.                                                                                                                                                                                                                                                                          |

|                       | When using the EMAC in multi-channel mode, application software must verify writes to the RX[0–7]INTACK/TX[0–7]INTACK registers by checking that the corresponding bits in the MACINVECTOR register have been cleared. Alternatively, an application my be coded that is tolerant of receiving duplicate interrupts from the EMAC.  |

|                       | The ideal workaround approach is dependent on the software architecture. When using descriptor rings as circular queues, verifying the writes to the ACK registers is the cleanest and safest approach.                                                                                                                             |

|                       | When using the CSL HAL to develop driver software, programmers will need to mind this advisory. However, the CSL Ethernet MAC (EMAC) interface functions have the proper workarounds in place.                                                                                                                                      |

| Advisory 2.0.4        | Video Port: Y/C Edge Pixel Bug/Mode Filtering Bug                                                                                                                                                                                                                                                                                                                    |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.0 and earlier                                                                                                                                                                                                                                                                                                                                                      |

| Details:              | This error occurs under the following conditions:                                                                                                                                                                                                                                                                                                                    |

|                       | • Y/C 08-bit mode                                                                                                                                                                                                                                                                                                                                                    |

|                       | • Filter mode = 01 and 11 (1/2 scaling and 1/2 scaling with resampling)                                                                                                                                                                                                                                                                                              |

|                       | When capture window is NOT the entire active video                                                                                                                                                                                                                                                                                                                   |

|                       | Cr samples ONLY                                                                                                                                                                                                                                                                                                                                                      |

|                       | For the last Cr (right-hand-side edge pixel), a value of 80h is used instead of taking the next pixel from outside the captured window. This results in a maximum error or $\pm 3$ for the last Cr pixel.                                                                                                                                                            |

| Workaround:           | There are some potential software workarounds.                                                                                                                                                                                                                                                                                                                       |