#### 查询TPIC2101供应商

## 捷多邦,专业PCB打样工厂,24小时加急出货 TPIC2101 DC BRUSH MOTOR CONTROLLER

SLIS060 - OCTOBER 1995

#### description

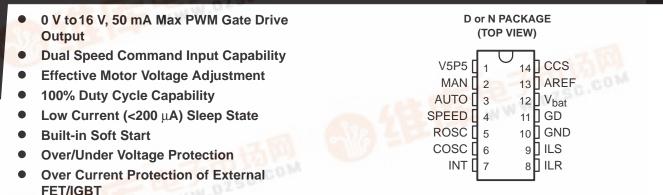

The TPIC2101 is a monolithic integrated control circuit designed for direct current (dc) brush motor control that generates a user-adjustable, fixed-frequency, variable duty cycle, pulse width modulated (PWM) signal primarily to control rotor speed of a permanent magnet dc motor. The TPIC2101 can also be used to control power to other loads such as solenoids and incandescent bulbs. This device drives the gate of an external, low side NMOS power transistor to provide PWM controlled power to a motor or other loads. Inductive current from motor or solenoid loads during PWM off-time is recirculated through an external diode.

The TPIC2101 accepts a 0% to 100% PWM signal (auto mode) or a 0 V to 2.2 V differential voltage (manual mode), and internally engages the correct operating mode to accept the input type.

The device operates in a sleep state, a run state, or a fault state. In the sleep state the gate-drive (GD) terminal is held low and the overall current draw is less than 200  $\mu$ A. The normal operating mode of the device is in the run state and is initiated by any speed command. When the device detects an overvoltage or current fault, it enters the fault state.

The TPIC2101 is offered in a 14-terminal plastic DIP (N) package, and a SOIC (D) package, and is characterized for operation over the operating free-air temperature range of  $-40^{\circ}$ C to  $105^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLIS060 - OCTOBER 1995

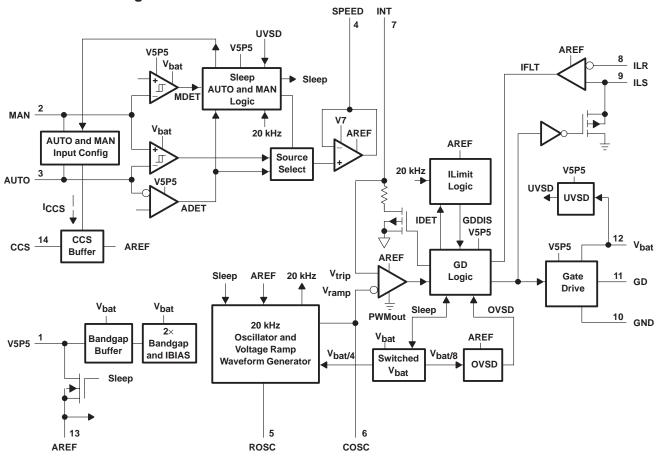

## functional block diagram

NOTE A: For correct operation, no terminal may be taken below GND.

SLIS060 - OCTOBER 1995

#### **Terminal Functions**

| TERMIN           | AL  |     | DECODIDATION                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME             | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

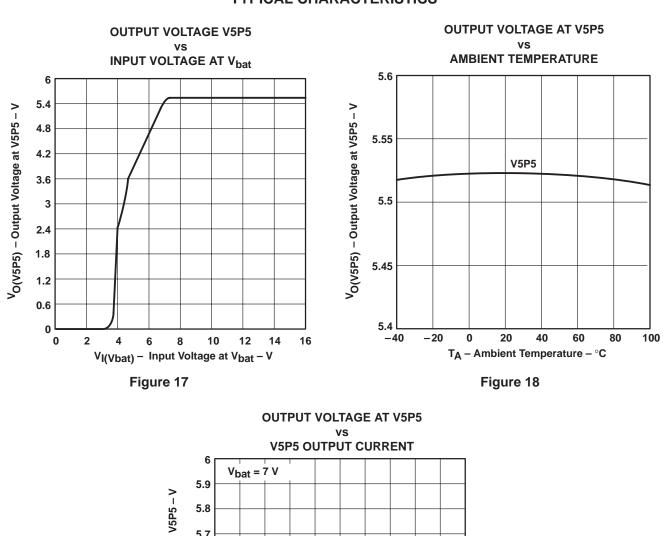

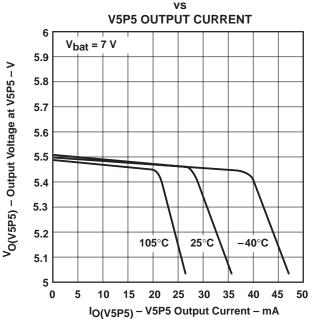

| V5P5             | 1   | 0   | 5.5 V supply voltage. V5P5 is a regulated voltage supply from V <sub>bat</sub> , internally switched to AREF during the run state. This requires a 4.7 $\mu$ F tantalum capacitor from V5P5 to GND for stability.                                                                                                                  |  |  |  |  |

| MAN              | 2   | I   | Manual control input. MAN is an active high (greater than 5.5 V asserts the manual mode) input that serves as a positive differential input (0-2.3 V full range) for the manual mode. In man mode, $I_{man}$ is approx. $20 \times I_{CCS}$ .                                                                                      |  |  |  |  |

| AUTO             | 3   | I   | PWM control input. AUTO is an active low input that remains active if pulsed every 2048 counts of the oscillator frequency. It also serves as a negative differential input for the manual mode. In auto mode, I <sub>auto</sub> is approx. 13×Iccs pullup, I <sub>auto</sub> is approx. 20×I <sub>ccs</sub> pulldown in man mode. |  |  |  |  |

| SPEED            | 4   | 0   | Integrator output. SPEED is an integrator output with a required minimum resistance between SPEED and INT terminals of 20 k $\Omega$ (typically 1 second RC time constant, or as required for soft start).                                                                                                                         |  |  |  |  |

| ROSC             | 5   | 0   | Oscillator resistor output. ROSC has an external resistor connected to ground which determines the constant charging current of COSC. The IC forces a voltage of $V_{bat}/4$ in run state.                                                                                                                                         |  |  |  |  |

| COSC             | 6   | 0   | Oscillator capacitor output. COSC has an external capacitor connected to ground which determines (with ROSC) switching frequency. $f(osc) = 2/(ROSC \times COSC)$                                                                                                                                                                  |  |  |  |  |

| INT              | 7   | I   | Integrator input. INT is an input from an integrator that requires a 4.7 $\mu$ F capacitor and a 20 k minimum resistance between the SPEED and INT terminals.                                                                                                                                                                      |  |  |  |  |

| ILR              | 8   | 1   | Current limit reference. ILR is an input from a resistor divider off AREF.                                                                                                                                                                                                                                                         |  |  |  |  |

| ILS              | 9   | 1   | Current limit sense. ILS senses drain voltage of external FET. ILS trips within ±10 mV of ILR.                                                                                                                                                                                                                                     |  |  |  |  |

| GND              | 10  |     | Ground terminal                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| GD               | 11  | 0   | Gate drive output. GD, PWM output, 0-V <sub>bat</sub> voltage, provides a 0-V <sub>bat</sub> PWM output pre-drive for an external FET.                                                                                                                                                                                             |  |  |  |  |

| V <sub>bat</sub> | 12  | I   | Positive power input.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| AREF             | 13  | 0   | 5.5 V reference voltage. AREF is a 5.5 V reference voltage switched from V5P5 during the run state. AREF is used as a reference for ILR in current limit detection and is capable of sourcing 2 mA of current.                                                                                                                     |  |  |  |  |

| CCS              | 14  |     | Constant current sink. ICCS equals AREF/(2×R <sub>CCS</sub> ). Requires an external resistor.                                                                                                                                                                                                                                      |  |  |  |  |

## recommended external components for auto and manual modes (see Figures 2 and 4)

| TERMINAL |     | DESCRIPTION                                                 |  |  |

|----------|-----|-------------------------------------------------------------|--|--|

| NAME     | NO. | DESCRIPTION                                                 |  |  |

| V5P5     | 1   | Capacitor – 4.7 μF tantalum                                 |  |  |

| MAN      | 2   | Capacitor – 0.1 μF                                          |  |  |

| MAN      | 2   | Resistor – 499 Ω, 1%, 100 ppm                               |  |  |

| AUTO     | 3   | acitor – 0.47 μF                                            |  |  |

| AUTO     | 3   | Resistor – 499 Ω, 1%, 100 ppm                               |  |  |

| SPEED    | 4   | stor – 100 kΩ, 1%, 100 ppm to INT terminal, (minimum 20 kΩ) |  |  |

| ROSC     | 5   | sistor – 45.3 k $\Omega$                                    |  |  |

| COSC     | 6   | pacitor – 2200 pF                                           |  |  |

| INT      | 7   | apacitor – 4.7 μF                                           |  |  |

| CCS      | 14  | esistor – 27.4 kΩ, 1%, 100 ppm                              |  |  |

#### SLIS060 - OCTOBER 1995

#### detailed description

The TPIC2101 is an integrated circuit that generates a fixed frequency, variable duty cycle PWM signal to control the rotor speed of a permanent-magnet dc motor. This section provides a functional description of the device.

#### dual command speed input capability

The TPIC2101 is user configurable to either auto or manual mode, and can sense either configuration internal to the IC. In automatic mode, the speed-command-signal is an open-collector PWM signal on the AUTO terminal, and the MAN terminal is floating. In manual mode, the speed-command-signal is a variable resistance across the AUTO and MAN terminals with the MAN terminal connected to V<sub>bat</sub>.

#### sleep, run, and fault states

The TPIC2101 operates in a sleep state, a run state, or a fault state. In the auto mode, a zero-speed input initiates the sleep state. In the manual mode, an open-circuit at the AUTO and MAN terminals initiates the sleep state. The device will also be in the sleep state during fault conditions. In the sleep state, the gate drive terminal (GD) is held low and the overall current draw is less than 200  $\mu$ A. Any speed command initiates the run state, which is the normal operating state of the device. The fault state is entered only when the device detects an overvoltage or current fault. Fault state is exited either by removal of the overvoltage condition (exiting to run state) or by resetting a current fault by entering the sleep state.

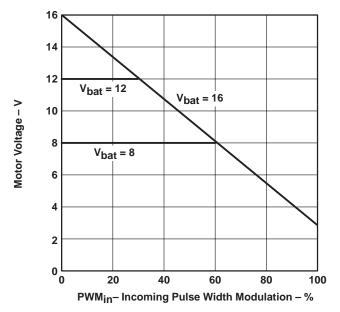

#### speed command adjustment

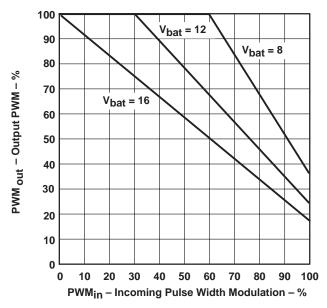

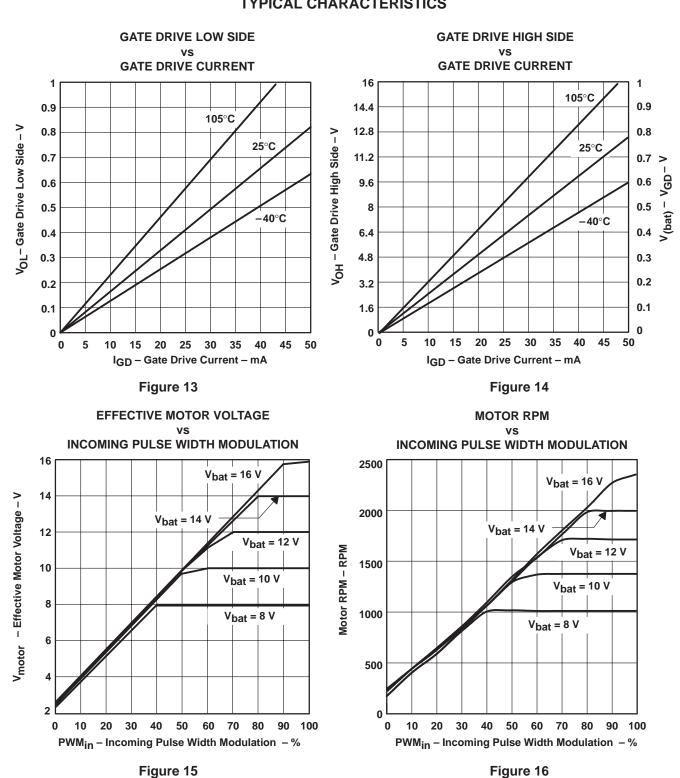

The device adjusts the GD terminal PWM signal with changes in  $V_{bat}$  to keep the effective motor voltage constant. The effective motor voltage is defined to be the product of the GD terminal PWM rate and the voltage of  $V_{bat}$ . Figure 1 shows motor voltage as a function of input speed command in the automatic mode for various battery voltages. PWM<sub>in</sub> is described as the duty cycle of the PWM signal at the AUTO terminal.

Figure 1. Motor Voltage vs. Incoming PWM for Various Battery Voltages

#### over/under voltage protection

The IC enters the fault state if  $V_{bat}$  rises above over-voltage shutdown ( $V_{OV}$  typically equals 18.5 V). If  $V_{bat}$  falls below the under-voltage shutdown ( $V_{UV}$  typically equals 7.5 volts) the IC enters sleep state. Hysteresis assures that the device will not toggle into and out of sleep state or fault condition.

#### current limit protection

Current through the motor is limited by lowering the GD terminal PWM when a high current situation occurs. If the condition persists, the device shuts off the gate drive (GD terminal) until the circuit is reset externally by entering the sleep state.

#### theory of operation

This section explains the normal circuit operation for the automatic and manual states.

#### power supply and oscillator

Positive voltage is supplied to the integrated circuit on the V<sub>bat</sub> terminal, ground is the GND terminal. The IC steps down the V<sub>bat</sub> supply to the regulated 5.5 V supply at the V5P5 terminal. AREF is shorted to V5P5 in run state and disconnected when the IC is in sleep state. Two terminal connections (COSC and ROSC) are provided to control an internal oscillator. The oscillator freq,  $f_{(OSC)}$ , is defined by the following equation:

$$f_{(OSC)} = \frac{2}{ROSC \times COSC}$$

Nominal oscillator frequency is 20-kHz based on the recommended components.

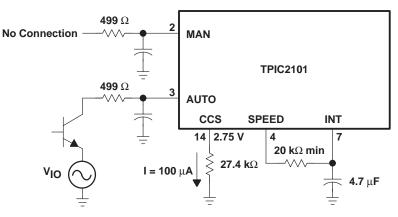

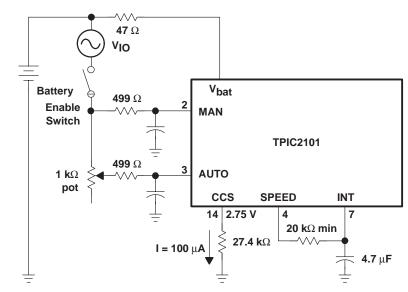

#### automatic mode signal decoding

In automatic state, a high-to-low signal transition on the AUTO terminal (open collector) will wake the device from the sleep state into the run state. The speed command information is contained in the duty cycle of a 100 Hz PWM signal on the same terminal. The speed information is inverted, i.e. a signal that is 10% high commands a faster speed than a 20% high signal. In automatic mode the MAN terminal is floating. The device is capable of rejecting  $\pm$  2 V of ground offset V<sub>IO</sub> between the open-collector switching transistor and the GND terminal without affecting the output duty cycle. Two terminals are provided for an RC integrator (SPEED and INT) to average the incoming PWM signal for use as a PWM comparator input. Figure 2 illustrates the automatic state connections.

Figure 2. Automatic Mode Connections

SLIS060 - OCTOBER 1995

#### automatic mode signal decoding (continued)

The device enters the sleep state if the PWM signal on the AUTO terminal is absent (the AUTO terminal remains high or low) for 2048 clock cycles of the 20 KHz oscillator. An internal 1 mA pull-up resistor is provided for the AUTO terminal when in the auto mode. This pull-up resistor is not present in the manual mode or during sleep state.

The device adjusts the output PWM duty cycle to keep the effective motor voltage constant with changing battery voltages ( $V_{bat}$ ) as per the equation:

$$PWM_{out} = \frac{(2.88 + 13.12(1 - Input Duty Cycle))}{V_{bat}} \times 100\%$$

Figure 3 illustrates this transfer curve with various battery voltages.

Figure 3. Output PWM vs. Incoming PWM for Various Battery Voltages

The allowable automatic mode  $\text{PWM}_{out}$  variation is  $\pm\,7\%$  over all operating conditions as indicated in the AC characteristics Table.

#### manual mode speed signal decoding

In manual mode, a high input (>5.5V) on the MAN terminal changes the state of the device from sleep to run. While in the run state the device senses the resistance between the MAN and AUTO terminals by turning on a 2 mA current sink to each terminal. The MAN and AUTO current sinks are multiplied 20 X from the CCS current. This 2 mA current sink creates a 1 V drop across each 0.5 k $\Omega$  resistor and a 0 to 2.2 V differential across the 0 to 1 k $\Omega$  potentiometer (and thus across the 2 terminals). The SPEED and INT terminals should be utilized as in the proceeding section as a low-pass filter. When the connection to the MAN terminal is opened, the device enters the sleep state. In addition, the device is capable of rejecting up to 2.2 V of source voltage offset (V<sub>IO</sub>), as indicated in Figure 4.

SLIS060 - OCTOBER 1995

#### manual mode speed signal decoding (continued)

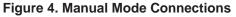

As in the automatic mode, the device will adjust the GD terminal PWM duty cycle to keep the effective motor voltage constant with changing battery voltages (V<sub>bat</sub>). The transfer equation for the manual mode is:

$$PWM_{out} = \frac{(2.88 + 6.56(V_{MAN} - V_{AUTO}))}{V_{bat}} \times 100\%$$

Figure 5 shows the output characteristic for various source voltages.

Figure 5. Manual Mode Input Signal vs. Output PWM

The allowable manual mode  $PWM_{out}$  variation is  $\pm 7\%$  over all operating conditions as indicated in the AC characteristics table.

#### SLIS060 - OCTOBER 1995

#### over/under voltage operating

The TPIC2101 detects an over or under voltage condition (on the V<sub>bat</sub> terminal) and turns off the gate drive circuit. The device remains in this condition until the supply voltage returns to normal operating voltage. Hysteresis assures that the over/under voltage condition does not toggle off and on near the threshold. The INT terminal pulls toward GND through an internal impedance of less than 500  $\Omega$  during the over-voltage condition or during sleep state. This ensures a slow ramp up of the GD terminal PWM when the V<sub>bat</sub> voltage returns to the operating range.

#### current limit operation

An over-current condition is detected if the ILS terminal is higher than the ILR terminal while the gate drive (GD terminal) is high. This condition activates a closed-loop control, causing the INT terminal to be pulled low (through an internal resistance less than 500  $\Omega$ ) lowering the commanded duty cycle to close the loop.

#### current fault operation

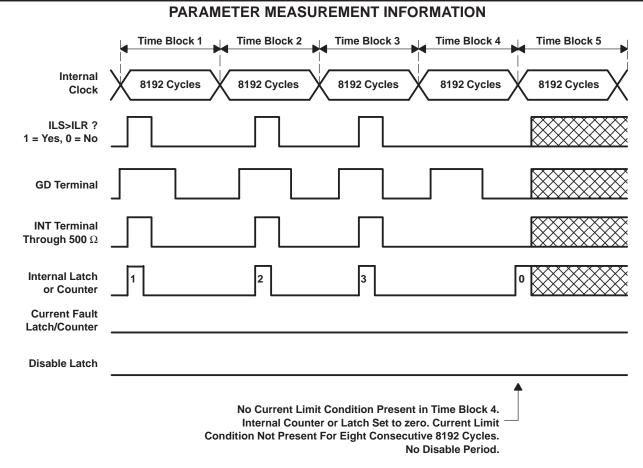

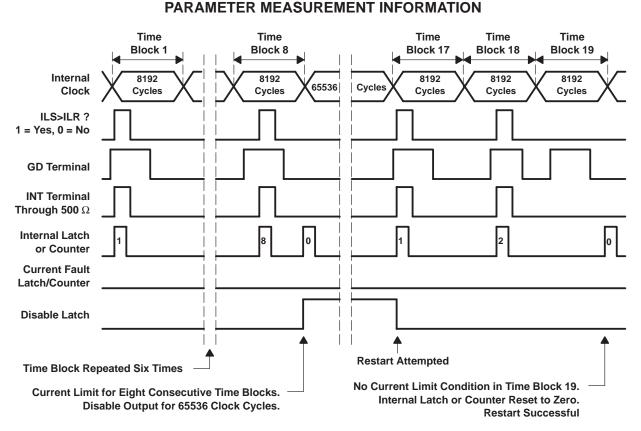

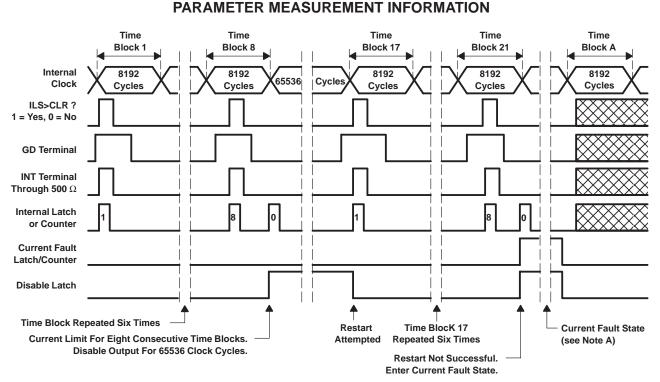

During a window of 8192 clock cycles, a latch is set if at least once during the window, a current limit condition is detected. If a current limit condition is set for eight consecutive 8192 clock cycle windows, the gate drive (GD terminal) will be shut off for a disable period of 65536 clock cycles. During the disable period, the INT terminal is pulled to GND through an internal resistance of less than 500  $\Omega$ . After the disable period is completed, an internal restart is attempted. If the current limit is present again, as described above, for 8 consecutive windows, the GD and INT terminals are again pulled to GND and the device remains in this current fault state until the device is cycled through a sleep state to run state. However, if the current limit condition is not present during any of the eight 8192 clock cycle windows, the latches for the 8 count window timer and the two cycle shutdown/restart are reset. See timing diagrams, Figures 6, 7, and 8.

# absolute maximum ratings over the operating free-air temperature range (unless otherwise noted) $\!\!\!^\dagger$

| Supply voltage range, V <sub>bat</sub> ‡                                  | 0 V |

|---------------------------------------------------------------------------|-----|

| Input voltage range, MAN, AUTO                                            |     |

| Input voltage range, INT CCS_ILR0.3 V to                                  |     |

| Continuous gate drive output current, I <sub>GD</sub> ±50                 | mΑ  |

| Continuous speed output current, I <sub>O(SPEED)</sub> ±1                 |     |

| Continuous output current, I <sub>O(V5P5)</sub> , I <sub>O(AREF)</sub> 20 |     |

| Continuous ROSC output Current, I <sub>O(ROSC)</sub> 1                    | mΑ  |

| Continuous output current, I <sub>O(CCS)</sub> 500                        | μΑ  |

| Thermal Resistance, junction to ambient, R <sub>OJA</sub> : D package     | :/W |

| N package                                                                 |     |

| Operating free-air termperature range, T <sub>A</sub> –40°C to 105        | 5°C |

| Maximum junction temperature, T <sub>JM</sub>                             | )°C |

| Storage temperature range, T <sub>stg</sub> –65°C to 150                  |     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> Under load dump conditions, the voltage on  $V_{bat}$  can reach 40 V within 1 ms.

SLIS060 - OCTOBER 1995

## recommended operating conditions

|                                                                     | MIN  | NOM  | MAX  | UNIT |

|---------------------------------------------------------------------|------|------|------|------|

| Supply voltage, V <sub>bat</sub>                                    | 8    | 12   | 16   | V    |

| AREF Input current I(AREF)                                          | 0    |      | 2    | mA   |

| Input voltage, VI(MAN), VI(AUTO) (manual mode)                      | 6    |      | 16   | V    |

| Differential voltage, V <sub>I(MAN)</sub> – V <sub>I(AUTO)</sub>    | 0    |      | 2.2  | V    |

| Input voltage, V <sub>I(AUTO)</sub> (auto mode)                     | 0    |      | 5.5  | V    |

| V <sub>I</sub> , ILR, ILS                                           | 0.5  |      | 2.75 | V    |

| Output resistance, input resistance, R <sub>(CCS)</sub>             | 27.2 | 27.5 | 27.8 | kΩ   |

| Output Resistance, ROSC, r <sub>o</sub>                             | 20   |      | 100  | kΩ   |

| Output Capacitance, COSC, CO                                        | 1    |      | 5    | nF   |

| Gate drive frequency f = $2/(ROSC \times COSC)$ , f <sub>(GD)</sub> |      | 20   |      | kHz  |

| Gate drive output capacitance, C <sub>O(GD)</sub>                   |      |      | 3300 | pF   |

| Operating free-air temperature, T <sub>A</sub>                      | -40  |      | 105  | °C   |

SLIS060 - OCTOBER 1995

## electrical characteristics, $V_{bat}$ = 8 V to 16 V, $T_A$ = 25°C

|                      | PARAMETER                                                                      | TEST CONDITION                                                                                                                                      | MIN   | TYP | MAX   | UNIT |

|----------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                      |                                                                                | $V_{bat} = 16 V,$ GD open,<br>f(osc) = 20 kHz,<br>MAN = AUTO = $V_{bat}$                                                                            |       | 4   | 10    | mA   |

| l <sub>bat</sub>     | Supply current (average), V <sub>bat</sub>                                     | V <sub>bat</sub> = 16 V, GD open,<br>f(osc) = 20 kHz, MAN open,<br>Auto mode,<br>AUTO – 99% PWM <sub>in</sub>                                       |       | 2   | 10    | mA   |

| I <sub>bat</sub> (Q) | Quiescent current (sleep state), V <sub>bat</sub>                              | V <sub>bat</sub> = 13 V,<br>AUTO and MAN open                                                                                                       |       | 150 | 200   | μΑ   |

| 'bat(Q)              | daloscom our on chore state), "Dat                                             | V <sub>bat</sub> = 13 V,<br>AUTO shorted to MAN, floating                                                                                           |       | 165 | 200   | μΑ   |

| V(AREF)              | Voltage supply regulation, AREF                                                | $I_{(AREF)} = 0 - 2 \text{ mA},$<br>MAN = AUTO = V <sub>bat</sub>                                                                                   | 5.225 | 5.5 | 5.775 | V    |

| V <sub>IO</sub>      | Input offset voltage, current limit comparator, ILS, ILR                       | AUTO or MAN mode, ILS,<br>ILR common mode,<br>Voltage range $0.5 - 2.75$ V,<br>V <sub>int</sub> = 4.5 V,<br>Detect I <sub>(int)</sub> > 100 $\mu$ A |       |     | 10    | mV   |

| IIB                  | Input bias current, current limit comparator, ILS, ILR $^{\dagger,}$           | ILS, ILR common mode,<br>Voltage range 0.5 – 2.75 V                                                                                                 |       |     | 250   | nA   |

| IIO                  | Input offset current, current limit comparator, ILS, ILR $\!\!\!\!\!\!\dagger$ | ILS, ILR common mode,<br>Voltage range 0.5 – 2.75 V                                                                                                 |       |     | 100   | nA   |

| IOL(CLS)             | Pulldown current, ILS terminal<br>blanking, ILS                                | ILS = 100 mV,<br>GD commanded low                                                                                                                   | 250   | 360 |       | μΑ   |

| VIL(AUTO)            | Automatic mode low level input voltage, AUTO                                   | MAN open, AUTO mode,<br>Lower V <sub>I(AUTO)</sub> until V <sub>I</sub> (SPEED) >2.4V                                                               | 2.7   | 3   | 3.3   | V    |

| VIH(AUTO)            | Automatic mode high level input voltage, AUTO                                  | MAN open, AUTO mode,<br>Raise V <sub>I(AUTO)</sub> until V <sub>I(SPEED)</sub> < 2.4 V                                                              | 3.6   | 4   | 4.4   | V    |

| II(AUTO)             | Input current, automatic mode, AUTO                                            | MAN open, Auto mode,<br>VI(AUTO) = 0 V                                                                                                              | -1    |     | -10   | mA   |

| II(AUTOQ)            | Input current, auto sleep mode, AUTO                                           | MAN open, Sleep state,<br>VI(AUTO) = 0 V                                                                                                            | -40   | -80 |       | μΑ   |

| VIH(MAN)             | High level input voltage, manual mode, MAN                                     |                                                                                                                                                     | 5     | 5.5 | 6     | V    |

| VIL(MAN)             | Low level input voltage, manual mode, MAN                                      | VI(MAN) <sup>=V</sup> I( AUTO),<br>Lower VI(MAN) until VI(AREF) < 2.5 V                                                                             | 2.3   | 2.5 | 2.7   | V    |

| VID(MAN)             | Input voltage, manual mode high differential (high speed command), MAN-AUTO    | $V_{bat} = 16 V,$<br>$V_{bat} - 3.5 V < MAN < V_{bat}$                                                                                              | 1.7   |     | 2.3   | V    |

<sup>†</sup> Indicates electrical parameter not tested in production.

SLIS060 - OCTOBER 1995

|                                             | PARAMETER                                                                       | TEST CO                                                                                                                                                                                                                                                           | NDITION                                             | MIN                   | TYP  | MAX              | UNIT |

|---------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------|------|------------------|------|

| V <sub>ID(low)</sub>                        | Input voltage, manual mode<br>low differential (low speed<br>command), MAN–AUTO | $ \begin{array}{l} V_{bat} - 3.5 \ V < MAN < V_{bat} + \Delta V \\ \text{where ``\Delta'' is the lesser of 2 V and 16 V } - V_{bat}, \\ \text{PWM}_{out} @ \ V_{(diff)} = 0.2 \ V \geq \text{PWM}_{out} @ \\ V_{I}(\text{DIFF}) = 0 \ V \end{array} $             |                                                     |                       |      | 0.2              | V    |

| <sup>I</sup> I(MAN)<br><sup>I</sup> I(AUTO) | Input currents, auto and manual mode, MAN, AUTO                                 | $ \begin{array}{l} V_{bat} - 3.5 \ V < MAN < V_{bat} + \Delta V \\ \text{where "}\Delta\text{" is the lesser of 2 V and 16 V } - V_{bat}, \\ \text{MAN} - AUTO = 0 \ V \text{ to 2 V}, \\ R_{(\text{CSS})} = 27.5 \ \texttt{k}\Omega \text{ to GND} \end{array} $ |                                                     | 1.70                  | 2    | 2.30             | mA   |

| I(MANRATIO)                                 | Input current, manual mode matching ratio, MAN, AUTO                            | $ \begin{array}{l} V_{bat} \ -3.5 \ V < MAN < V_{bat} \ +\DeltaV \\ \text{where ``\Delta'' is the lesser of 2 V and 16 V -V_{bat}, \\ \text{MAN} - AUTO = 0 \ V \ \text{to 2 V}, \\ R_{\text{CSS}} = 27.5 \ \mathrm{k\Omega} \ \text{to GND} \end{array} $        |                                                     | -7                    |      | 7                | %    |

| li(MAN(a))                                  | Input current, man terminal auto mode, MAN                                      | Auto mode,                                                                                                                                                                                                                                                        | MAN = 2.2 V                                         | 5                     | 10   | 15               | μΑ   |

| li(MANQ)                                    | Input current, man terminal sleep mode, MAN                                     | Sleep state,                                                                                                                                                                                                                                                      | MAN = 2.2 V                                         | 5                     | 10   | 15               | μΑ   |

| V(CCS)                                      | Constant current sink voltage regulation, CCS                                   | Auto or Man mode,                                                                                                                                                                                                                                                 | I(CCS) = -100 μA                                    | 2.58                  | 2.78 | 2.92             | V    |

| V <sub>(OV)</sub>                           | Over voltage shutdown, $V_{bat}$                                                | V <sub>bat</sub> rising from 16 V,<br>Detect I <sub>(INT)</sub> > 100 μA                                                                                                                                                                                          | INT = 1 V,                                          | 17                    | 18.5 | 20               | V    |

| V <sub>hys(OV)</sub>                        | Hysteresis, over voltage, V <sub>bat</sub>                                      | $V_{bat}$ rising from 20.1 V,<br>Detect I <sub>(INT)</sub> < 100 $\mu$ A                                                                                                                                                                                          | INT = 1 V,                                          | 0.5                   | 0.8  | 0.99             | V    |

| VIT-(UVLO)                                  | Under voltage shutdown<br>negative going threshold<br>voltage, V <sub>bat</sub> | MAN = V <sub>bat</sub> ,<br>Detect AREF < 2.5 V                                                                                                                                                                                                                   | V <sub>bat</sub> falling from 9 V,                  | 7                     | 7.5  | 8                | V    |

| VIT+(UVHI)                                  | Under voltage shutdown<br>positive going threshold<br>voltage, V <sub>bat</sub> | MAN = V <sub>bat</sub> ,<br>Detect AREF > 2.5 V                                                                                                                                                                                                                   | V <sub>bat</sub> rising from 6.9 V,                 | 8                     | 8.5  | 9                | V    |

| V <sub>hys(UV)</sub>                        | Hysteresis, under voltage, Vbat                                                 | V(UVHI) - V(UVLO)                                                                                                                                                                                                                                                 |                                                     | 0.5                   | 1    |                  | V    |

| Variation                                   | High level output voltage, gate                                                 | I <sub>GD</sub> = −50 mA,<br>Run state                                                                                                                                                                                                                            | INT = 4.5 V,                                        | V <sub>bat</sub> -3   |      | V <sub>bat</sub> | V    |

| VOH(GD)                                     | drive, GD                                                                       | I <sub>GD</sub> = −2 mA,<br>Run state                                                                                                                                                                                                                             | INT = 4.5 V,                                        | V <sub>bat</sub> -0.2 |      | V <sub>bat</sub> | V    |

| Valuasi                                     | Low level output voltage, gate                                                  | Run state,<br>VI(INT) = 0 V,                                                                                                                                                                                                                                      | I <sub>GR</sub> = 50 mA,<br>V <sub>COSC</sub> = 1 V |                       |      | 3.5              | V    |

| VOL(GD)                                     | drive, GD                                                                       | Run state,<br>INT = 0 V,                                                                                                                                                                                                                                          | I <sub>GD</sub> = 2 mA,<br>V <sub>COSC</sub> = 1 V  |                       |      | 0.75             | V    |

| VGD(SL)                                     | Gate voltage, sleep-state, GD                                                   | Sleep state,                                                                                                                                                                                                                                                      | I <sub>GD</sub> = 2 mA                              |                       | 0.03 | 0.75             | V    |

| I(GDP)                                      | Pulldown current, gate drive<br>passive, GD                                     | V <sub>bat</sub> open,                                                                                                                                                                                                                                            | V <sub>GD</sub> = 0.75 V                            | 7.5                   | 20   |                  | μΑ   |

| I <sub>(INT)</sub>                          | Pulldown current, INT                                                           | Run state,<br>V <sub>I(INT)</sub> = 1 V                                                                                                                                                                                                                           | $V_{ILS} > V_{ILR},$                                | 2                     | 3    |                  | mA   |

## electrical characteristics, $V_{bat} = 8 V$ to 16 V, $T_A = 25^{\circ}C$ (continued)

SLIS060 - OCTOBER 1995

## switching characteristics, $V_{bat} = 8 V$ to 16 V, $T_A = 25^{\circ}C$

|                    | PARAMETER                                     | TEST CONDITIONS                                                                                                                                                            | MIN      | TYP | MAX | UNIT |

|--------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----|------|

| t <sub>r</sub>     | Rise time                                     | $V_{bat} = 16 V$ , Load = 3300 pF,<br>ROSC = 45.3 k $\Omega$ , COSC = 2200 pF                                                                                              |          |     | 1   | μs   |

| t <sub>f</sub>     | Fall time                                     | $V_{bat} = 16 V$ , Load = 3300 pF,<br>ROSC = 45.3 k $\Omega$ , COSC = 2200 pF                                                                                              |          |     | 0.8 | μs   |

|                    | Output PWM absolute accuracy to spec equation | $\begin{array}{l} 16 > V_{bat} > 9 \qquad \mbox{Manual and automatic modes} \\ \mbox{GD open,} \\ \mbox{Measure at GD} = 0.5 \times V_{bat} @ 20 \ \mbox{kHz} \end{array}$ | s<br>_7% |     | 7%  |      |

| f <sub>(osc)</sub> | Oscillator frequency                          | $ROSC = 45.3 \text{ k}\Omega$ , $COSC = 2200 \text{ pF}$                                                                                                                   | 19       | 20  | 21  | kHz  |

|                    |                                               | $MAN = AUTO = V_{bat} = 16$                                                                                                                                                | 15       |     | 21  | %DC  |

|                    | Minimum speed pedestal                        | V <sub>bat</sub> = 16, MAN floating,<br>AUTO @ 99% duty cycle                                                                                                              | 15       |     | 21  | %DC  |

Figure 6. Current Fault Timing Diagram, Normal State

SLIS060 - OCTOBER 1995

Figure 7. Current Fault Timing Diagram, Over-Current Limit Condition

SLIS060 - OCTOBER 1995

NOTE A: The integrated circuit remains in this state until cycled through the sleep state into the run state. Timing resumes as shown in time block A at right.

SLIS060 - OCTOBER 1995

SLIS060 - OCTOBER 1995

TEXAS

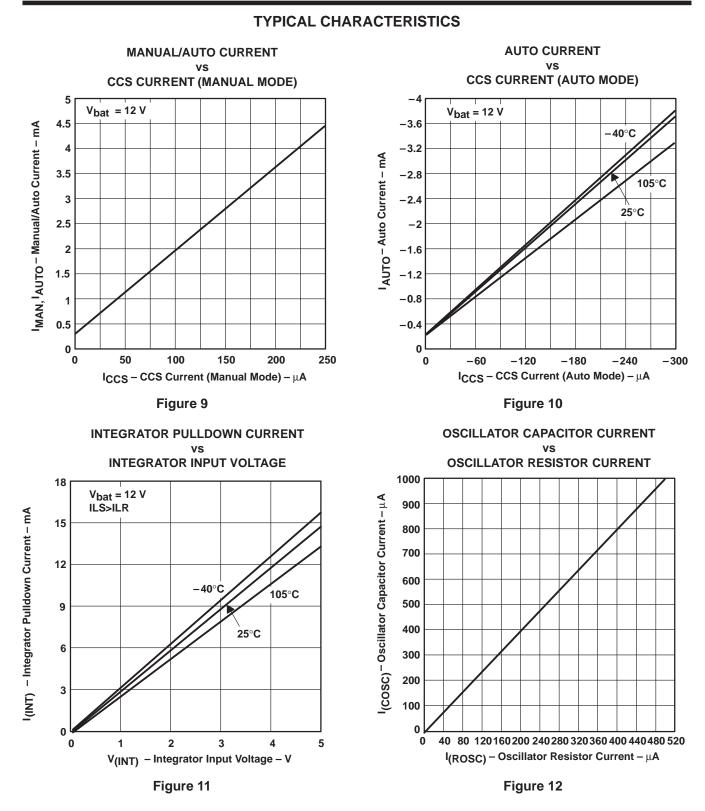

**TYPICAL CHARACTERISTICS**

SLIS060 - OCTOBER 1995

**TYPICAL CHARACTERISTICS**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated