SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

- Fully Supports Provisions of IEEE 1394-1995 Standard for High Performance Serial Bus

- Fully Interoperable with FireWire<sup>™</sup> and i.LINK<sup>™</sup> Implementation of IEEE 1394-1995

- Provides Three Fully Compliant Cable Ports at 100/200 Megabits per Second (Mbits/s)

- Cable Ports Monitor Line Conditions for Active Connection to Remote Node

- Device Power-Down Feature to Conserve Energy in Battery-Powered Applications

- Inactive Ports Disabled to Save Power

- Logic Performs System Initialization and Arbitration Functions

- Encode and Decode Functions Included for Data-Strobe Bit-Level Encoding

- Incoming Data Resynchronized to Local Clock

- Single 3.3-V Supply Operation

- Interface to Link-Layer Controller Supports Low Cost TI<sup>™</sup> Bus-Holder Isolation

- Data Interface to Link-Layer Controller Provided Through 2/4 Parallel Lines at 49.152 MHz

- Low Cost 24.576-MHz Crystal Oscillator and PLL Provide Transmit/Receive Data at 100/200 Mbits/s, and Link-Layer Controller Clock at 49.152 MHz

- Interoperable with 1394 Link-Layer Controllers Using 5-V Supplies

- Interoperable Across 1394 Cable with 1394 Physical Layers (Phy) Using 5-V Supplies

- Node Power-Class Information Signaling for System Power Management

- Cable Power Presence Monitoring

- Separate Cable Bias and Driver Termination Voltage Supply for Each Port

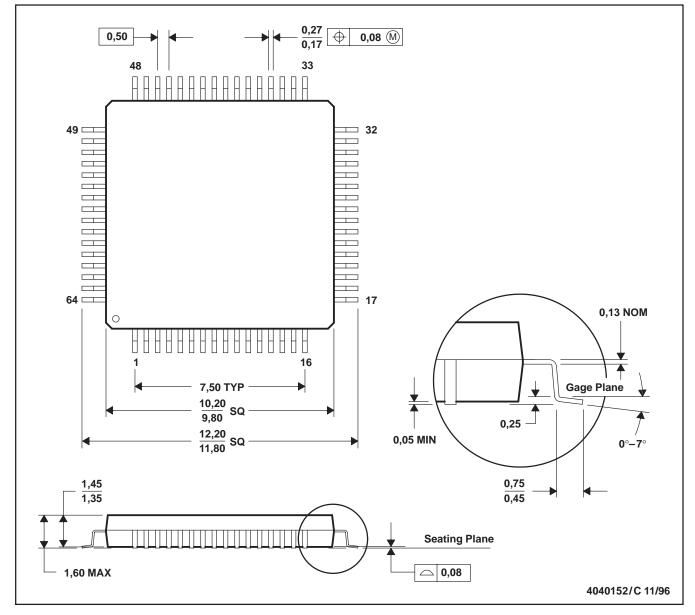

- High Performance 64-Pin TQFP (PM) Package and 68-Pin CFP (HV) Package

### description

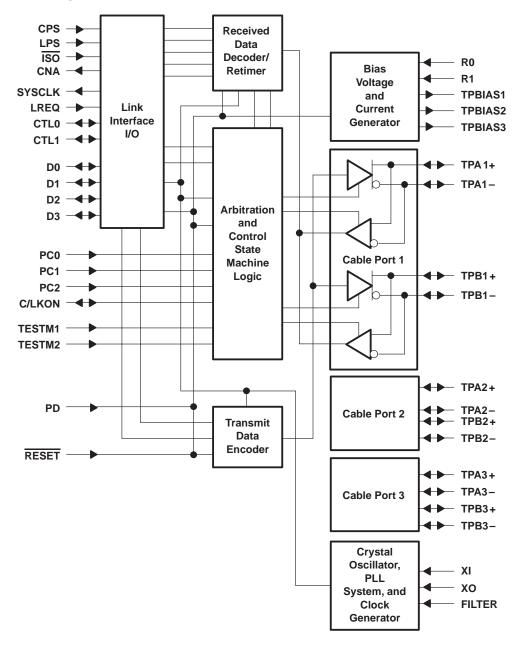

The TSB21LV03C provides the analog and digital physical layer functions needed to implement a three-port node in a cable-based IEEE 1394-1995 network. Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The TSB21LV03C is designed to interface with a link-layer controller (LLC), such as the TSB12LV21, TSB12LV31, TSB12C01, TSB12LV22, TSB12LV41, or TSB12LV01.

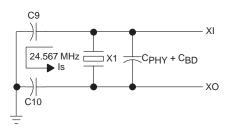

The TSB21LV03C requires either an external 24.576-MHz crystal or crystal oscillator. The internal oscillator drives an internal phase-locked loop (PLL), which generates the required 196.608-MHz reference signal. The 196.608-MHz reference signal is internally divided to provide the 49.152/98.304-MHz clock signals that control transmission of the outbound encoded strobe and data information. The 49.152-MHz clock signal is also supplied to the associated LLC for synchronization of the two chips and is used for resynchronization of the received data. For the TSB21LV03C, the 49.152 MHz clock output is active when RESET is asserted low. The power-down function, when enabled by taking the PD terminal high, stops operation of the PLL and disables all circuitry except the cable-not-active signal circuitry.

The TSB21LV03C supports an optional isolation barrier between itself and its LLC. When  $\overline{ISO}$  is tied high, the link interface outputs behave normally. Also, when  $\overline{ISO}$  is tied high, the internal bus hold function is enabled for use with the TI Bus Holder isolation. TI bus holder isolation is implemented when  $\overline{ISO}$  is tied high.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

FireWire is a trademark of Apple Computer, Incorporated. i.LINK is a trademark of SONY. TI is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

#### description (continued)

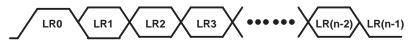

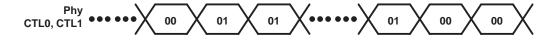

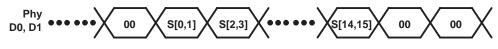

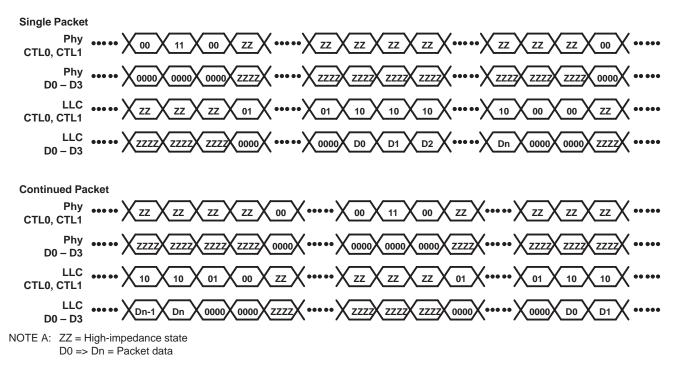

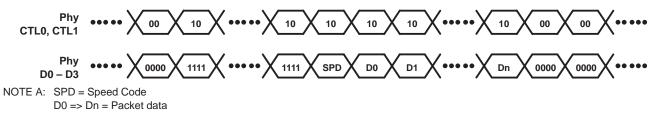

Data bits to be transmitted through the cable ports are received from the LLC on two or four data lines (D0 – D3), and are latched internally in the TSB21LV03C in synchronization with the 49.152-MHz system clock. These bits are combined serially, encoded, and transmitted at 98.304 or 196.608 Mbits/s as the outbound data-strobe information stream. During transmission, the encoded data information is transmitted differentially on the TPB cable pair(s), and the encoded strobe information is transmitted differentially on the TPA cable pair(s).

During packet reception the TPA and TPB transmitters of the receiving cable port are disabled, and the receivers for that port are enabled. The encoded data information is received on the TPA cable pair, and the encoded Strobe information is received on the TPB cable pair. The received data-strobe information is decoded to recover the receive clock signal and the serial data bits. The serial data bits are split into two or four parallel streams, resynchronized to the local system clock, and sent to the associated LLC. The received data is also transmitted (repeated) out of the other active (connected) cable ports.

Both the TPA and TPB cable interfaces incorporate differential comparators to monitor the line states during initialization and arbitration. The outputs of these comparators are used by the internal logic to determine the arbitration status. The TPA channel monitors the incoming cable common-mode voltage. The value of this common mode voltage is used during arbitration to set the speed of the next packet transmission. In addition, the TPB channel monitors the incoming cable common-mode voltage is used as an indication of twisted-pair bias voltage. The presence or absence of this common-mode voltage is used as an indication of cable connection status. The cable connection status signal is internally debounced in the TSB21LV03C on a cable disconnect-to-connect. The debounced cable connection status signal initiates a bus reset. On a cable disconnect-to-connect a debounce delay is incorporated. There is no delay on a cable disconnect.

The TSB21LV03C provides a 1.86-V nominal bias voltage for driver load termination. This bias voltage, when seen through a cable by a remote receiver, indicates the presence of an active connection. The value of this bias voltage has been chosen to allow interoperability between transceiver chips operating from either 5-V or 3-V nominal supplies. This bias voltage source should be stabilized by using an external filter capacitor of approximately 1.0  $\mu$ F.

The transmitter circuitry is disabled under the following conditions: power down, cable not active, reset, or transmitter disable. The receiver circuitry is disabled under the following conditions: power down, cable not active, or receiver disable. The twisted-pair bias voltage circuitry is disabled under the following conditions: power down or reset. The power-down condition occurs when the PD input is high. The cable-not-active (CNA) condition occurs when the cable connection status indicates that no cable is connected. The reset condition occurs when the RESET input terminal is low. The transmitter disable and receiver disable conditions are determined from the internal logic.

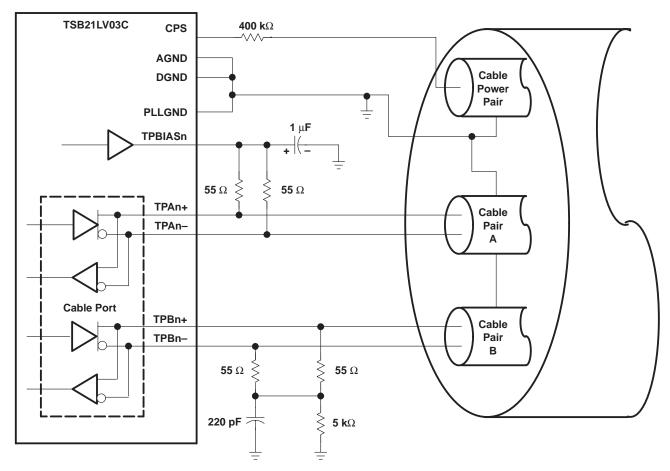

The line drivers in the TSB21LV03C operate in a high-impedance current mode and are designed to work with external 110- $\Omega$  line-termination resistor networks. One network is provided at each end of each twisted-pair cable. Each network is composed of a pair of series-connected 55- $\Omega$  resistors. The midpoint of the pair of resistors that is directly connected to the twisted-pair A (TPA) package terminals is connected to the TPBIAS voltage terminals is coupled to ground through a parallel RC network with recommended resistor and capacitor values of 5 k $\Omega$  and 220 pF respectively. The values of the external resistors are designed to meet the draft standard specifications when connected in parallel with the internal receiver circuits and are shown in Figure 3.

The driver output current, along with other internal operating currents, is set by an external resistor. This resistor is connected between the R0 and R1 terminals and has a value of 6.3 k $\Omega$ , ±0.5%. This might be accomplished by placing a 6.34 k $\Omega$ , ±0,5% resistor in parallel with a 1-M $\Omega$  resistor.

### description (continued)

Four package terminals are used as inputs to set four configuration status bits in the self-identification (Self-ID) packet. These terminals are hardwired high or low as a function of the equipment design. PC0 – PC2 are the three terminals that indicate either the need for power from the cable or the ability to supply power to the cable. The fourth terminal, C/LKON, indicates whether a node is a contender for bus manager. When the C/LKON terminal is asserted, it means the node can be a contender for bus manager. When the terminal is not asserted, it means that the node is not a contender. The C bit corresponds to bit 20 in the Self-ID packet, PC0 corresponds to bit 21, PC1 corresponds to bit 22, and PC2 corresponds to bit 23 (see Table 4–29 of the IEEE 1394–1995 standard for additional details).

A power-down terminal, PD, is provided to allow a power-down mode where most of the TSB21LV03C circuits are powered down to conserve energy in battery-powered applications. A cable status terminal, CNA, provides a high output when all twisted-pair cable ports are disconnected. This output is not debounced. The CNA output can be used to determine when to power the TSB21LV03C down or up. In the power-down mode all circuitry is disabled except the CNA circuitry. It should be noted that when the device is powered-down it does not act in a repeater mode. When the TSB21LV03C is powered down using the PD terminal, the twisted-pair transmitter and receiver circuitry has been designed to present a high impedance to the cable to prevent loading the TPBias terminal voltage on the other end of the cable.

NOTE:

Reference suspend/resume section in the current 1394a specification for interoperability with PD implementation of power down.

If the TSB21LV03C is being used with one or more of the ports not being brought out to a connector, the TPB terminals must be terminated for reliable operation. For each unused port, the TPB+ and TPB– terminals must be connected to GND. This is done in the normal termination network. When a port does not have a cable connected, the normal termination network pulls TPB+ and TPB– to ground through a 5-k $\Omega$  resistor, thus disabling the port.

#### NOTE:

All gap counts on all nodes of a 1394 bus must be identical. This may only be accomplished by using phy configuration packets (see section 4.3.4.3 of IEEE 1394-1995 Standard) or by using two bus resets, which resets the gap counts to the maximum level (3 Fh).

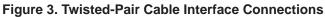

The link power status (LPS) terminal works with the C/LKON terminal to manage the LLC power usage of the node. The LPS terminal indicates that the LLC of the node is powered down and powers down the phy-LLC interface to save power. If the phy then receives a link-on packet, the C/LKON terminal is activated to output a 6.114 MHz signal, which can be used by the LLC to power itself up. Once the LLC is powered up, the LPS signal communicates this to the TSB21LV03C and the C/LKON signal is turned off and the phy-link interface is enabled.

Two of the package terminals are used to set up various test conditions used in manufacturing. These terminals, TESTM1 and TESTM2, should be connected to V<sub>DD</sub> for normal operation.

The TSB21LV03C is characterized for operation from 0°C to 70°C. The TSB21LV03CI is characterized for operation from -40°C to 85°C. The TSB21LV03CM is characterized for operation over the full military temperature range of -55°C to 125°C.

SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

### functional block diagram

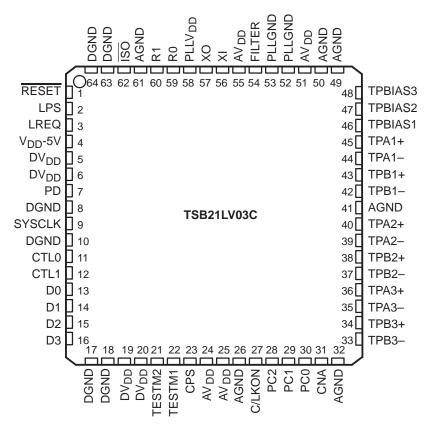

#### package outline

PLASTIC QUAD FLATPACK (PM) (TOP VIEW)

SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

AV<sub>DD</sub> FILTER PLLGND PLLGND DGND <u>ISO</u> AGND AGND AV<sub>DD</sub> AGND AGND R1 R0 X0 X1 X1 9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61 RESET 1 10 60 **Г TPBIAS3** LPS 11 59 [ **TPBIAS2** LREQ 12 **TPBIAS1** 58 V<sub>DD</sub>–5V 🛛 13 57 TPA1+ DV<sub>DD</sub> 14 TPA1-56 L DV<sub>DD</sub> 15 TPB1+ 55 l PD 16 54 TPB1-DGND 17 AGND 53 DGND 18 52 AGND SYSCLK 19 51 TPA2+ DGND 20 TPA2-50 CTL0 21 49 TPB2+ CTL1 22 48 TPB2-D0 23 47 TPA3+ D1 24 46 TPA3-D2 25 45 TPB3+ D3 26 44 [ TPB3- $27 \ 28 \ 29 \ 30 \ 31 \ 32 \ 33 \ 34 \ 35 \ 36 \ 37 \ 38 \ 39 \ 40 \ 41 \ 42 \ 43$ DVDD DVDD TESTM2 TESTM1 CPS DGND AV DD AV DD AGND AGND C/LKON PC2 PC1 PC0 CNA AGND

CERAMIC QUAD FLATPACK (HV) (TOP VIEW)

|                | PACH                              | AGE                               |

|----------------|-----------------------------------|-----------------------------------|

| T <sub>A</sub> | PLASTIC QUAD<br>FLAT PACK<br>(PM) | CERAMIC QUAD<br>FLAT PACK<br>(HV) |

| 0°C to 70°C    | TSB21LV03CPM                      | —                                 |

| -40°C to 85°C  | TSB21LV03CIPM                     | —                                 |

| -55°C to 125°C | —                                 | TSB21LV03CMHVB                    |

#### AVAILABLE OPTIONS

SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

### **Terminal Functions**

|                  | TERMINAL                               |                           |        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|----------------------------------------|---------------------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | N                                      | 0.                        | ТҮРЕ   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NAME             | HV                                     | РМ                        | 1      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AGND             | 5, 6, 36,<br>37, 43, 52,<br>53, 61, 62 | 26, 32, 41,<br>49, 50, 61 | Supply | -   | Analog circuit ground. All AGND terminals should be tied together to the low-impedance circuit-board ground plane. External to the device, AGND should be tied to DGND and PLLGND.                                                                                                                                                                                                                                                                                                                                                                                                     |

| AVDD             | 34, 35,<br>63, 67                      | 24, 25,<br>51, 55         | Supply | _   | Analog circuit power. A combination of high frequency decoupling capacitors near each AV_DD terminal is suggested, such as 0.1- $\mu$ F and 0.001- $\mu$ F capacitors. Lower frequency 10- $\mu$ F filtering capacitors are also recommended. AV_DD terminals are separated from DV_DD terminals internally from the other supply terminals to provide noise isolation. They should be tied together to a power plane on the circuit board. Each supply source should be individually filtered.                                                                                        |

| C/LKON           | C/LKON 38 27                           |                           | CMOS   | I/O | Bus manager capable (input). When set as an input, C/LKON specifies in the Self-ID packet that the node is bus manager capable. The bit value programming is done by tying the terminal through a 10-k $\Omega$ resistor to V <sub>DD</sub> (high, bus manager capable) or to GND (low, not bus manager capable). Using either the pullup or pulldown resistor allows the LINK ON output to override the input bit value when necessary.                                                                                                                                               |

|                  |                                        |                           |        |     | Link-on (output). When set as an output, C/LKON indicates the reception of a link-on message by asserting a 6.114-MHz signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CNA              | 42                                     | 31                        | CMOS   | 0   | Cable-not-active output. CNA is asserted high when none of the TSB21LV03C ports are connected to another active port. This circuit remains active during the power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPS              | 33                                     | 23                        | CMOS   | I   | Cable power status. CPS is normally connected to the cable power through a 400-k $\Omega$ resistor. This circuit drives an internal comparator that detects the presence of cable power. This information is maintained in two internal registers and is available to the LLC by way of a register read (see the Phy-Link Interface Annex in the IEEE 1394-1995 standard).                                                                                                                                                                                                             |

| CTL0<br>CTL1     | 21<br>22                               | 11<br>12                  | CMOS   | I/O | Control I/O. The CTLn terminals are bidirectional communications control signals between the TSB21LV03C and the LLC. These signals control the passage of information between the two devices. Control I/O terminals are 5-V tolerant. The CTLn terminals have an internal bus-holder function built-in.                                                                                                                                                                                                                                                                               |

| D0 – D3          | 23, 24,<br>25, 26                      | 13, 14,<br>15, 16         | CMOS   | I/O | Data I/O. The D terminals are bidirectional and pass data between the TSB21LV03C and the LLC. Data I/O terminals are 5-V tolerant. The D terminals have an internal bus-holder function built-in.                                                                                                                                                                                                                                                                                                                                                                                      |

| DGND             | 8, 9, 17,<br>18, 20,<br>27, 28         | 8, 10, 17,<br>18, 63, 64  | Supply | -   | Digital circuit ground. The DGND terminals should be tied to the low-impedance circuit-board ground plane. External to the device, AGND should be tied to DGND and PLLGND.                                                                                                                                                                                                                                                                                                                                                                                                             |

| DV <sub>DD</sub> | 14, 15,<br>29, 30                      | 5, 6,<br>19, 20           | Supply | -   | Digital circuit power. DV <sub>DD</sub> supplies power to the digital portion of the device. It is recommended that a combination of high-frequency decoupling capacitors be connected to DV <sub>DD</sub> (i.e., paralleled 0.1 $\mu$ F and 0.001 $\mu$ F). Lower frequency 10- $\mu$ F filtering capacitors can also be used. These supply terminals are separated from AV <sub>DD</sub> internally in the device to provide noise isolation. These terminals should also be tied together to a power plane on the circuit board. Individual filtering networks for each is desired. |

| FILTER           | 66                                     | 54                        | CMOS   | I/O | PLL filter. FILTER is connected to a $0.1-\mu$ F capacitor and then to PLLGND to complete the internal lag-lead filter. This filter is required for stable operation of the frequency multiplier PLL running off of the crystal oscillator.                                                                                                                                                                                                                                                                                                                                            |

SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

# **Terminal Functions (Continued)**

|                  | TERMINAL   |            |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|------------|------------|----------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | N          | 0.         | TYPE I/O |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NAME             | HV         | PM         |          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ISO              | 7          | 62         | CMOS     | I | Link interface isolation input. ISO is normally tied high both to implement TI bus-holder isolation or no isolation. The TSB21LV03C does not support Annex J isolation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LPS              | 11         | 2          | CMOS     | Ι | Link power status. LPS is connected to either the V <sub>DD</sub> supplying the LLC through a 1–k $\Omega$ resistor or directly to a pulsed output that is active when the LLC is powered for the purpose of monitoring the LLC power status. The pulsed signal must be between 220 kHz and 5.5 MHz to be sensed as active. If LPS is inactive, the phy-LLC interface is disabled, and the TSB21LV03C performs only the basic repeater functions required for network initialization and operation. LPS is 5-V tolerant and has an internal bus-holder function built-in. If this terminal is tied through a resistor to a fixed state, the resistor must be 1 k $\Omega$ or less.      |

| LREQ             | 12         | 3          | CMOS     | I | Link request. LREQ is an input from the LLC that requests the TSB21LV03C to perform some service. LREQ is 5-V tolerant and has an internal bus-holder function built-in. If this terminal is tied through a resistor to a fixed state, the resistor must be 1 k $\Omega$ or less.                                                                                                                                                                                                                                                                                                                                                                                                       |

| PC2 – PC0        | 39, 40, 41 | 28, 29, 30 | CMOS     | I | Power class indicators. The PC signals set the bit values of the three power-class bits in the Self-ID packet (bits 21, 22, and 23). These bits can be programmed by tying the terminals to $V_{DD}$ (high) or to GND (low).                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PD               | 16         | 7          | CMOS     | I | Power down. When asserted high, PD turns off all internal circuitry except the CNA monitor circuits that drive the CNA terminal. PD is 5-V tolerant. The PD terminal may be tied directly to V <sub>DD</sub> or to DGND. If this terminal is tied through a resistor to a fixed state, the resistor must be 1 k $\Omega$ or less. The PD terminal has an internal bus-holder function built in to it.                                                                                                                                                                                                                                                                                   |

| PLLGND           | 64, 65     | 52, 53     | Supply   | _ | PLL circuit ground. The PLLGND terminals should be tied to the low-impedance circuit-board ground plane. External to the device, AGND should be tied to DGND and PLLGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PLLVDD           | 2          | 58         | Supply   | _ | PLL circuit power. PLLV <sub>DD</sub> supplies power to the PLL portion of the device. It is recommended that a combination of high-frequency decoupling capacitors be connected to PLLV <sub>DD</sub> (i.e., paralleled 0.1 $\mu$ F and 0.001 $\mu$ F). Lower frequency 10- $\mu$ F filtering capacitors can also be used. The PLLV <sub>DD</sub> supply terminals are separated from AV <sub>DD</sub> and DV <sub>DD</sub> internally in the device to provide noise isolation. The PLLV <sub>DD</sub> , AV <sub>DD</sub> , and DV <sub>DD</sub> terminals should also be tied together to a power plane on the circuit board. Individual filtering networks for each is recommended. |

| R0<br>R1         | 3<br>4     | 59<br>60   |          | _ | Current setting resistor. An internal reference voltage is applied to a resistor connected between R0 and R1 to set the operating current and the cable driver output current. A resistance of 6.3 k $\Omega$ ±0.5% should be used to meet the IEEE 1394-1995 standard requirements for output voltage limits.                                                                                                                                                                                                                                                                                                                                                                          |

| RESET            | 10         | 1          | CMOS     | I | Reset. When RESET is asserted low (active), a bus reset condition is set on the active cable ports and the the internal logic is reset to the reset start state. An internal pullup resistor, which is connected to $V_{DD}$ , is provided so only an external delay capacitor is required. This input is a standard logic buffer and can also be driven by an open-drain logic output buffer. The minimum hold time for RESET is listed in the recommended operating characteristics table.                                                                                                                                                                                            |

| SYSCLK           | 19         | 9          | CMOS     | 0 | System clock. SYSCLK provides a 49.152-MHz clock signal, which is synchro-<br>nized with the data transfers to the LLC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TESTM1<br>TESTM2 | 32<br>31   | 22<br>21   | CMOS     | I | Test mode control. TESTM1 and TESTM2 are used during the manufacturing test and should be tied to $V_{\mbox{DD}}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

### **Terminal Functions (Continued)**

|                               | TERMINAL       |                |        |     |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |  |  |  |   |  |  |   |                                                                  |

|-------------------------------|----------------|----------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|---|--|--|---|------------------------------------------------------------------|

| NAME                          | N              | 0.             | ТҮРЕ   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |                                                                  |  |  |  |   |  |  |   |                                                                  |

|                               | HV             | РМ             |        |     |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |  |  |  |   |  |  |   |                                                                  |

| TPA1+<br>TPA2+<br>TPA3+       | 57<br>51<br>47 | 45<br>40<br>36 | Cable  |     | Portn, port cable pair A. TPAn is the port A connection to the twisted-pair cable.<br>Board traces from these terminals should be kept matched and as short as pos-                                                                                                                                                                                                                   |                                                                  |  |  |  |   |  |  |   |                                                                  |

| TPA1–<br>TPA2–<br>TPA3–       | 56<br>50<br>46 | 44<br>39<br>35 | Cable  | 0   | 0                                                                                                                                                                                                                                                                                                                                                                                     | sible to the external load resistors and to the cable connector. |  |  |  |   |  |  |   |                                                                  |

| TPB1+<br>TPB2+<br>TPB3+       | 55<br>49<br>45 | 43<br>38<br>34 | Cable  | 0   | Portn, port cable pair B. TPBn is the port B connection to the twisted-pair cable.<br>Board traces from these terminals should be kept matched and as short as pos-                                                                                                                                                                                                                   |                                                                  |  |  |  |   |  |  |   |                                                                  |

| TPB1–<br>TPB2–<br>TPB3–       | 54<br>48<br>44 | 42<br>37<br>33 | Cable  |     |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |  |  |  | Ű |  |  | - | sible to the external load resistors and to the cable connector. |

| TPBIAS1<br>TPBIAS2<br>TPBIAS3 | 58<br>59<br>60 | 46<br>47<br>48 | Cable  | ο   | Portn, twisted-pair bias. TPBIASn provides the 1.86-V nominal bias voltage needed for proper operation of the twisted-pair cable drivers and receivers and for sending a valid cable connection signal to the remote nodes.                                                                                                                                                           |                                                                  |  |  |  |   |  |  |   |                                                                  |

| V <sub>DD</sub> –5V           | 13             | 4              | Supply | _   | $5\text{-}VV_{DD}$ supply. $V_{DD}$ – $5V$ should be connected to the LLC $V_{DD}$ supply when a $5\text{-}V$ LLC is connected to the phy, and it should be connected to the phy $DV_{DD}$ when a 3-V LLC is used.                                                                                                                                                                    |                                                                  |  |  |  |   |  |  |   |                                                                  |

| XI<br>XO                      | 68<br>1        | 56<br>57       | _      | _   | Crystal oscillator. XO and XI connect to a 24.576-MHz parallel resonant funda-<br>mental mode crystal. Although, when a 24.576-MHz crystal oscillator is used, it<br>can be connected to XI with XO left unconnected. The optimum values for the<br>external shunt capacitors are dependent on the specifications of the crystal<br>used. See application note on crystal oscillator. |                                                                  |  |  |  |   |  |  |   |                                                                  |

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>DD</sub>                        | 0.3 V to 4 V                     |

|--------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>1</sub>                          | –0.5 V to V <sub>DD</sub> +0.5 V |

| Output voltage range at any output, V <sub>O</sub>           | –0.5 V to V <sub>DD</sub> +0.5V  |

| Continuous total power dissipation                           | See Dissipation Rating Table     |

| Operating free-air temperature, T <sub>A</sub> , TSB21LV03C  | 0°C to 70°C                      |

| TSB21LV03CI                                                  | 40°C to 85°C                     |

| TSB21LV03CM                                                  | –55°C to 125°C                   |

| Junction temperature, T <sub>J</sub> , PM package            | 150°C                            |

| HV package                                                   | 165°C                            |

| Storage temperature range, T <sub>stg</sub>                  |                                  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 220°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR <sup>‡</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|-------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| PM      | 1866 mW                               | 14.9 mW/°C                                                  | 1194 mW                               | 972 mW                                | —                                      |

| HV      | 2943 mW                               | 21.02 mW/°C                                                 | 1997 mW                               | 1681 mW                               | 841 mW                                 |

<sup>‡</sup>This is the inverse of the traditional junction-to-ambient thermal resistance (R<sub>0JA</sub>) and uses a board-mounted 67°C/W for PM package and 47.57°C/W for HV package.

### recommended operating conditions

|                                             |                                                   |                                 | MIN                  | NOM    | MAX                | UNIT |

|---------------------------------------------|---------------------------------------------------|---------------------------------|----------------------|--------|--------------------|------|

|                                             | Source power node                                 | 3                               | 3.3                  | 3.6    | V                  |      |

| bifferential input voltage, VID             | Nonsource power node§                             |                                 | 2.7                  | 3      | 3.6                | V    |

| Lligh lovel input veltage. Ver              | Commercial                                        |                                 |                      |        |                    | V    |

| High-level input voltage, vIH               | CMOS inputs                                       | Industrial, Military            | 0.85 V <sub>DD</sub> |        |                    | V    |

| Low-level input voltage, VIL                | CMOS inputs                                       |                                 |                      |        | 0.2V <sub>DD</sub> | V    |

|                                             | Cable inputs, 100-Mbit op                         | peration                        | 142                  |        | 260                |      |

| Differential input voltage, V <sub>ID</sub> | Cable inputs, 200-Mbit op                         | peration                        | 132                  |        | 260                | mV   |

|                                             | Cable inputs, during arbit                        | 171                             |                      | 262    |                    |      |

|                                             | TPB cable inputs, 100-MI power node               | 1.165                           |                      | 2.515  |                    |      |

|                                             | TPB cable inputs, 100-MI<br>Nonsource power node§ | 1.165                           |                      | 2.015  | V                  |      |

| Common-mode input voltage, VIC              | TPB cable inputs, 200-MI node                     | 0.935                           |                      | 2.515  |                    |      |

|                                             | TPB cable inputs, 200-MI power node§              | 0.935                           |                      | 2.015  |                    |      |

| Peopius input iittor                        | TPA, TPB cable inputs, 1                          | 00-Mbit operation               |                      |        | *±1.08             |      |

| Receive input jitter                        | TPA, TPB cable inputs, 2                          |                                 |                      | *±0.5  | ns                 |      |

| Pagaiya input alaw                          | Between TPA and TPB ca                            | able inputs, 100-Mbit operation |                      |        | *±0.8              | 20   |

| Receive input slew                          | Between TPA and TPB ca                            |                                 |                      | *±0.55 | ns                 |      |

| Output current, IOL/IOH                     | Control, Data, CNA and C                          | C/LKON outputs, SYSCLK          | -12                  |        | 12                 | mA   |

| Output current, IO                          | TPBIAS outputs                                    |                                 | -3                   |        | 1.3                | mA   |

| Hold time, power-up reset (RESET)           |                                                   |                                 | *2                   |        |                    | ms   |

§ For a node that does not source power (see Section 4.2.2.2 in IEEE 1394–1995 Standard).

\* These parameters are not production tested for the HV package.

### electrical characteristics over recommended operating conditions (unless otherwise noted)

#### driver

|          | PARAMETER                                           | TEST CONDITION                      | MIN    | TYP MAX | UNIT |

|----------|-----------------------------------------------------|-------------------------------------|--------|---------|------|

| VOD      | Differential output voltage                         | 55-Ω load                           | 172    | 265     | mV   |

| V(OFF)   | Off-state differential output voltage               | Drivers disabled                    |        | 20      | mV   |

| IO(diff) | Differential current (TPA+, TPA–, TPB+, TPB–)       | Driver enabled, Speed signaling off | -1.05† | 1.05†   | mA   |

| I(SP)    | Common-mode speed signaling current<br>(TPB+, TPB–) | 200-Mbit speed signaling enabled    | -2.53‡ | -4.84‡  | mA   |

<sup>†</sup> Limits are defined as the algebraic sum of TPA+ and TPA– driver currents. Limits also apply to TPB+ and TPB– as the algebraic sum of driver currents.

<sup>‡</sup>Limits are defined as the absolute limit of each of TPB+ and TPB– driver currents.

# electrical characteristics over recommended operating conditions (unless otherwise noted) (continued)

### receiver

|                 | PARAMETER                                                    | TEST CONDITION  | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------------------------------------------|-----------------|-----|-----|-----|------|

| VIT             | Input threshold voltage                                      |                 | -30 |     | 30  | mV   |

| VIT             | Cable bias-detect input threshold voltage, TPBn cable inputs | Driver disabled | 0.6 |     | 1   | V    |

| <sup>I</sup> IC | Common-mode input current                                    | Driver disabled | -40 |     | 40  | μΑ   |

| -               |                                                              | Deixen disekted | 15  |     |     | kΩ   |

| ZID             | Differential input impedance                                 | Driver disabled |     |     | *6  | pF   |

| 7               | Common mode impedance                                        | Driver disabled | 20  |     |     | kΩ   |

| ZIC             | Common-mode impedance                                        | Driver disabled |     |     | *24 | pF   |

\* These parameters are not production tested for the HV package.

#### device

|                  | PARAMETER                                                        | TEST (                         | CONDITIONS                        | MIN                   | TYP | MAX   | UNIT |

|------------------|------------------------------------------------------------------|--------------------------------|-----------------------------------|-----------------------|-----|-------|------|

|                  | Supply current                                                   | V <sub>DD</sub> = 3.3 V        | Node transmitting<br>or repeating |                       | 114 |       | mA   |

| IDD              |                                                                  |                                | Node receiving                    |                       | 140 |       | mA   |

|                  |                                                                  | V <sub>DD</sub> = 3.6 V        |                                   |                       |     | *175  | mA   |

|                  |                                                                  | V <sub>DD</sub> = 3.6 V,       | Power-down mode                   |                       | 20  |       | IIIA |

| VIT              | Power status input threshold voltage (CPS)                       | $R_L = 400 \text{ k}\Omega$    |                                   | 4.7                   |     | 7.5   | V    |

| VOH              | High-level output voltage                                        | V <sub>DD</sub> = min,         | I <sub>OH</sub> max               | V <sub>DD</sub> -0.55 |     |       | V    |

| VOL              | Low-level output voltage                                         | V <sub>DD</sub> = max,         | I <sub>OL</sub> min               |                       |     | 0.5   | V    |

| Ц                | Input current (TESTM1, TESTM2, PC0, PC1, PC2)                    | $V_{I} = V_{DD} \text{ or } 0$ |                                   |                       |     | ±1    | μA   |

|                  | Off-state output current<br>(CTL0, CTL1, D0, D1, D2, D3, C/LKON) | $V_{O} = V_{DD}$ or 0          |                                   |                       |     | ±5    | μA   |

| loff             | Pullup current (RESET)                                           | $V_{I} = 0 \text{ or}$         | Commercial                        | -90                   | -45 | -10   | μA   |

|                  |                                                                  | 1.5 V                          | Industrial, Military              | -110                  | -45 | -10   | μΑ   |

| V <sub>TH+</sub> | Positive arbitration comparator-input threshold voltage          |                                |                                   | 89                    |     | 168   | mV   |

| $V_{\text{TH}-}$ | Negative arbitration comparator-input threshold voltage          |                                |                                   | -168                  |     | -89   | mV   |

| VIT              | Speed-signal input threshold voltage                             | TPBIAS – TPA<br>voltage        | common-mode                       | 49                    |     | 131   | mV   |

| VO               | Output voltage (TPBIAS1, TPBIAS2, TPBIAS3)                       | At rated IO cu                 | rrent                             | 1.665                 |     | 2.015 | V    |

|                  | Bus holding current (LPS, LREQ, CTLn, Dn, PD)                    | $V_{I} = 1/2 (V_{DD})$         | )                                 |                       | 725 |       | μA   |

$^{\ast}$  These parameters are not production tested for the HV package.

#### thermal characteristics

| PARAMETER |                                                         | TEST CONDITIONS | MIN                       | TYP | MAX   | UNIT |       |  |

|-----------|---------------------------------------------------------|-----------------|---------------------------|-----|-------|------|-------|--|

|           |                                                         | PM package      | EIA/JESD51-3, No air flow | 67  |       |      | °C/W  |  |

| κθJΑ      | $R_{\theta JA}$ Junction-to-free-air thermal resistance |                 |                           |     | 47.57 |      | -0/00 |  |

| Pairs     | $R_{\theta JC}$ Junction-to-case thermal resistance     |                 |                           |     | 10.4  |      | °C/W  |  |

| βJC       |                                                         |                 |                           |     | 3     |      | C/W   |  |

### switching characteristics

|                 | PARAMETER                                                      | MEASURED            | TEST CONDITIONS                   | MIN | TYP MAX | UNIT |

|-----------------|----------------------------------------------------------------|---------------------|-----------------------------------|-----|---------|------|

|                 | Jitter, transmit                                               | TPA, TPB            |                                   |     | ±0.25   | ns   |

|                 | Skew rate, transmit                                            | Between TPA and TPB |                                   |     | *±0.15  | ns   |

| tr              | Rise time, transmit                                            | 10% to 90%          | $R_L = 55 \Omega$ , $C_L = 10 pF$ |     | *2.2    | ns   |

| t <sub>f</sub>  | Fall time, transmit                                            | 90% to 10%          | $R_L = 55 \Omega$ , $C_L = 10 pF$ |     | *2.2    | ns   |

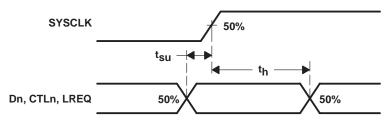

| t <sub>su</sub> | Setup time, Dn, CTLn, LREQ↑↓ to<br>SYSCLK↑                     | 50% to 50%          | See Figure 1                      | *5  |         | ns   |

| t <sub>h</sub>  | Hold time, Dn, CTLn, LREQ↑↓ before<br>SYSCLK↑                  | 50% to 50%          | See Figure 1                      | *2  |         | ns   |

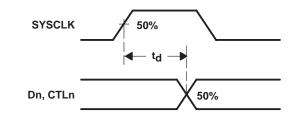

| t <sub>d</sub>  | Delay time, SYSCLK $\uparrow$ to Dn, CTLn $\uparrow\downarrow$ | 50% to 50%          | See Figure 2                      | 2   | 11      | ns   |

\* These parameters are not production tested for the HV package.

# PARAMETER MEASUREMENT INFORMATION

# Figure 1. Dn, CTLn, LREQ Input Setup and Hold Timing Waveforms

Figure 2. Dn and CTLn Output-Delay Timing Waveforms

# **APPLICATION INFORMATION**

# internal register configuration

The accessible internal registers of this device are listed in Table 1.

### Table 1. Internal Register Configuration

| Address | 0              | 1      | 2           | 3    | 4   | 5        | 6    | 7     |

|---------|----------------|--------|-------------|------|-----|----------|------|-------|

| 0000    |                |        | Physical ID |      |     |          | R    | CPS   |

| 0001    | RHB            | IBR    | GC          |      |     |          |      |       |

| 0010    | SPD            |        | R           | ev   | NP  |          |      |       |

| 0011    | AStat1         |        | BSt         | tat1 | Ch1 | Con1     | Rese | erved |

| 0100    | AS             | AStat2 |             | tat2 | Ch2 | Con2     | Rese | erved |

| 0101    | AS             | AStat3 |             | tat3 | Ch3 | Con3     | Rese | erved |

| 0110    | LoopInt CPSInt |        | CPS         | IR   |     | Reserved |      | С     |

| 0111    | Reserved       |        |             |      |     |          |      |       |

| 1000    | Reserved       |        |             |      |     |          |      |       |

#### **Table 2. Internal Register Field Descriptions**

| FIELD    | SIZE | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AStat(n) | 2    | Read<br>only | AStat contains the line state of TPAn. The status is indicated by the following:<br>11 = high-impedance state<br>01 = 1<br>10 = 0<br>00 = Invalid data state. Power-up reset initializes to this line state. This line state is also output during transmit<br>and receive operations, including date-end signaling. The line state outputs are generally valid during arbitration<br>and idle conditions on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BStat(n) | 2    | Read<br>only | BStat contains the line state of TPBn. The status is indicated by the following:<br>11 = high-impedance state<br>01 = 1<br>10 = 0<br>00 = Invalid data state. Power-up reset initializes to this line state. This line state is also output during transmit<br>and receive operations. The line state outputs are generally valid during arbitration and idle conditions on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| С        | 1    | R            | Bus manager capable. C indicates the state of the Bus Manager Capable input. When set, this bit is used by the TSB21LV03C to specify in the Self-ID packet that the node is Bus Manager Capable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ch(n)    | 1    | Read<br>only | When Ch = 1, the port is a child, otherwise it is a parent. This bit is invalid after a hardware reset or a bus reset until tree-ID processing is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Con(n)   | 1    | Read<br>only | Con indicates the connection status of the port. When Con = 1, the port is connected, otherwise it is disconnected. This bit is set to 1 by a hardware reset and is updated to reflect the actual cable connection status of the port during bus reset. The TSB21LV03C contains connection debounce circuitry that prevents a new cable connection on a port from initiating a bus reset until the connection status has been stable for at least 335 ms. A cable disconnect initiates a bus reset immediately. After a hardware reset, the TSB21LV03C sets the connection status of all ports to 0. The TSB21LV03C proceeds with the bus reset, tree-ID, and Self-ID, but with all ports considered to be disconnected child ports. The TSB21LV03C can not transmit any signals on the serial bus ports during this time. The TSB21LV03C does report itself as root with a physical address of 00h at the completion of Self-ID. If any port is actually connected, after the debounce delay, the TSB21LV03C initiates another bus reset, which proceeds normally with interaction between the TSB21LV03C and its peer nodes. |

# **APPLICATION INFORMATION**

#### Table 2. Internal Register Field Descriptions (continued)

| FIELD       | SIZE | TYPE           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPS         | 1    | Read<br>only   | Cable power status (CPS) contains the status of the CPS input terminal. When cable power voltage has dropped too low for reliable operation, CPS is reset (0). CPS is included twice in the internal registers to expedite handling of the CPSInt.                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPSInt      | 1    | Read/<br>Write | CPSint indicates that a cable power status interrupt has occurred. This interrupt occurs whenever the CPS input goes low. The interrupt indicates that the cable power voltage has dropped too low to ensure reliable operation. This bit is cleared (0) by a hardware reset or by writing a 0 to this register. However, if the CPS input is still low, another cable-power status interrupt immediately occurs.                                                                                                                                                                                                                                           |

| GC          | 6    | Read/<br>Write | The gap count (GC) register sets the fair and arb-reset gap times. The gap count may be set to a particular value to optimize bus performance. Typically, the gap count should be set to 2 times the maximum number of hops on the bus and <b>must</b> be set to the same value for all nodes on the bus. The gap count can be set by either a write to this register or by reception or transmission of a PHY_CONFIG packet. The gap count is reset to 3Fh after a hardware reset or after two consecutive bus resets without an intervening write to the gap count register (either a write to the gap count register by the LLC or a PHY_CONFIG packet). |

| IBR         | 1    | Read/<br>Write | When set, initiate bus reset (IBR) causes the current node to immediately initiate a bus reset. IBR is cleared (0) after a hardware reset or a bus reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IR          | 1    | Read/<br>Write | IR indicates that the last bus reset was initiated in this TSB21LV03C phy. This bit is also included in the self-ID packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LoopInt     | 1    | Read/<br>Write | LoopInt indicates that a configuration loop timeout has occurred. This interrupt occurs when the arbitration controller waits for too long a period of time during tree-ID. This interrupt can indicate that the bus is configured in a loop. This bit is cleared (0) by a hardware reset or by writing a 0 to this register bit.                                                                                                                                                                                                                                                                                                                           |

| NP          | 4    | Read<br>only   | NP contains the number of ports implemented in the core logic (not the number of ports actually on the device). For the TSB21LV03C, NP is set to 0011b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Physical ID | 6    | Read<br>only   | Physical ID contains the physical address of the local node. The physical ID in valid after a hardware reset or a bus reset until the Self-ID process has been completed. A complete Self-ID is indicated by an unsolicited status transfer of the register 0 contents to the LLC.                                                                                                                                                                                                                                                                                                                                                                          |

| R           | 1    | Read<br>only   | R indicates whether the current node is the root node or not. This bit is cleared (0) on a hardware reset or a bus reset. This bit is set during tree-ID when the current node is root.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rev         | 2    | Read<br>only   | The revision (Rev) bits indicate the design revision of the core logic. For the TSB21LV03C, Rev is set to 00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RHB         | 1    | Read/<br>Write | When set, the root hold-off bit (RHB) instructs the local node to try to become the root node during the next bus reset. RHB is reset (0) during a hardware reset and is not affected by a bus reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPD         | 2    | Read<br>only   | The speed (SPD) bits indicates the top signaling speed of the local port and for the TSB21LV03C is set to 01b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

SLLS331A – FEBRUARY 1999 – REVISED OCTOBER 1999

**APPLICATION INFORMATION**

SLLS331A – FEBRUARY 1999 – REVISED OCTOBER 1999

# **APPLICATION INFORMATION**

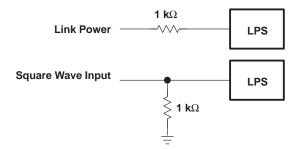

### Figure 5. Compliant DC Isolated Outer Shield Termination

Figure 6. Nonisolated Outer Shield Termination

SLLS331A – FEBRUARY 1999 – REVISED OCTOBER 1999

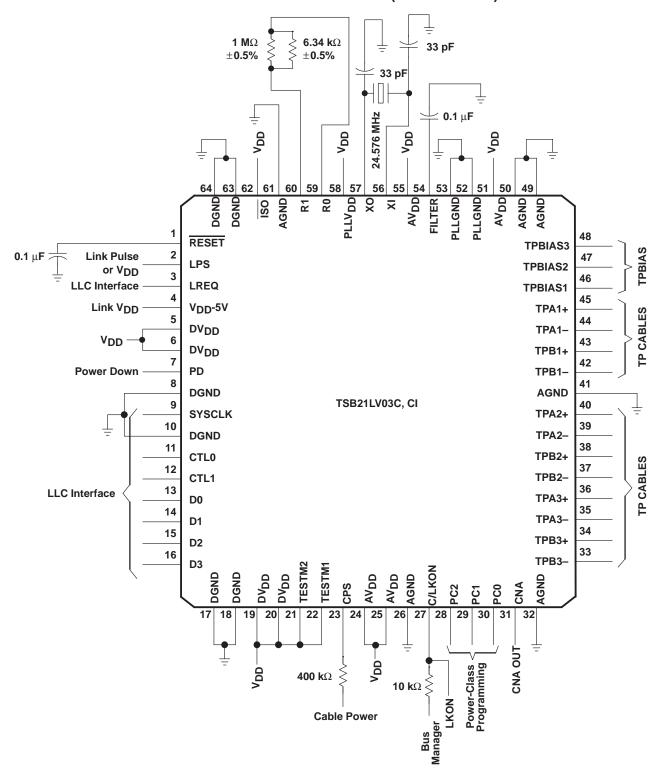

**APPLICATION INFORMATION (PM PACKAGE)**

NOTE A: For more information see the application note.

Figure 7. External Component Connections

SLLS331A - FEBRUARY 1999 - REVISED OCTOBER 1999

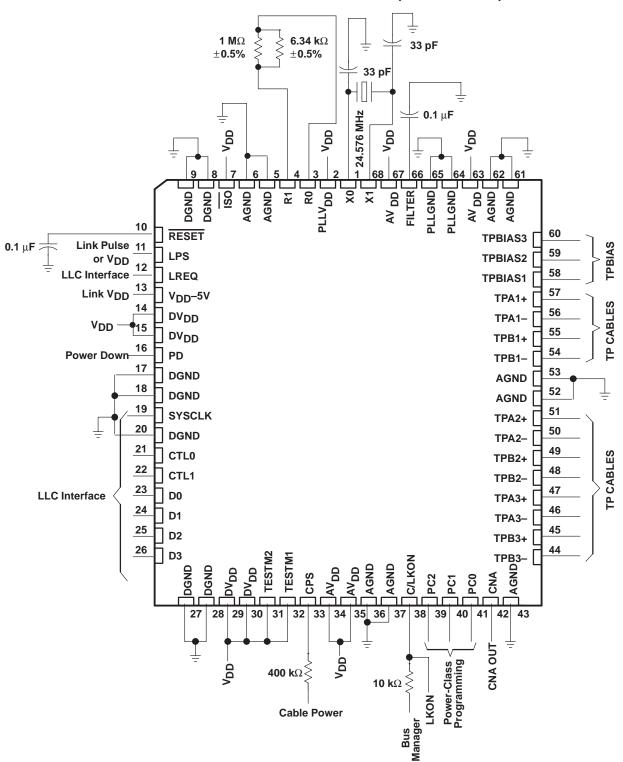

# **APPLICATION INFORMATION (HV PACKAGE)**

NOTE A: For more information see the application note.

# **APPLICATION INFORMATION**

#### crystal selection

TI PHYs may use an external 24.576 MHz crystal connected between the XI and XO pins on the PHY to provide the PHY clock. The following are some typical specifications for the crystals used with the Physical Layers from TI. The clock resulting from the input from the crystal must be within the tolerance of  $\pm$ 100 parts per million for the PHYs to function correctly. This is required by the 1394 standard. This frequency tolerance for the PHY clocks on each node must be maintained over the variation introduced over production runs of boards and environment the machines operate in. Every board must have an SYSCLK (clock generated by the PHY) within  $\pm$ 100 ppm of 49.152 MHz to be compliant to the 1394 standard. If adjacent nodes are more than 200 ppm away from one another then long packets sent across the 1394 bus may be corrupted, with the final bits of the packet being lost. TI PHYs are designed with a maximum of margin, but the limits imposed by 1394 must still be adhered to.

- 1. Crystal Mode of operation: Fundamental

- Frequency Tolerance at 25°C: Total variation specification for the complete circuit is 100ppm. The crystal is specified at less than 100 ppm.

- Frequency stability (over temperature): Total variation specification for the complete circuit is 100 ppm. The crystal is specified at less than 100 ppm.

#### NOTE: