# STV9432

# 100MHz OSD FOR MONITOR

#### FEATURE

- 100MHz MAX. PIXEL CLOCK, AVAILABLE FOR ANY LINE FREQUENCY BETWEEN 15 AND 140 kHz

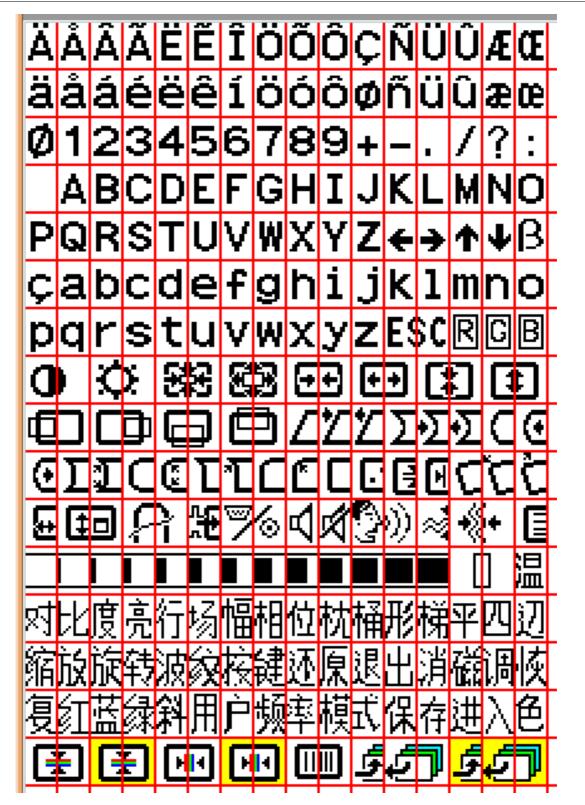

- 12 x 18 CHARACTER ROM FONT INCLUDES:

240 MONOCOLOR CHARACTERS

- 16 MULTICOLOR CHARACTERS

- CHARACTER FLASHING

- UP TO 1K CHARACTERS TEXT DISPLAY

- ULTRA HIGH FREQUENCY PLL FOR JITTER-FREE DISPLAY

- FLEXIBLE DISPLAY:

ANY CHARACTER WIDTH AND HEIGHT

- ANYWHERE IN THE SCREEN

- SINGLE BYTE CHARACTER CODES AND COLOR LOOK-UP TABLE FOR EASY PRO-GRAMMING AND FAST ACCESS

- CHARACTER FLIP OPERATIONS

- WIDE DISPLAY WINDOW ALLOWS PATTERN GENERATION FOR FACTORY ADJUSTMENTS

- I<sup>2</sup>C BUS MCU INTERFACE

#### **PIN CONNECTIONS**

| FILTER           | 1  | $\bigcirc$ | 24 | TEST             |

|------------------|----|------------|----|------------------|

| AGND             | 2  |            | 23 | ADCREF           |

| SDA 🗌            | 3  |            | 22 | N.C              |

| SCL              | 4  |            | 21 | N.C              |

| HS 🗌             | 5  |            | 20 | N.C              |

| VS               | 6  |            | 19 | AV <sub>DD</sub> |

| HFLY             | 7  |            | 18 |                  |

| N.C              | 8  |            | 17 | FBLK             |

|                  | 9  |            | 16 | BOUT             |

| DV <sub>ss</sub> | 10 |            | 15 | GOUT             |

| хті 🗌            | 11 |            | 14 | ROUT             |

| хто 🗌            | 12 |            | 13 | OV <sub>ss</sub> |

|                  |    |            |    |                  |

|                  |    |            |    |                  |

Version 4.0

DESCRIPTION

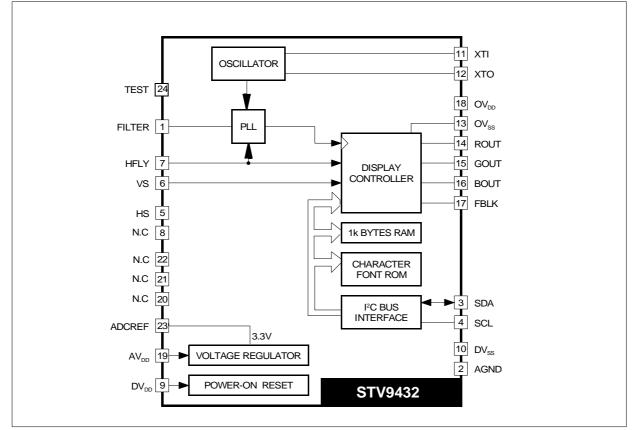

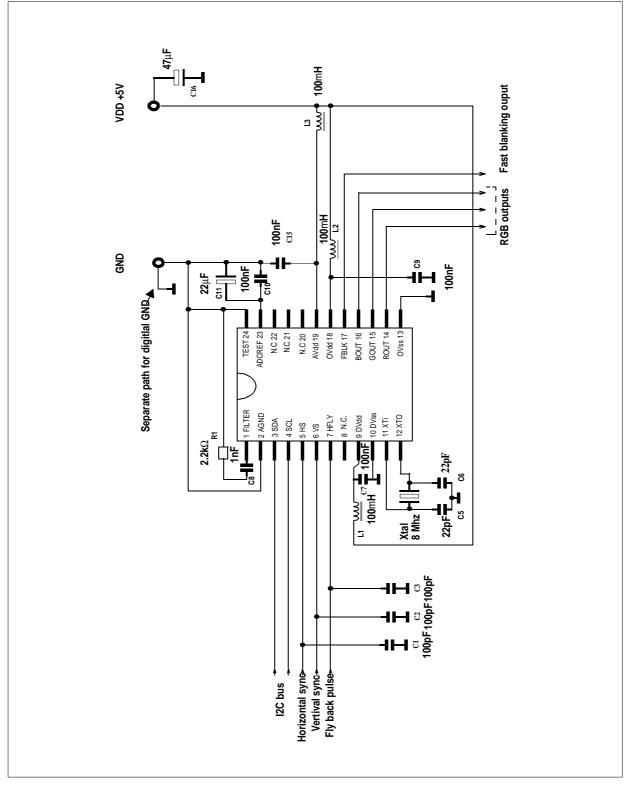

Connected to a host MCU via a serial I<sup>2</sup>C Bus, the STV9432TA is a multifunction slave peripheral device integrating the ON-Screen-Display block.

The On-screen Display (OSD) includes a MASK PROGRAMMABLE ROM that holds the CUSTOM CHARACTER FONT, a 1Kbytes RAM that stores the code strings of the different lines of text to be displayed, and a set of registers to program character sizes and colors. A built-in digital PLL, operating at very high frequency, provides an accurate display without visible jitter for a wide line frequency range from 15 to 140 kHz.

# **1 - PIN DESCRIPTION**

| Pin Number | Symbol           | Туре  | Description                       |

|------------|------------------|-------|-----------------------------------|

| 1          | FILTER           | I/O   | PLL Filter                        |

| 2          | AGND             | Power | Analog Ground                     |

| 3          | SDA              | I/O   | I <sup>2</sup> C Bus Serial Data  |

| 4          | SCL              |       | I <sup>2</sup> C Bus Serial Clock |

| 5          | HS               |       | Horizontal Sync Input             |

| 6          | VS               |       | Vertical Sync Input               |

| 7          | HFLY             |       | Horizontal Flyback Input          |

| 8          | N.C.             |       | Not Connected                     |

| 9          | DV <sub>DD</sub> | Power | Digital +5V Power Supply          |

| 10         | DV <sub>SS</sub> | Power | Digital Ground                    |

| 11         | XTI              |       | Crystal Oscillator Input          |

| 12         | XTO              | 0     | Crystal Oscillator Output         |

| 13         | OV <sub>SS</sub> | Power | Ground for the RGB Outputs        |

| 14         | ROUT             | 0     | Red Output                        |

| 15         | GOUT             | 0     | Green Output                      |

| 16         | BOUT             | 0     | Blue Output                       |

| 17         | FBLK             | 0     | Fast Blanking Output              |

| 18         | OV <sub>DD</sub> | Power | +5V Supply for the RGB Outputs    |

| 19         | AV <sub>DD</sub> | Power | Analog +5V Power Supply           |

| 20         | N.C.             |       | Not Connected                     |

| 21         | N.C.             |       | Not Connected                     |

| 22         | N.C.             |       | Not Connected                     |

| 23         | ADCREF           | I/O   | ADC Reference Voltage Pin         |

| 24         | TEST             | I/O   | Pin must be connected to ground   |

# 2 - BLOCK DIAGRAM

# **3 - ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                 | Parameter             | Value                                        | Unit |

|--------------------------------------------------------|-----------------------|----------------------------------------------|------|

| AV <sub>DD</sub> , DV <sub>DD</sub> , OV <sub>DD</sub> | Supply Voltage        | -0.3, +6.0                                   | V    |

| V <sub>IN</sub>                                        | Input Voltage         | V <sub>SS</sub> - 0.3, V <sub>DD</sub> + 0.3 | V    |

| T <sub>oper</sub>                                      | Operating Temperature | 0, +70                                       | °C   |

| T <sub>stg</sub>                                       | Storage Temperature   | -40, +125                                    | °C   |

# **4 - ELECTRICAL CHARACTERISTICS**

| $(V_{DD} = 5V, V_{SS} = 0V, GND = 0V, T_A = 0 \text{ to } 70^{\circ}, \text{ unless otherwise specified})$ |

|------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------|

| Symbol                        | Parameter                                                   | Min.               | Тур. | Max.            | Unit |

|-------------------------------|-------------------------------------------------------------|--------------------|------|-----------------|------|

| SUPPLY                        |                                                             |                    |      |                 |      |

| $AV_{DD}, DV_{DD}, OV_{DD}$   | Supply Voltage                                              | 4.75               | 5    | 5.25            | V    |

| $AI_{DD} + DI_{DD} + OI_{DD}$ | Analog and Digital Supply Current                           | -                  | -    | 150             | mA   |

| INPUTS (SCL, SDA)             |                                                             |                    |      |                 |      |

| V <sub>IL</sub>               | Input Low Voltage                                           |                    |      | 0.8             | V    |

| V <sub>IH</sub>               | Input High Voltage                                          | 2.4                |      |                 | V    |

| IIL                           | Input Leakage Current                                       | -1                 |      | +1              | μA   |

| INPUTS (HS, VS, HF            | LY)                                                         | •                  |      |                 |      |

| V <sub>IL</sub>               | Input Low Voltage                                           |                    |      | 0.8             | V    |

| V <sub>IH</sub>               | Input High Voltage HS, VS                                   | 2.4                |      |                 | V    |

| ۷IH                           | HFLY                                                        | 3.6                |      |                 | -    |

| V <sub>HYST</sub>             | Schmidt Trigger Hysteresis                                  |                    | 0.4  |                 | V    |

| I <sub>PU</sub>               | Pull-up Source Current (V <sub>IN</sub> = 0V)               |                    | 100  |                 | μA   |

| HSIN                          | Horizontal Synchro Input Range                              | 15                 |      | 140             | kHz  |

| OUTPUTS (SDA oper             |                                                             |                    |      |                 |      |

| V <sub>OL</sub>               | Output Low Voltage (I <sub>OL</sub> = 3mA)                  | 0                  |      | 0.4             | V    |

| OUTPUTS (R, G, B, F           |                                                             |                    |      |                 |      |

| V <sub>OL</sub>               | Output Low Voltage (I <sub>OL</sub> = 3mA)                  | 0                  |      | 0.4             | V    |

| V <sub>OH</sub>               | Output High Voltage (I <sub>OH</sub> = 3mA)                 | 0.8V <sub>DD</sub> |      | V <sub>DD</sub> | V    |

| OSCILLATOR (XTI, X            | (TO)                                                        |                    |      |                 |      |

| I <sub>IL</sub>               | XTI Input Source Current (V <sub>IN</sub> = 0V)             | 3                  |      | 15              | μA   |

| I <sub>IH</sub>               | XTI Input Sink Current (V <sub>IN</sub> = V <sub>DD</sub> ) | 3                  |      | 15              | μA   |

| V <sub>IL</sub>               | XTI Input Low Voltage                                       |                    |      | 1.4             | V    |

| V <sub>IH</sub>               | XTI Input High Voltage                                      | 0.7V <sub>DD</sub> |      |                 | V    |

| V <sub>OL</sub>               | XTI Output Low Voltage (I <sub>OL</sub> = 3mA)              | 0                  |      | 0.4             | V    |

| V <sub>OH</sub>               | XTI Output High Voltage (I <sub>OH</sub> = 3mA)             | 0.8V <sub>DD</sub> |      | V <sub>DD</sub> | V    |

| ADCREF                        |                                                             | ·                  |      |                 |      |

| V <sub>REF</sub>              | Output Voltage Reference                                    |                    | 3.3  |                 | V    |

| POWER-ON RESET                |                                                             | •                  |      |                 |      |

| DV <sub>DDTH</sub>            | Supply Threshold Level                                      |                    | 3.6  |                 | V    |

|                               |                                                             |                    |      |                 |      |

# **5 - TIMINGS**

| Symbol                           | Parameter                                  | Min.                                                      | Тур. | Max. | Unit |

|----------------------------------|--------------------------------------------|-----------------------------------------------------------|------|------|------|

| OSCILLATOR                       |                                            |                                                           |      |      |      |

| f <sub>OSC</sub>                 | Clock Frequency                            |                                                           | 8    |      | MHz  |

| f <sub>PXL</sub>                 | Pixel Frequency                            |                                                           |      | 100  | MHz  |

| R, G, B, FBLK (C <sub>LOAI</sub> | <sub>D</sub> = 30pF)                       |                                                           | •    |      | •    |

| t <sub>R</sub>                   | Rise Time (see Note 1)                     |                                                           | 5    |      | ns   |

| t <sub>F</sub>                   | Fall Time (see Note 1)                     |                                                           | 5    |      | ns   |

| t <sub>SKEW</sub>                | Skew between R, G, B, FBLK                 |                                                           | 5    |      | ns   |

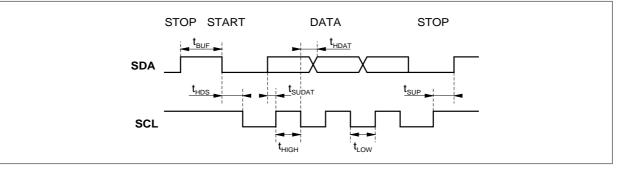

| I <sup>2</sup> C INTERFACE: SD/  | A AND SCL (see Figure 1)                   |                                                           |      |      |      |

| f <sub>SCL</sub>                 | SCL Clock Frequency                        | 0                                                         |      | 400  | kHz  |

| t <sub>BUF</sub>                 | Time the bus must be free between 2 access | 500                                                       |      |      | ns   |

| t <sub>HDS</sub>                 | Hold Time for Start Condition              | 500                                                       |      |      | ns   |

| t <sub>SUP</sub>                 | Set up Time for Stop Condition             | 500                                                       |      |      | ns   |

| t <sub>LOW</sub>                 | The Low Period of Clock                    | 400                                                       |      |      | ns   |

| t <sub>HIGH</sub>                | The High Period of Clock                   | 400                                                       |      |      | ns   |

| t <sub>HDAT</sub>                | Hold Time Data                             | 0                                                         |      |      | ns   |

| t <sub>SUDAT</sub>               | Set up Time Data                           | 500                                                       |      |      | ns   |

| t <sub>F</sub>                   | Fall Time of SDA                           |                                                           |      | 20   | ns   |

| t <sub>R</sub>                   | Rise Time of both SCL and SDA              | Depend on the pull-up resistor and the loa<br>capacitance |      |      |      |

Note : These parameters are not tested on each unit. They are measured during our internal qualification procedure which includes characterization on batches comming from corners of our processes and also temperature characterization

### Figure 1.

# **6 - SERIAL INTERFACE**

The 2-wires serial interface is an  $I^2C$  interface. To be connected to the  $I^2C$  bus, a device must own its slave address; the slave address of the STV9432 is BA (in hexadecimal).

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | RW |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 1  | 1  | 0  | 1  |    |

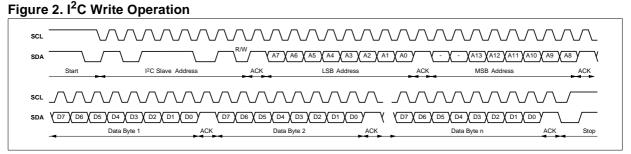

### 6.1 - DATA TRANSFER IN WRITE MODE

The host MCU can write data into the STV9432 registers or RAM.

To write data into the STVA9432TA after a start, the MCU must send (Figure 2):

- First, the I<sup>2</sup>C address slave byte with a low level for the R/W bit,

- The two bytes of the internal address where the MCU wants to write data(s),

- The successive bytes of data(s).

All bytes are sent MSB bit first and the write data transfer is ended with a stop.

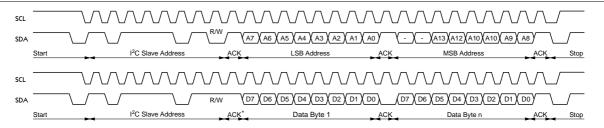

#### 6.2 - DATA TRANSFER IN READ MODE

The host MCU can read data from the STV9432 registers, RAM or ROM.

To read data from the STV9432 (Figure 3), the MCU must send 2 different  $I^2C$  sequences. The first one includes the  $I^2C$  slave address byte with R/W bit at low level and the 2 internal address bytes.

The second one includes the  $I^2C$  slave address byte with R/W bit at high level and all the successive data bytes read at successive addresses starting from the initial address given by the first sequence.

# Figure 3. I<sup>2</sup>C Read Operation

## 6.3 - ADDRESSING SPACE

#### 6.3.1 - General Mapping

STV9432 registers, RAM and ROM are mapped in a 32K address space. The mapping is:

| 0000<br>03FF | 1024 bytes RAM          | Descriptors and character codes |

|--------------|-------------------------|---------------------------------|

| 0400<br>07FF | Empty Space             |                                 |

| 0800<br>3FFF | Character Generator ROM |                                 |

| 4000<br>403F | Internal Registers      |                                 |

| 4040<br>7FFF | Empty Space             |                                 |

#### Important Notice:

All 16 bits datas are mapped LSB byte at lower address and MSB byte at higher address.

- Example: H1 12 bits register: @4000: 8 LSB bits - @4001: 4 MSB bits.

- Descriptors must also be written to RAM LSB byte first.

# 6.3.2 - I<sup>2</sup>C Registers Mapping

|           | o mapping |           |                       |

|-----------|-----------|-----------|-----------------------|

| 4000      | H1 LSB    | 4022      | Color 2               |

| 4001      | H1 MSB    | 4023      | Color 3               |

| 4002      | H2 LSB    | 4024      | Color 4               |

| 4003      | H2 MSB    | 4025      | Color 5               |

| 4004      | H3 LSB    | 4026      | Color 6               |

| 4005      | H3 MSB    | 4027      | Color 7               |

| 4006      | H4 LSB    | 4028      | Color 8               |

| 4007      | H4 MSB    | 4029      | Color 9               |

| 4008      | H5 LSB    | 402A      | Color 10              |

| 4009      | H5 MSB    | 402B      | Color 11              |

| 400A      | H6 LSB    | 402C      | Color 12              |

| 400B      | H6 MSB    | 402D      | Color 13              |

| 400C      | V1 LSB    | 402E      | Color 14              |

| 400D      | V1 MSB    | 402F      | Color 15              |

| 400E      | V2 LSB    | 4030      | Line Duration         |

| 400F      | V2 MSB    | 4031      | Top Margin            |

| 4010      | V3 LSB    | 4032      | Horizontal Delay      |

| 4011      | V3 MSB    | 4033      | Character Height      |

| 4012      |           | 4034      | Display Control       |

| 4013      |           | 4035      | Locking Time Constant |

| 4014      |           | 4036      | Capture Time Constant |

| 4015      | SBN       | 4037      | Initial Pixel Period  |

| 4016      | TIMG      | 4038-403E | Reserved              |

| 4017-401F | Reserved  | 403F      | RST                   |

| 4020      | Color 0   | 4040-7FFF | Reserved              |

| 4021      | Color 1   |           |                       |

# 7 - SOFTWARE RESET REGISTER

| 403F | - | - | - | - |  |

|------|---|---|---|---|--|

To perform a software I<sup>2</sup>C reset of the device, set the RST bit to ONE.

This bit will be automatically reset by the device.

Software Reset will put all Write registers at their default power-on value, and reset all internal logic blocks except the I<sup>2</sup>C bus interface itself. It will not change the RAM contents.

SELXTAL This bit must be set to ONE in order to operate the oscillator in the external crystal mode.

In its ZERO default state, this bit enables the internal RC mode oscillator.

# 8 - ON-SCREEN DISPLAY

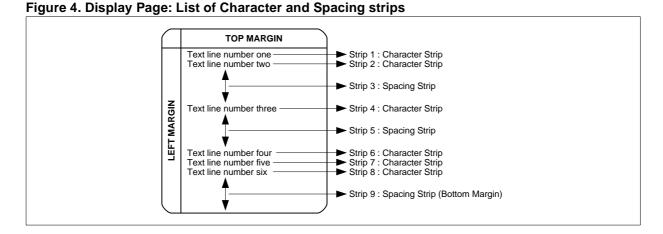

The STV9432 on-screen display is able to display any line of characters (character strip) anywhere in the screen.

Character strings are programmed by the MCU in RAM via I<sup>2</sup>C bus. Character shapes are coded in the internal ROM font. Character strips may be adjacent or separated by vertical spaces (Spacing strips).

Consequently, one display page is made of a list of Character strips and Spacing strips.

A Top Margin and a Left Margin are programmable in dedicated registers.

#### 8.1 - RAM PROGRAMMING

#### 8.1.1 - Two kinds of Data:

Strip Descriptors and Character Codes

An OSD screen is made of a number of Character and Spacing strips.

Two groups of Data make one OSD screen:

- a Strip Descriptors list,

• Text strings - one per Character strip.

Each Strip is associated with a 2 bytes Strip Descriptor.

RST

**لرک**ا

-

There are two Strip Descriptors:

- The Character Strip Descriptors containing the Text string Ram address of the Character Strip,

- The Spacing Strip Descriptors which specify the vertical space height.

In the example shown in Figure 4 on page 8, the OSD screen, is made of 9 strips.

In RAM, there is:

- one list of 9 Strip descriptors (size = 9 x 2 bytes = 18 bytes),

- 6 Text strings, each of them made of the character codes from the line of text.

Text strings can be programmed anywhere in RAM. The Descriptor list can be located at 16 different addresses in RAM. The address is defined in the Display Control Register. It is consequently possible to store up to 16 different pages in RAM.

The current Displayed page is specified in the Display Control Register. It refers to a given Page Descriptor list.

| 8.1.2 - Des<br>Spacing | scriptors                                                                                                                                                                                                                                 |                   |            |               |          |      |     |     |  |  |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|---------------|----------|------|-----|-----|--|--|--|--|--|--|

| MSB                    | 0                                                                                                                                                                                                                                         | L/ C              | -          | -             | -        | -    | -   | -   |  |  |  |  |  |  |

| LSB                    | SL7                                                                                                                                                                                                                                       | SL6               | SL5        | SL4           | SL3      | SL2  | SL1 | SL0 |  |  |  |  |  |  |

| L/C                    | <ul> <li>LINE or CHARACTER spacing:</li> <li>= 0, spacing descriptor defined as character height (SL[7:0] = 1 to 255 character).</li> <li>= 1, spacing descriptor defined as scan line height (SL[7:0] = 1 to 255 scan lines).</li> </ul> |                   |            |               |          |      |     |     |  |  |  |  |  |  |

| SL[7:0]                | : Number of selected height (character or scan lines according L/ C ).                                                                                                                                                                    |                   |            |               |          |      |     |     |  |  |  |  |  |  |

| Character              |                                                                                                                                                                                                                                           |                   |            |               |          |      |     |     |  |  |  |  |  |  |

| MSB                    | 1 DE                                                                                                                                                                                                                                      | CLU3              | CLL        | 12            | CLU1     | CLU0 | C9  | C8  |  |  |  |  |  |  |

| LSB                    | C7 C6                                                                                                                                                                                                                                     | C5                | C4         | L             | C3       | C2   | C1  | C0  |  |  |  |  |  |  |

| DE                     | <ul> <li>DE : Display enable:</li> <li>= 0, R = G = B = 0 and FBLK = FBK bit of display control register on the whole strip,</li> <li>= 1, display of the characters.</li> </ul>                                                          |                   |            |               |          |      |     |     |  |  |  |  |  |  |

| CLU[3:0]               | : Active c                                                                                                                                                                                                                                | olor selection    | at the beg | gining of the | e strip. |      |     |     |  |  |  |  |  |  |

| C[9:1]                 | : Address                                                                                                                                                                                                                                 | s of the first ch | aracter co | ode of the s  | strip.   |      |     |     |  |  |  |  |  |  |

| C0                     | : Address                                                                                                                                                                                                                                 | s 0 must be 0.    |            |               |          |      |     |     |  |  |  |  |  |  |

# 8.1.3 - Code Format

There are basically 3 kinds of code:

- the control codes from 0 to 15 (00H to 0FH),

- the ROM monochrome character codes from 16 to 255 (10H to FFH),

- the two bytes multicolor character codes from 08F0 to 08FF (Hex).

#### For code definitions see Table 1.

## Table 1 Character and Command Codes

|   | 0        | 1 | 2 | 3 | 4 | 5     | 6   | 7   | 8   | 9    | Α    | В    | С | D | Е | F |

|---|----------|---|---|---|---|-------|-----|-----|-----|------|------|------|---|---|---|---|

| 0 | col 0    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 1 | col 1    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 2 | col 2    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 3 | col 3    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 4 | col 4    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 5 | col 5    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 6 | col 6    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 7 | col 7    |   |   |   | 2 | 240 I | Mon | och | rom | e Cł | nara | cter | S |   |   |   |

| 8 | multicol |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| 9 | nop      |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| Α | vflip    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| В | hflip    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| С | dflip    |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| D | call     |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| E | rtn      |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

| F | eof      |   |   |   |   |       |     |     |     |      |      |      |   |   |   |   |

Single byte codes 00 to 0f are command codes. Single byte codes 10 to ff are monochrome character codes. Double byte codes 08F0 to 08FF are multicolor character codes.

57

#### **Control Codes**

Control codes must be followed by a displayable code, except for RTN & EOL. They must not be used twice consecutively without a displayable code between them.

The control code CALL is preceded by an address byte. The control codes are not displayed except if mentioned.

#### Codes 0 to 7 (0h to 7h):

COL0 to COL7 codes select 1 byte among 8 within the CLUT in RAM. The block selection is fixed by CLU3 bit of the active character descriptor (see Table 1 and Table 2).

#### Code 8 (08h):

Multicolor character precode, must be followed by a multicolor character number from F0h to FFh.

#### **Code 9** (09h):

NOP: no operation is performed, can be used to spare a location in RAM for an active control code.

#### Codes 10 to 12 (0Ah to 0Ch):

#### FLIPS:

*HFLIP(0Bh)* Horizontal Flip code flips horizontaly the following displayable code.

*VFLIP(0Ah)* Vertical Flip code flips vertically the following displayable code.

*DFLIP(0Ch)* Horizontal & Vertical Flip code flips horizontaly and verticaly the following displayable code.

#### Code 13 (0Dh):

CALL, this control code switches the display of the next character to the code address given by the next byte as follows:

| CALL CODE<br>(odd @) MSB     | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 1  |

|------------------------------|----|----|----|----|----|----|----|----|

| ADDRESS BYTE<br>(even @) LSB | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 |

A[9:1] : Address of the next code to be used (A0 = 0 only even addresses), in low half part of RAM.

Notes:

CALL and RTN code must be used simultaneously.

CALL and RTN codes are displayed as a SPACE character.

CALL and RTN codes must be placed at odd addresses. They may be preceded by a NOP to place them at the right position.

#### Code 14 (0Eh):

RTN: return to the CALL + 1 code location (see Note).

Code 15 (0Fh):

EOL, end of line terminates the display of the current row.

#### **ROM Character Codes**

Codes 16 to 255 (10h to FFh):

ROM monochrome character codes. The character shapes are 12x18 pixel matrix described in Figure 5 .

#### Codes 256 to 272 (F0h to FFh):

ROM multicolor character codes. They must be preceded by the multicolor pre-code 08h. The character shapes are 12x18 pixel matrix described in Figure 5.

#### 8.2 - OSD LOOK-UP TABLE

Color look-up table [CLUT] is read/write RAM table. Mapping address is described in 6.3.2 I2C Registers Mapping.

The CLUT is splitted into 2 blocks of 8 bytes. Each byte contains foreground and background informations as described below:

| TRA    | BR    | BG | BB      | FL       | FR     | FG  | FB |

|--------|-------|----|---------|----------|--------|-----|----|

| TRA    |       | :  | Transp  | arent b  | ackgro | und |    |

| FL     |       | :  | Flashir | ng foreg | ground |     |    |

| BR, BO | G, BB | :  | Backg   | round c  | olor   |     |    |

| FR, FC | G, FB | :  | Foregr  | ound c   | olor   |     |    |

Each block may store a different set of colors. One block of colors may be used for the normal items of the menu while the second block, with brighter colors, may be used for selected items of the menu.

The block selection is done by programming bit CLU3 of CLU[3:0] of the character descriptor (see Table 2). It remains selected for the whole row.

Bit CLU2, CLU1 and CLU0 of CLU[3:0] of the character descriptor select the active color at the beginning of the row.

The active color can be modified along the row, using 8 control codes COL0 to COL7.

Each control code (COL0 to COL7) activates a dedicated color byte in the CLUT as described in Table 2.

| CLU3 | CLU[2:0] | Code Name | Command<br>Code (hex) | Ram @(hex) | Reset Value<br>(hex) |

|------|----------|-----------|-----------------------|------------|----------------------|

|      | 0        | Col 0     | 00                    | @4020      | 07                   |

|      | 1        | Col 1     | 01                    | @4021      | 16                   |

| 0    | 2        | Col 2     | 02                    | @4022      | 25                   |

|      | 3        | Col 3     | 03                    | @4023      | 34                   |

|      | 4        | Col 4     | 04                    | @4024      | 43                   |

|      | 5        | Col 5     | 05                    | @4025      | 52                   |

|      | 6        | Col 6     | 06                    | @4026      | 61                   |

|      | 7        | Col 7     | 07                    | @4027      | 70                   |

|      | 0        | Col 0     | 00                    | @4028      | 70                   |

|      | 1        | Col 1     | 01                    | @4029      | 61                   |

|      | 2        | Col 2     | 02                    | @402A      | 52                   |

| 1    | 3        | Col 3     | 03                    | @402B      | 43                   |

|      | 4        | Col 4     | 04                    | @402C      | 34                   |

|      | 5        | Col 5     | 05                    | @402D      | 25                   |

|      | 6        | Col 6     | 06                    | @402E      | 16                   |

|      | 7        | Col 7     | 07                    | @402F      | 07                   |

# Table 2CLUT Block Selection

# 8.3 - OSD CONTROL REGISTERS

| Line Dura | tior | <b>n</b> (reset va                      | lue: 20H)      |                            |     |     |     |     |     |

|-----------|------|-----------------------------------------|----------------|----------------------------|-----|-----|-----|-----|-----|

| 4030      |      | VSP                                     | HSP            | LD6                        | LD5 | LD4 | LD3 | LD2 | LD1 |

| VSP       | :    | V-SYNC a<br>= 0, falling<br>= 1, rising |                | election                   |     |     |     |     |     |

| HSP       | :    | HFLY act<br>= 0, rising<br>= 1, falling |                | ction                      |     |     |     |     |     |

| LD[6:1]   | :    |                                         | periods of cha | aracter<br>s 12 pixels lor | ng. |     |     |     |     |

# Top Margin (reset value: 30H)

| 4031   | M9                                | M8                               | M7          | M6           | M5    | M4                | M3             | M2         |

|--------|-----------------------------------|----------------------------------|-------------|--------------|-------|-------------------|----------------|------------|

| M[9:2] | : TOP MA<br>M0 = 0, M<br>M2 = 4 s | -                                | rom the VSY | NC reference | edge. |                   |                |            |

| Note   |                                   | margin is disp<br>DL register is |             |              |       | list. It can be t | olack if FBK o | of DISPLAY |

| Horizonta | l De   | lay (reset                          | t value: 20H,            | )                                   |                |                 |                 |                |                        |

|-----------|--------|-------------------------------------|--------------------------|-------------------------------------|----------------|-----------------|-----------------|----------------|------------------------|

| 4032      |        | DD7                                 | DD6                      | DD5                                 | DD4            | DD3             | DD2             | DD1            | DD0                    |

|           |        |                                     |                          |                                     |                |                 |                 |                |                        |

| DD[7:0]   | t<br>I | ter strips.<br>Unit = 6 pi          | xel periods. N           |                                     | e is 08H. Firs | t pixel positio | on = [DD[7:0] - | ·              | of the charac-<br>vith |

| Character | rs He  | eight (res                          | et value: 24             | H)                                  |                |                 |                 |                |                        |

| 4033      |        | -                                   | -                        | CH5                                 | CH4            | CH3             | CH2             | CH1            | CH0                    |

|           | L      |                                     |                          |                                     |                |                 |                 |                |                        |

| CH[5:0]   | I      | HEIGHT o<br>played is g<br>SLICE-NU | jiven by:                | er strips in sca                    | an lines. For  | each scan lin   | e, the number   | of the slice w | vhich is dis-          |

|           |        | (                                   | SCAN-LIN                 | E-NUMBER x                          | (18)           |                 |                 |                |                        |

|           |        | round                               | (                        | CH[5:0]                             |                |                 |                 |                |                        |

|           | :      | SCAN-LIN                            | E-NUMBER                 | = Number of t                       | the current so | can line of the | e strip.        |                |                        |

| Dienlay C | ontr   | ol (reset                           | Value: 00H)              |                                     |                |                 |                 |                |                        |

| 4034      |        | OSD                                 | FBK                      | FL1                                 | FL0            | P9              | P8              | P7             | P6                     |

| 1001      |        | 000                                 | 1 Bit                    |                                     | 1 20           |                 | 10              |                | 10                     |

| OSD       |        |                                     |                          | and FBLK out                        | toute are 0)   |                 |                 |                |                        |

| FBK       | :      |                                     | king control:            | anu FBLK Uu                         | ipuis ale 0).  |                 |                 |                |                        |

| 1 BIX     | •      | = 1, force                          | s FBLK pin a             | t "1" outside a                     |                |                 |                 |                |                        |

|           |        |                                     |                          | eo RGB and                          |                |                 |                 | data           |                        |

| FL[1:0]   |        | Flashing                            | •                        | according cr                        |                | e lor normal d  | isplay of OSD   | uala.          |                        |

| 1 [1.0]   | •      | •                                   |                          | character attr                      | ibute is ianor | ed              |                 |                |                        |

|           |        |                                     | •                        | % duty cycle)                       | •              | ou,             |                 |                |                        |

|           |        |                                     | hing at 2 f <sub>F</sub> | ,,.,.,.,,.,,                        | 1              |                 |                 |                |                        |

|           |        |                                     | hing at 4 f <sub>F</sub> |                                     |                |                 |                 |                |                        |

|           |        |                                     |                          | rtical frequen                      | су.            |                 |                 |                |                        |

| P[9:6]    | :      |                                     |                          | criptor of the 0<br>0; up to 16 dif |                |                 | d in the RAM.   |                |                        |

| Locking ( | Conc   | dition Tim                          | ne Constant              | (reset value                        | : 01H)         |                 |                 |                |                        |

| 0       |     |          |                 | `              | ,            |                |                 |        |     |

|---------|-----|----------|-----------------|----------------|--------------|----------------|-----------------|--------|-----|

| 4035    |     | FR       | AS2             | AS1            | AS0          | LUK            | BS2             | BS1    | BS0 |

|         |     |          |                 |                |              |                |                 |        |     |

| FR      | : F | ree Run  | nning; if = 1 P | LL is disabled | and the pixe | el frequency k | eeps its last v | /alue. |     |

| AS[2:0] | : P | hase co  | onstant during  | locking cond   | litions.     |                |                 |        |     |

| BS[2:0] | : F | requend  | cy constant d   | uring locking  | conditions.  |                |                 |        |     |

| LUK     | : L | ock unlo | ock status bit  |                |              |                |                 |        |     |

|         | 0   | = unloc  | ked PLL         |                |              |                |                 |        |     |

|         | 1   | = Locke  | ed PLL          |                |              |                |                 |        |     |

|         |     |          |                 |                |              |                |                 |        |     |

\_\_\_\_\_

57

| Capture P    | roc   | ess Time          | Constant (                           | eset value: 2  | 24H)         |         |     |     |     |

|--------------|-------|-------------------|--------------------------------------|----------------|--------------|---------|-----|-----|-----|

| 4036         |       | LEN               | AF2                                  | AF1            | AF0          | -       | BF2 | BF1 | BF0 |

| LEN          | :     |                   | ble<br>3, FBLK are a<br>3,, FBLK are | ,              | ,            | locked. |     |     |     |

| AF[2:0]      | :     | Phase co          | onstant during                       | the capture    | process.     |         |     |     |     |

| BF[2:0]      | :     | Frequenc          | cy constant du                       | uring the capt | ure process. |         |     |     |     |

| Initial Pixe | el Po | <b>eriod</b> (res | et value: 06l                        | H)             |              |         |     |     |     |

|      |     |     | •   |     |     |     |     |     |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 4037 | PP7 | PP6 | PP5 | PP4 | PP3 | PP2 | PP1 | PP0 |

|      |     |     |     |     |     |     |     |     |

PP[7:0] : Value to initialize the pixel period of the PLL.

#### 8.4 - OSD TIMINGS

The number of pixel periods is given by the LINE DURATION register and is equal to:

[LD[6:1] x 2 + 1 ] x 12.

(LD[6:1]: value of the LINE DURATION register).

This value is used to define the horizontal size of the characters.

The horizontal left margin is given by the HORI-ZONTAL DELAY register and is equal to:

(DD[7:0] -6) x 6 + 54

(DD[7:0]: value of the DISPLAY DELAY register).

This value is used to define the horizontal position of the characters on the screen. Due to internal logic, minimum horizontal delay is fixed at 4.5 characters (54 pixel) when DD is even and inferior or equal to 6, and it is fixed at 5 characters (60 pixel) when DD is odd and inferior or equal to 7.

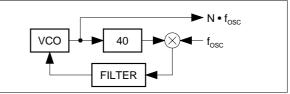

#### 8.5 - PLL

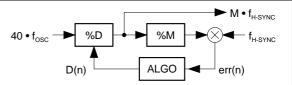

The PLL function of the STV9432 provides the internal pixel clock locked on the horizontal synchro signal and used by the display processor to generate the R, G, B and fast blanking signals. It is made of 2 PLLs. The first PLL which is analog (see Figure 6) provides a high frequency that is 40 times the internal oscillator frequency, or 320MHz. This high frequency clock is used by the Display controller.

The 320MHz frequency is then divided by three. The resulting 106.7MHz clock is used by the Video timings analysis block. The second PLL, fully digital (see Figure 7), provides a pixel frequency locked on the horizontal synchro signal. The ratio between the frequencies of these 2 signals is:

$M = 12 \times (LD[6:1] \times 2 + 1)$  where LD[6:1] is the value of the LINE DURATION register.

#### Figure 6. Analog PLL

Figure 7. Digital PLL

## 8.5.1 - Programming of the PLL Registers Initial Pixel Period (@4037)

This register allows to increase the speed of the PLL convergence when the horizontal frequency changes (new graphic standard).

The relationship between PP[7:0], LD[6:1],  $f_{\mbox{HSYNC}}$  and  $f_{\mbox{OSC}}$  is:

$$PP[7:] = round \begin{pmatrix} 40 \cdot f_{OSC} \end{pmatrix}$$

$$6^{\cdot} (2^{\cdot} LD + 1)^{\cdot} f_{HSYNC}$$

#### Locking Condition Time Constant (@ 4035)

This register provides the AS[2:0] and BS[2:0] constants used by the algo part of the PLL (see Figure 6). These two constants as well as the phase error (err(n)) give the new value (Dn) of the high frequency signal division. Consequently, AS[2:0] and BS[2:0] fix the pixel clock frequency. These two constants are used only in locking condition, if the phase error is inferior to a fixed value during at least 4 scan lines. If the phase error becomes superior to the fixed value, the PLL is not in locking condition but in capture process. In this case, the algo part of the PLL uses the other constants AF[2:0] and BF[2:0] from the next register.

#### Capture Process Time Constant (@ 4036)

The choice between these two time constants (locking condition or capture process) allows to decrease the capture process time by changing the time response of the PLL.

#### 8.5.2 - How to choose the time constant value

The time response of the PLL is given by its characteristic equation which is:

$(x - 1)^2 + (\alpha + \beta) \cdot (x - 1) + \beta = 0$ Where:

$\alpha$  = 3  $\cdot$  LD[6:1]  $\cdot$  2<sup>A -11</sup> and  $\beta$  = 3  $\cdot$  LD[6:1]  $\cdot$  2<sup>B - 19</sup>

(LD[6:1] = value of the LINE DURATION register,

A = value of the 1st time constant, AF or AS and B = value of the  $2^{d}$  time constant, BF or BS).

As can be seen, the solution depends only on the LINE DURATION and the TIME CONSTANTS given by the  $I^2C$  registers.

#### Table 3 Valid Time Constants Examples

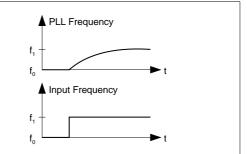

If  $(\alpha + \beta)^2 - 4\beta \ge 0$  and  $2\alpha - \beta < 4$ , the PLL is stable and its response is as shown in Figure 15.

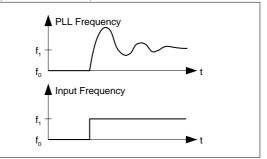

If  $(\alpha + \beta)^2 - 4\beta \le 0$ , the response of the PLL is as shown in Figure 9. In this case the PLL is stable if  $\tau > 0.7$  damping coefficient.

Table 3 gives some good values for A and B constants for different values of the LINE DURATION.

Figure 8. Time Response of the PLL/ Characteristic equation solutions (with real solutions)

Figure 9. Time Response of the PLL/ Characteristic equation solutions (with complex solutions)

|       |      |                     | inpioo | _    |      |      | <u>.</u> |

|-------|------|---------------------|--------|------|------|------|----------|

| B \ A | 0    | 1                   | 2      | 3    | 4    | 5    | 6        |

| 0     | YYYY | YYYY                | YYYY   | YYYN | YNNN | NNNN | NNNN     |

| 1     | YYYY | YYYY                | YYYY   | YYYN | YNNN | NNNN | NNNN     |

| 2     | NYYY | YYYY                | YYYY   | YYYN | YNNN | NNNN | NNNN     |

| 3     | NNNY | YYYY                | YYYY   | YYYN | YNNN | NNNN | NNNN     |

| 4     | NNNN | NYYY <sup>(1)</sup> | YYYY   | YYYN | YNNN | NNNN | NNNN     |

| 5     | NNNN | NNNY                | YYYY   | YYYN | YNNN | NNNN | NNNN     |

| 6     | NNNN | NNNN                | NYYY   | YYYN | YNNN | NNNN | NNNN     |

| 7     | NNNN | NNNN                | NNNY   | YYYN | YNNN | NNNN | NNNN     |

Notes: - Table meaning: N = No possible capture - No stability, Y = PLL can lock. - Case of A[2:0] = 1 (001) and B[2:0] = 4 (100):

| LD[6:1]              | 8 | 16 | 24 | 32 |

|----------------------|---|----|----|----|

| Valid Time Constants | N | Y  | Y  | Y  |

**/**

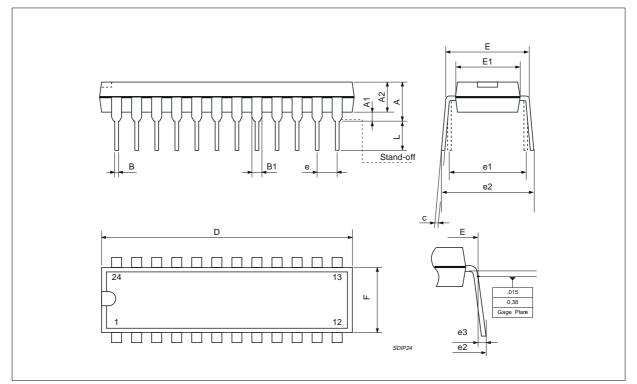

# PACKAGE MECHANICAL DATA

24 PINS - PLASTIC DIP (SHRINK)

| Dimensions |       | Millimeters |       |        | Inches |        |

|------------|-------|-------------|-------|--------|--------|--------|

|            | Min.  | Тур.        | Max.  | Min.   | Тур.   | Max.   |

| A          |       |             | 5.08  |        |        | 0.20   |

| A1         | 0.51  |             |       | 0.020  |        |        |

| A2         | 3.05  | 3.30        | 4.57  | 0.120  | 0.130  | 0.180  |

| В          | 0.36  | 0.46        | 0.56  | 0.0142 | 0.0181 | 0.0220 |

| B1         | 0.76  | 1.02        | 1.14  | 0.030  | 0.040  | 0.045  |

| С          | 0.23  | 0.25        | 0.38  | 0.0090 | 0.0098 | 0.0150 |

| D          | 22.61 | 22.86       | 23.11 | 0.890  | 0.90   | 0.910  |

| E          | 7.62  |             | 8.64  | 0.30   |        | 0.340  |

| E1         | 6.10  | 6.40        | 6.86  | 0.240  | 0.252  | 0270   |

| е          |       | 1.778       |       |        | 0.070  |        |

| e1         |       | 7.62        |       |        | 0.30   |        |

| e2         |       |             | 10.92 |        |        | 0.430  |

| e3         |       |             | 1.52  |        |        | 0.060  |

| L          | 2.54  | 3.30        | 3.81  | 0.10   | 0.130  | 0.150  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics.

© 2000 STMicroelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of STMicroelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

#### STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Korea - Malaysia - Malta -Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand -United Kingdom - U.S.A.

http://www.st.com

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com