查询TVP5020供应商

TEXAS INSTRUMENTS

WWW.DZS

May 2000

**Mixed-Signal Products**

SLAS186B

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

| Contents |  |

|----------|--|

|----------|--|

| Se | ction                                           | Title                                                                                                                                                                                                     | Page                                      |

|----|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1  | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | duction         Features         Applications         Functional Block Diagram         Terminal Assignments         Ordering Information         Terminal Functions                                       | . 1–1<br>. 1–2<br>. 1–2<br>. 1–3<br>. 1–3 |

| 2  | <b>Deta</b><br>2.1                              | Analog Video Processors and A/D Converter         2.1.1 Video Input Selection         2.1.2 Analog Input Clamping and Automatic Gain Control Circuits                                                     | . 2–1<br>. 2–1<br>. 2–1                   |

|    | 2.2                                             | <ul> <li>2.1.3 A/D Converter</li> <li>Digital Processing</li> <li>2.2.1 Y/C Separation</li> <li>2.2.2 Luminance Processing</li> <li>2.2.3 Chrominance Processing</li> <li>2.2.4 Clock Circuits</li> </ul> | . 2–1<br>. 2–2<br>. 2–3<br>. 2–6          |

|    | 2.3                                             | <ul> <li>Video Output Format</li></ul>                                                                                                                                                                    | . 2–7<br>. 2–8<br>. 2–9                   |

|    | 2.4                                             | Synchronization Signals                                                                                                                                                                                   |                                           |

|    | 2.5                                             | I <sup>2</sup> C/VIP/VMI Host Interface                                                                                                                                                                   |                                           |

|    | 2.6                                             | I <sup>2</sup> C Interface                                                                                                                                                                                |                                           |

|    | 2.0                                             | 2.6.1 I <sup>2</sup> C Host Port Select                                                                                                                                                                   |                                           |

|    |                                                 | 2.6.2 I <sup>2</sup> C Write Operation                                                                                                                                                                    |                                           |

|    |                                                 | 2.6.3 I <sup>2</sup> C Read Operation                                                                                                                                                                     |                                           |

|    |                                                 | 2.6.4 I <sup>2</sup> C Microcode Write Operation                                                                                                                                                          |                                           |

|    |                                                 | 2.6.5 I <sup>2</sup> C Microcode Read Operation                                                                                                                                                           |                                           |

|    | 2.7                                             | VIP Host Interface Port                                                                                                                                                                                   |                                           |

|    | 2.1                                             | 2.7.1 VIP Host Port Terminal Description                                                                                                                                                                  |                                           |

|    |                                                 | 2.7.2 VIP Phases                                                                                                                                                                                          |                                           |

|    |                                                 | 2.7.3 Command Byte                                                                                                                                                                                        |                                           |

|    |                                                 | 2.7.4 VIP Microcode Write Operation                                                                                                                                                                       |                                           |

|    |                                                 | 2.7.5 VIP Microcode Read Operation                                                                                                                                                                        |                                           |

|    | 2.8                                             | Video Module Interface (VMI) Host Interface                                                                                                                                                               |                                           |

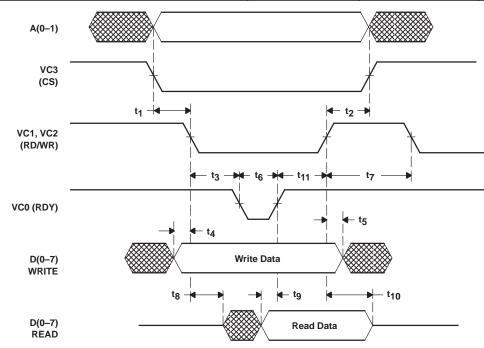

|    | 2.9                                             | Host Port – Mode A Timing                                                                                                                                                                                 |                                           |

|    | 2.10                                            | Host Port – Mode B Timing                                                                                                                                                                                 |                                           |

|    |                                                 | Host Port – Mode C Timing (PPC)                                                                                                                                                                           |                                           |

|      | 2.11.1 VMI Register Mapping                       | 2–29 |

|------|---------------------------------------------------|------|

|      | 2.11.2 VMI Microcode Write Operation              | 2–30 |

|      | 2.11.3 VMI Microcode Read Operation               | 2–31 |

| 2.12 | Genlock Control                                   | 2–31 |

| 2.13 | VBI Data Processor                                | 2–32 |

|      | 2.13.1 Teletext Data Byte Order                   | 2–32 |

|      | 2.13.2 Teletext as Ancillary Data in Video Stream | 2–33 |

| 2.14 | Reset                                             | 2–36 |

| 2.15 | Internal Control Registers                        | 2–37 |

|      | 2.15.1 Register Definitions                       |      |

|      | 2.15.2 Vendor ID                                  |      |

|      | 2.15.3 Device ID                                  |      |

|      | 2.15.4 Subsystem Vendor ID                        |      |

|      | 2.15.5 Subsystem Device ID                        |      |

|      | 2.15.6 Subsystem Revision ID                      |      |

|      | 2.15.7 Analog Input Source Selection              |      |

|      | 2.15.8 Analog Channel Controls                    |      |

|      | 2.15.9 Operation Mode Controls                    |      |

|      | 2.15.10 Miscellaneous Controls                    |      |

|      | 2.15.11 Color Killer Threshold Control            |      |

|      | 2.15.12 Luminance Processing Control 1            |      |

|      | 2.15.13 Luminance Processing Control 2            |      |

|      | 2.15.14 Brightness Control                        |      |

|      | 2.15.15 Color Saturation Control                  |      |

|      | 2.15.16 Hue Control                               |      |

|      | 2.15.17 Contrast Control                          |      |

|      | 2.15.18 Outputs and Data Rates Select             |      |

|      | 2.15.19 Horizontal Sync (HSYN) Start              |      |

|      | 2.15.20 Vertical Blanking Start                   |      |

|      | 2.15.21 Vertical Blanking Stop                    |      |

|      | 2.15.22 Chrominance Control                       |      |

|      | 2.15.23 Digital Channel Selection                 |      |

|      | 2.15.24 Firmware Version                          |      |

|      | 2.15.25 Status Register 1                         |      |

|      | 2.15.26 Status Register 2                         |      |

|      | 2.15.27 AGC Gain                                  |      |

|      | 2.15.28 TXF Filter #1 Parameters                  |      |

|      | 2.15.29 TXF Filter #2 Parameters                  |      |

|      | 2.15.30 TXF Error Filtering Enables               |      |

|      | 2.15.31 TXF Transaction Processing Enables        |      |

|      | 2.15.32 TTX Control Register                      |      |

|      | 2.15.33 Line Enable Registers                     |      |

|      | 2.15.34 Sync Pattern Register                     |      |

|      | 2.15.35 Teletext FIFO                             |      |

|      | 2.15.36 Closed Caption Data                       |      |

|      | 2.15.37 Buffer Status                             |      |

|      | 2.15.38 Interrupt Threshold                       | 2-60 |

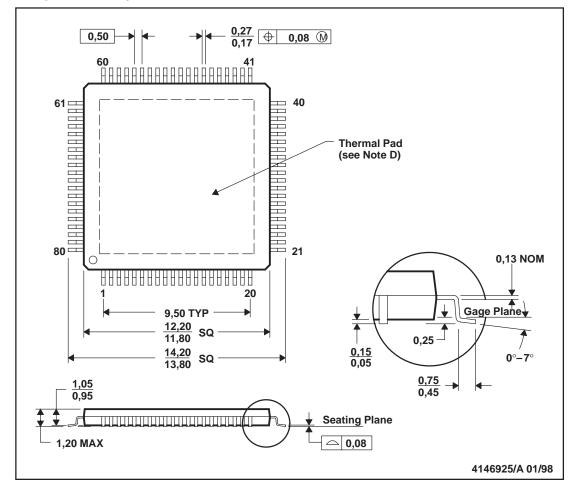

| 4 | Мес  | hanical Data                                                                                                                                                       |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

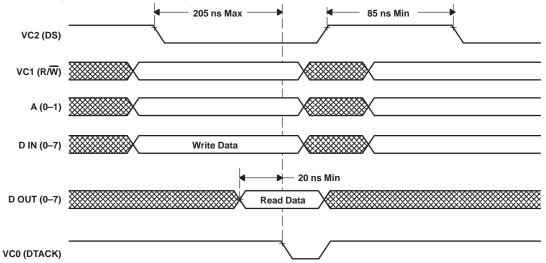

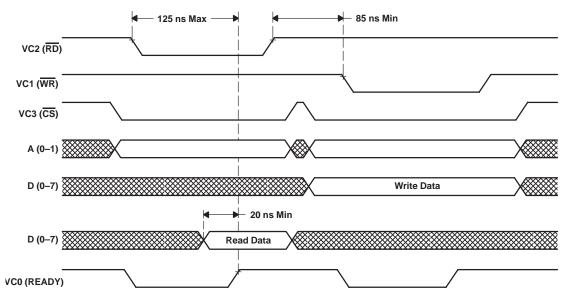

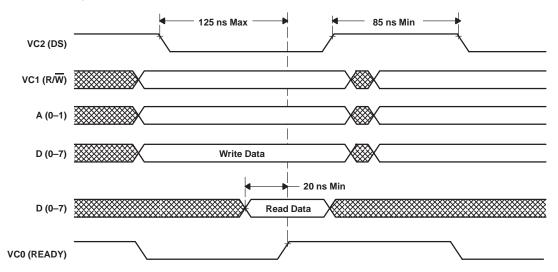

|   |      | 3.4.3       VIP Host Port Timing       3–4         3.4.4       VMI Host Port Timing (Mode A)       3–5         3.4.5       VMI Host Port Timing (Mode B)       3–6 |

|   |      | 3.4.2 I <sup>2</sup> C Host Bus Timing                                                                                                                             |

|   |      | 3.4.1 Clocks, Video Data, Sync Timing 3–3                                                                                                                          |

|   | 3.4  | Timing                                                                                                                                                             |

|   |      | 3.3.2 DC Electrical Characteristics 3–2                                                                                                                            |

|   |      | 3.3.1 Analog Processing and Analog-to-Digital Converter 3–2                                                                                                        |

|   | 3.3  | Electrical Characteristics 3–2                                                                                                                                     |

|   | 3.2  | Recommended Operating Conditions 3–1                                                                                                                               |

|   | 3.1  | Absolute Maximum Ratings† 3–1                                                                                                                                      |

| 3 | Elec | trical Specifications                                                                                                                                              |

|   |      | 2.15.44 Interrupt Status Register                                                                                                                                  |

|   |      | 2.15.43 Interrupt Configuration Register                                                                                                                           |

|   |      | 2.15.42 Interrupt Enable Register                                                                                                                                  |

|   |      | 2.15.40 FIFO Control                                                                                                                                               |

|   |      | 2.15.39 Interrupt Line Number                                                                                                                                      |

|   |      | 2.15.20 Interrupt Line Number                                                                                                                                      |

v

# List of Illustrations

| Figure                                  | Title                                     | Page |

|-----------------------------------------|-------------------------------------------|------|

| 2-1 Analog Video Processo               | rs and A/D Converter                      | 2–1  |

|                                         | cessing Block Diagram                     |      |

|                                         | quency Response for 13.5 MHz Sampling     |      |

| 2-4 Chroma Trap Filter Fred             | quency Response for Square-Pixel Sampling | 2–3  |

| 2-5 Luminance Edge-Enhar                | ncer                                      | 2–4  |

| 2-6 Peaking Filter Response             | e, 13.5 MHz Sampling                      | 2–4  |

|                                         | e, NTSC AND PAL-M SQUARE PIXEL            |      |

| 2-8 Peaking Filter Response             | e, PAL Square Pixel                       | 2–5  |

|                                         | g Circuit                                 |      |

|                                         | ~                                         |      |

| 2–11 Reference Clock Confi              | igurations                                | 2–7  |

|                                         | ~                                         |      |

| 2-13 4:1:1 Sampling                     |                                           | 2–8  |

| 2-14 16-Bit 4:2:2 Output Fo             | rmat                                      | 2–8  |

| 2-15 12-bit 4:1:1 Output For            | rmat                                      | 2–9  |

| 2-16 8-Bit 4:2:2 and ITU-R              | BT.656 Output Formats                     | 2–9  |

| 2-17 Vertical Synchronization           | on Signals                                | 2–10 |

| 2-18 Horizontal Synchroniza             | ation Signals                             | 2–11 |

| 2–19 Host Interface                     |                                           | 2–12 |

| 2-20 I <sup>2</sup> C Data Transfer Exa | mple                                      | 2–13 |

| 2-21 VIP Transfer Example               |                                           | 2–20 |

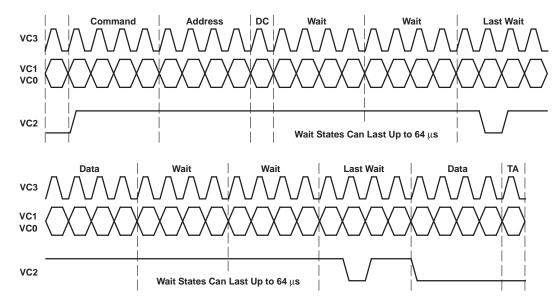

| 2-22 Functional Timing Rea              | ading From TVP (Example)                  | 2–22 |

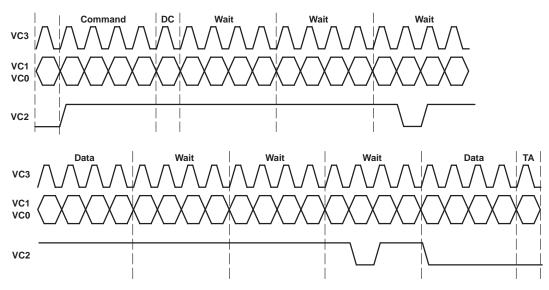

| 2-23 Functional Timing Writ             | ting to TVP (Example)                     | 2–23 |

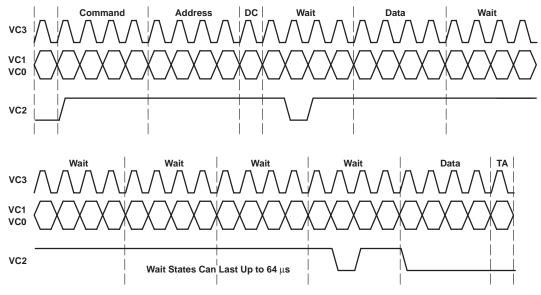

|                                         | ading From FIFO (Example)                 |      |

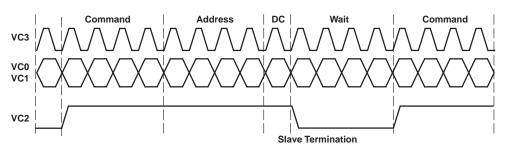

|                                         | mple of Slave Termination                 |      |

|                                         | . Timing                                  |      |

|                                         | ing                                       |      |

|                                         | ing                                       |      |

| 2-29 VMI Address Register               | Map                                       | 2–29 |

|                                         |                                           |      |

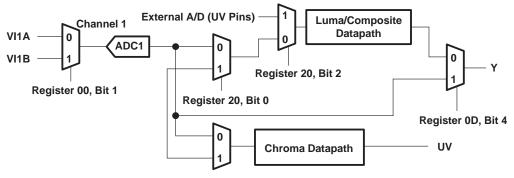

|                                         | election                                  |      |

|                                         | Timing                                    |      |

|                                         |                                           |      |

|                                         |                                           |      |

|                                         | Mode A)                                   |      |

| 3-5 VMI Host Port Timing (M             | Mode B)                                   | 3–6  |

# **List of Tables**

| Table                                               | Title                   | Page  |

|-----------------------------------------------------|-------------------------|-------|

| 2-1 Summary of the Line Frequencies, Data           | Rates, and Pixel Counts | . 2–7 |

| 2-2 Host Port Select                                |                         | 2–12  |

| 2-3 I <sup>2</sup> C Host Port Terminal Description |                         | 2–13  |

| 2-4 VIP Host Port Terminal Description              |                         | 2–20  |

| 2–5 VIP Host Port Phase Description                 |                         | 2–21  |

| 2-6 Condensed Table Command/Address .               |                         |       |

| 2–7 VMI Host Port Select                            |                         | 2–26  |

| 2-8 VMI Host Port Terminal Definitions              |                         |       |

| 2–9 Teletext Byte Order                             |                         | 2–32  |

| 2-10 NABTS 525/625-Line Ancillary Data Se           |                         |       |

| 2-11 WST 525-Line Ancillary Data Sequence           | e                       | 2–35  |

| 2-12 WST 625-Line Ancillary Data Sequence           |                         |       |

| 2–13 Dummy Timing Ancillary Data Sequence           | e                       | 2–36  |

| 2–14 Ancillary Data ID                              |                         | 2–36  |

| 2–15 Power-Up Reset Sequence                        |                         |       |

| 2–16 Registers Summary                              |                         | 2–37  |

| 2–17 Analog Channel and Video Mode Selec            |                         |       |

| 2–18 YUV Output Controls                            |                         | 2–43  |

I

# 1 Introduction

The TVP5020 is a high-quality single-chip digital video decoder that converts base-band analog NTSC and PAL video signals into digital component video. Sampling is square-pixel or ITU-R BT.601 (13.5 MHz) and is line-locked for correct pixel alignment. The output formats can be 8-bit or 16-bit 4:2:2, 12-bit 4:1:1, or 8-bit ITU-R BT.656. The TVP5020 uses TI patented technology for locking to weak, noisy, or unstable signals. A genlock control output is generated for synchronizing downstream video encoders.

Two-line (1-H delay) comb filtering is available for both the luma and chroma data paths to reduce both cross-luma and cross-chroma artifacts; a chroma trap filter is also available. Video characteristics including hue, contrast, and saturation are programmable using one of five supported host port interfaces. The TVP5020 generates synchronization, blanking, field, lock, and clock signals in addition to digital video outputs.

The TVP5020 includes advanced vertical blanking interval (VBI) data retrieval. The VBI data processor slices, parses, and performs error checking on teletext data in several formats. A built-in FIFO stores up to 14 lines of teletext data and, with proper host port synchronization, full-field teletext retrieval is possible. The VBI data processor also retrieves closed-caption data.

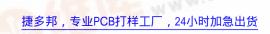

The main blocks of TVP5020 include:

- Analog processors and A/D converter

- Y/C separation

- Chrominance processor

- Luminance processor

- Clock/Timing processor and power-down control

- Output formatter

- Host port interface

- VBI data processor

#### 1.1 Features

- NTSC (M) and PAL (B, D, G, H, I, M, N) composite video

- Two analog video inputs for up to two composite inputs

- Single built-in-analog signal processing channels with clamping and AGC

- Single high speed 8-bit A/D converter

- Patented architecture for locking to weak, noisy, or unstable signals

- Comb filters for both cross-color and cross-luminance noise reductions

- Line locked clock and sampling

- Programmable data rates:

- 12.2727 MHz square-pixel (NTSC)

- 14.7500 MHz square-pixel (PAL)

- 13.5 MHz ITU-R BT.601 (NTSC and PAL)

- Programmable output formats: 16-bit or 8-bit 4:2:2 YCbCr, 12-Bit 4:1:1 YCbCr and ITU-R BT.656 with embedded syncs

- Teletext (NABTS, WST) and closed caption decode with FIFO

- ITU-R BT.601 or extended coding range

- Programmable host port options including I<sup>2</sup>C, VMI (3 modes), and VIP

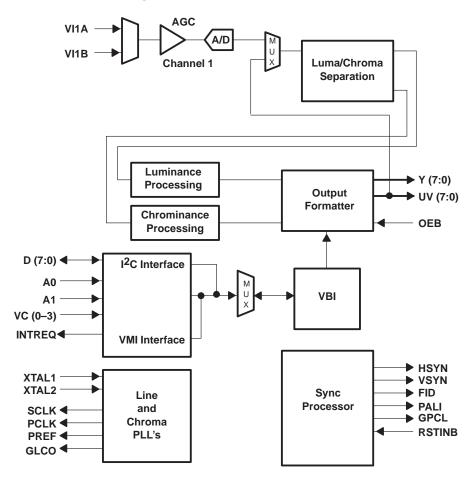

- 80-terminal TQFP package

# 1.2 Applications

- Digital image processing

- Video conferencing

- Multimedia

- Digital video

- Desktop video

- Video capture

- Video editing

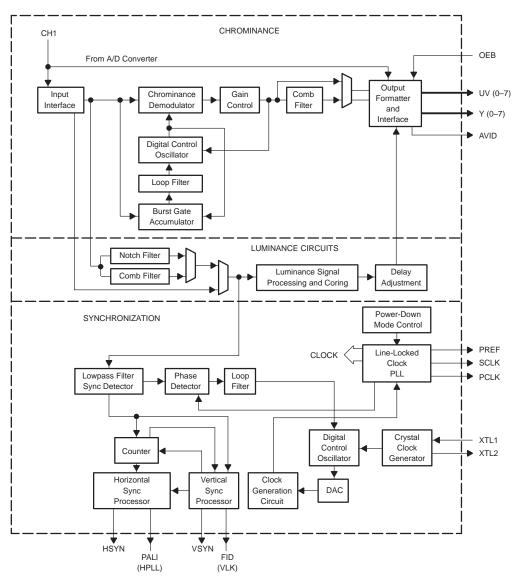

#### 1.3 Functional Block Diagram

# **1.4 Terminal Assignments**

#### 1.5 Ordering Information

| DEVICE: | TVP5020CPFP                     |

|---------|---------------------------------|

| PFP:    | Plastic flat-pack with PowerPAD |

| TERMIN         | AL                                      |     |                                                                                                                                                                                                                                             | DECODIDITIONO                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |

|----------------|-----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|

| NAME           | NO.                                     | 1/0 | DESCRIPTIONS                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| Analog video   |                                         |     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| VI_1A<br>VI_1B | 5<br>4                                  | I   | Analog video inputs. Up to two recommended coupling capa                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                             | s must be AC coupled. The          |  |  |

| Clock Signals  |                                         |     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

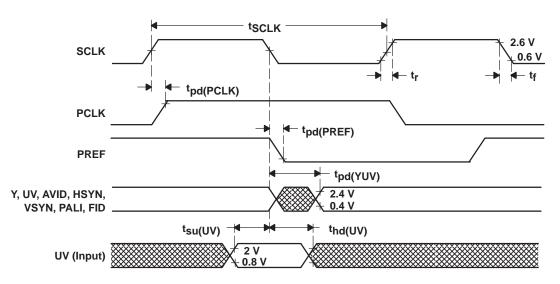

| PCLK           | 40                                      | 0   | Pixel clock output. The free 14.75 MHz for square-pixel P                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| PREF           | 39                                      | 0   | Clock phase reference signal.<br>clock data that is changing at                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                             | dges when SCLK is used to          |  |  |

| SCLK           | 38                                      | 0   | System clock output with twic                                                                                                                                                                                                               | e the frequency of the pixe                                                                                                                                                                                                                                                                                                                                                 | clock (PCLK).                      |  |  |

| XTAL1<br>XTAL2 | 35<br>36                                | I   | oscillator or to one terminal of<br>other terminal of the crystal<br>sampling uses an oscillator fro                                                                                                                                        | External clock reference. The user may connect XTAL1 to a TTL-compatible oscillator or to one terminal of a crystal oscillator. The user may connect XTAL2 to the other terminal of the crystal oscillator or not connect XTAL2 at all. Square pixel sampling uses an oscillator frequency of 26.800 MHz. ITU-R BT.601 sampling uses an oscillator frequency of 24.576 MHz. |                                    |  |  |

| Digital Video  |                                         |     | •                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| EXT_DATA_8     | 61                                      | Ι   | Bit [8] of a 9-or 10-bit digital c                                                                                                                                                                                                          | omposite video input                                                                                                                                                                                                                                                                                                                                                        |                                    |  |  |

| UV[0:7]        | 51, 52,<br>53, 55,<br>56, 58,<br>59, 60 | I/O | Digital chrominance outputs. These terminals may be configured to output data from the channel 2 A/D converter. A vendor modifiable subsystem ID may be initialized by configuring the UV [7:0] terminals with pull-up/pull-down resistors. |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| Y[0:7]         | 41, 42,<br>43, 45,<br>46, 48,<br>49, 50 | 0   | Digital luminance outputs, or multiplexed luminance and chrominance outputs.<br>These terminals may be configured to output data from the channel 1 A/D converter.                                                                          |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| HOST PORT-b    | ous                                     |     | VMI                                                                                                                                                                                                                                         | l <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                            | VIP                                |  |  |

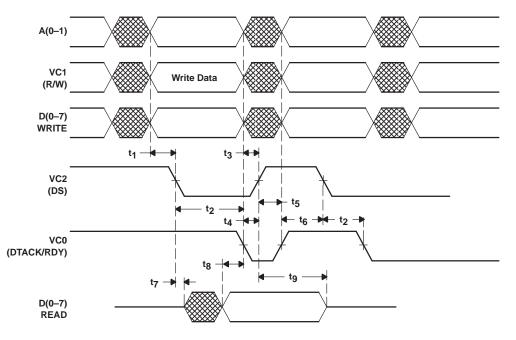

| A[0:1]         | 73, 74                                  | I   | VMI address port                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| D[0:7]         | 63, 64<br>66, 67<br>69, 70<br>71, 72    | I/O | VMI data port – bit [7:0].                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

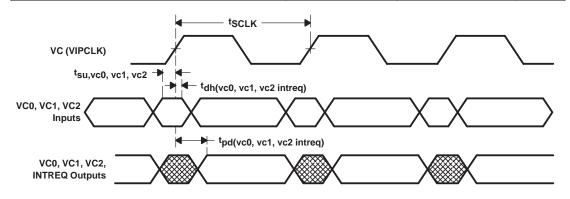

| INTREQ         | 80                                      | 0   | Interrupt request (INTREQ)                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                             | Interrupt request (VIRQ)           |  |  |

| VC0            | 79                                      | I/O | VMI port data ack. or ready signal (DTACK)                                                                                                                                                                                                  | Serial clock (SCL)                                                                                                                                                                                                                                                                                                                                                          | Hardware address<br>bit-0 (HAD[0]) |  |  |

| VC1            | 78                                      | I/O | VMI Port Read-Write or         Serial data (SDA)         Hardware address bit-1           Write (RW/WR)         HAD[1]                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| VC2            | 77                                      | I/O | VMI port data strobe or read Hardware control (HCTL) signal (DS/RD)                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

| VC3            | 76                                      | I   | VMI port chip select. (VC) Slave address select VIPCLK (I <sup>2</sup> CA)                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                             |                                    |  |  |

# **1.6 Terminal Functions**

| TERMINAL         |                                  |     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------|----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  | I/O                              |     | DESCRIPTIONS                                                                                                                                                                                                                                                                                                        |  |  |  |

| NAME             |                                  |     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Miscellaneous    |                                  |     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| GPCL             | 26                               | I/O | <ul><li>General-purpose control logic. This terminal has three functions:</li><li>1. General-purpose output. In this mode the state of GPCL is directly programmed via the host port.</li></ul>                                                                                                                     |  |  |  |

|                  |                                  |     | <ol><li>Vertical blank output. In this mode the GPCL terminal is used to indicate<br/>the vertical blanking interval of the output video. The beginning and end<br/>times of this signal are programmable via the host port control.</li></ol>                                                                      |  |  |  |

|                  |                                  |     | <ol><li>Sync lock control input. In this mode when GPCL is high, the output clock<br/>frequencies and sync timing are forced to nominal values.</li></ol>                                                                                                                                                           |  |  |  |

| GLCO             | 31                               | I/O | This serial output carries color PLL information. A slave device can decode the information to allow genlocking to the TVP5020. Data is transmitted at the SCLK rate. Additionally, this terminal, in conjunction with PALI and FID, is used to determine the host port mode configuration during initial power up. |  |  |  |

| OEB              | 62                               | I   | Output enable for Y and UV terminals. Output enable is also controllable via the host port.                                                                                                                                                                                                                         |  |  |  |

| PLL_BYP          | 28                               |     | Connect a 0.1 $\mu$ F capacitor between this terminal and PLL_AVDD                                                                                                                                                                                                                                                  |  |  |  |

| RSTINB           | 23                               | Ι   | Reset input, active low                                                                                                                                                                                                                                                                                             |  |  |  |

| NC               | 1, 2, 13,<br>14, 15              |     | Not connected                                                                                                                                                                                                                                                                                                       |  |  |  |

| Power Supplie    | es                               |     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| AFE_GND          | 16                               |     | Analog ground                                                                                                                                                                                                                                                                                                       |  |  |  |

| AFE_VDD          | 18                               |     | Analog supply, connect to 5 V                                                                                                                                                                                                                                                                                       |  |  |  |

| CH1_AGND<br>AGND | 3<br>12                          |     | Analog grounds                                                                                                                                                                                                                                                                                                      |  |  |  |

| CH1_AVDD<br>AVDD | 6<br>9                           |     | Analog supply, connect to 5 V                                                                                                                                                                                                                                                                                       |  |  |  |

| DGND             | 21, 22, 24,<br>37, 47, 57,<br>68 |     | Digital grounds                                                                                                                                                                                                                                                                                                     |  |  |  |

| DTO_AGND         | 20                               |     | DTO ground, connect to analog ground                                                                                                                                                                                                                                                                                |  |  |  |

| DTO_AVDD         | 19                               |     | DTO supply, connect to 5 V analog                                                                                                                                                                                                                                                                                   |  |  |  |

| DVDD             | 34, 44, 54,<br>65, 75            |     | Digital supply, connect to 3.3 V                                                                                                                                                                                                                                                                                    |  |  |  |

| NSUB             | 17                               |     | Substrate ground, connect to analog ground                                                                                                                                                                                                                                                                          |  |  |  |

| PLL_AVDD         | 25                               |     | PLL supply connect to 3.3 V                                                                                                                                                                                                                                                                                         |  |  |  |

| REFP             | 8                                |     | A/D reference supply, connect to 5 V analog                                                                                                                                                                                                                                                                         |  |  |  |

| REFM             | 7                                |     | A/D reference ground, connect to analog ground                                                                                                                                                                                                                                                                      |  |  |  |

# **1.6 Terminal Functions (Continued)**

| TERMIN       | TERMINAL |     | DECODIDITIONS                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.     |          | 1/0 | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Sync Signals |          |     |                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

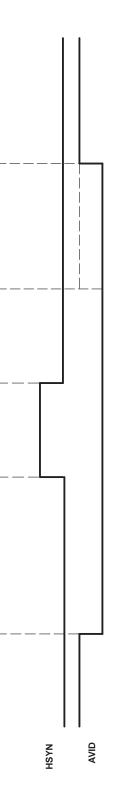

| AVID         | 27       | 0   | Active video indicator. This signal is high during the horizontal active time of the video output on the Y and UV terminals. AVID continues to toggle during vertical blanking intervals.                                                                                                                                                                                                                   |  |  |

| FID          | 33       | I/O | Odd/even field indicator or vertical lock indicator. For odd/even indicator, a logic 1 indicates the odd field. For vertical lock indicator, a logic 1 indicates the internal vertical PLL is in a locked state. Additionally, this terminal in conjunction with GLCO and PALI is used to determine the host port mode configuration during initial power up and reset.                                     |  |  |

| HSYN         | 30       | 0   | Horizontal sync signal. The rising edge time is programmable via the host.                                                                                                                                                                                                                                                                                                                                  |  |  |

| PALI         | 32       | I/O | PAL line indicator or horizontal lock indicator. For PAL line indicator, a logic 1 indicates a noninverted line, and a logic 0 indicates an inverted line. For horizontal lock indicator, a logic 1 indicates the internal horizontal PLL is in a locked state. Additionally, this terminal in conjunction with GLCO and FID is used to determine the host port mode configuration during initial power up. |  |  |

| VSYN         | 29       | 0   | Vertical sync signal                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

# **1.6 Terminal Functions (Continued)**

# 2 Detailed Description

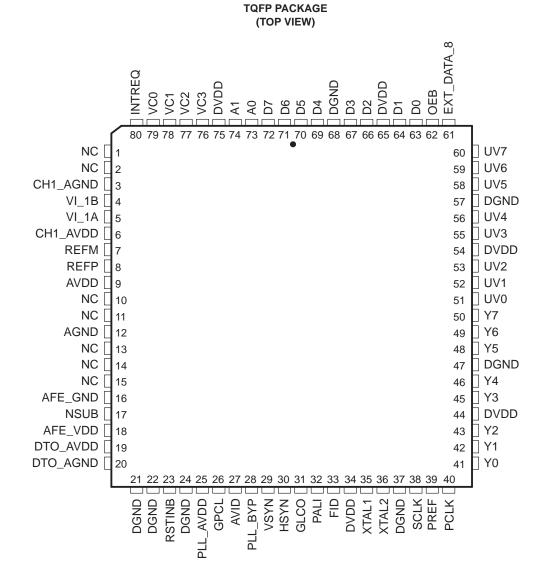

# 2.1 Analog Video Processors and A/D Converter

Figure 2–1 is a functional diagram of the TVP5020 analog video processors and A/D converter. This block accepts up to two inputs and performs analog signal conditioning (i.e., video clamping, video amplifying), and carries out analog-to-digital conversion.

#### 2.1.1 Video Input Selection

Two high-impedance video inputs are sources for a single internal analog channel in the TVP5020. The user can connect the two analog video inputs to two selectable individual composite video inputs.

# 2.1.2 Analog Input Clamping and Automatic Gain Control Circuits

The internal clamp circuit restores the ac-coupled video signals to a fixed dc level before A/D conversion. The clamping circuit provides line-by-line restoration of the video sync level to a fixed dc reference voltage. The circuit has two modes of clamping, coarse and fine. In coarse mode, the most negative portion of the signal (typically the sync tip) is clamped to a fixed dc level. The circuit uses fine mode to prevent spurious level shifting caused by noise that is more negative than the sync tip on the input signal. When fine mode is enabled, after the sync position is detected, clamping is only enabled during the sync period.

Input video signal amplitudes may vary significantly from the nominal level of 1 Vpp. An automatic gain control (AGC) circuit adjusts the signal amplitude to use the maximum range of the A/D converter without clipping.

The AGC circuit adjusts the signal amplitude based on the detected amplitude of the sync portion of the input signal. Signal peaks may be present on nonstandard signals that cause clipping at the A/D converter after gain adjustment based only on sync amplitude. In these cases, the signal will be attenuated before A/D conversion.

Figure 2–1. Analog Video Processors and A/D Converters

# 2.1.3 A/D Converter

The TVP5020 contains one 8-bit A/D converter which digitizes the selected analog video signal input. To prevent high frequencies which are above half of the sampling rate from entering into the system, video inputs may require external anti-aliasing low pass filters.

# 2.2 Digital Processing

Figure 2–2 is a block diagram of the TVP5020 digital video processing. This block receives digitized composite or signals from the A/D converter, and performs Y/C separation, chroma demodulation, and Y-signal enhancements. It also generates the horizontal and vertical syncs. The YUV digital output may be programmed into various formats: 16-bit or 8-bit 4:2:2, 12-bit 4:1:1 and ITU-R BT.656 parallel interface standard. The circuit uses comb filters to reduce the cross-chroma and cross-luma noise.

Figure 2–2. Digital Video Signal Processing Block Diagram

# 2.2.1 Y/C Separation

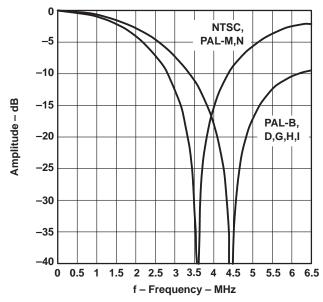

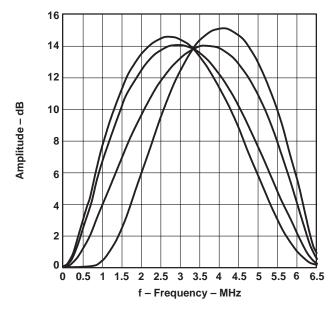

Luma/chroma separation may be done using either 2-line (1–H delay) comb filtering or a chroma trap filter. Comb filtering is available for both the luminance and the chrominance portion of the data path. The characteristics of the chroma trap filter are shown in Figures 2–3 and 2–4.

Figure 2–3. Chroma Trap Filter Frequency Response for 13.5 MHz Sampling

Figure 2–4. Chroma Trap Filter Frequency Response for Square-Pixel Sampling

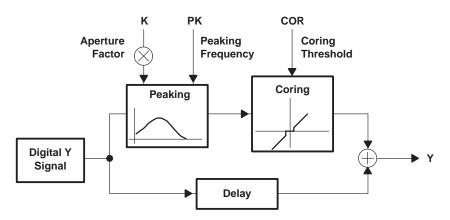

#### 2.2.2 Luminance Processing

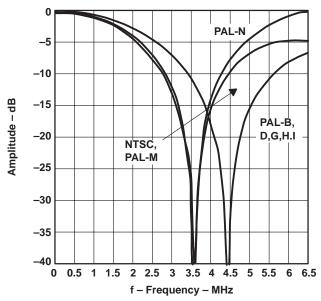

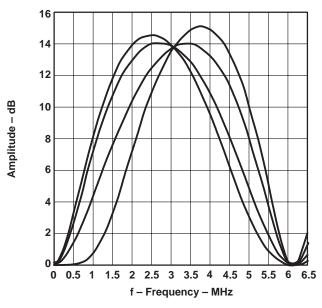

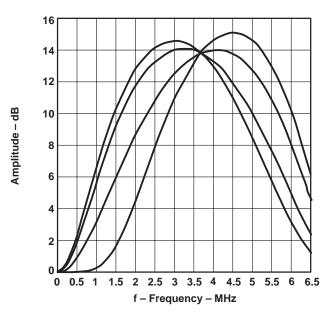

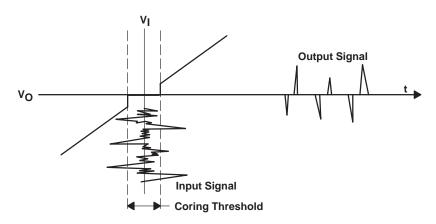

The digitized composite video signal from the output of the A/D converter passes through a luminance comb filter or a chroma trap filter that removes the chrominance signal from the composite signal to generate the luminance signal. The luminance signal is then fed to the input of luminance signal peaking and coring circuits. Figure 2–5 illustrates the functions of the luminance data path. High frequency components of the luminance signal are enhanced further by the peaking filter (edge enhancer). Figures 2–6, 2–7, and 2–8 show the characteristic of the peaking filter at maximum gain. The coring circuit reduces low-level, high

-frequency noise. Figure 2–9 shows the transfer curve of the coring function. The peaking frequency, peaking gain, and coring threshold are programmable.

Figure 2–5. Luminance Edge-Enhancer

Figure 2–6. Peaking Filter Response, 13.5 MHz Sampling

Figure 2–7. Peaking Filter Response, NTSC AND PAL-M SQUARE PIXEL

Figure 2–8. Peaking Filter Response, PAL Square Pixel

Figure 2–9. Transfer Curve of Coring Circuit

#### 2.2.3 Chrominance Processing

A quadrature demodulator removes the U and V components from the composite signal in composite video mode. The U/V signals then pass through the gain control stage for chroma saturation adjustment. The U and V components pass through a comb filter to eliminate cross-chrominance noise. Phase shifting the digitally-controlled oscillator controls hue. The block includes an automatic color killer (ACK) circuit that suppresses the chroma output when the color burst of the video signal is weak or not present.

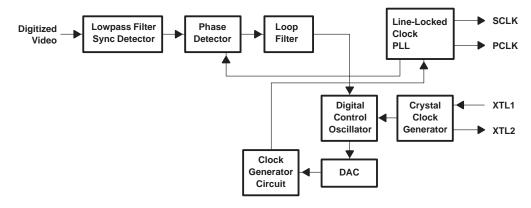

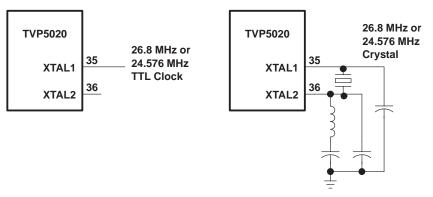

#### 2.2.4 Clock Circuits

An internal line-locked PLL generates the system and pixel clocks. Figure 2–10 shows a simplified clock circuit diagram. The digital control oscillator (DCO) generates the reference signal for the horizontal PLL. The DCO outputs a signal that is fed to the D/A converter. The D/A converter outputs a line-locked clock signal (LCLK). The DCO requires a 26.8 or a 24.576 MHz clock as an input. The input for the DCO may be connected to terminal XTAL1 or a 26.8 or 24.576 MHz crystal may be connected across terminals XTAL1 and XTAL2. Figure 2–11 shows the various reference clock configurations.

Figure 2–10. Clock Circuit Diagram

Figure 2–11. Reference Clock Configurations

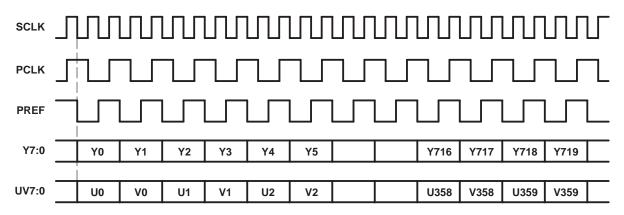

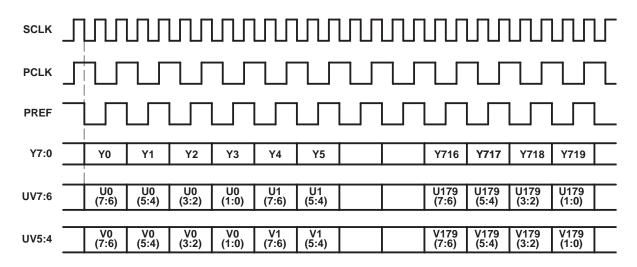

The TVP5020 generates three signals PCLK, SCLK, and PREF used for clocking data. PCLK is the pixel clock at the sampling frequency. PCLK can be used for clocking data in the 16-bit 4:2:2 and the 12-bit 4:1:1 output formats. SCLK is at twice the sampling frequency and may be used for clocking data in the 8-bit 4:2:2 and ITU-R BT.656 formats. PREF is used as a clock qualifier with SCLK to clock data in the 16-bit 4:2:2 and the 12-bit 4:1:1 formats

# 2.3 Video Output Format

The TVP5020 supports both square-pixel and ITU-R BT.601 sampling formats and multiple output formats:

- 16-bit 4:2:2

- 12-bit 4:1:1

- 8-bit 4:2:2

- ITU-R BT.656

#### 2.3.1 Sampling Frequencies and Patterns

The sampling frequencies that control the number of pixels per line differ depending on the video format and standards. Table 2–1 shows a summary of the sampling frequencies.

Table 2–1.

Summary of the Line Frequencies, Data Rates, and Pixel Counts

| STANDARDS                     | HORIZONTAL<br>LINE RATE<br>(kHz) | PIXELS<br>PER LINE | ACTIVE PIXELS<br>PER LINE | PCLK (MHz) | SCLK (MHz) |

|-------------------------------|----------------------------------|--------------------|---------------------------|------------|------------|

| NTSC, square-pixel            | 15.73426                         | 780                | 640                       | 12.2727    | 24.54      |

| NTSC, ITU-R BT.601            | 15.73426                         | 858                | 720                       | 13.5       | 27.0       |

| PAL (B,D,G,H,I), square-pixel | 15.625                           | 944                | 768                       | 14.75      | 29.5       |

| PAL (B,D,G,H,I), ITU-R BT.601 | 15.625                           | 864                | 720                       | 13.5       | 27.0       |

| PAL(M), square-pixel          | 15.73426                         | 780                | 640                       | 12.2727    | 24.54      |

| PAL(M), ITU-R BT.601          | 15.73426                         | 858                | 720                       | 13.5       | 27.0       |

| PAL(N), square-pixel          | 15.625                           | 944                | 768                       | 14.75      | 29.5       |

| PAL(N), ITU-R BT.601          | 15.625                           | 864                | 720                       | 13.5       | 27.0       |

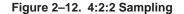

Depending on the output format chosen, The TVP5020 outputs data in the 4:2:2 or 4:1:1 sampling pattern. The patterns differ in the number of chrominance samples derived from the original samples. For the 4:2:2 pattern, every second sample is both a luminance and a chrominance sample; the remainder are luminance-only samples. For the 4:1:1 pattern, every fourth sample is both a luminance and a chrominance sample; the remainder are luminance-only samples.

= Luminance and Chrominance Sample

Numbering Shown is for 13.5 MHz Sampling.

= Luminance and Chrominance Sample

Numbering Shown is for 13.5 MHz Sampling.

Figure 2–13. 4:1:1 Sampling

2.3.2 Video Port 16-Bit 4:2:2 Output Format Timing

Numbering Shown is for 13.5 MHz Sampling.

Figure 2–14. 16-Bit 4:2:2 Output Format

#### 2.3.3 Video Port 12-Bit 4:1:1 Output Format Timing

UV3:0 Logic 0 Numbering Shown is for 13.5 MHz Sampling.

#### Figure 2–15. 12-bit 4:1:1 Output Format

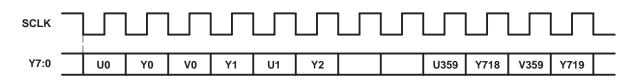

#### 2.3.4 Video Port 8-Bit 4:2:2 and ITU-R BT.656 Output Format Timing

UV7:0 High Impedance

Numbering Shown is for 13.5 MHz Sampling.

Figure 2–16. 8-Bit 4:2:2 and ITU-R BT.656 Output Formats

#### 2.4 Synchronization Signals

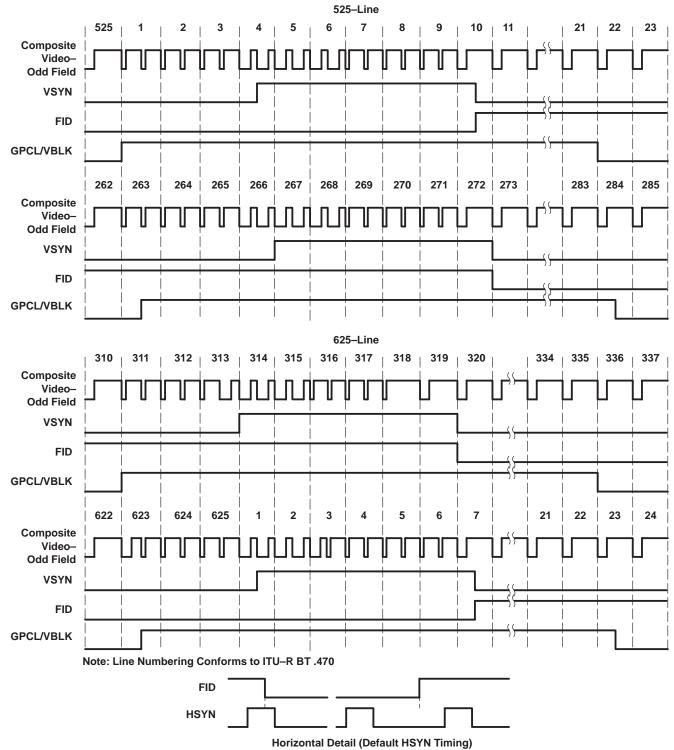

The TVP5020 generates synchronization signals to accompany the output video data stream. The following figures show the default timing for the horizontal and vertical sync and associated signals.

Figure 2–17. Vertical Synchronization Signals

2–10

| Reference       |

|-----------------|

| (SCLK)          |

| Clock           |

| <b>2x Pixel</b> |

| With 3          |

| Timing          |

| -Bit 4:2:2      |

| ò               |

Ľ

I

|                          | _       |                              | _        |                       | _        |                              |

|--------------------------|---------|------------------------------|----------|-----------------------|----------|------------------------------|

| 3                        | 3       | ≻-                           | °        | ≻-                    | e        | ≻-                           |

| 2                        | 2       | ບົວ                          | 2        | సం                    | 2        | ບົວ                          |

| 1                        | 1       | 0<br>人                       | 1        | ۲ 0                   | 1        | 0<br>人                       |

| 0                        | 0       | o Cp                         | 0        | o Cb                  | 0        | e c                          |

| 1715                     | 1727    | хх                           | 1559     | хх                    | 1887     | xx                           |

| 1714                     | 1726    | 00                           | 1558     | 00                    | 1886     | 00                           |

| 1713                     | 1725    | 00                           | 1557     | 00                    | 1885     | 00                           |

| 1711 1712 1713 1714 1715 | 1724    | FF                           | 1556     | FF                    | 1884     | ΕF                           |

| 1711                     | 1723    | 10                           | <br>1555 | 10                    | <br>1883 | 10                           |

|                          | :       | :                            | :        | :                     | :        | :                            |

| 1560                     | 1592    | 80                           | 1452     | 80                    | 1716     | 80                           |

| 1599                     | 1591    | 10                           | <br>1451 | 10                    | <br>1715 | 10                           |

|                          | :       | :                            | :        | :                     | :        | :                            |

| 1471 1472                | 1464    | 80                           | 1324     | 80                    | 1588     | 80                           |

| 1471                     | 1463    | 10                           | <br>1323 | 10                    | <br>1587 | 10                           |

|                          | :       | :                            | :        | :                     | :        | :                            |

| 1441                     | 1441    | 00                           | 1281     | 00                    | 1537     | 00                           |

| 439 1440                 | 1440    | FF                           | 1280     | ΕF                    | 1536     | ЧЧ                           |

| 1439                     | 1439    | Υ<br>719                     | 1279     | Υ<br>639              | 1535     | ۲67                          |

| 1438                     | 1438    | Cr<br>359                    | 1278     | Cr<br>319             | 1534     | 383<br>383                   |

| 1437                     | 1437    | Υ<br>718                     | 1277     | Υ<br>638              | 1533     | ۲<br>766                     |

| 1436 1437                | 1436    | Cb<br>359                    | 1276     | Cb<br>319             | 1532     | 383<br>383<br>383            |

| <b>NTSC 601</b>          | PAL 601 | ITU 656 Cb<br>Datastream 359 | NTSC sqp | ITU 656<br>Datastream | PAL sqp  | ITU 656 Cb<br>Datastream 383 |

|                          |         |                              |          |                       |          |                              |

# 16-Bit 4:2:2 Timing With 1x Pixel Clock (PCLK) Reference

| 1               | 1       | 1        | 1       |      |      |      |  |

|-----------------|---------|----------|---------|------|------|------|--|

| 0               | 0       | 0        | 0       |      |      |      |  |

| 857             | 863     | 779      | 943     | <br> |      |      |  |

| 856             | 862     | 778      | 942     |      |      |      |  |

| 855             | 861     | 777      | 941     |      |      |      |  |

| :               | :       | :        | :       |      |      |      |  |

| 800             | 796     | 726      | 858     |      |      |      |  |

| 799             | 795     | 725      | 857     | <br> |      |      |  |

| :               | :       | :        | :       |      |      |      |  |

| 736             | 732     | 662      | 794     |      |      |      |  |

| 735             | 731     | 661      | 793     |      |      |      |  |

|                 | :       |          |         |      |      |      |  |

| 720             | 720     | 640      | 768     |      |      |      |  |

| 719             | 719     | 639      | 767     |      |      |      |  |

| 718             | 718     | 638      | 766     |      |      |      |  |

| <b>NTSC 601</b> | PAL 601 | NTSC sqp | PAL sqp |      | ΝλSΗ | AVID |  |

Figure 2–18. Horizontal Synchronization Signals

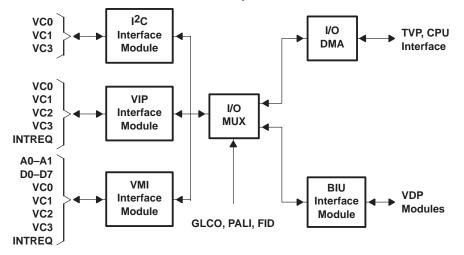

# 2.5 I<sup>2</sup>C/VIP/VMI Host Interface

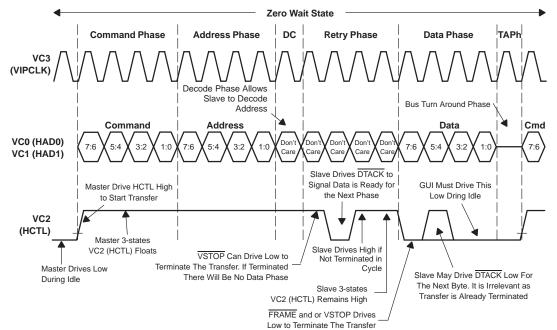

Communication with the TVP5020 is via an interface that is configurable at power up to support an I<sup>2</sup>C, VIP, or VMI bus host. The host interface accesses status and control registers and retrieves sliced VBI data. The host interface also initializes the TVP5020's internal microprocessor.

Figure 2–19. Host Interface

The host port mode is selected by attaching external pullup and pulldown resistors to the GLCO, PALI, and FID terminals. The TVP5020 samples the state of the terminals at trailing edge of RSTINB and configures the host port accordingly. Table 2–2 shows the pullup/pulldown combinations required to select each of the host port modes. Figure 2–19 is a block diagram of the host interface showing the mode selection and host interface terminals, as well as interfaces to the internal microprocessor and VBI data processor.

| TERMINALS                  | GLCO | PALI | FID |  |  |  |  |  |  |

|----------------------------|------|------|-----|--|--|--|--|--|--|

| TERMINALS                  | 2    | 1    | 0   |  |  |  |  |  |  |

| I <sup>2</sup> C Host Port | 0    | 0    | 1   |  |  |  |  |  |  |

| VIP Host Port              | 0    | 1    | 0   |  |  |  |  |  |  |

| VMI Host Port Mode A       | 1    | 0    | 1   |  |  |  |  |  |  |

| VMI Host Port Mode B       | 1    | 1    | 0   |  |  |  |  |  |  |

| VMI Host Port Mode C       | 1    | 1    | 1   |  |  |  |  |  |  |

| Table | 2–2. | Host  | Port | Select |

|-------|------|-------|------|--------|

| Iable | _    | 11000 |      | 001001 |

### 2.6 I<sup>2</sup>C Interface

The TVP5020 host port interface is configured for  $I^{2}C$  operation by attaching external pull-up and pull-down resisters to the GLCO, PALI, and FID terminals. The following is the combination of resisters required to select the  $I^{2}C$  host mode. (1 is pullup and 0 is pulldown)

| TERMINALS                          | GLCO | PALI | FID |

|------------------------------------|------|------|-----|

|                                    | 2    | 1    | 0   |

| I <sup>2</sup> C Host Port Enabled | 0    | 0    | 1   |

### 2.6.1 I<sup>2</sup>C Host Port Select

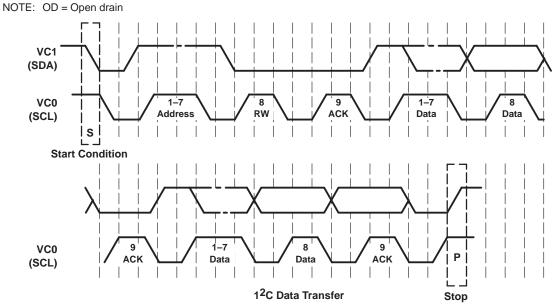

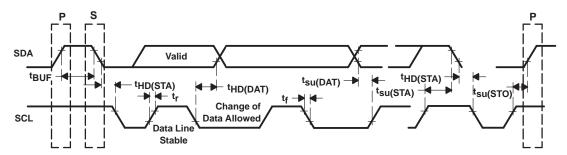

The I<sup>2</sup>C standard consists of two signals, serial input/output data (VC1) line and input/output clock line (VC0), that carry information between the devices connected to the bus. A third signal (VC3) is used for slave address selection. Although the I<sup>2</sup>C system can be multimastered, the TVP5020 will function as a slave device only.

Both SDA and SCL are bidirectional lines that connect to a positive supply voltage via a pullup resistor. When the bus is free, both lines are high.

The slave address select terminal (VC3) enables the use of two TVP5020 devices tied to the same I<sup>2</sup>C bus.

Table 2–3 summarizes the terminal functions of the I<sup>2</sup>C mode host interface.

| SIGNAL     | TYPE              | DESCRIPTION             |

|------------|-------------------|-------------------------|

| VC3 (I2CA) | I                 | Slave address selection |

| VC0 (SCL)  | I/O ( <b>OD</b> ) | Input/output clock line |

| VC1 (SDA)  | I/O ( <b>OD</b> ) | Input/output data line  |

Table 2–3. I<sup>2</sup>C Host Port Terminal Description

Figure 2–20. I<sup>2</sup>C Data Transfer Example

Data transfer rate on the bus is up to 400 kbits/s. The number of interfaces connected to the bus is dependent on the bus capacitance limit of 400 pF. The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change with the clock signal on the SCL line being low.

- When transferring multiple bytes during one read or write operation, the internal subaddress is not automatically incremented.

- A high to low transition on the SDA line while the SCL is high indicates a start condition.

- A low to high transition on the SDA line while the SCL is high indicates a stop condition

- Acknowledge is signalled by SDA low during the ninth SCL high.

- Not-acknowledge is signalled by SDA high during the ninth SCL high.

Every byte placed on the SDA line must be 8 bits long. The number of bytes that can be transferred is unrestricted. An acknowledge bit follows each byte. If the slave can not receive another complete byte of data until it has performed another function, it holds the clock line (SCL) low. An SCL low forces the master

into a wait state. Data transfer continues when the slave is ready for another byte of data and releases the clock line (SCL).

Data transfer with acknowledge is necessary. The master generates an acknowledge related clock pulse. The master releases the SDA line high during the acknowledge clock pulse. The slave pulls down the SDA line during the acknowledge clock pulse so that it remains stable low during the high period of this clock pulse.

When a slave does not acknowledge the slave address, the data line is left high. The master then generates a stop condition to abort the transfer.

If a slave acknowledges the slave address, but some time later in the transfer cannot receive any more data bytes, the master again aborts the transfer. The slave indicates a not ready condition by generating the not acknowledge. The slave leaves the data line high and the master generates the stop condition.

If a master-receiver is involved in a transfer, it indicates the end of data to the slave-transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line to allow the master to generate a stop or repeated start condition.

#### 2.6.2 I<sup>2</sup>C Write Operation

Data transfers occur using the following illustrated formats.

The I<sup>2</sup>C master initiates a write operation to the TVP5020 by generating a start condition followed by the TVP5020's I<sup>2</sup>C address (101110X). The address is in MSB first bit order followed by a 0 to indicate a write cycle. After receiving a TVP5020 acknowledge, the I<sup>2</sup>C master sends a subaddress of the register or the block of registers where it will write. Following the subaddress is one or more bytes of data, with MSB first. The TVP5020 acknowledges the receipt of each byte upon completion of each transfer. The I<sup>2</sup>C master ends a write operation by generating a stop condition.

The X in the address of the TVP5020 is 0 when the  $I^2CA$  terminal is low and the X is 1 when the  $I^2CA$  is high. If the read or write cycle contains more than one byte, the internal subaddress does not increment automatically.

|                                                  | 0    | 1    |      |      |      |      |      |      |

|--------------------------------------------------|------|------|------|------|------|------|------|------|

|                                                  |      | {    |      |      |      |      |      |      |

| I <sup>2</sup> C Start (Master)                  | S    | l    |      |      |      |      |      |      |

|                                                  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General address (Master)        | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

|                                                  | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)             | A    | ]    |      |      |      |      |      |      |

|                                                  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write register address (Master) | Addr |

|                                                  | 9    | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)             | А    | ]    |      |      |      |      |      |      |

|                                                  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write data (Master)             | Data |

|                                                  | 9    | 1    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (Slave)             | А    | ]    |      |      |      |      |      |      |

|                                                  | 0    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (Master)                   | Р    | 1    |      |      |      |      |      |      |

#### 2.6.3 I<sup>2</sup>C Read Operation