# TVP6000C Data Manual

## NTSC/PAL Digital Video Encoder

SLAS184 July 1998

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

## **Contents**

| Sect | tion                                     | Title                                                                                                                                                                                                                                                                                                                     | Page                                                                 |

|------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|      | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Applications Functional Block Diagram                                                                                                                                                                                                                                                                                     | 1–1<br>1–2<br>1–2<br>1–3<br>1–4                                      |

| 4    | <b>Deta</b> 2.1 2.2 2.3 2.4 2.5          | Illitialization Initialization IPC Interface Data Manager Scaling Processor Video Encoder 2.5.1 Luminance Encoding 2.5.2 Luminance Low-Pass and Interpolation Filter 2.5.3 Cross Color Reduction Filter 2.5.4 Chrominance Encoding                                                                                        | 2-1<br>2-3<br>2-4<br>2-5<br>2-6<br>2-6<br>2-6<br>2-8                 |

| 4    | 2.6<br>2.7<br>2.8<br>2.9                 | 2.5.4       Chroninance Encoding         Closed Caption       2         Clock Generation       2         Analog Output       2         Video Port Interface       2         2.9.1       RCV1         2.9.2       RCV2         2.9.3       RCM1         2.9.4       RCM2                                                   | 2–9<br>2–11<br>2–11<br>2–12<br>2–12<br>2–12<br>2–12                  |

| 2    | 2.10                                     | Modes of Operation       2         2.10.1 Master Mode       2         2.10.2 Slave Mode       2         2.10.3 Demand Mode       2         2.10.4 Genlock Mode       2                                                                                                                                                    | 2–13<br>2–13<br>2–13<br>2–14                                         |

| 2    | 2.11                                     | Register Descriptions       2         2.11.1 DEV_ID       2         2.11.2 REV_ID       2         2.11.3 STATUS       2         2.11.4 F_CONTROL       2         2.11.5 C_PHASE       2         2.11.6 GAIN_U       2         2.11.7 GAIN_V       2         2.11.8 BLACK_LEVEL       2         2.11.9 BLANK LEVEL       2 | 2-15<br>2-17<br>2-17<br>2-17<br>2-18<br>2-19<br>2-19<br>2-19<br>2-19 |

# **Contents (Continued)**

| Section |         | Title             | Page |

|---------|---------|-------------------|------|

|         | 2.11.10 | GAIN_Y            | 2–20 |

|         | 2.11.11 | X_COLOR           |      |

|         | 2.11.12 | M_CONTROL         | 2-21 |

|         | 2.11.13 | BSTAMP            | 2-21 |

|         | 2.11.14 | S_CARR1, 2, 3, 4  | 2-22 |

|         | 2.11.15 | LINE21_00         | 2-23 |

|         | 2.11.16 | LINE21_O1         | 2-23 |

|         | 2.11.17 | LINE21_E0         | 2-23 |

|         | 2.11.18 | LINE21_E1         | 2-23 |

|         | 2.11.19 | LN_SEL            | 2-23 |

|         | 2.11.20 | SYN_CTRL0         | 2-24 |

|         | 2.11.21 | RCM_L21           | 2-26 |

|         | 2.11.22 | HTRIGGER0         | 2-28 |

|         | 2.11.23 | HTRIGGER1         | 2-28 |

|         | 2.11.24 | VTRIGGER          | 2-28 |

|         | 2.11.25 | BMRQ              | 2-29 |

|         | 2.11.26 | EMRQ              | 2-29 |

|         | 2.11.27 | BEMRQ             | 2-29 |

|         | 2.11.28 | BRCV              | 2-29 |

|         | 2.11.29 | ERCV              | 2-30 |

|         | 2.11.30 | BERCV             | 2-30 |

|         | 2.11.31 | FLEN              | 2-30 |

|         | 2.11.32 | FAL               | 2-30 |

|         | 2.11.33 | LAL               | 2-31 |

|         | 2.11.34 | FLAL              | 2-31 |

|         | 2.11.35 | SYN_CTRL1         | 2-31 |

|         | 2.11.36 | SCM               | 2-32 |

|         | 2.11.37 | SLPF              | 2-32 |

|         | 2.11.38 | SPPL              | 2-33 |

|         | 2.11.39 | SLPH              | 2-33 |

|         | 2.11.40 | DLPF              | 2-33 |

|         | 2.11.41 | DPPL              | 2-33 |

|         | 2.11.42 | DLPH              | 2-34 |

|         | 2.11.43 | VDTAL             | 2-34 |

|         | 2.11.44 | VDTAH             | 2-34 |

|         | 2.11.45 | HDTAL             | 2-34 |

|         | 2.11.46 | HDTAH             | 2-35 |

|         | 2.11.47 |                   |      |

|         | 2.11.48 | HOFS              |      |

|         | 2.11.49 | NLR               | 2-35 |

|         | 2 11 50 | TEST1 TEST2 TEST3 | 2-35 |

# **Contents (Continued)**

| Section                                      | Title                                                                                                                                                                                                                                                                                                                                                                | Page                                   |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3 Electric 3.1 3.2 3.3 3.4 3.5 3.6 3.7       | Absolute Maximum Ratings Over Operating Free-Air Temperature Range Recommended Operating Conditions DC Electrical Characteristics, T <sub>A</sub> = 25°C, DV <sub>DD</sub> = AV <sub>DD</sub> = 5 V AC Electrical Characteristics, T <sub>A</sub> = 25°C, DV <sub>DD</sub> = AV <sub>DD</sub> = 5 V Timing Requirements Demand Mode Timing Switching Characteristics | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-2 |

| A Exa                                        | mple Register Settings                                                                                                                                                                                                                                                                                                                                               | A-1                                    |

| B Mec                                        | hanical Data                                                                                                                                                                                                                                                                                                                                                         | B-1                                    |

| Figure                                       | List of Illustrations  Title  minal Assignments                                                                                                                                                                                                                                                                                                                      | Page                                   |

| 2–1 Blo<br>2–2 I <sup>2</sup> C              | ck Diagram                                                                                                                                                                                                                                                                                                                                                           | . 2–2<br>. 2–3                         |

| 2–4 I <sup>2</sup> C<br>2–5 I <sup>2</sup> C | Access Cycles Write Cycle Read Cycle na Path Frequency Response                                                                                                                                                                                                                                                                                                      | . 2–4<br>. 2–4                         |

| 2–7 Lur<br>2–8 Chi<br>2–9 NT                 | na Cross Color Reduction Filter                                                                                                                                                                                                                                                                                                                                      | . 2–7<br>. 2–9<br>2–10                 |

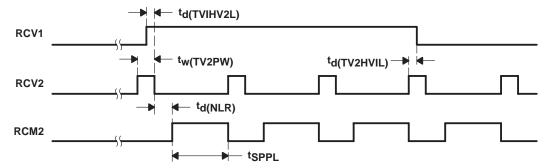

| 2–11 N7<br>2–12 PA<br>2–13 O                 | TSC Square Pixel Rate Closed Caption Line  AL Square Pixel Rate Closed Caption Line  utput Filter  ansmission Timing                                                                                                                                                                                                                                                 | 2–11<br>2–11<br>2–12                   |

| 3–1 Dat                                      | ta Setup and Hold Timing                                                                                                                                                                                                                                                                                                                                             | . 3–3                                  |

# **List of Tables**

| Table                                 | Title      | Page |

|---------------------------------------|------------|------|

| 2-1 16-Bit Video Port YUV 4:2:2       |            | 2–5  |

| 2-2 8-Bit Multiplexed Video Port CC   |            |      |

| 2-3 100/100 Color Bar in Twos Com     | plement    | 2–5  |

| 2–4 Master Mode                       | ·          | 2–13 |

| 2-5 Crystal Frequencies               |            | 2–13 |

| 2-6 Slave Mode Signals                |            | 2–14 |

| 2–7 Base Addresses                    |            |      |

| 2–8 Register Bit Allocation Map       |            |      |

| 2-9 Input Format and Data Sampling    | g          | 2–18 |

| 2-10 Chroma Channel Delays            |            | 2–20 |

| 2-11 Total Horizontal Pixel Selection |            |      |

| 2-12 S_CARR Values                    |            | 2–22 |

| 2–13 RCV1 Pin Configurations          |            | 2–25 |

| 2-14 RCV1 Symbols and Signal Des      | scriptions | 2–25 |

| 2–15 RCV2 Pin Configurations          |            | 2–25 |

| 2–16 RCV2 Symbols and Signal Des      |            |      |

| 2-17 RCM1 Output Signals              |            | 2–27 |

| 2–18 RCM2 Pin Configurations          |            |      |

| 2–19 Encoding Setting                 |            | 2–27 |

| 2–20 Phase Reset Modes                |            | 2–28 |

| 2–21 Active Video Modes               |            |      |

#### 1 Introduction

The TVP6000 is a digital video encoder designed for multimedia systems requiring high-quality flicker free display of computer graphics, video, and internet content.

The TVP6000 provides advanced horizontal and vertical scaling for overscan compensation. It features a 3 tap antiflicker filter. The encoder has different filters in the luma and the chroma channels. Additionally, the output is interpolated to twice the pixel frequency. All of these features combine to produce a high-quality display of non-interlaced data on a traditional interlaced TV.

The TVP6000 converts Y Cb Cr video data to base-band analog video output. The input can come from a video decoder (such as the TI TVP5010/TVP5020), a 3D graphics controller (such as the TI 4020), or a MPEG decoding device. Simultaneous composite and S-video (Y, C separated) provides high-quality video output.

#### 1.1 Features

- Digital Input Formats:

- YUV 4:2:2 on a 16-Bit Port

- CCIR-656 YUV 4:2:2 on an 8-Bit Port

- YUV 4:2:2 on an 8-Bit Port

- CCIR601 or Square Pixel Operation

- Analog Output Formats:

- NTSC-M

- PAL-B,D,G,H,I

- PAL-M

- PAL-N

- PAL-Nc

- Simultaneous S-Video and CVBS (Composite Baseband Video) Output

- 2x Over-Sampling

- 3-Tap Antiflicker Filter

- Triple 10-Bit DACs

- Overscan Compensation

- Programmable Video Port Interface

- Supports Master, Slave, CCIR656 and Demand Mode Video Port Interface

- Programmable Blank Level, Black Level, and Color Burst Amplitude

- Programmable Luminance and Chrominance Gains

- Programmable Subcarrier Frequency

- Programmable SCH

- Subcarrier Genlock Capability

- Programmable Luminance Delay

- I<sup>2</sup>C Serial Interface

- On Chip Color Bar Generation

- Closed Caption Support

- Software Detection of TV Connection

- On Chip Voltage Reference

- Cross Color Reduction Filter

- Power Down Mode

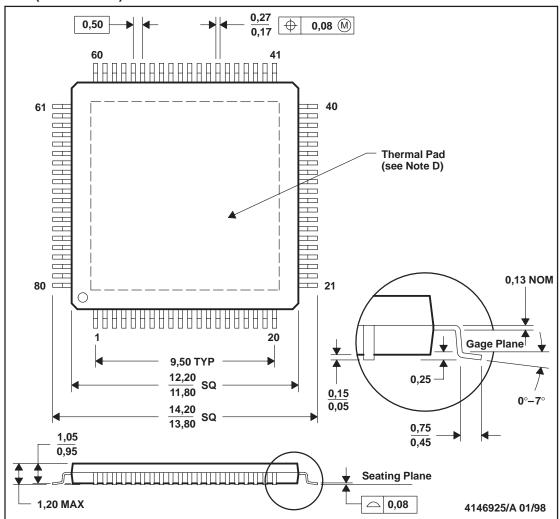

- 80-pin TQFP Package

- 5-V Operation

- Supports PC98 Hardware Design Specification

- SMPTE 170M NTSC Composite Video Specification Compliant

- CCIR624/CCIR601 PAL Composite Video Specification Compliant

## 1.2 Applications

- Digital Entertainment/ Set Top Box

- Internet PC

- Internet Appliance

- PC-to-TV Appliance

- Digital Video Disk (DVD)

- Digital Video Camera

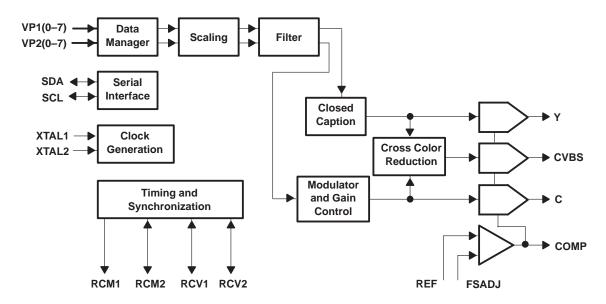

## 1.3 Functional Block Diagram

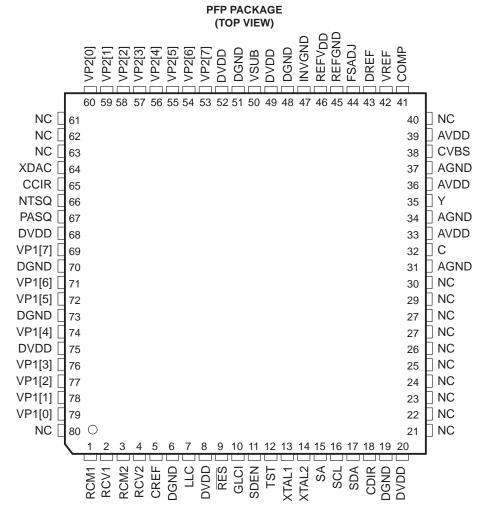

## 1.4 Terminal Assignments

Figure 1-1. Terminal Assignments

## 1.5 Ordering Information

Device TVP6000CPFP

PFP: Plastic Flat Pack With Power Pad

## 1.6 Terminal Functions

| TERMINAL |                       |     | DESCRIPTION                                                                                                                                                                                                              |  |  |  |

|----------|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.                   | 1/0 | DESCRIPTION                                                                                                                                                                                                              |  |  |  |

| AGND     | 31,34,37              |     | Analog ground                                                                                                                                                                                                            |  |  |  |

| AVDD     | 33,36,39              |     | Analog power supply                                                                                                                                                                                                      |  |  |  |

| С        | 32                    | 0   | Chrominance analog output signal for S-video output                                                                                                                                                                      |  |  |  |

| CCIR     | 65                    | 0   | External clock source select. CCIR can be programmed to select different external clock sources. When CCIR = 1, the encoder is set to CCIR601 mode. For detailed programming information, refer to Table 2–11.           |  |  |  |

| CDIR     | 18                    | ı   | Clock direction input. When CDIR = 0, LLC and CREF are outputs. When CDIR = 1, LLC and CREF are inputs.                                                                                                                  |  |  |  |

| COMP     | 41                    | I/O | Compensation pin for the internal reference amplifier. A 0.1- $\mu F$ capacitor should be connected between COMP and AVDD.                                                                                               |  |  |  |

| CREF     | 5                     | I/O | Clock reference signal                                                                                                                                                                                                   |  |  |  |

| CVBS     | 38                    | 0   | Composite video output signal                                                                                                                                                                                            |  |  |  |

| DGND     | 6,19,48,<br>51,70,73  |     | Digital ground                                                                                                                                                                                                           |  |  |  |

| DREF     | 43                    | I/O | Test pin. For normal applications no connect.                                                                                                                                                                            |  |  |  |

| DVDD     | 8,20,49,<br>52,68,75  |     | Digital power supply                                                                                                                                                                                                     |  |  |  |

| FSADJ    | 44                    | I/O | Full scale adjust control. A 264- $\Omega$ resistor should be connected between FSADJ and AGND to control the full-scale output current on the analog outputs.                                                           |  |  |  |

| GLCI     | 10                    | -1  | Genlock control input. GLCI is used for communicating with TVP5xxx decoder series.                                                                                                                                       |  |  |  |

| INVGND   | 47                    |     | INVGND should be connected to AGND for normal applications.                                                                                                                                                              |  |  |  |

| LLC      | 7                     | I/O | Line locked clock. One of the 24.54 MHz, 27.00 MHz, or 29.5 MHz clocks for different standards and pixel rates.                                                                                                          |  |  |  |

| NC       | 21–30,40,<br>61–63,80 |     | No connect                                                                                                                                                                                                               |  |  |  |

| NTSQ     | 66                    | 0   | External clock source select. NTSQ can be programmed to select different external clock sources. When NTSQ = 1, the encoder is set to NTSC square pixel mode. For detailed programming information, refer to Table 2–11. |  |  |  |

| PASQ     | 67                    | 0   | External clock source select. PASQ can be programmed to select different external clock sources. When PASQ = 1, the encoder is set to PAL square pixel mode. For detailed programming information, refer to Table 2–11.  |  |  |  |

## 1.6 Terminal Functions (Continued)

| TERMINAL           |                       | 1/0 | DESCRIPTION                                                                                                                                                                                                         |  |  |  |  |

|--------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME               | E NO.                 |     |                                                                                                                                                                                                                     |  |  |  |  |

| RCM1               | 1                     | 0   | Programmable video vertical timing signal. For detailed programming information see the RCM_L21 register definition.                                                                                                |  |  |  |  |

| RCM2               | 3                     | I/O | Programmable video horizontal timing signal (can also be programmed for horizontal active video signal. For detailed programming information, see RCM_L21 register definition.                                      |  |  |  |  |

| RCV1               | 2                     | I/O | Programmable video vertical timing signal. For programming infromation, se SYN_CTRL0 register definition.                                                                                                           |  |  |  |  |

| RCV2               | 4                     | I/O | Programmable video horizontal timing signal (can also be programmed for horizontal active video signal). For detailed programming infromation, see SYN_CTRL0 register definition.                                   |  |  |  |  |

| VREF               | 42                    | I/O | Test pin. VREF can be used for bandgap voltage output. For normal operation no connection.                                                                                                                          |  |  |  |  |

| REFGND             | 45                    |     | Reference ground of output DACs. REFGND should be connected to AGND.                                                                                                                                                |  |  |  |  |

| REFV <sub>DD</sub> | 46                    |     | Reference power supply of the DACs. REFV <sub>DD</sub> should be connected to AV <sub>DD</sub> .                                                                                                                    |  |  |  |  |

| RES                | 9                     | I   | Reset input, active low                                                                                                                                                                                             |  |  |  |  |

| SA                 | 15                    | I   | I <sup>2</sup> C slave address select                                                                                                                                                                               |  |  |  |  |

| SCL                | 16                    | I/O | I <sup>2</sup> C serial clock input. Maximum clock rate of 400 kHz.                                                                                                                                                 |  |  |  |  |

| SDA                | 17                    | I/O | I <sup>2</sup> C serial data line                                                                                                                                                                                   |  |  |  |  |

| SDEN               | 11                    | I   | Test pin. For normal applications connect to DGND.                                                                                                                                                                  |  |  |  |  |

| TST                | 12                    | I   | Test pin. For normal applications connect to DGND.                                                                                                                                                                  |  |  |  |  |

| VP1[7:0]           | 69,71,72,<br>74,76–79 | I   | Y input port in 16-bit mode. For 8-bit multiplexed mode, VP1[7:0] is either the YUV multiplexed port or should be left unconnected based on the FMT(2) register bit.                                                |  |  |  |  |

| VP2[7:0]           | 53–60                 | ı   | UV input port in 16-bit mode. For 8-bit multiplexed mode, VP2[7:0] is either the YUV multiplexed port or should be left unconnected based on the FMT(2) register bit.                                               |  |  |  |  |

| VSUB               | 50                    |     | VSUB should be connected to AGND.                                                                                                                                                                                   |  |  |  |  |

| XDAC               | 64                    | I   | XDAC sets the initial mode of operation for the output DACs immediately after reset. If XDAC = GND the DACs will be in normal operation mode after reset. If XDAC = $V_{DD}$ , the DACs will be in power down mode. |  |  |  |  |

| XTAL1              | 13                    | I   | Crystal or oscillator input. CMOS input levels                                                                                                                                                                      |  |  |  |  |

| XTAL2              | 14                    | I   | Crystal input. Crystal is connected between XTAL1 and XTAL2.                                                                                                                                                        |  |  |  |  |

| Υ                  | 35                    | 0   | Luminance analog output signal for S-video output                                                                                                                                                                   |  |  |  |  |

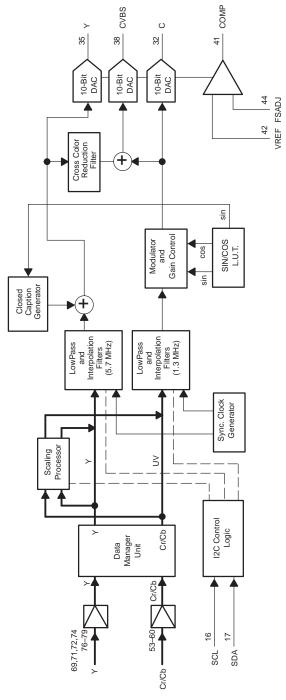

## 2 Detailed Description

The TVP6000 is a digital video encoder designed for systems requiring high-quality display of computer graphics, video, video conferencing, and Internet content. It is designed to convert a digital video input data stream into NTSC or PAL composite video output. Digital input formats include 8 or 16 bit YUV 4:2:2 or 8 bit CCIR–656 YUV. Analog output formats are NTSC and PAL.

The encoder provides picture quality enhancement features such as overscan compensation, which allows up to a 12.5% down scaling of pixels (horizontal) and lines (vertical) to allow fitting a VGA frame on a NTSC. A 3-tap antiflicker filter greatly reduces annoying flicker associated with displaying progressive scan graphics data or text on an interlace display, like TV. The output has simultaneous S-video and composite baseband video (CVBS) via three 10-bit DACs. Programmable features such as blank levels, color burst amplitude, luminance and chrominance gains, subcarrier frequency, luminance delay allow for easy optimization of picture quality and subcarrier genlock capability when used with a compatible video decoder provides accurate color reproduction even with nonstandard or unstable video sources such as a VCR.

See Figure 2–1 for an overview of the major functional blocks of the TVP6000.

#### 2.1 Initialization

Upon power up, the TVP6000 is initialized by the internal logic to display a color bar. With this feature, the TVP6000 is able to demonstrate basic functionality while using only a 27-MHz clock signal at the LLC pin or the XTAL1 and XTAL2 crystal pins. No software programming is required for this initial operation. This serves as a quick diagnostic tool during the initial debug of a system.

The DACs can also be optionally turned off immediately after reset by connecting the XDAC pin (pin 64) to  $V_{DD}$  if the initial color bar display is not desired. In this case, video is not output after reset. See Section 2.11, *Register Descriptions* for details about the default values immediately after power up.

Figure 2-1. Block Diagram

#### 2.2 I<sup>2</sup>C Interface

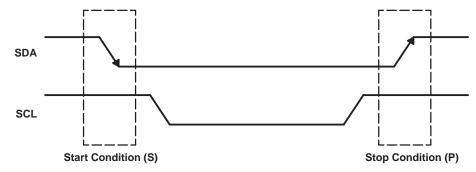

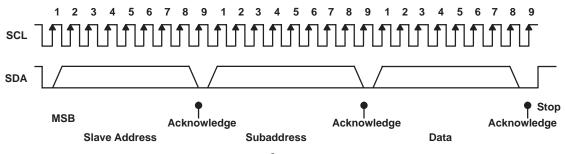

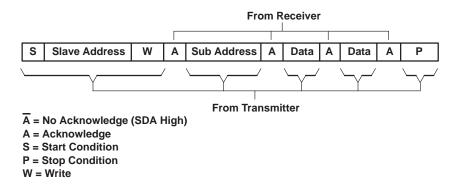

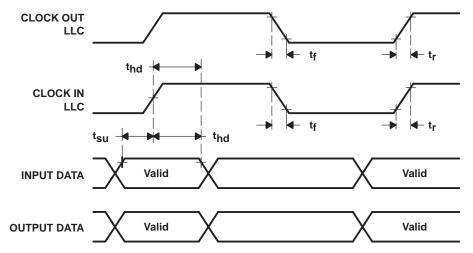

The I<sup>2</sup>C interface is used to access the internal registers of the TVP6000 encoder. This two pin interface consists of one clock line, SCL, and one serial data line, SDA. The basic I<sup>2</sup>C access cycles are shown in Figure 2–3.

Figure 2-2. I<sup>2</sup>C Start and Stop Conditions

The basic access cycle consists of the following:

- 1. A start condition

- 2. A slave address cycle

- 3. A subaddress cycle

- 4. Any number of data cycles

- 5. A stop condition

The start and stop conditions are shown in Figure 2–2. The high-to-low transition of SDA while SCL is high, defines the start condition. The low-to-high transition of SDA while SCL is high, defines the stop condition. Each cycle, data or address, consists of 8 bits of serial data followed by one acknowledge bit generated by the receiving device. Thus, each data/address cycle contains nine bits as shown in Figure 2–3.

Figure 2–3. I<sup>2</sup>C Access Cycles

As indicated in Figure 2–3, following a start condition, each  $I^2C$  device decodes the slave address. The TVP6000 responds with an acknowledge by pulling the SDA line low during the ninth clock cycle, if it decodes the address as its address. During subsequent subaddress and data cycles, the TVP6000 responds with an acknowledge as shown in Figure 2–3. The subaddress is auto-incremented after each data cycle.

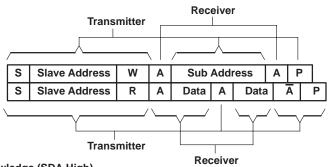

The transmitting device must not drive the SDA signal during the acknowledge cycle so that the receiving device may drive the SDA signal low. The not acknowledge,  $\overline{A}$ , condition is indicated by the master by keeping the SDA signal high just before it asserts the stop, P, condition. This sequence terminates a read cycle as shown in Figure 2–5.

The slave address consists of 7 bits of address along with 1 bit of read/write information as shown in Figures 2–4 and 2–5. For the TVP6000, the possible slave addresses (including the read/write bit) are 0x40 or 0x42 for write cycles or 0x41 and 0x43. Refer to Table 2–7 for additional base address information.

Figure 2-4. I<sup>2</sup>C Write Cycle

$\overline{A}$  = No Acknowledge (SDA High)

A = Acknowledge

S = Start Condition

P = Stop Condition

W = Write

R = Read

Figure 2-5. I<sup>2</sup>C Read Cycle

#### 2.3 Data Manager

The data manager resides at the very beginning of the processing pipeline. It receives the Y Cb Cr pixel data from the pixel bus and converts it to its internal YUV representation. Register F\_CONTROL at subaddress 3A and the SCN bit of the SCM register at subaddress 90 define the function of the data manager.

The data manager can receive data on either an 8-bit or 16-bit video port. In the 8-bit format, it receives data at port VP1 or VP2 (both 8-bits wide) depending on register bit FMT2, at every rising edge of LLC if scan conversion is disabled, and at every (rising and falling) edge of LLC if scan conversion is enabled. In the 16-bit format, it receives luminance information on the VP1 port and chrominance information on the VP2 port, at alternate rising edges of LLC (qualified by CREF) if scan conversion is disabled, or at every rising edge of LLC if scan conversion is enabled. Additionally, the data manager can generate pixels internally for a 100/100 color bar if the CBAR bit is set. The Y, U, and V values for this color bar are shown in Table 2–3.

Table 2-1. 16-Bit Video Port YUV 4:2:2

| TIME                | 0 | 1          | 2 | 3   | 4 | 5   | 6 | 7  |

|---------------------|---|------------|---|-----|---|-----|---|----|

| VP1[7:0]            | Y | <b>'</b> 0 | Y | 1   | Y | 2   | Y | '3 |

| VP2[7:0]            | С | Cb0        |   | Cb1 |   | Cb2 |   | 53 |

| Luma pixel number   |   | 0          |   | 1   |   | 2   |   | 3  |

| Chroma pixel number |   | (          |   |     |   | 2   | 2 |    |

Table 2–2. 8-Bit Multiplexed Video Port CCIR656 YUV 4:2:2

| TIME                 | 0   | 1  | 2   | 3  | 4   | 5  | 6   | 7  |

|----------------------|-----|----|-----|----|-----|----|-----|----|

| VP1[7:0] or VP2[7:0] | Cb0 | Y0 | Cr0 | Y1 | Cb2 | Y2 | Cr2 | Y3 |

| Luma pixel number    | 0   |    | 1   | 1  | 2   | 2  | 3   | 3  |

| Chroma pixel number  | C   |    | )   |    |     | 2  | 2   |    |

Table 2-3. 100/100 Color Bar in Twos Complement

| COLOR   | Y (hex) | Cb (hex) | Cr (hex) |

|---------|---------|----------|----------|

| White   | 6B      | 00       | 00       |

| Yellow  | 52      | 90       | 12       |

| Cyan    | 2A      | 26       | 90       |

| Green   | 11      | B6       | A2       |

| Magenta | EA      | 4A       | 5E       |

| Red     | D1      | DA       | 70       |

| Blue    | A9      | 70       | EE       |

| Black   | 90      | 00       | 00       |

The SCN bit in the SCM register enables or disables scan conversion. When scan conversion is disabled (SCN = 0), the input scan lines are interlaced at a field rate of 60 Hz for 525-line systems or 50 Hz for 625-line systems. When scan conversion is enabled (SCN = 1), the input scan lines are non-interlaced at a frame rate of 60 Hz or 50 Hz.

## 2.4 Scaling Processor

The scaling processor scales down the input image in both horizontal and vertical directions. In addition to scaling, the scaling processor filters the image in the vertical direction and removes annoying flickers, which are common when a computer-generated graphics or text, especially a static image, is displayed on TV. The scaling processor uses a 3-tap adaptive filter, whose coefficients are dynamically adjusted on a line-by-line basis to maintain optimal performance.

The scaling processor is enabled by setting the SCN register bit to 1. When scan conversion is enabled, the data manager receives non-interlaced pixel data via the demand mode interface and passes pixel data on to the scaling processor for overscan-compensation processing. The output of the scaling processor feeds the video encoder core for encoding. See Section 2.5, *Video Encoder* for a detailed description.

When the scaling processor is disabled, SCN reset to 0, the data manager receives pixel data via master or slave mode and passes pixel data directly to the video encoder core, bypassing the scaling processor.

The scaling processor, when enabled, is controlled by the following registers: SPPL, DPPL, SLPF, and DLPF. These registers define the size of the image before and after scaling. The SPPL register defines the number of active pixels per line before scaling and the DPPL register defines the number of active pixels per line after scaling. The SLPF register defines the number of active lines before scaling and the DLPF register defines the number of active lines after scaling. Refer to Section 2.11, *Register Descriptions* for additional information on these registers.

Vertical and horizontal over-scan compensation ratios are independently controlled by two pairs of registers. The VDTAH and VDTAL register pair define the vertical scaling ratio and the HDTAH and HDTAL register pair define the horizontal scaling ratio. The scaling ratio equations are given in the register description section. An over-scan compensation ratio up to 12.5% in both vertical and horizontal directions is supported.

When enabled, three modes of vertical scaling and two modes of horizontal scaling are provided for optimal performance of the target application. For computer graphics and text intensive static images, mode 2 vertical scaling (VSC[1:0] = 2) should be used for maximum flicker reduction. For DVD playback, mode 3 (VSC[1:0] =3) should be used for sharpness. The nearest neighbor mode is provided only for comparison and diagnostic purposes, and should not be used for normal applications.

Finally, the scaled image can be placed on the TV screen at a location defined by the VOFS and HOFS registers. VOFS and HOFS define the location of the upper left corner of the output image. See the definitions of the VOFS and HOFS registers for details.

Note that the SWPF bit is provided for test and diagnostic purposes. For normal applications, this bit must be set to 0 at all times.

#### 2.5 Video Encoder

#### 2.5.1 Luminance Encoding

Programmable gain is first applied to the luminance data output from the data manger or scaling processor depending on whether the TVP6000 is in regular or scan-conversion mode. The luminance gain is defined by the GAIN\_Y register at subaddresses 5F and 60. The horizontal sync, vertical sync, and setup insertion are then performed. Both black level and blank level are programmable through the BLACK\_LEVEL and BLANK\_LEVEL registers at subaddresses 5D and 5E, respectively.

All of the transition edges of the luminance signal such as the sync edges and active video edges are properly shaped and filtered to limit the bandwidth within the standards.

#### 2.5.2 Luminance Low-Pass and Interpolation Filter

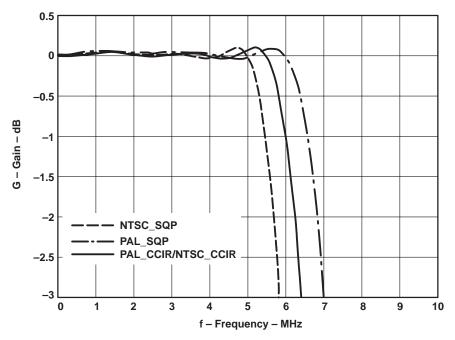

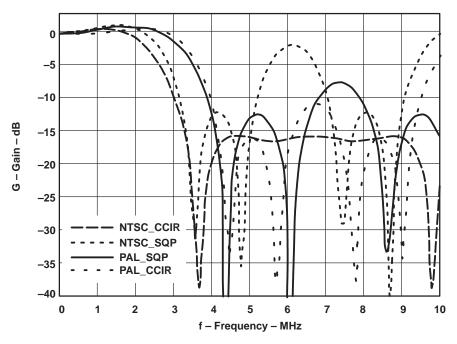

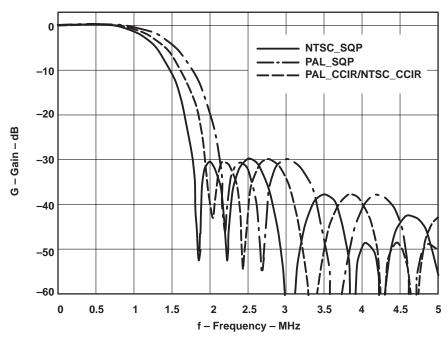

After all of the necessary components of the luminance signal have been added, the resultant signal is low-passed and interpolated to a 2x pixel rate. This 2x interpolation simplifies the external analog reconstruction filter design and improves the signal-to-noise ratio. Refer to Figure 2–6 for the filter frequency response.

Figure 2–6. Luma Path Frequency Response

Figure 2-7. Luma Cross Color Reduction Filter

#### 2.5.3 Cross Color Reduction Filter

An optional cross color reduction filter can be applied to the luminance signal before the luminance signal combines with the chrominance signal to form the composite signal. The cross color reduction filter reduces the interference between the luminance and chrominance in the composite signal. The cross reduction filter does not apply to S-video.

#### 2.5.4 Chrominance Encoding

The time-multiplexed U/V signal is adjusted by a pair of programmable gains. The gain for U and the gain for V are independently controlled by the GAIN\_U and GAIN\_V register bits respectively at subaddresses 5B, 5C, 5D, and 5E. The gain-adjusted signal then passes through a chrominance low-pass filter to limit the bandwidth of the U/V signal. The chrominance low-pass filter can be optionally bypassed by setting the CBW bit of the M\_CONTROL register at subaddress 61 to 0. This setting enlarges the bandwidth on U/V for S-video output.

The low-passed U/V signal is then subjected to a 1-to-4 interpolation through an interpolation filter. The data rate for both U and V is now at a 2x pixel rate.

The U and V signals are then quadrature-modulated by the internally generated subcarrier signal to form the chrominance (C) signal. The subcarrier reference signal color burst is inserted right before the active video.

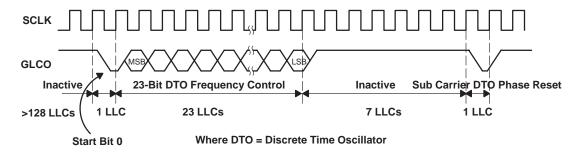

The frequency, the phase of the modulating subcarrier, and the amplitude of the color burst are all programmable. When genlock is disabled (the GLCE bit of the M\_CONTROL register set to 0), the subcarrier frequency is controlled by the S\_CARR registers at subaddresses 63, 64, 65, and 66. The values of the registers are computed based on the desired subcarrier frequency and the LLC clock using the equation in the register description. Table 2–12 lists the most commonly used values for various standards. When genlock is enabled (GLCE set to 1), the subcarrier frequency is updated once every scan line using the frequency control bits serially shifted in at the GLCI pin.

The C\_PHASE register at subaddress 5A controls the phase of the subcarrier. The phase of the color subcarrier is reset to C\_PHASE when enabled. Four modes of color subcarrier reset are provided: reset every two lines, every two fields, every eight fields, or at a reset bit input at the GLCI pin if genlock is enabled. Users can use the C\_PHASE register to adjust the subcarrier-to-horizontal sync phase. The bits BSTAP[6:0] of the BSTAMP register at subaddress 62 sets the amplitude of the color burst. The PAL bit of the M\_CONTROL register enables phase alternation line encoding. A sweeping subcarrier is generated to encode the chrominance signal when the PAL bit is set to 1. Otherwise a normal subcarrier is generated. Phase alternation line refers to an encoding scheme in which the subcarrier alternates between two different phases every scan line. There are two possible alternate sequences and the PALPHS bit of the M\_CONTROL register selects one of the sequences.

Figure 2-8. Chroma Path Frequency Response

## 2.6 Closed Caption

The TVP6000 can be programmed to encode closed caption data and extended data in the selected line. The closed caption data are sent to the TVP6000 through the I<sup>2</sup>C interface. The data stream consists of a seven-bit US-ASCII code and one odd parity bit as shown below.

| 1 | MSB ,      | 7    |      | US   | S-ASCII |      |      | LSB  |

|---|------------|------|------|------|---------|------|------|------|

|   | odd-parity | bit6 | bit5 | bit4 | bit3    | bit2 | bit1 | bit0 |

Closed caption data format

The standard service encodes closed caption only in the odd field, while the extended service encodes closed caption in both fields. L21ENA, when set to 1, enables closed caption encoding in the odd field and L21ENB, when set to 1 enables closed caption encoding in the even field.

The scan line where closed caption is to be encoded is programmable through the SLINE register at subaddress 6B.

Four closed caption data registers contain the closed caption data to be encoded. Registers LINE21\_O0 and LINE21\_O1 contain the first byte and the second byte of the close caption data to be encoded in the odd field. Registers LINE21\_E0 and LINE21\_E1 contain the first byte and the second byte of the closed caption data to be encoded in the even field. Immediately after the closed caption data is written to the closed caption data registers either for the odd field or even field, the corresponding closed caption status bit, CCE or CCO in the STATUS register at subaddress 02, is reset to 0 to indicate the closed caption data is available in the closed caption data registers and yet to be encoded. Immediately after the closed caption is encoded, the CCE or CCO bit is set to 1 to indicate the closed caption data has been encoded and is ready to accept new data. The null character is automatically inserted if the closed caption data is not written to the closed caption data registers in time for encoding.

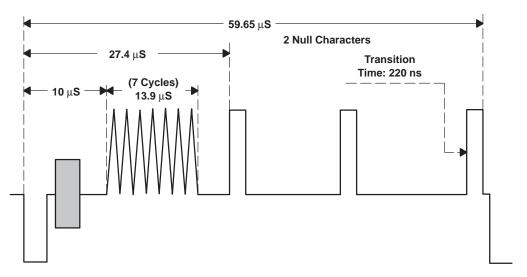

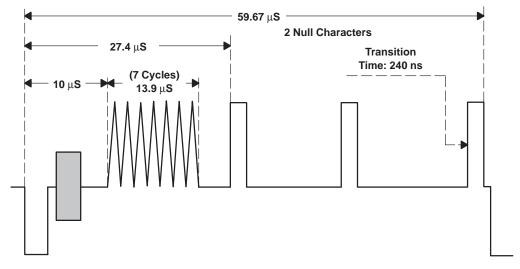

The run-in clock frequency is  $503496.5 \, \text{Hz}$  (  $32 \times \text{fline}$  of NTSC ). The closed caption data is encoded in the format of non-return to zero (NRZ). Additionally, the data translates to the IRE scale in the following manner:  $0 = 0 \, \text{IRE}$ ;  $1 = 50 \, \text{IRE}$ .

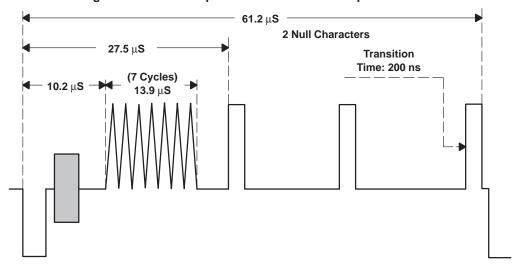

The following four figures present the parameters of a closed caption line implemented in different standards.

Figure 2-9. NTSC CCIR601 Rate Closed Caption Line

Figure 2-10. PAL CCIR601 Pixel Rate Closed Caption Line

Figure 2-11. NTSC Square Pixel Rate Closed Caption Line

Figure 2-12. PAL Square Pixel Rate Closed Caption Line

#### 2.7 Clock Generation

When the CDIR pin is tied low, the TVP6000 generates the clock from the crystal connected between XTAL1 and XTAL2. Optionally, an oscillator connected to XTAL1 can also be used. The clock is used internally and is also properly buffered and output at the LLC pin. The clock qualifying reference signal, CREF, is also an output in this mode.

When CDIR is tied high, the LLC and CREF pins are inputs. The TVP6000 receives the clock signal from the LLC pin and the clock qualifying reference signal from the CREF pin.

#### 2.8 Analog Output

The TVP6000 supports simultaneous composite and S-video outputs. Additionally, the DACs may be independently turned off via software to minimize power dissipation.

The output DACs are current sources and are optimal for driving a 37.5- $\Omega$  load with double 75- $\Omega$  termination. A 264- $\Omega$  full-scale adjust resistor must be connected between the FSADJ pin and ground.

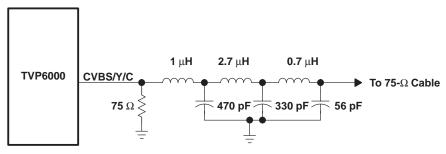

For cost-sensitive consumer applications, passive low-pass filters are recommended. Figure 2–13 illustrates the termination of the output DACs. An external analog filter, as shown in the figure, is also required.

Figure 2-13. Output Filter

#### 2.9 Video Port Interface

The TVP6000 provides a highly flexible video port interface, which users can tailor to fit their target applications. The video port interface consists of four raster controls: RCV1, RCV2, RCM1, and RCM2, an 8-bit or 16-bit pixel port: VP1 and/or VP2, and two clock related signals: LLC and CREF.

#### 2.9.1 RCV1

When scan conversion is disabled (SCN reset to 0), RCV1 can be programmed as an input or an output.

When RCV1 is used as an input, RCV1 can be programmed to receive vertical sync, frame sync, or sequence sync. At the same time, RCV1 can optionally be selected as the source of horizontal sync. The TVP6000 maintains three counters internally; horizontal counter, vertical counter, and field counter in order to generate correct timing for encoding. The horizontal sync input re-triggers the horizontal counter by resetting the horizontal counter to a preset value defined by the HTRIGGER0 and HTRIGGER1 registers.

Similarly, the vertical sync input re-triggers the vertical counter by resetting the vertical counter to a preset value defined by the VTRIGGER0 and VTRIGGER1 registers. The frame sync input forces the field to be the odd field. The sequence sync resets the field to be the first field of the field sequence.

When RCV1 is used as an output, RCV1 can be programmed to generate either vertical sync, frame sync, or sequence sync.

When scan-conversion is enabled (SCN =1), the demand mode video port interface is activated and RCV is output only and operates as the new frame indicator.

The polarity of RCV1 is programmable. Refer to the description of the SYN\_CTRL0 register for details.

#### 2.9.2 RCV2

When scan conversion is disabled, the RCV2 pin can be programmed as an input or an output.

When RCV2 is used as an input, RCV2 can be used as the horizontal sync based on the HSINSEL bit of the SYN\_CTRL0 register. RCV2 is used as the blanking signal if the CBLFV2 bit of the SYN\_CTRL0 register is set to 1, regardless whether or not RCV2 has been selected as the horizontal sync.

When scan-conversion is enabled, the demand mode video port interface is activated and RCV2 is output only and operates as the new line indicator.

Similar to RCV1, the polarity of RCV2 is programmable. Refer to the description of the SYN\_CTRL0 register for details.

#### 2.9.3 RCM1

RCM1 is always an output. This pin may be programmed to output either vertical sync, frame sync, or sequence sync. Unlike RCV1 and RCV2, the polarity of RCM1 is not programmable. Refer to the description of the RCM\_L21 register for details.

#### 2.9.4 RCM2

The RCM2 pin may be configured as an input or an output as shown in Table 2–19. The polarity of the RCM2 pin is programmable via this register as well.

As an output, this pin may be operated as a horizontal sync, composite blank, or a demand mode data request signal. As in input, this pin is always a composite blanking input.

When scan-conversion is enabled, the demand mode video port interface is activated and the RCM2 pin acts as the request output pin.

#### 2.10 Modes of Operation

With a highly programmable video port interface, the TVP6000 may be configured to operate in various modes, each tailored for a target application. In the following sections, several of the most commonly used modes are described.

#### 2.10.1 Master Mode

In the master mode, the TVP6000 generates all of the video timing signals for controlling an external graphics controller or MPEG decoder device. Table 2–4 lists the timing signals that are output from the TVP6000 during master mode.

PIN NAME I/O TYPE **DESCRIPTION** LLC Line locked clock; with 2X pixel clock frequency. Input/output **CREF** Input/output Data phase reference clock. RCM1 Output vertical/field timing, can be programmed as VSO/FSO/FSEQO Output RCV1 Output Output vertical/field timing, can be programmed as VSO/FSO/FSEQO Output horizontal timing, programmed as CBNO. Active duration is defined RCM2 Output by registers BMRQ and EMRQ, excluding vertical blanking interval. Output horizontal timing, programmed as HSO. Active duration is defined RCV2 Output by registers BRCV and ERCV.

Table 2-4. Master Mode

Refer to Table 2–15 and Table 2–17 for the definitions of VSO, FSO, FSEQO, and HSO.

A crystal with the correct frequency according to Table 2–5 should be connected between pins XTAL1 and XTAL2.

Table 2-5. Crystal Frequencies

| PIXEL RATE   | CLOCK FR    | EQUENCY  |

|--------------|-------------|----------|

| CCIR-601     | 27 MHz      | 27 MHz   |

| Square pixel | 24.5454 MHz | 29.5 MHz |

#### 2.10.2 Slave Mode

In slave mode, all clock and video timing signals are supplied from an external source. The source may be a graphics controller, an MPEG device, or a TV decoder such as the TVP5010/TVP5020 decoders. Table 2–6 lists the signal definitions for slave mode.

Table 2-6. Slave Mode Signals

| PIN NAME | I/O TYPE | DESCRIPTION                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LLC      | Input    | Line locked clock with 2X pixel clock frequency. CDIR pin is tied high. |

| CREF     | Input    | Data phase reference clock. CDIR pin is tied high.                      |

| RCM1     | Output   | Output Vertical/Field timing, can be programmed as VSO/FSO/FSEQO        |

| RCV1     | Input    | Can be programmed as VSI/FSI/FSEQI.                                     |

| RCM2     | Input    | Programmed as CBNI.                                                     |

| RCV2     | Input    | Programmed as HSI.                                                      |

Refer to Table 2–15 and Table 2–17 for the definition of VSO, FSO, FSEQO, HSO, VSI, FSI, FSEQI, CBNI, and HSI.

#### 2.10.3 Demand Mode

Demand mode is an interface specially designed for scan conversion. When scan conversion is enabled, the TVP6000 accepts non-interlaced pixel data, performs signal processing functions which include non-interlace-to-interlace conversion, flicker filtering and overscan-compensation, and outputs interlaced NTSC/PAL video. Due to the nature of the functions that the TVP6000 performs during scan conversion, the bandwidth of the input pixel increases and exceeds what the master and slave mode interface can provide. Demand mode provides extra bandwidth to meet the needs of the TVP6000.

Unlike master mode and slave mode, the video port interface timing for demand mode is decoupled from the timing of the internal encoder core.

The TVP6000 operates in demand mode when it requests data from an external graphics controller or an MPEG device. Demand mode is enabled by setting SCM[0] = 1, the SCN bit.

In demand mode, the TVP6000 asserts the RCM2 pin high to request additional data from the external source and negates the RCM2 pin to stop additional data transfer. Table 2–19 shows how the RCM2 pin may be programmed to operate as a request signal during demand mode. In addition, the NLR register is used to program the threshold where the RCM2 pin is toggled for requests.

#### 2.10.4 Genlock Mode

The TVP6000 may be configured in a genlock mode to an external TV decoder such as the TVP5000/TVP5010 device. This configuration allows the decoder to drive video timing information to the TVP6000 encoder. The genlock mode is used to control clock jitter and thus allows the encoder to generate accurate color burst information.

In this configuration, GLCI pin is connected to the GLCO pin of the decoder, and the line-lock clock pin, LLC, is fed by the decoder main pixel clock output. Moreover, the color sub-carrier information is formatted as a 23-bit binary number and is transmitted serially. The transmission timing diagram is shown in Figure 2–13.

Figure 2-14. Transmission Timing

## 2.11 Register Descriptions

The TVP6000 is a standard  $I^2C$  slave device. All of the registers can be written and read through the  $I^2C$  interface. The  $I^2C$  base addresses of the TVP6000 are dependent on pin 15 (SA) as listed in Table 2–7.

Table 2-7. Base Addresses

| PIN 15 | WRITE ADDRESS<br>(hex) | READ ADDRESS (hex) |

|--------|------------------------|--------------------|

| 0      | 40                     | 41                 |

| 1      | 42                     | 43                 |

Table 2-8. Register Bit Allocation Map

| REGISTER    | R/W | SUB-<br>ADDRESS | ВІТ7        | ВІТ6           | BIT5   | BIT4   | ВІТ3       | BIT2 | BIT1     | ВІТ0  |

|-------------|-----|-----------------|-------------|----------------|--------|--------|------------|------|----------|-------|

| DEV_ID      | R   | 00              | Dev id[7:0] |                |        |        |            |      |          |       |

| REV_ID      | R   | 01              |             |                |        | Rev id | [7:0]      |      |          |       |

| STATUS      | R   | 02              |             | Scon           | Ccon   | Cce    | Cco        |      | Fsq[2:0] |       |

| Reserved    |     | 03–39           |             |                |        | Rese   | rved       |      |          |       |

| F_CONTROL   | R/W | 3A              | Cbar        |                |        | Fmt2   | Y2c        | Uv2c | Fmt[     | [1:0] |

| Reserved    |     | 3B-59           |             |                |        | Rese   | rved       |      |          |       |

| C_PHASE     | R/W | 5A              |             |                |        | Cphase | e[7:0]     |      |          |       |

| GAIN_U      | R/W | 5B              |             |                |        | Gu[7   | ':0]       |      |          |       |

| GAIN_V      | R/W | 5C              |             | Gv[7:0]        |        |        |            |      |          |       |

| BLACK_LEVEL | R/W | 5D              | Gu8         | Gu8 Black[6:0] |        |        |            |      |          |       |

| BLANK_LEVEL | R/W | 5E              | Gv8         |                |        | Е      | 3lank[6:0] |      |          |       |

| GAIN_Y      | R/W | 5F              |             |                |        | Gy[7   | ':0]       |      |          |       |

| X_COLOR     | R/W | 60              | 0           | Хc             | Gy8    |        |            |      | Lcd[2:0] |       |

| M_CONTROL   | R/W | 61              | Sdown       | Cdown          | Palphs | 0      | Glce       | Cbw  | Pal      | Ffrq  |

| BSTAMP      | R/W | 62              | Sqp         |                |        | Е      | 3stap[6:0] |      |          |       |

| S_CARR1     | R/W | 63              |             |                |        | Fsc[7  | 7:0]       |      |          |       |

| S_CARR2     | R/W | 64              |             |                |        | Fsc[1  | 5:8]       |      |          |       |

| S_CARR3     | R/W | 65              | Fsc[23:16]  |                |        |        |            |      |          |       |

| S_CARR4     | R/W | 66              | Fsc[31:24]  |                |        |        |            |      |          |       |

| LINE21_O0   | R/W | 67              | L21o[7:0]   |                |        |        |            |      |          |       |

| LINE21_O1   | R/W | 68              |             |                |        | L21o[  | 15:8]      |      |          |       |

Table 2–8. Register Bit Allocation Map (Continued)

| REGISTER  | R/W | SUB-<br>ADDRESS | BIT7           | BIT6   | BIT5       | BIT4   | BIT3  | BIT2       | BIT1        | BIT0   |

|-----------|-----|-----------------|----------------|--------|------------|--------|-------|------------|-------------|--------|

| LINE21_E0 | R/W | 69              |                |        |            | L21e   | 7:0]  | •          |             |        |

| LINE21_E1 | R/W | 6A              |                |        |            | L21e[  | 15:0] |            |             |        |

| LN_SEL    | R/W | 6B              |                |        |            |        |       | Sline[4:0] |             |        |

| SYN_CTRL0 | R/W | 6C              | Rcv1a          | Rcv1b  | Hsinel     | Orcv1  | Prcv1 | Cblfv2     | Orcv2       | Prcv2  |

| RCML21    | R/W | 6D              | Crcm2          | Cblfm2 | Orcm2      | Prcm2  | Rcm1a | Rcm1b      | L21ena      | L21enb |

| HTRIGGER0 | R/W | 6E              |                |        |            | htrig[ | 7:0]  |            |             |        |

| HTRIGGER1 | R/W | 6F              |                |        |            |        |       |            | Htrig[10:8] |        |

| VTRIGGER  | R/W | 70              | Presa          | Presb  | Sblank     |        |       | Vtrig[4:0] |             |        |

| BMRQ      | R/W | 71              |                |        |            | Bmrq   | [7:0] |            |             |        |

| EMRQ      | R/W | 72              |                |        |            | Emrq   | [7:0] |            |             |        |

| BEMRQ     | R/W | 73              |                |        | Emrq[10:8] |        |       |            | Bmrq[10:8   | ]      |

| RESERVED  |     | 74–76           |                |        |            | Rese   | rved  |            |             |        |

| BRCV      | R/W | 77              |                |        |            | Brcv[  | 7:0]  |            |             |        |

| ERCV      | R/W | 78              |                |        |            | Ercv[  | 7:0]  |            |             |        |

| BERCV     | R/W | 79              |                |        | Ercv[10:8] |        |       |            | Brcv[10:8]  |        |

| FLEN      | R/W | 7A              |                |        |            | Flen[  | 7:0]  |            |             |        |

| FAL       | R/W | 7B              |                |        |            | Fal[7  | 7:0]  |            |             |        |

| LAL       | R/W | 7C              | Lal[7:0]       |        |            |        |       |            |             |        |

| FLAL      | R/W | 7D              | Lal8 Fal8 Flen |        |            |        |       | [9:8]      |             |        |

| SYN_CTRL1 | R/W | 7E              |                | Esav   | Ignp       | Free   | Blnks | Avm        | [1:0]       |        |

| RESERVED  |     | 7F              |                |        |            | Rese   | rved  |            |             |        |

| SCM       | R/W | 90              |                |        | Swpf       | Hsc    | [1:0] | Vsc        | [1:0]       | Scn    |

| SLPF      | R/W | 91              |                |        |            | Slpf[  | 7:0]  |            |             |        |

| SPPL      | R/W | 92              |                |        |            | Sppl[  | 7:0]  |            |             |        |

| SLPH      | R/W | 93              |                |        | Sppl[      | 9:8]   |       |            | Slpf        | [9:8]  |

| DLPF      | R/W | 94              |                |        |            | Dlpf[  | 7:0]  |            |             |        |

| DPPL      | R/W | 95              |                |        |            | Dppl[  | 7:0]  |            |             |        |

| DLPH      | R/W | 96              |                |        | Dppl[      | 9:8]   |       |            | Dlpf        | [9:8]  |

| VDTAL     | R/W | 97              |                |        |            | Vdta[  | 7:0]  |            |             |        |

| VDTAH     | R/W | 98              |                |        |            | Vdta[  | 15:8] |            |             |        |

| HDTAL     | R/W | 99              |                |        |            | Hdta[  | 7:0]  |            |             |        |

| HDTAH     | R/W | 9A              |                |        |            | Hdta[  | 15:8] |            |             |        |

| VOFS      | R/W | 9B              |                |        |            | Vofs[  | 7:0]  |            |             |        |

| HOFS      | R/W | 9C              | Hofs[7:0]      |        |            |        |       |            |             |        |

| NLR       | R/W | 9D              | Nlr[7:0]       |        |            |        |       |            |             |        |

| TEST1     | R/W | 9E              |                |        |            |        |       |            |             |        |

| TEST2     | R/W | 9F              |                |        |            |        |       |            |             |        |

| TEST3     | R/W | A0              |                |        |            |        |       |            |             |        |

| RESERVED  |     | A1–FF           |                |        |            | Rese   | rved  |            |             |        |

#### 2.11.1 DEV\_ID

#### Subaddress:00 (Read Only) Default: 0x60

| 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------|---|---|---|---|---|---|---|--|

| Dev_ID[7:0] |   |   |   |   |   |   |   |  |

This read only register contains the device ID for the TVP6000. The 8-bit device ID for the TVP6000 is 0x60.

#### 2.11.2 REV ID

#### Subaddress:01 (Read Only) Default: 0x00

| 7 | 6 | 5 | 4     | 3       | 2 | 1 | 8 |

|---|---|---|-------|---------|---|---|---|

|   |   |   | Rev_I | ID[7:0] |   |   |   |

This read only register contains the revision ID for the TVP6000. The revision ID identifies different revisions of the device.

#### 2.11.3 STATUS

#### Subaddress:02 (Read Only)

|   | 7 | 6    | 5    | 4   | 3   | 2        | 1 | 0 |

|---|---|------|------|-----|-----|----------|---|---|

| Ī |   | SCON | CCON | CCE | cco | FSQ[2:0] |   |   |

Where:

SCON S-video connection status

0 Not connected

1 Connected

CCON Composite video connection status

0 Not connected

1 Connected

CCE Closed-caption status bit for even field. This bit is set immediately after the data in registers LINE21\_E0 and LINE21\_E1 has been encoded to closed caption. This bit is reset when both of these registers are written.

CCO Closed-caption status bit for odd field. This bit is set immediately after the data in registers LINE21\_O0 and LINE21\_O1 has been encoded to closed caption. This bit is reset when both of these registers are written.

FSQ[2:0] Field sequence ID. For PAL, all three bits FSQ[2:0] are used whereas for NTSC only bits FSQ[1:0] are meaningful. Futhermore, FSQ(0) represents the odd field when it is a 0 and the even field when it is 1.

## 2.11.4 F\_CONTROL

Subaddress:3A Default: 0x8D

| 7    | 6 | 5 | 4      | 3   | 2    | 1        | 0 |

|------|---|---|--------|-----|------|----------|---|

| CBAR |   |   | FTM[2] | Y2C | UV2C | FTM[1:0] |   |

Format control register. This register specifies the input video source and format. Where:

CBAR Select video data source

Use external video sourceUse internal color bars

Y2C Y data format selection

0 The input Y data are in twos complement format

The input Y data are in binary format

UV2C CrCb data format selection

The input CrCb data is in twos complement format

1 The inputCrCb data is in binary format

FTM[2:0] These three bits determine the video input data stream format and timing as listed

in Table 2-9. The SCN bit (subaddress 90, bit 0) is also used in this decode.

Table 2-9. Input Format and Data Sampling

| SCN | F               | TM[2:0 | )]        | INPUT FORMAT                              | SAMPLING TIME                                                | INTERNAL<br>ENCODER<br>CLOCK |

|-----|-----------------|--------|-----------|-------------------------------------------|--------------------------------------------------------------|------------------------------|

| 0   | Х               | ( 0 0  |           | Reserved                                  | Reserved                                                     | Reserved                     |

| 0   | X 0 1           |        | 1         | YUV 4:2:2 on VP1 and VP2                  | Data is sampled at the rising edge of LLC qualified by CREF. | LLC                          |

| 0   | 0 1 0           |        | 0         | YUV 4:2:2 on VP1 port                     | Data is sampled at the rising edge of LLC                    | LLC                          |

| 0   | 1               | 1      | 0         | YUV 4:2:2 on VP2 port                     | Data is sampled at the rising edge of LLC                    | LLC                          |

| 0   | 0               | 1      | 1         | CCIR 656 on VP1 port                      | Data is sampled at the rising edge of LLC                    | LLC                          |

| 0   | 1               | 1      | 1         | CCIR 656 on VP2 port                      | Data is sampled at the rising edge of LLC                    | LLC                          |

| 1   | Х               | 0      | 0         | Reserved                                  | Reserved                                                     | Reserved                     |

| 1   | X 0 1 YUV 4:2:2 |        | YUV 4:2:2 | Data is sampled at the rising edge of LLC | LLC                                                          |                              |

| 1   | 0 1 0           |        | 0         | YUV 4:2:2 on VP1 port                     | Data is sampled at both edges of LLC                         | LLC                          |

| 1   | 1 1 0           |        | 0         | YUV 4:2:2 on VP2 port                     | Data is sampled at both edges of LLC                         | LLC                          |

| 1   | X 1 1           |        |           | Reserved                                  |                                                              |                              |

## 2.11.5 C\_PHASE

Subaddress: 5A Default: 0x00

| 7 | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|---|---|---|------|--------|---|---|---|

|   |   |   | CPH: | S[7:0] |   |   |   |

Where:

CPHS[7:0] Phase of encoded video color subcarrier (including the color burst) relative to Hsync. The adjustable step is 360/256.

#### 2.11.6 GAIN\_U

Subaddress: 5B Default: 0x01

| 7 | 6 | 5 | 4  | 3     | 2 | 1 | 0 |

|---|---|---|----|-------|---|---|---|

|   |   |   | GU | [7:0] |   |   |   |

Where:

GU[7:0] Gain control of Cb signal. The MSB, GU8, is located at subaddress 5D, bit 7.

In the case of NTSC with a 7.5 IRE pedestal, WHITE – BLACK = 92.5 IRE

Gain\_U= 0x101.

In the case of no pedestal (PAL/SECAM), WHITE - BLACK = 100 IRE.

Gain\_U = 0x115.

## 2.11.7 GAIN\_V

Subaddress: 5C Default: 0x6B

| 7 | 6 | 5 | 4  | 3     | 2 | 1 | 0 |

|---|---|---|----|-------|---|---|---|

|   |   |   | GV | [7:0] |   |   |   |

Where:

GV[7:0] Gain control of Cr signal. The MSB, GV8 is located at subaddress 5E, bit 7.

In the case of NTSC with a 7.5 IRE pedestal, WHITE – BLACK = 92.5 IRE.

$Gain_V = 0x16B.$

In the case of no pedestal (PAL/SECAM), WHITE – BLACK = 100 IRE.

$Gain_V = 0x18C.$

#### 2.11.8 BLACK\_LEVEL

Subaddress: 5D Default: 0xCC

| 7   | 6 | 5 | 4 | 3          | 2 | 1 | 0 |

|-----|---|---|---|------------|---|---|---|

| GU8 |   |   |   | BLACK[6:0] |   |   |   |

Where:

GU8 The most significant bit of the GAIN\_U register. See the GAIN\_U register for more information.

BLACK[6:0] Black level setting for NTSC = 0x4C and for PAL = 0x3C.

## 2.11.9 BLANK\_LEVEL

Subaddress: 5E Default: 0xB8

| 7   | 6 | 5 | 4 | 3          | 2 | 1 | 0 |

|-----|---|---|---|------------|---|---|---|

| GV8 |   |   |   | BLANK[6:0] |   |   |   |

Where:

GV8

The most significant bit of the GAIN\_V register. See the GAIN\_V register for more information

BLANK[6:0]Blank level setting for NTSC = 0x38 and for PAL = 0x3C.

#### 2.11.10 GAIN\_Y

Subaddress: 5F Default: 0x2E

| 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---|---|---|---|---|---|---|--|--|

| GY(7-0) |   |   |   |   |   |   |   |  |  |

Where:

GY[7:0]

Gain control of Y signal. The MSB, bit 8, is located at subaddress 60, bit 5. In the case of NTSC with a 7.5 IRE pedestal, WHITE – BLACK = 92.5 IRE.

Gain Y = 0x12E

In the case of no pedestal (PAL/SECAM), WHITE – BLACK = 100 IRE.

$Gain_Y = 0x145$

#### 2.11.11 X\_COLOR

Subaddress: 60 Default: 0x20

| 7 | 6  | 5   | 4 | 3 | 2        | 1 | 0 |

|---|----|-----|---|---|----------|---|---|

|   | XC | GY8 |   |   | LCD(2-0) |   |   |

Cross color and chroma delay compensation register

Where:

XC Cross color reduction enable for composite video output. Cross color does not affect

S-video output

O Cross color reduction is disabled (default)

1 Cross color reduction is enabled

GY8 MSB of Gain\_Y register.

LCD[2:0] These three bits can be used for chroma channel delay compensation during S-video mode. Table 2–10 shows the delay corresponding to the LCD[2:0] settings.

Table 2-10. Chroma Channel Delays

|   | LCD[2:0] |   | DELAY ON CHROMA<br>CHANNEL |  |  |  |

|---|----------|---|----------------------------|--|--|--|

| 0 | 0        | 0 | 0                          |  |  |  |

| 0 | 0 1      |   | 0.5 pixel clock period     |  |  |  |

| 0 | 1 0      |   | 1 pixel clock period       |  |  |  |

| 0 | 0 1 1    |   | 1.5 pixel clock period     |  |  |  |

| 1 | Х        | Х | 2 pixel clock period       |  |  |  |

#### 2.11.12 M\_CONTROL

Subaddress: 61 Default: 0x05

| 7     | 6     | 5      | 4 | 3    | 2   | 1   | 0    |

|-------|-------|--------|---|------|-----|-----|------|

| SDOWN | CDOWN | PALPHS |   | GLCE | CBW | PAL | FFRQ |

Mode control register. This register provides various operating mode controls including DAC power management.

Where:

SDOWN S-video DAC power down

0 Normal operation (default)

1 Power down mode

CDOWN Composite video DAC power down

0 Normal operation (default)

1 Power down mode

PALPHS PAL switch phase setting

O PAL switch phase is nominal (default)

1 PAL switch phase is inverted compared to nominal

GLCE Genlock control enable. See Table 2–20.

No genlock to the color subcarrier frequency (default)

1 Genlock-to-color subcarrier frequency is from the TVP5010

CBW Chrominance encoding bandwidth enlarge enable

0 Bandwidth for chrominance encoding is enlarged

Standard bandwidth for chrominance encoding (default)

PAL Phase alternation line encoding selection

O Phase alternation line encoding disabled (default)

1 Phase alternation line encoding enabled

FFRQ Field rate selection. Refer to Table 2–11 for programming information.

0 50 Hz

1 60 Hz (default)

#### 2.11.13 BSTAMP

Subaddress: 62 Default:0x38

| ĺ | 7   | 6 | 5 | 4 | 3          | 2 | 1 | 0 |

|---|-----|---|---|---|------------|---|---|---|

|   | SQP |   |   |   | BSTAP[6:0] |   |   |   |

Color burst amplitude

Where:

SQP Square-pixel sampling rate. Refer to Table 2–11 for programming information.

0 CCIR601 sampling rate

1 Square-pixel sampling rate

BSTAP[6:0] Setting of the amplitude of color burst. The value for NTSC = 0x38 and for PAL = 0x41.

The SQP and FFRQ bits control the total number of horizontal pixels displayed per scan line. In addition, these bits control the CCIR, NTSQ, and PASQ status pins as shown in Table 2–11.

Table 2-11. Total Horizontal Pixel Selection

| MODE              | SQP | FFRQ | CCIR | NTSQ | PASQ | NUMBER OF PIXELS PER LINE |

|-------------------|-----|------|------|------|------|---------------------------|

| CCIR601 PAL       | 0   | 0    | high | low  | low  | 864                       |

| CCIR601 NTSC      | 0   | 1    | high | low  | low  | 858                       |

| Square pixel PAL  | 1   | 0    | low  | low  | high | 944                       |

| Square pixel NTSC | 1   | 1    | low  | high | low  | 780                       |

## 2.11.14 S\_CARR1, 2, 3, 4

Subaddress: 63, 64, 65, 66 Default: 0xF6, 0x7B, 0xF0, 0x21

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FSC07 | FSC06 | FSC05 | FSC04 | FSC03 | FSC02 | FSC01 | FSC00 |

| FSC15 | FSC14 | FSC13 | FSC12 | FSC11 | FSC10 | FSC09 | FSC08 |

| FSC23 | FSC22 | FSC21 | FSC20 | FSC19 | FSC18 | FSC17 | FSC16 |

| FSC31 | FSC30 | FSC29 | FSC28 | FSC27 | FSC26 | FSC25 | FSC24 |

Color subcarrier frequency registers

Where:

FSC[31:0] These four bytes of data are used to program the color subcarrier frequency. These four bytes are determined by the following formula.

$S_{carr} = ROUND((Fsc/Fclock) \times 2^{32})$

Table 2–12 lists some common values for S\_CARR.

Table 2-12. S\_CARR Values

| STANDARD                     | PIXEL<br>TYPE | SUBCARRIER<br>FREQUENCY (fsc) | CLOCK<br>(fclock) | S_CARR (dec)        | S_CARR (hex) |

|------------------------------|---------------|-------------------------------|-------------------|---------------------|--------------|

| M/NTSC                       | Rectangular   | 3.579545 MHz                  | 27 MHz            | 569408543 (default) | 21F07C1F     |

| B, D, G, H, I, N/PAL         | Rectangular   | 4.43361875 MHz                | 27 MHz            | 705268427           | 2A098ACB     |

| N/PAL (combination N/PAL)    | Rectangular   | 3.58205625 MHz                | 27 MHz            | 569807942           | 21F69446     |

| M/PAL                        | Rectangular   | 3.5756083125 MHz              | 27 MHz            | 568782819           | 21E6EFE3     |

| M/NTSC                       | Square        | 3.579545 MHz                  | 24.5454 MHz       | 626349397           | 25555555     |

| B, D, G, H, I, N/PAL         | Square        | 4.43361875 MHz                | 29.5 MHz          | 645499916           | 26798C0C     |

| N/PAL<br>(combination N/PAL) | Square        | 3.58205625 MHz                | 29.5 MHz          | 521519134           | 1F15C01E     |

| Combinational N              | Square        | 3.5756083125 MHz              | 24.5454 MHz       | 625661101           | 254AD4AD     |

## 2.11.15 LINE21\_O0

#### Subaddress: 67

| 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---|-----------|---|---|---|---|---|---|--|--|

|   | L210[7:0] |   |   |   |   |   |   |  |  |

Where: