**UC1633** UC2633 UC3633

## Phase Locked Frequency Controller

#### **FEATURES**

- Precision Phase Locked Frequency Control System

- Crystal Oscillator

- Programmable Reference Frequency Dividers

- Phase Detector with Absolute Frequency

- Digital Lock Indicator

- Double Edge Option on the Frequency Feedback Sensing Amplifier

- Two High Current Op-Amps

- 5V Reference Output

#### DESCRIPTION

The UC1633 family of integrated circuits was designed for use in phase locked frequency control loops. While optimized for precision speed control of DC motors, these devices are universal enough for most applications that require phase locked control. A precise reference frequency can be generated using the device's high frequency oscillator and programmable frequency dividers. The oscillator operates using a broad range of crystals, or, can function as a buffer stage to an external frequency source.

The phase detector on these integrated circuits compares the reference frequency with a frequency/phase feedback signal. In the case of a motor, feedback is obtained at a hall output of other speed detection device. This signal is buffered by a sense ampilfier that squares up the signal as it goes into the digital phase detector. The phase detector responds proportionally to the phase error between the reference and the sense amplifier output. This phase detector includes absolute frequency steering to provide maximum drive signals when any frequency error exists. This feature allows optimum start-up and lock times to be realized.

Two op-amps are included that can be configured to provide necessary loop filtering. The outputs of the op-amps will source or sink in excess of 16mA, so they can provide a low impedence control signal to driving circuits.

Additional features include a double edge option on the sense amplifier that can be used to double the loop reference frequency for increased loop bandwidths. A digital lock signal is provided that indicates when there is zero frequency error, and a 5V reference output allows DC operating levels to be accurately set.

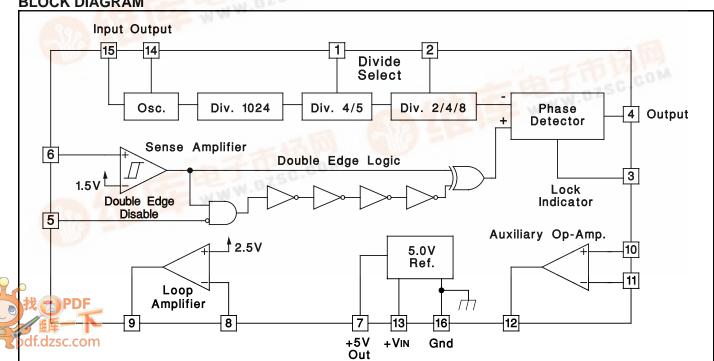

## **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Input Supply Voltage (+VIN) +20V               |

|------------------------------------------------|

| Reference Output Current30mA                   |

| Op-Amp Output Currents                         |

| Op-Amp Input Voltages                          |

| Phase Detector Output Current                  |

| Lock Indicator Output Current +15mA            |

| Lock Indicator Output Voltage +20V             |

| Divide Select Input Voltages3V to +10V         |

| Double Edge Disable Input Voltage 3V to +10V   |

| Oscillator Input Voltage                       |

| Sense Amplifier Input Voltage                  |

| Power Dissipation at TA = 25°C (Note 2 1000mW  |

| Power dissipation at Tc = 25°C (Note 2) 2000mW |

| Operating Junction Temperature55°C to +150°C   |

| Storage Temperature65°C to +150°C              |

| Lead Temperature (Soldering, 10 Seconds) 300°C |

|                                                |

Note1: Voltages are referenced to ground, (Pin 16). Currents are positive into, negative out of, the specified terminals. Note 2: Consult Packaging Section of Databook for thermal limitations and considerations of package.

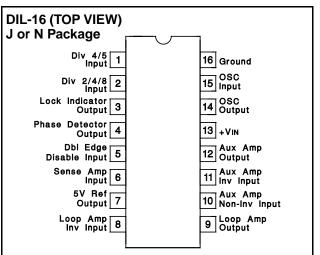

## **CONNECTION DIAGRAMS**

| PLCC-20 (TOP VIEW)     | PACKAGE PIN FUNCTION   |     |  |

|------------------------|------------------------|-----|--|

| Q Package              | FUNCTION               | PIN |  |

|                        | N/C                    | 1   |  |

|                        | Div 4/5 Input          | 2   |  |

|                        | Div 2/4/8 Input        | 3   |  |

|                        | Lock Indicator Output  | 4   |  |

|                        | Phase Detector Output  | 5   |  |

|                        | N/C                    | 6   |  |

| / <del>2 2 2 2 2</del> | Dbl Edge Disable Input | 7   |  |

| 3 2 1 20 19            | Sense Amp Input        | 8   |  |

|                        | 5V Ref Output          | 9   |  |

| 5 17                   | Loop Amp Inv Input     | 10  |  |

| 6 16                   | N/C                    | 11  |  |

| 7 15                   | Loop Amp Output        | 12  |  |

| 1                      | Aux Amp Non-Inv Input  | 13  |  |

| 8 9 10 11 12 13 14 I   | Aux Amp Inv Input      | 14  |  |

|                        | Aux Amp Output         | 15  |  |

|                        | N/C                    | 16  |  |

|                        | +VIN                   | 17  |  |

|                        | OSC Output             | 18  |  |

|                        | OSC Input              | 19  |  |

|                        | Ground                 | 20  |  |

**ELECTRICAL CHARACTERISTICS:** (Unless otherwise stated, these specifications apply for TA =  $0^{\circ}$ C to +70°C for the UC3633, -25°C to +85°C for the UC2633, -55°C to +125°C for the UC1633, +VIN = 12V; TA=TJ.)

| PARAMETER                   | TEST CONDITIONS                           | MIN. | TYP. | MAX. | UNITS |

|-----------------------------|-------------------------------------------|------|------|------|-------|

| Supply Current              | +VIN = 15V                                |      | 20   | 28   | mA    |

| Reference                   |                                           |      |      |      |       |

| Output Voltage (VREF)       |                                           | 4.75 | 5.0  | 5.25 | V     |

| Load Regulation             | IOUT = 0V to 7mA                          |      | 5.0  | 20   | mV    |

| Line Regulation             | +VIN = 8V to 15V                          |      | 2.0  | 20   | mV    |

| Short Circuit Current       | Vout = 0V                                 | 12   | 30   |      | mA    |

| Oscillator                  |                                           |      | _    | _    |       |

| DC Voltage Gain             | Oscillator Input to Oscillator Output     | 12   | 16   | 20   | dB    |

| Input DC Level (VIB)        | Oscillator Input Pin Open, TJ = 25°C      | 1.15 | 1.3  | 1.45 | V     |

| Input Impedance (Note 3)    | $VIN = VIB \pm 0.5V$ , $TJ = 25^{\circ}C$ | 1.3  | 1.6  | 1.9  | kΩ    |

| Output DC Level             | Oscillator Input Pin Open, TJ = 25°C      | 1.2  | 1.4  | 1.6  | V     |

| Maximum Operating Frequency |                                           | 10   |      |      | MHz   |

| Dividers                    |                                           |      | _    | _    |       |

| Maximum Input Frequency     | Input = 1VPP at Oscillator Input          | 10   |      |      | MHz   |

| Div. 4/5 Input Current      | Input = 5V (Div. by 4)                    |      | 150  | 500  | μΑ    |

|                             | Input = 0V (Div. by 5)                    | -5.0 | 0.0  | 5.0  | μΑ    |

| Div. 4/5 Threshold          |                                           | 0.5  | 1.6  | 2.2  | V     |

Note 3: These impedence levels will vary with T<sub>J</sub> at about 1700ppm/°C

**ELECTRICAL** (Unless otherwise stated, these specifications apply for TA =  $0^{\circ}$ C to +70°C for the UC3633, CHARACTERISTICS (cont.): -25°C to +85°C for the UC2633, -55°C to +125°C for the UC1633, +VIN = 12V; TA=TJ.)

| PARAMETER                           | TEST CONDITIONS                                   | MIN. | TYP. | MAX. | UNITS |

|-------------------------------------|---------------------------------------------------|------|------|------|-------|

| Dividers (cont.)                    |                                                   |      |      |      |       |

| Div. 2/4/8 Input Current            | Input = 5V (Div. by 8)                            |      | 150  | 500  | μΑ    |

|                                     | Input = 0V (Div. by 2)                            | -500 | -150 |      | μΑ    |

| Div. 2/4/8 Open Circuit Voltage     | Input Current = 0μA (Div. by 4)                   | 1.5  | 2.5  | 3.5  | V     |

| Div. by 2 Threshold                 |                                                   | 0.20 | 0.8  |      | V     |

| Div. by 4 Threshold                 |                                                   | 1.5  |      | 3.5  | V     |

| Div. by 8 Threshold                 | Volts Below VREF                                  | 0.20 | 0.8  |      | V     |

| Sense Amplifier                     |                                                   |      |      |      |       |

| Threshold Voltage                   | Percent of VREF                                   | 27   | 30   | 33   | %     |

| Threshold Hysteresis                |                                                   |      | 10   |      | mV    |

| Input Bias Current                  | Input = 1.5V                                      | -1.0 | -0.2 |      | μΑ    |

| Double Edge Disable Input           |                                                   |      | _    |      | -     |

| Input Current                       | Input = 5V (Disabled)                             |      | 150  | 500  | μΑ    |

|                                     | Input = 0V (Enabled)                              | -5.0 | 0.0  | 5.0  | μΑ    |

| Threshold Voltage                   |                                                   | 0.5  | 1.6  | 2.2  | ٧     |

| Phase Detector                      |                                                   |      |      |      |       |

| High Output Level                   | Positive Phase/Freq. Error, Volts Below VREF      |      | 0.2  | 0.5  | V     |

| Low Output Level                    | Negative Phase/Freq. Error                        |      | 0.2  | 0.5  | V     |

| Mid Output Level                    | Zero Phase/Freq. Error, Percent of VREF           | 47   | 50   | 53   | %     |

| High Level Maximum Source Current   | VOUT = 4.3V                                       | 2.0  | 8.0  |      | mA    |

| Low Level Maximum Sink Current      | Vout = 0.7V                                       | 2.0  | 5.0  |      | mA    |

| Mid Level Output Impedance (Note 3) | IOUT = $-200$ to $+200\mu$ A, TJ = $25^{\circ}$ C | 4.5  | 6.0  | 7.5  | kΩ    |

| Lock Indicator Output               |                                                   |      |      |      |       |

| Saturation Voltage                  | Freq. Error, IOUT = 5mA                           |      | 0.3  | 0.45 | V     |

| Leakage Current                     | Zero Freq. Error, Vout = 15V                      |      | 0.1  | 1.0  | μΑ    |

| Loop Amplifier                      |                                                   |      | _    |      | -     |

| NON INV. Reference Voltage          | Percent of VREF                                   | 47   | 50   | 53   | %     |

| Input Bias Current                  | Input = 2.5V                                      | -0.8 | -0.2 |      | μΑ    |

| AVOL                                |                                                   | 60   | 75   |      | dB    |

| PSRR                                | +V <sub>IN</sub> = 8V to 15V                      | 70   | 100  |      | dB    |

| Short Circuit Current               | Source, V <sub>OUT</sub> = 0V                     | 16   | 35   |      | mA    |

|                                     | Sink, V <sub>OUT</sub> = 5V                       | 16   | 30   |      | mA    |

| Auxiliary Op-Amp                    | ·                                                 | •    |      |      |       |

| Input Offset Voltage                | V <sub>CM</sub> = 2.5V                            |      |      | 8    | mV    |

| Input Bias Current                  | V <sub>CM</sub> = 2.5V                            | -0.8 | -0.2 |      | μΑ    |

| Input Offset Current                | VcM = 2.5V                                        |      | .01  | 0.1  | μA    |

| AVOL                                |                                                   | 70   | 120  |      | dB    |

| PSRR                                | +V <sub>IN</sub> = 8V to 15V                      | 70   | 100  |      | dB    |

| CMRR                                | Vcm = 0V to 10V                                   | 70   | 100  |      | dB    |

| Short Circuit Current               | Source, Vout = 0V                                 | 16   | 35   |      | mA    |

|                                     | Sink, Vout = 5V                                   | 16   | 30   |      | mA    |

|                                     | •                                                 | -    |      | •    | •     |

Note 3: These impedence levels will vary with T<sub>J</sub> at about 1700ppm/°C

# APPLICATION AND OPERATING INFORMATION Determining the Oscillator Frequency

The frequency at the oscillator is determined by the desired RPM of the motor, the divide ratio selected, the number of poles in the motor, and the state of the double edge select pin.

fosc(Hz) = (Divide Ratio) • (Motor RPM) • (1/60 SEC/MIN) • (No. of Rotor Poles/2) • (x 2 if Pin 5 Low)

The resulting reference frequency appearing at the phase detector inputs is equal to the oscillator frequency divided by the selected divide ratio. If the double edge option is used, (Pin 5 low), the frequency of the sense amplifier input signal is doubled by responding to both the rising and falling edges of the input signal. Using this option, the loop reference frequency can be doubled for a given motor RPM.

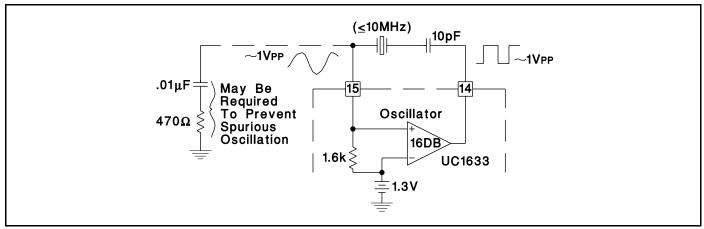

## **Recommended Oscillator Configuration Using AT Cut Quartz Crystal**

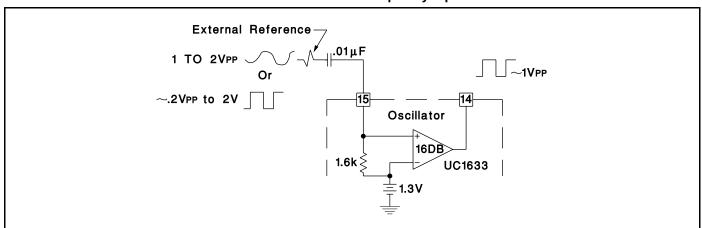

#### **External Reference Frequency Input**

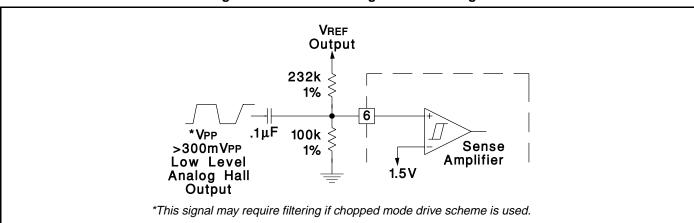

### Method for Deriving Rotation Feedback Signal from Analog Hall Effect Device

## APPLICATION AND OPERATION INFORMATION Phase Detector Operation

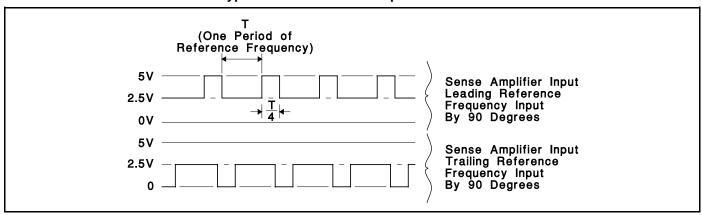

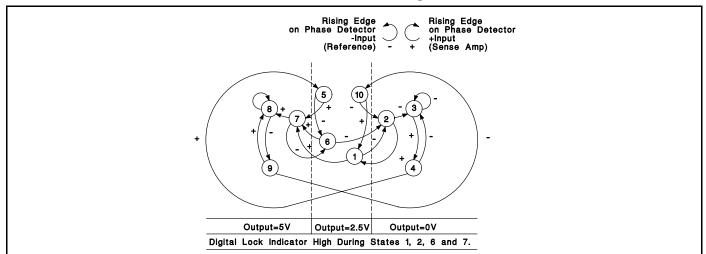

The phase detector on these devices is a digital circuit that responds to the rising edges of the detector's two inputs. The phase detector output has three states: a high, 5V state, a low, 0V state, and a middle, 2.5V state. In the high and low states the output impedance of the detector is low and the middle state output impedence is high, typically  $6.0k\Omega$ . When there is any static frequency difference between the inputs, the detector output is fixed at its high level if the +input (the sense amplifier signal) is greater in frequency, and fixed at its low level if the -input (the reference frequency signal) is greater in frequency.

When the frequencies of the two inputs to the detector are equal, the phase detector switches between its middle state and either the high or low states, depending on the relative phase of the two signals. If the +input is leading in phase then, during each period of the input frequency, the detector output will be high for a time equal to the time difference between the rising edges of the inputs, and will be at its middle level for the remainder of the period. If the phase relationship is reversed, then the detector will go low for a time proportional to the phase difference of the inputs. The resulting gain of the phase detector. kø, is

$5V/4\pi$  radians or about 0.4V/radian. The dynamic range of the detector is  $\pm 2\pi$  radians.

The operation of the phase detector is illustrated in the figures below. The upper figure shows typical voltage waveforms seen at the detector output for leading and lagging phase conditions. The lower figure is a state diagram of the phase detector logic. In this figure, the circles represent the 10 possible states of the logic, and the connecting arrows represent the transition events/paths to and from these states. Transition arrows that have a clockwise rotation are the result of a rising edge on the +input, and conversely, those with counter-clockwise rotation are tied to the rising edge of the -input signal.

The normal operational states of the logic are 6 and 7 for positive phase error, 1 and 2 for a negative phase error. States 8 and 9 occur during positive frequency error, 3 and 4 during negative frequency error. States 5 and 10 occur only as the inputs cross over from the frequency error to a normal phase error only condition. The level of the phase detector output is determined by the logic state as defined in the state diagram figure. The lock indicator output is high, off, when the detector is in states 1, 2, 6, or 7.

## **Typical Phase Detector Output Waveforms**

#### Phase Detector State Diagram

#### **APPLICATION AND OPERATION INFORMATION**

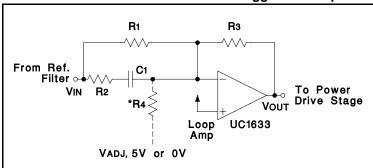

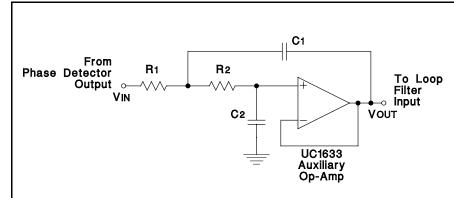

#### **Suggested Loop Filter Configuration**

\* The static phase error of the loop is easily adjusted by adding resistor, R4, as shown. To lock at zero phase error R4 is determined by:

$$R4 = \frac{2.5V \bullet R_3}{|\Delta V_{OUT}|}$$

$$\frac{V_{OUT}}{V_{IN}}(s) = \frac{R_3}{R_1} \bullet \frac{1 + \frac{s}{\omega} z}{1 + \frac{s}{\omega} p}$$

$$\omega_p = \frac{1}{R_2 C_1}$$

$$\omega_z = \frac{1}{(R_1 + R_2) C_1}$$

Where: |ΔVOUT| = |VOUT - 2.5V| and VOUT = DC Operating Voltage At Loop Amplifier Output During Phase Lock

If: (VOUT - 2.5) > 0, R4 Goes to 0V (VOUT - 2.5) < 0, R4 Goes to 5.0V

## **Reference Filter Configuration**

$$\frac{V_{OUT}}{V_{IN}}(s) = \frac{1}{1 + \frac{s \cdot 2\zeta}{\omega_{PL}} + \frac{s^2}{\omega_{PL}^2}}$$

$$\omega_N = \frac{1}{\sqrt{R_1 R_2 C_1 C_2}}$$

$$\zeta = \frac{1}{2Q} = \frac{1}{2} \sqrt{\frac{C_2}{C_1}} \frac{R_1 + R_2}{\sqrt{R_1 R_2}}$$

Note: with

$$R_1 = R_2$$

,  $\zeta = \sqrt{\frac{C_2}{C_1}}$

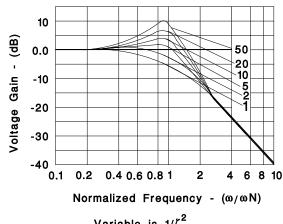

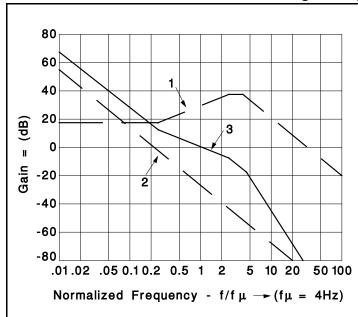

#### Reference Filter Design Aid - Gain Response

Variable is  $1/\zeta^2$ (For R1=R2,  $1/\zeta^2$ =C1/C2)

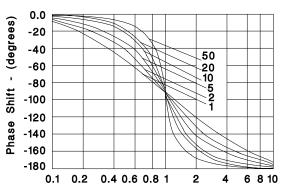

## Reference Filter Design Aid - Phase Response

Normalized Frequency - (ω/ωN)

Variable is  $1/\zeta^2$ (For R1=R2,  $1/\zeta^2$ =C1/C2)

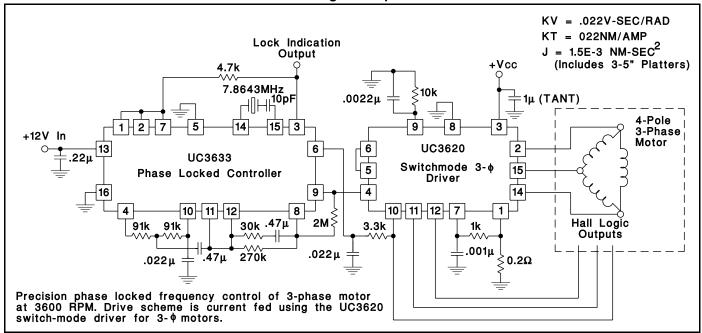

### **APPLICATION AND OPERATION INFORMATION**

#### **Design Example**

#### **Bode Plots - Design Example Open Loop Response**

- 1.) KLF(s) KRF(s)

N KΦ GPD K

- 2.\*)  $\frac{N \cdot K\phi \cdot G_{PD} \cdot K\tau}{s^2 \cdot J}$

- 3.) Combined Overall Open Loop Response

#### Where:

KLF(s) = Loop Filter Response

KRF(s) = Reference Filter Response

N = 4 (Using Double Edge Sensing With 4 Pole Motor)

$K\phi$  = Phase Detector Gain (.4V/RAD)

GPD = Power Stage Transductance (1A/V)

KT = Motor Torque Constant (.022NM/A)

J = Motor Moment of Inertia (.0015NM/A - SEC<sup>2</sup>)

$s = 2\pi i f$

\*Note: For a current mode driver the electrical time constant, LM/RM, of the motor does not enter into the small signal response. If a voltage mode drive scheme is used, then the asymptote, plotted as **2** above, can be approximated by:

$$\frac{N \bullet K \phi \bullet K p D \bullet K T}{s^2 \bullet J \bullet R M} \quad \text{if: } R M > K T \sqrt{\frac{L M}{J}} \quad \text{and, } \quad \frac{K T^2}{2 \pi \bullet J \bullet R M} < f < \frac{R M}{2 \pi \bullet L M}$$

Here: KPD = Voltage gain of Driver Stage Rм = Motor Winding Resistance Lм = Motor Winding Inductance

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated