### UNITRODE

**UC1717 UC2717** UC3717

# Stepper Motor Drive Circuit

### **FEATURES**

- Half-step and Full-step Capability

- Bipolar Constant Current Motor Drive

- Built-in Fast Recovery Schottky Commutating Diodes

- Wide Range of Current Control 5-1000mA

- Wide Voltage Range 10-45V

- Designed for Unregulated Motor Supply Voltage

- Current Levels can be Selected in Steps or Varied Continuously

- Thermal Overload Protection

### DESCRIPTION

The UC3717 has been designed to control and drive the current in one winding of a bipolar stepper motor. The circuit consists of an LS-TTL-compatible logic input, a current sensor, a monostable and an output stage with built-in protection diodes. Two UC3717s and a few external components form a complete control and drive unit for LS-TTL or micro-processor controlled stepper motor systems.

The UC1717 is characterized for operation over the full military temperature range of -55°C to +125°C, the UC2717 is characterized for -25°C to +85°C, and the UC3717 is characterized for 0°C to +70°C.

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| voltage                                     |  |

|---------------------------------------------|--|

| Logic Supply, Vcc                           |  |

| Output Supply, VM                           |  |

| Input Voltage                               |  |

| Logic Inputs (Pins 7, 8, 9) 6V              |  |

| Analog Input (Pin 10)                       |  |

| Reference Input (Pin 11) 15V                |  |

| Input Current                               |  |

| Logic Inputs (Pins 7, 8, 9)10mA             |  |

| Analog Inputs (Pins 10, 11)10mA             |  |

| Output Current (Pins 1, 15)                 |  |

| Junction Temperature, TJ+150°C              |  |

| Storage Temperature Range, Ts55°C to +150°C |  |

|                                             |  |

Note 1: All voltages are with respect to ground, Pins 4,5, 12, 13. Pin numbers refer to DIL-16 package. Currents are positive into, negative out of the specified ter-

Note 2: Consult Packaging Section of Databook for information on thermal limitations and considerations of package.

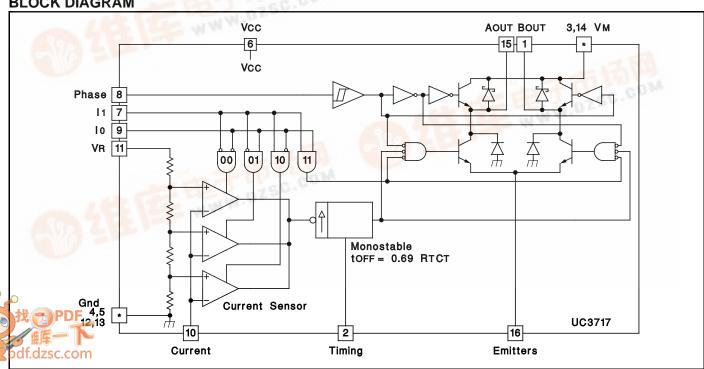

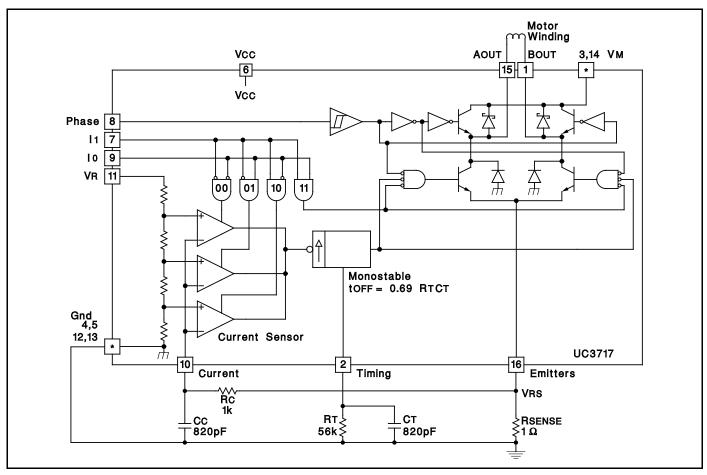

### **BLOCK DIAGRAM**

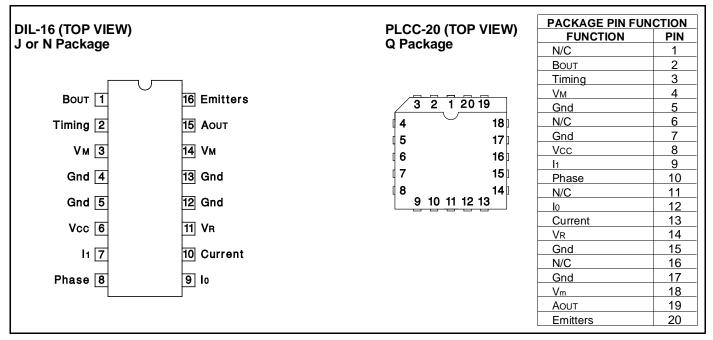

### **CONNECTION DIAGRAMS**

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                  | MIN  | TYP | MAX  | UNITS |

|----------------------------|------|-----|------|-------|

| Supply Voltage, Vcc        | 4.75 | 5   | 5.25 | V     |

| Supply Voltage, VM         | 10   |     | 40   | V     |

| Output Current. Iм         | 20   |     | 800  | mA    |

| Rise Time Logic Inputs, tR |      |     | 2    | μs    |

| Fall Time Logic Inputs, tr |      |     | 2    | μs    |

| Ambient Temperature, TA    |      |     |      |       |

| UC1717                     | -55  |     | 125  | °C    |

| UC2717                     | -25  |     | 85   | °C    |

| UC3717                     | 0    |     | 70   | °C    |

# $\textbf{ELECTRICAL CHARACTERISTICS} \quad \textbf{Unless otherwise specified, these specifications apply for $Vcc = 5V$, $TA = TJ$.}$

| PARAMETER                              | TEST CONDITIONS                                                  | MIN  | TYP | MAX  | UNITS |

|----------------------------------------|------------------------------------------------------------------|------|-----|------|-------|

| Supply Current, Icc                    |                                                                  |      |     | 25   | mA    |

| High-Level Input Voltage, Pins 7, 8, 9 |                                                                  | 2.0  |     |      | V     |

| Low-Level Input Voltage, Pins 7, 8, 9  |                                                                  |      |     | 0.8  | V     |

| High-Level Input Current, Pins 7, 8, 9 | VI = 2.4V                                                        |      |     | 20   | μΑ    |

| Low Level Input Current, Pins 7, 8, 9  | VI = 0.4V                                                        | -0.4 |     |      | mA    |

| Comparator Threshold Voltage           | IO = 0, $I1 = 0$ , $VR = 5.0V$                                   | 390  | 420 | 440  | mV    |

|                                        | Io = 1, $I1 = 0$ , $VR = 5.0V$                                   | 230  | 250 | 270  | mV    |

|                                        | IO = 0, $I1 = 1$ , $VR = 5.0V$                                   | 65   | 80  | 90   | mV    |

| Comparator Input Current               |                                                                  | -20  |     | 20   | μΑ    |

| Output Leakage Current                 | Io = 1, I1 = 1, TA = +25°C                                       |      |     | 100  | μΑ    |

| Total Saturation Voltage Drop          | IM = 500mA                                                       |      |     | 4.0  | V     |

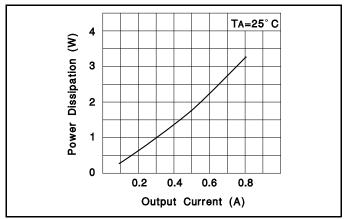

| Total Power Dissipation                | IM = 500mA, $fs = 30kHz$                                         |      | 1.4 | 2.1  | W     |

|                                        | IM = 800mA, $fs = 30kHz$                                         |      | 2.9 | 3.1  | W     |

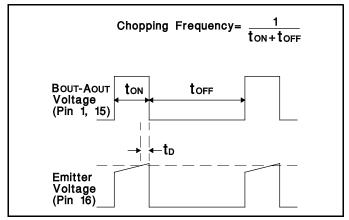

| Cut Off Time, toff                     | V <sub>M</sub> = 10V, to <sub>N</sub> ≥ 5μs (See Figure 5 and 6) | 25   | 30  | 35   | μs    |

| Turn Off Delay, to                     | T <sub>A</sub> = +25°C; dVc/dt ≥ 50mV/μs (See Figure 5 and 6)    |      | 1.6 | 2.0  | μs    |

| Thermal Shutdown Junction Temperatur   | е                                                                | +160 |     | +180 | °C    |

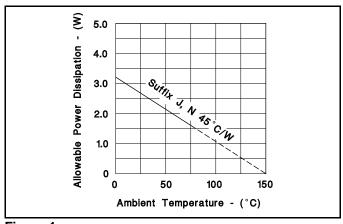

Figure 1

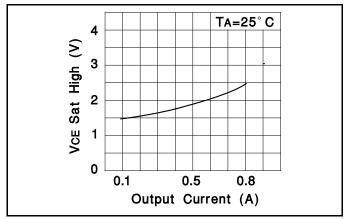

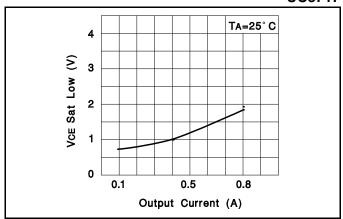

Figure 2: Typical Source Saturation Voltage vs Output Current

# **FUNCTIONAL DESCRIPTION**

The UC3717 drive circuit shown in the block diagram includes the following functions:

- (1) Phase Logic and H-Bridge Output Stage

- (2) Voltage Divider with three Comparators for current control

- (3) Two Logic inputs for Digital current level select

- (4) Monostable for off time generation

**Input Logic:** If any of the logic inputs are left open, the circuit will treat it as a high level input.

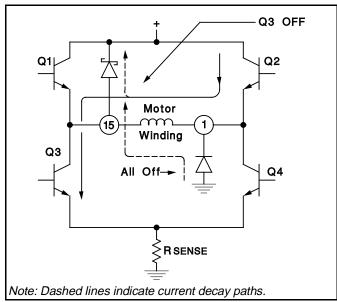

Phase Input: The phase input terminal, pin 18, controls the direction of the current through the motor winding. The Schmidt-Trigger input coupled with a fixed time delay assures noise immunity and eliminates cross conduction in the output stage during phase changes. A low level on the phase input will turn Q2 on and enable Q3 while a high level will turn Q1 on and enable Q4. (See Figure 7).

**Output Stage:** The output stage consists of four Darlington transistors and associated diodes connected in an H-Bridge configuration. The diodes are needed to provide a current path when the transistors are being switched. For fast recovery, Schottky diodes are used

Figure 3: Typical Sink Saturation Voltage vs Output Current

Figure 4: Typical Power Losses vs Output Current

Figure 5: Connections and Component Values as in Figure 6.

across the source transistors. The Schottky diodes allow the current to circulate through the winding while the sink transistors are being switched off. The diodes across the sink transistors in conjunction with the Schottkys provide the path for the decaying current during phase reversal. (See Figure 7).

| PHASE INPUT | Q1, Q4 | Q2, Q3 |

|-------------|--------|--------|

| Low         | Off    | On     |

| High        | On     | Off    |

Figure 6

| lo | <b>I</b> 1 | <b>CURRENT LEVEL</b> |

|----|------------|----------------------|

| 0  | 0          | 100%                 |

| 1  | 0          | 60%                  |

| 0  | 1          | 19%                  |

| 1  | 1          | Current Inhibit      |

Current Control: The voltage divider, comparators and monostable provide a means for current sensing and control. The two bit input (Io, I1) logic selects the desired comparator. The monostable controls the off time and therefore the magnitude of the current decrease. The time duration is determined by RT and CT connected to the timing terminal (pin 2). The reference terminal (pin 11) provides a means of continuously varying the current for situations requiring half-stepping and microstepping. The relationship between the logic input signals at pin 7 and 9 in reference to the current level is shown in Table 1. The values of the different current levels are determined by the reference voltage together with the value of the external sense resistor Rs (pin 16).

**Single-Pulse Generator:** The pulse generator is a monostable triggered on the positive going edge of the comparator. Its output is high during the pulse time and this pulse switches off the power feed to the motor wind-

ing causing the current to decay. The time is determined by the external timing components RT and CT as:

$$Toff = 0.69 RTCT$$

If a new trigger signal should occur during Toff, it is ignored.

Figure 7: Simplified Schematic of Output Stage

### **FUNCTIONAL DESCRIPTION (cont.)**

**Overload Protection:** The circuit is equipped with a thermal shutdown function, which will limit the junction temperature by reducing the output current. It should be noted however, that a short circuit of the output is not permitted.

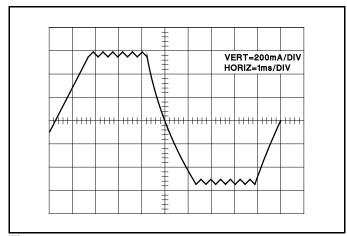

**Operation:** When the voltage is applied across the motor winding the current rises linearly and appears across the external sense resistor as an analog voltage. This voltage is fed through a low pass filter Rc, Cc to the voltage comparator (pin 10). At the moment the voltage rises beyond the comparator threshold voltage the monostable is triggered and its output turns off the sink transistors. The current then circulates through the source transistor and the appropriate Schottky diode. After the one shot has timed out, the sink transistsor is turned on again and the procedure repeated until a current reverse command is given. By reversing the logic level of the phase input (pin 8), both active transistors are being turned off and the opposite pair turned on. When this happens the current must first decay to zero before it can reverse. The current path then provided is through the two diodes and the power-supply. Refer to Figure 7. It should be noted at this time that the slope of the current decay is steeper, and this is due to the higher voltage build up across the winding. For better speed performance of the stepping motor at half step mode, the phase logic level should be changed at the same time the current inhibit is applied. A typical current wave form is shown in Figure 8.

Figure 8

### **APPLICATIONS**

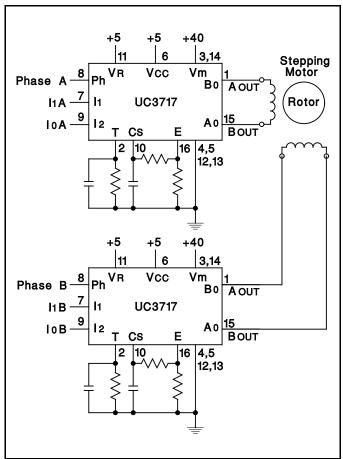

A typical chopper drive for a two phase bipolar permanent magnet or hybrid stepping motor is shown in Figure 9. The input can be controlled by a microprocessor, TTL, LS or CMOS logic.

Figure 9

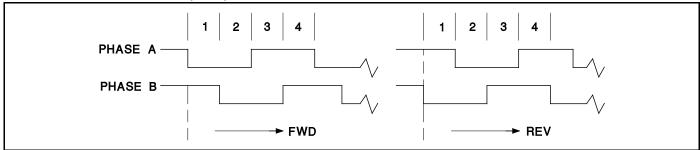

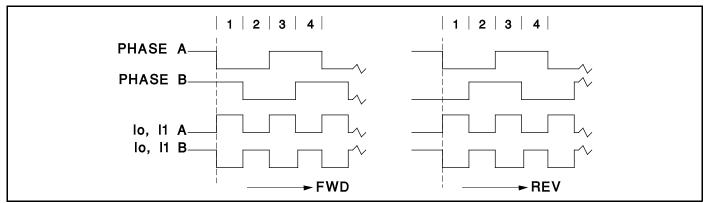

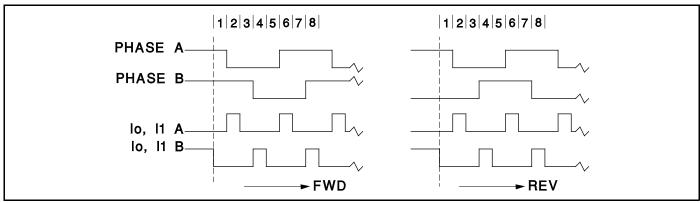

The timing diagram in Figure 10 shows the required signal input for a two phase, full step, stepping sequence. Figure 11 shows a one phase, full step, stepping sequence, commonly referred to as wave drive. Figure 12 shows the required input signal for a one phase-two phase stepping sequence called half-stepping.

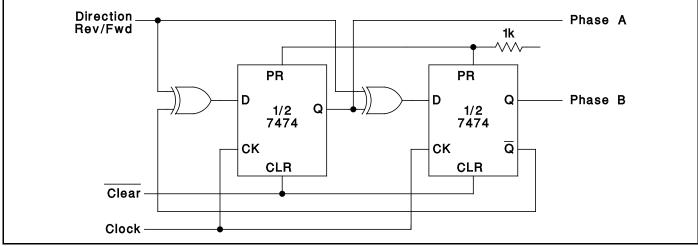

The circuit of Figure 13 provides the signal shown in Figure 10, and in conjunction with the circuit shown in Figure 9, will implement a pulse-to-step two phase, full step, bidirectional motor drive.

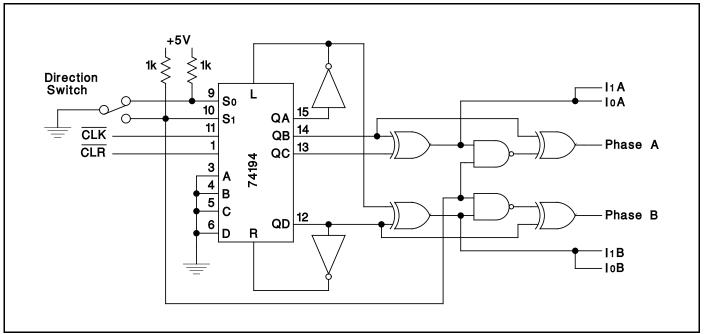

The schematic of Figure 14 shows a pulse to half step circuit generating the signal shown in Figure 12. Care has been taken to change the phase signal the same time the current inhibit is applied. This will allow the current to decay faster and therefore enhance the motor performance at higher step rates.

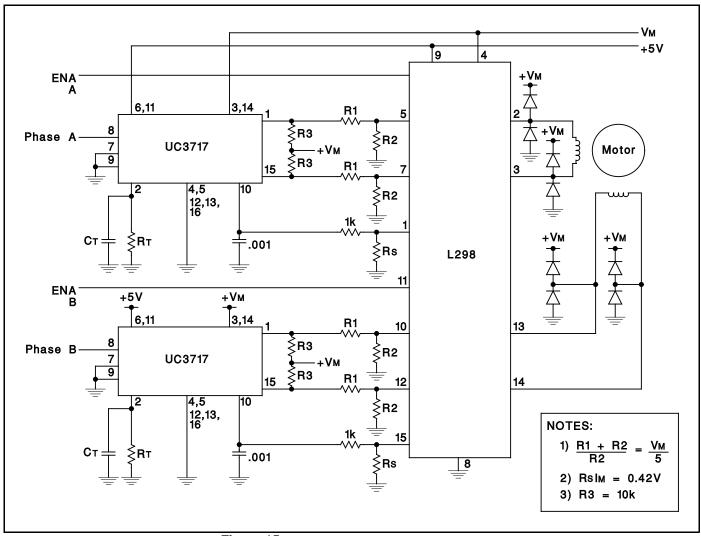

Using the UC3717 to drive the L298 provides a uniquely packaged state-of-the-art high power stepper motor control and drive. See Figure 15.

# **FUNCTIONAL DESCRIPTION (cont.)**

Figure 10: Phase Input Signal for Two Phase Full Step Drive (4 Step Sequence)

Figure 11: Phase and Current-Inhibit Signal for Wave Drive (4 Step Sequence)

Figure 12: Phase and Current-Inhibit Signal for Half Stepping (8 Step Sequence)

Figure 13: Full Step Bidirectional Two Phase Drive Logic

Figure 14: Half-Step, Bidirectional Drive Logic

### **CONSIDERATION**

**Half-Stepping:** In the half step sequence the power input to the motor alternates between one or two phases being energized. In a two phase motor the electrical phase shift between the windings is 90 degrees. The torque developed is the vector sum of the two windings energized. Therefore when only one winding is energized the torque of the motor is reduced by approximately 30%. This causes a torque ripple and if it is necessary to compensate for this, the  $V_R$  input can be used to boost the current of the single energized winding.

Ramping: Every drive system has inertia and must be considered in the drive scheme. The rotor and load inertia plays a big role at higher speeds. Unlike the DC motor the stepping motor is a synchronous motor and does not change its speed due to load variations. Examining typical stepping motors, torque vs. speed curves indicates a sharp torque drop off for the start-stop without error curve, even with a constant current drive. The reason for this is that the torque requirements increase by the square of the speed change, and the power need increases by the cube of the speed change. As it can be seen, for good motor performance controlled acceleration and deceleration should be considered.

**Iron Core Losses:** Some motors, especially the Tin-Can type, exhibit high iron losses mostly due to eddy currents

which rise in an exponential manner as the frequency or step rate is increased. The power losses can not be calculated by I<sup>2</sup>R where I is the chopping current level and R the DC resistance of the coil. Actual measurements indicate the effective resistance may be many times larger. Therefore, for 100% duty cycle the current must be limited to a value which will not overheat the motor. This may not be necessary for lower duty cycle operation.

Interference: Electrical noise generated by the chopping action can cause interference problems, particularly in the vicinity of magnetic storage media. With this in mind, printed circuit layouts, wire runs and decoupling must be considered. 0.01 to 0.1  $\mu F$  ceramic capacitors for high frequency bypass located near the drive package across V+ and ground might be very helpful. The connection and ground leads of the current sensing components should be kept as short as possible.

### **Ordering Information**

UNITRODE TYPE NUMBER UC3717N - 16 Pin Dual-in-line (DIL) "Bat Wing" Package UC1717J - 16 Pin Dual-in-line Ceramic Package

UC1717SP - 16 Pin Dual-in-line Hermetic Power Package

Figure 15: UC3717 with L298 Power Amplifier

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated