# Unitrode Products from Texas Instruments

# UCC2961, UCC3961 ADVANCED PRIMARY-SIDE STARTUP CONTROLLER

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

- Operates with Secondary–Side PWM Control

- Isolated PWM Command through a Pulse Transformer

- Initial Free-Running Soft-Startup with Duty-Cycle Clamping

- Up to 400-kHz Synchronizable Switching Frequency

- High-Current FET Drive (1.5-A Sink, 0.75-A Source)

Multi-Mode Overcurrent Protection with Restart, Latching, or Cycle-by-Cycle Current Limiting

- Programmable Volt-Second Clamp for Transformer Reset

- Undervoltage Lockout with 2-V Hysteresis

- Low-Current Startup with Optional Disconnect

- Programmable Overvoltage and Undervoltage Protection

- 8-pin Version Also Available (UCC3960)

UDG-99039

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2000, Texas Instruments Incorporated

#### SLUS431A - MAY 2000 - REVISED DECEMBER 2000

### description

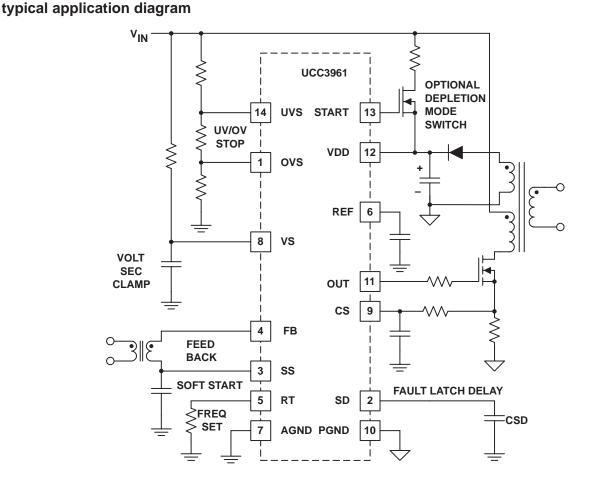

The UCC3961 advanced primary-side startup controller is a unique solution that provides all the primary-side functions required for a single-ended, isolated, switch-mode power converter incorporating secondary-side PWM control. It is usable with a wide range of secondary control circuits and is especially well suited for systems where sophisticated handling of overload conditions is required.

Secondary-side control assumes that output voltage and current measurements are interfaced directly to an output ground-referenced PWM stage that develops the power switch command for the supply. This digital PWM command can then be transmitted to the primary-side power switch through a simple and low-cost isolating pulse transformer. With secondary-side control, it is much easier to monitor and control the system load with tightly coupled analog control loops. Load-oriented features such as output current sharing and synchronous rectification are implemented more easily.

The UCC3961 provides all the circuitry required on the primary side of a secondary-side controlled power supply. It features a free running 60-kHz to 360-kHz oscillator which is synchronizable to the secondary-side PWM signal and also has the ability to accept start/stop PWM commands from the isolating pulse-edge transformer (PET). The use of an extremely small and low-cost pulse transformer allows for higher converter bandwidth. This also eliminates the loop-gain variations due to initial accuracy and aging of an opto-coupler feedback element or the size penalty of a gate transformer. It also includes an undervoltage lockout circuit with 2-V hysteresis, a low-current startup with active low during UVLO, a soft-start capability, a 5-V reference and a high-current power output.

Advanced features of UCC3961 allows implementation of initial startup with optional high-voltage disconnect after starting, and input voltage monitoring with turnoff for either undervoltage or overvoltage conditions. Other features include power-switch current protection, pulse-by-pulse current limiting, shutdown after a programmable delay and continuous input volt\*second clamp. The UCC3961 also provides a multi purpose, bidirectional shutdown pin (SD), that can be used in conjunction with the devices on the START pin, to modify the converters behavior in overload conditions. The possible configurations include continuous-peak current limiting, delayed or immediate shutdown with full cycle soft restart or fully latched overcurrent shutdown.

In a non-typical use, the UCC3961 can accommodate an analog feedback signal through an opto-isolator where the UCC3961 then can operate in voltage-mode control mode with primary-side peak current limiting.

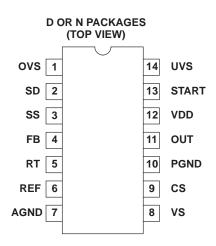

The UCC3961 and the UCC2961 are available in the 14-pin SOIC (D) and PDIP (P) packages. For applications where only startup and control are desired, a simplified version of this product is offered in an 8-pin package as the UCC2960 and UCC3960.

|               | PACKAGEI                        | DEVICES                       |

|---------------|---------------------------------|-------------------------------|

| ТА            | SOIC-14<br>SMALL OUTLINE<br>(D) | PDIP–14<br>PLASTIC DIP<br>(N) |

| –40°C to 85°C | UCC2961D                        | UCC2961N                      |

| 0°C to 70°C   | UCC3961D                        | UCC3961N                      |

**AVAILABLE OPTIONS**

<sup>†</sup> The SOIC (D) packages are available taped and reeled. Add an R suffix to the device type (e.g., UCC2961DR) to order quantities of 2500 devices per reel.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†‡</sup>

| Input voltage, $V_{I(VDD)}$<br>Input current, $I_{I(VDD)}$<br>Output current §, I <sub>O</sub> |                     |

|------------------------------------------------------------------------------------------------|---------------------|

| Input current, I <sub>I(VDD)</sub>                                                             |                     |

| Output current <sup>§</sup> , I <sub>O</sub> <sup>′</sup>                                      | –1.5 A / 2 A        |

| Output voltage: REF, START                                                                     | –0.3 V to VDD+0.3 V |

| Input voltage: OVS, SD, SS, RT, VS, CS, UVS                                                    | –0.3 V to VDD+0.3 V |

| FB                                                                                             | –7.0 V to VDD+0.3 V |

| Operating junction temperature range, T <sub>J</sub>                                           | –55°C to 150°C      |

| Storage temperature range, T <sub>stg</sub>                                                    | –65°C to 150°C      |

| Lead temperature soldering 1,6 mm (1/16 inch) from case for 10 seconds                         | 300°C               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> Unless otherwise indicated, voltages are reference to ground and currents are positive into and negative out of the specified terminals. Pulsed is defined as a less than 10% duty cycle with a maximum duration of 500 μs. All voltages are with respect to ground unless otherwise stated. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the *Power Supply Control Data Book (TI Literature Number SLUD003)* for thermal limitations and considerations of packages.

$\S 4nF$  load with 4- $\Omega$  series resistor.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

electrical characteristics V<sub>DD</sub> = 12 V, RT = 53.3 k $\Omega$ , C<sub>VDD</sub> = 1  $\mu$ F, C<sub>REF</sub> = 0.1  $\mu$ F, C<sub>SS</sub> = 0.01  $\mu$ F, R<sub>OUT</sub> = 4  $\Omega$ , C<sub>OUT</sub> = 1 nF and T<sub>A</sub> = T<sub>J</sub> (unless otherwise stated)

### supply section (VDD)

| PARAMETER         | TEST CONDITIONS          | MIN | TYP  | MAX | UNITS |

|-------------------|--------------------------|-----|------|-----|-------|

| Clamp voltage     | I <sub>VDD</sub> = 10 mA | 16  | 17.5 | 19  | V     |

| Operating current | No load, $C_{OUT} = 0$   | 1.8 | 2.3  | 2.8 | mA    |

| Starting current  | VDD = 9 V                | 100 | 150  | 200 | μΑ    |

#### undervoltage lockout section

| PARAMETER               | TEST CONDITIONS | MIN | TYP | MAX  | UNITS |

|-------------------------|-----------------|-----|-----|------|-------|

| Start threshold voltage |                 | 9.5 | 10  | 10.5 | V     |

| Hysteresis voltage      |                 | 1.7 | 2   | 2.3  | V     |

### voltage reference section (REF)

| PARAMETER               | TEST CONDITIONS                                  | MIN  | TYP | MAX  | UNITS |

|-------------------------|--------------------------------------------------|------|-----|------|-------|

| Reference voltage       |                                                  | 4.75 | 5.0 | 5.25 | V     |

| Load regulation voltage | $I_{REF} = 0 \text{ mA to } -2.5 \text{ mA}$     |      | 3   | 5    | mV    |

| Line regulation voltage | $V_{DD} = 10 \text{ V} \text{ to } 12 \text{ V}$ |      | 1   | 5    | mV    |

| Short-circuit current   |                                                  | 8    | 10  | 16   | mA    |

#### overvoltage sense section (OVS)

| PARAMETER          | TEST CONDITIONS | MIN  | TYP | MAX  | UNITS |

|--------------------|-----------------|------|-----|------|-------|

| Threshold voltage  |                 | 3.68 | 4   | 4.32 | V     |

| Input bias current |                 |      |     | 0.2  | μΑ    |

#### undervoltage sense section (UVS)

| PARAMETER          | TEST CONDITIONS | MIN  | TYP | MAX  | UNITS |

|--------------------|-----------------|------|-----|------|-------|

| Threshold voltage  |                 | 3.68 | 4   | 4.32 | V     |

| Input bias current |                 |      |     | 0.2  | μA    |

#### soft start section (SS)

| PARAMETER             | TEST CONDITIONS         | MIN | TYP | MAX  | UNITS |

|-----------------------|-------------------------|-----|-----|------|-------|

| Discharge current     | SD = 4.5 V pulsed       | 3   | 5   | 7    | μΑ    |

| Charge current        | SD = 4.5 V pulsed       | -5  | -7  | -10  | μΑ    |

| Low-threshold voltage |                         | 0.9 | 1   | 1.1  | V     |

| Clamp threshold       |                         | 4.5 | 5   | 5.5  | V     |

| On resistance         | V <sub>DD</sub> = 7.5 V | 600 | 800 | 1000 | Ω     |

### shutdown section (SD)

| PARAMETER         | TEST CONDITIONS         | MIN  | TYP | MAX  | UNITS |

|-------------------|-------------------------|------|-----|------|-------|

| Threshold voltage |                         | 3.68 | 4   | 4.32 | V     |

| Discharge current |                         | 0.4  | 0.6 | 0.8  | μΑ    |

| Charge current    |                         | -4   | -6  | -8   | μΑ    |

| On resistance     | V <sub>DD</sub> = 7.5 V | 2.5  | 3.3 | 5    | kΩ    |

NOTES: 1. OUT Low, nominal of 0.7 V reflects the 3  $\Omega$  DMOS ON resistance plus 4  $\Omega$  RSERIES.

2. OUT High (VDD-OUT), nominal of 0.56 V reflects the 10W HVPMOS ON resistance plus 4W RSERIES.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# electrical characteristics V<sub>DD</sub> = 12 V, RT = 53.3 k $\Omega$ , C<sub>VDD</sub> = 1 $\mu$ F, C<sub>REF</sub> = 0.1 $\mu$ F, C<sub>SS</sub> = 0.01 $\mu$ F, R<sub>OUT</sub> = 4 $\Omega$ , C<sub>OUT</sub> = 1 nF and T<sub>A</sub> = T<sub>J</sub> (unless otherwise stated) (continued)

# current sense section (CS)

| PARAMETER            | TEST CONDITIONS   | MIN | TYP | MAX  | UNITS |

|----------------------|-------------------|-----|-----|------|-------|

| Threshold            | Pulse-by-pulse    | 0.9 | 1   | 1.1  | V     |

|                      | Immediate         | 1.3 | 1.4 | 1.5  | V     |

| Input bias           | CS = 1.1 V pulsed |     |     | 0.2  | μΑ    |

| Delay time CS to OUT |                   | 60  | 100 | 140  | ns    |

| On resistance        |                   | 600 | 800 | 1000 | Ω     |

#### oscillator section

| PARAMETER                     | TEST CONDITIONS                                  | MIN | TYP  | MAX | UNITS |

|-------------------------------|--------------------------------------------------|-----|------|-----|-------|

| Frequency                     |                                                  | 135 | 150  | 165 | kHz   |

| Frequency change with voltage | $V_{DD} = 10 \text{ V} \text{ to } 12 \text{ V}$ |     | 0.02 | 0.2 | %/V   |

| Minimum duty cycle            |                                                  |     | 0%   |     |       |

| Maximum duty cycle            |                                                  | 69% | 72%  | 75% |       |

### volt-second section (VS)

| PARAMETER     | TEST CONDITIONS | MIN  | TYP | MAX  | UNITS |

|---------------|-----------------|------|-----|------|-------|

| Threshold     |                 | 3.68 | 4   | 4.32 | V     |

| Input bias    |                 |      |     | 0.2  | μΑ    |

| On resistance |                 | 600  | 800 | 1000 | Ω     |

### output section (OUT)

| PARAMETER                            | TEST CO                         | TEST CONDITIONS         |  |      | MAX | UNITS |

|--------------------------------------|---------------------------------|-------------------------|--|------|-----|-------|

| Low-level output voltage             | I <sub>OUT</sub> = 100 mA (dc)  | See Note 1              |  | 0.7  | 1.0 | V     |

| High-level output voltage            | $I_{OUT} = -40 \text{ mA} (dc)$ | See Note 2              |  | 0.56 | 1.0 | V     |

| Low-level output voltage during UVLO | I <sub>OUT</sub> = 20 mA (dc),  | V <sub>DD</sub> = 7.5 V |  |      | 1.5 | V     |

| Rise time                            |                                 |                         |  | 30   | 60  | ns    |

| Fall time                            |                                 |                         |  | 15   | 30  | ns    |

### bias regulator section (START)

| PARAMETER        | TEST CONDITIONS                             | MIN  | TYP  | MAX  | UNITS |

|------------------|---------------------------------------------|------|------|------|-------|

| Bias regulator   | $V_{DD} - START = 0.5 V$                    | 11.7 | 12.1 | 12.5 | V     |

| Override voltage | V <sub>DD</sub> – START = 1.0 V, See Note 3 |      | 12.2 |      | V     |

### feedback section (FB)

| PARAMETER                              | TEST CO             | NDITIONS | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|---------------------|----------|------|------|------|-------|

| input bias current                     | FB = 4.5 V,         | SS = 0 V |      |      | 0.4  | μΑ    |

| Negative compliance voltage            | IFB = -100 mA,      | SS = 0 V | -6.8 | -7.2 | -7.6 | V     |

| Delay time, FB–SS to OUT, rising edge  | FB–SS Pulsed = 2 V, | FB = SS  | 40   | 70   | 100  | ns    |

| Delay time, FB–SS to OUT, falling edge | FB–SS Pulsed = 2 V, | FB = SS  | 50   | 85   | 120  | ns    |

NOTES: 1. OUT Low, nominal of 0.7 V reflects the 3  $\Omega$  DMOS ON resistance plus 4  $\Omega$  R<sub>SERIES</sub>.

2. OUT High (VDD–OUT), nominal of 0.56 V reflects the 10  $\Omega$  HVPMOS ON resistance plus 4  $\Omega$  R<sub>SERIES</sub>.

3. The override V<sub>DD</sub> voltage for shutting off the bias regulation is 100 mV higher than the bias regulator voltage.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

| TERMINAL |     |     | DECODIDEION                                                                                                                                                                                                                                                                                                                           |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

| AGND     | 7   |     | This pin is the reference point for grounding all analog functions and must be kept as clean as possible from all switching noise. It should be connected to PGND in only one location as close to the IC as practical.                                                                                                               |

| CS       | 9   | I   | Pulse-by-pulse and shutdown overcurrent sense input pin                                                                                                                                                                                                                                                                               |

| FB       | 4   | I   | Control input for the signal from a secondary-side PWM controller                                                                                                                                                                                                                                                                     |

| OUT      | 11  | 0   | Drive pin for the MOSFET power switch                                                                                                                                                                                                                                                                                                 |

| OVS      | 1   | I   | This pin is used with an external resistor divider of VIN to terminate operation if a voltage is sensed above the internal 4 V threshold. Activation sets the shutdown latch that requires recycling the voltage on VDD to restart.                                                                                                   |

| PGND     | 10  |     | This power ground for the PWM output stage conducts any current transients from the power switch gate drive. It should be closely bypassed to VDD and connected to AGND in only one location as close to the IC as possible.                                                                                                          |

| REF      | 6   | 0   | This is a 5-V output usable with external loads of up to 10 mA. This voltage is also the source for all internal analog threshold settings and should be bypassed with a minimum of $0.1$ - $\mu$ F capacitance to AGND.                                                                                                              |

| RT       | 5   | I   | Sets the free-running startup oscillator frequency                                                                                                                                                                                                                                                                                    |

| SD       | 2   | I   | Input to the shutdown circuit                                                                                                                                                                                                                                                                                                         |

| SS       | 3   | I   | The pin implements the primary-side soft-start function. This is the connection point for an external capacitor that determines the rate of increase in commanded pulse width for the power switch at startup. It also serves as the ac ground return for the feedback pulse transformer to provide a tracking bias for the FB input. |

| START    | 13  | 0   | Used to develop a regulated 12 V at VDD and thereby minimize or eliminate continuous current drain                                                                                                                                                                                                                                    |

| UVS      | 14  | I   | This pin is used with an external resistor divider of Vin to terminate operation if a voltage is sensed below the internal 4-V threshold. Activation maintains the circuit in shutdown with the soft-start capacitor clamped low.                                                                                                     |

| VDD      | 12  | I   | Power input connection for all control circuitry                                                                                                                                                                                                                                                                                      |

| VS       | 8   | I   | Volt-second clamp                                                                                                                                                                                                                                                                                                                     |

# **Terminal Functions**

# detailed descriptions

# current sense (CS)

This is the pulse-by-pulse and shutdown overcurrent sense input pin. This current-sense pin triggers a pulse-by-pulse termination anytime a 1.0-V threshold is exceeded while a signal in excess of 1.375 V on this pin initiates a complete shutdown. Each activation of pulse-by-pulse termination also sends a current pulse to the SD pin where an external capacitor can be used to provide a delayed shutdown. Since the CS pin can be noise sensitive, it is good practice to insert a small low-pass RC filter between this pin and the current sensor.

# feedback (FB)

This is the control input for the signal from a secondary-side PWM controller whose pulse-width command has been differentiated by the feedback pulse-edge transformer into positive *start* and negative *stop* pulses. These signals are used to turn on and turn off the primary power switch and must have an amplitude of at least  $V_{SS} \pm 2.0V$  (4 V peak-to-peak) for at least 25 ns per pulse and no more than 200 ns per pulse. The maximum amplitude allowed on this pin is  $V_{SS} \pm 7.0$  V.

# output drive (OUT)

This is the drive pin for the MOSFET power switch and sinks (1.5 A) and sources (0.75 A) fast, high-current gate-drive pulses. During shutdown, this pin is self–biased to an active low state. A minimum of 4 W should be added in series with the output to ensure that the on-chip driver safe operating area is not exceeded. (Data from the IRF820/830/840 family of MOSFETs, commonly available in the TO–220 package, is used to derive this value. The gate charge needed to provide full enhancement was used to establish an equivalent capacitance of up to 4000 pF.)

### timing resistor (RT)

A resistor from this pin to AGND establishes a current,

$$I_{\text{SET}} = \frac{2 \text{ V}}{\text{RT}}$$

that is mirrored internally for several functions. It establishes the free-running startup switching frequency with an internal capacitor according to the relationship,

$$fs = \frac{8.0 \times 10^9}{RT}$$

The startup oscillator has a rise and fall time set to limit the duty-cycle of the power switch to a maximum of 72%, a limit that is maintained even after the feedback signal takes command. The range of RT is 22.2 k $\Omega$  to 133 k $\Omega$ , giving a free-run frequency range range of 60 kHz to 360 kHz, respectively. Variations in the free-running oscillator frequency overtemperature are very small. The typical temperature coefficient is –40 Hz per degree Celsius, measured at 150 kHz.

### shutdown (SD)

This pin is the input to the shutdown circuit. Like OVS, this pin also sets the shutdown latch when a threshold above 4 V is exceeded. The primary intent of this input is to allow the use of an external capacitor to program a delay between the onset of current limiting and the issuance of a shutdown command by integrating current pulses that appear on this pin with each activation of the CS input. This pin is pulled low with a current sink of 0.33/RT when there is no CS signal. The shutdown function can be disabled by connecting SD pin to AGND.

### soft-start (SS)

The pin implements the primary-side soft-start function. This is the connection point for an external capacitor that determines the rate of increase in commanded pulse width for the power switch at startup. It also serves as the ac ground return for the feedback pulse transformer to provide a tracking bias for the FB input.

### start bias regulator (START)

In conjunction with an external depletion-mode N-channel FET, such as the Supertex DN2530, this pin can be used to develop a regulated voltage of 12 V at VDD and thereby minimize or eliminate continuous current drain when starting from a variable high voltage source. If this function is unused, this pin can be left open.

### power (VDD)

This is the power input connection for all the control circuitry and, in addition, conducts all the gate charge current for the power FET. It should be closely bypassed with at least  $1.0-\mu$ F to PGND and  $1.0-\mu$ F to AGND. This pin is internally shunt regulated to clamp at 17.5V to protect the internal components so if a voltage source above this value is possible, external current limiting must be provided.

### volt-second clamp (VS)

This pin provides a volt–second clamp for the operation of the transformer–driving power switch with the aid of an external capacitor to ground and a high value resistor to the transformer's voltage source (Vin). With the initiation of each power pulse, the circuit releases an internal grounding clamp across the capacitor allowing it to charge with a current from the resistor proportional to the input voltage. If this pin reaches 4 V prior to output termination from other control functions, then this ends the power pulse.

$$T_{VS} = 1.61 \times R_{VS} \times C_{VS}$$

$$R_{VS} > 100 \,\Omega$$

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# pin descriptions (continued)

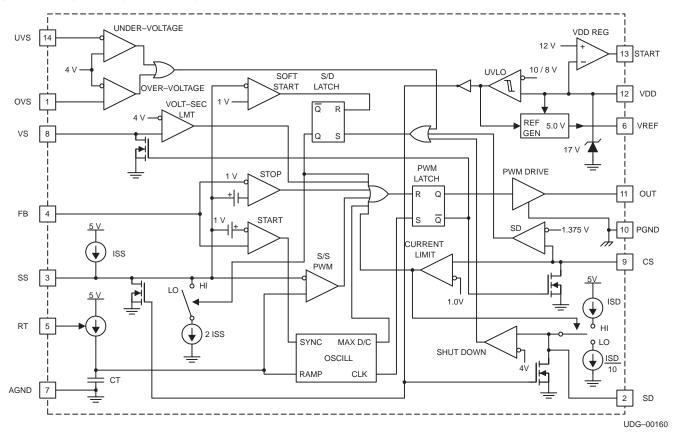

Figure 1. Block Diagram

# DETAILED DESCRIPTION

# start-up oscillator

The RT pin is connected to an internal 2.0 V nominal, unity-gain closed-loop amplifier that is referenced to a voltage divider off the 5.0-V reference. When a 22.2-k $\Omega$  resistor is connected from the RT pin to GND an approximate  $I_{RT} = 90\mu$ A internal current is realized that charges the internal oscillator capacitor that is approximately 58 pF.  $I_{RT} = 90\mu$ A produces a maximum free running oscillator frequency of 360 KHz at a 72% duty cycle. When a 133.3-k $\Omega$  resistor is connected from the RT pin to GND an approximate  $I_{RT} = 15$  mA internal current is realized that produces a minimum free running oscillator frequency of 60 KHz at approximately 72% duty cycle. This maximum duty cycle is setup by on-chip MOSFET current mirrors that are not programmable.

Any frequency between these two limits (6:1 maximum to minimum frequency) is obtainable by linearly scaling the RT resistance between the minimum 22.2-k $\Omega$  and maximum 133.3-k $\Omega$  values. The secondary-side PWM frequency should be fixed at (1 / 0.9) or 1.11 times the user programmed primary-side free running oscillator frequency for proper primary-side synchronization. Therefore, in all cases the recommended secondary-side synchronization frequency shall be 1.11 times higher than the selected primary-side free running startup frequency. Taking into consideration the two extreme limits for primary-side free running startup frequency, the secondary-side operating frequency should be set between 400 kHz and 67 kHz.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# DETAILED DESCRIPTION

### soft start

The soft-start section contains all the circuitry required to produce a user programmable slowly increasing PWM duty cycle, starting from 0% to a maximum of 72%. The soft-start cycle is triggered either by the initial primary-side startup procedure or after any one of three user-programmable fault conditions and one fixed-fault condition. The PWM duty cycle increases according to the charge rate of an user selectable external soft-start capacitor, connected from the SS pin to GND. The SS capacitor is charged by a nominal 7- $\mu$ A internal current source.

Voltage comparators referenced to a 4.0-V threshold monitor the OVS pin, SD pin and the UVS pin and trigger a soft-start cycle when a fault condition is detected on any of these pins. Should the CS pin rise in voltage above 1.375 V a soft-start cycle is also triggered. The soft-start cycle disables the output driver OUT and holds it in the low state until the capacitor connected from the SS pin to GND is discharged below 1.0 V by an internal  $5-\mu$ A current sink. After this discharge period the PMW output OUT is enabled and the duty cycle is allowed to slowly increase as before.

### synchronization

The SS pin and the FB pin accept the secondary side of a small-signal synchronization transformer. A series-blocking capacitor inserted in the primary-side of the synchronization transformer is intended to differentiate the square-wave gate drive output of the secondary-side PWM controller while preventing the transformer from saturation. The SS capacitor also provides an ac GND at the SS pin or the synchronization transformer secondary. The small signal synchronization transformer provides galvanic isolation between primary and secondary side and must have adequate voltage breakdown rating between the primary and secondary windings.

Two comparators, with an approximate 1.0-V offset each, are connected to the FB pin to provide plus and minus differential voltage comparison with a 2.0-V deadband between the FB and SS pins. The 2.0-V deadband prevents inductive backswing of the small signal transformer from giving false secondary-side pulse-edge detection.

Enough energy must be coupled into the comparator differential inputs to ensure reliable comparator switching. This requires sufficient voltage overdrive above the 1.0-V comparator threshold and a specified transformer circuit time constant to provide a minimum synchronization pulse width.

On receiving the first recognizable negative going voltage pulse (turnoff command) generated from the falling edge of the differentiated square-wave gate drive signal on the secondary-side, the PWM latch is reset and a synchronization latch is set. After this event all primary-side PMW driver output is slaved to the secondary-side driver output in both frequency and duty cycle. The triggering of a soft-start cycle by a fault condition resets the synchronization latch to again allow the internal startup oscillator to control the PWM latch.

### pulse-width modulation

The PWM section consists of a reset dominant SR latch with necessary logical gating on the SET input to allow control from the free running startup oscillator until feedback from the secondary-side PWM gate drive output is detected. After the occurrence of detectable feedback from the secondary-side gate driver, the control of the primary-side PWM latch is handed off to the secondary-side PWM controller. A nine-input OR gate on the PWM latch reset dominant input allows the numerous fault conditions to reset the PWM latch and control from either the startup oscillator or feedback from the secondary-side PWM output driver.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# DETAILED DESCRIPTION

### undervoltage lockout

The undervoltage lockout (UVLO) circuit enables normal operation after VDD exceeds the 10.0-V turnon threshold and permits operation until VDD falls below the 8-V turnoff threshold. While activated, the UVLO circuit holds the PWM gate driver output (OUT) and the internal-reference buffer amplifier output REF low. To ensure proper soft-start and to prevent false SD detection, internal N-channel MOSFET switches discharge external capacitors connected to the SS and SD pins during undervoltage conditions.

# voltage reference

The 5-V internal reference is connected to the REF pin and must be bypassed using a good quality, high-frequency capacitor. This 5-V reference is not available externally while the chip is disabled by the undervoltage lockout circuit.

### current sensing

The current sense (CS) circuit monitors the voltage across a ground referenced current sense resistor, connected between the source of the external power MOSFET and GND. The signal amplitude at the CS pin is compared to two thresholds (1.0 V, and 1.375 V respectively) by two independent voltage comparators.

A voltage level greater than 1.0 V, but less than 1.375 V, sets the reset dominant shutdown latch and resets the PWM latch. The SD latch is reset by the startup oscillator arriving at its 4.0 V compare threshold. When the SD latch is set, a scaled current,  $I_{SD} = -(1/6) \times (I_{RT})$ , charges an user-selected external capacitor connected between the SD pin and GND. When the SD latch is reset, a scaled current  $I_{SD} = (1/10)^*(1/6) \times (I_{RT})$ , discharges the user-selected capacitor connected between the SD pin and GND.

A current-sense voltage greater than 1.375 V immediately triggers a SD event and also reset the PWM latch. During the off period of the PWM latch, any capacitance connected to the CS pin is discharged to GND potential by an internal  $800-\Omega$  device.

# volt-second clamp

The volt-second (VS) clamp circuit monitors the voltage at the VS pin produced by an external-series RC circuit. The resistor is connected from the HV primary-side power input, that is derived from the rectified line voltage, to the VS pin. The capacitor is from the VS pin to GND and being charged by the resistor during the on-time of the OUT driver. The resulting exponential voltage at the VS pin is monitored by a voltage comparator with a 4.0-V threshold. Should the voltage at the VS pin exceed 4.0-V, the PWM latch is reset, and as a result the output drive signal is terminated. This RC circuit can be tailored to prevent the power transformer from saturation by effectively limiting the applied maximum volt-second product across the primary winding. During the off period of the PWM output driver the VS capacitor is discharged to GND potential by an internal switch with  $800\Omega$  on resistance.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# DETAILED DESCRIPTION

### start regulator and VDD clamp

To facilitate the primary-side startup, a  $V_{DD} = 12V$  voltage regulator may be implemented by using an external depletion-mode FET. The gate of this device is then connected to the START pin, the source terminal is attached to the VDD pin, and the drain is tied to the HV primary-side power input that is derived from the rectified line voltage. An auxiliary bootstrap winding off the main power transformer can be used to generate a bias voltage greater than 12 V, that effectively shuts down the 12-V regulator and increase the efficiency of the biasing solution during normal operation.

To ensure that the absolute-maximum voltage ratings of internal devices are not violated, an internal-shunt voltage regulator is provided to clamp the VDD pin at a nominal 17.5-V maximum voltage. Similarly to other shunt or Zener-like voltage regulator circuits, the current through the internal VDD clamp must be limited below the maximum current level indicated in the datasheet. In addition to limiting the current through the clamp circuit, the maximum power dissipation capability of the particular package used in the application must be considered.

### **OUT driver**

An internal output driver (OUT) is provided to drive the gate of an external N–channel power MOSFET. The output driver consists of a nominal 4.0-W ON-resistance P-channel MOSFET for turn-on, and a nominal 2.0- $\Omega$  ON resistance DMOS FET utilized during the turn–off of the external MOSFET transistor. An external series gate resistance is specified to maintain an acceptable safe operating area (SOA) for the DMOS device of the internal output driver. As discussed in the UVLO section of this datasheet, the undervoltage lockout (UVLO) circuit holds the PWM gate driver output low while UVLO conditions exists.

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# **APPLICATION INFORMATION**

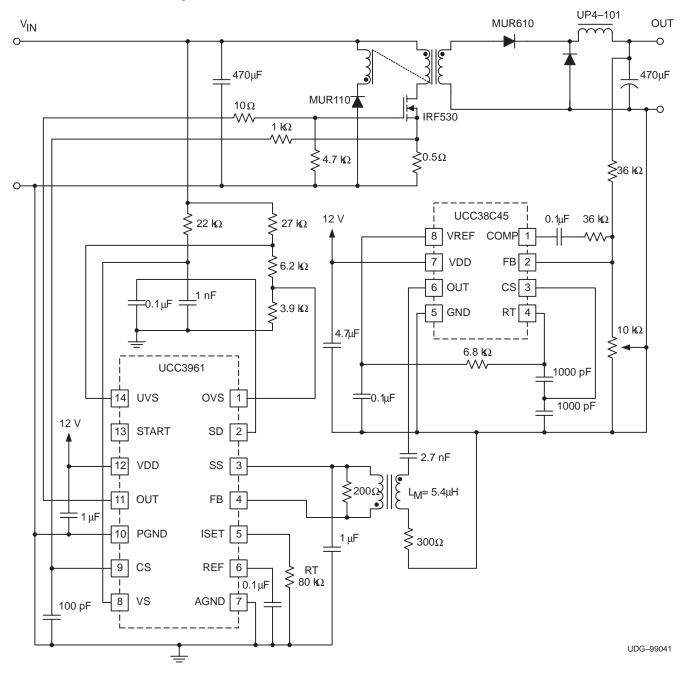

The evaluation circuit of UCC3961 as the primary-side startup circuit and UCC38C45 as the secondary-side controller is shown in Figure 2.

Figure 2. Evaluation Circuit of UCC3961

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

# **APPLICATION INFORMATION**

#### pulse edge transmission circuit

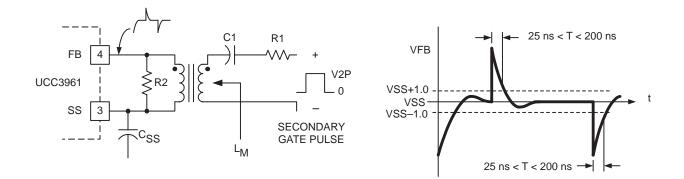

The UCC3961 uses a pulse-edge-transmission (PET) circuit to transmit isolated gate-pulse information from the secondary-side controller. It is important for the PET circuit to have proper frequency response and adequately high damping (low Q-factor) in order to prevent excessive overshoot. The circuit is shown in Figure 3.

#### Figure 3. Pulse Edge Transmission Circuit

The pulse width measured at the FB pin must be between 25 ns when measured at 1 V above the soft-start voltage and and 200 ns when measured at 1 V below the soft-start voltage. The FB voltage must not be overdriven by more than 5 V above or 5 V below the soft-start voltage. In order to prevent false triggering, the FB voltage must not ring below the soft-start voltage by more than  $\pm 0.9$  V. This can be met if the PET circuit has a resonant frequency of 880 kHz and a Q of 0.25. The following values meet the specifications for a 12-V secondary-gate pulse signal, over the full range of UCC3961 operating frequencies.

- T1 1:1 turns ratio,  $LM = 5.4 \mu H$ , Ferronics 11–622J, N1 = N2 = 4 turns

- R1 300 Ω

- C1 2700 pF

- R2 200 Ω

Pulse-edge-transmission (PET) circuits in standard surface-mount packages are available from Pulse Engineering (Part #PA0128, Part #PA0115) and from Cooper Electronic Technologies (Coiltronix), (Part #CTX01–15157).

SLUS431A - MAY 2000 - REVISED DECEMBER 2000

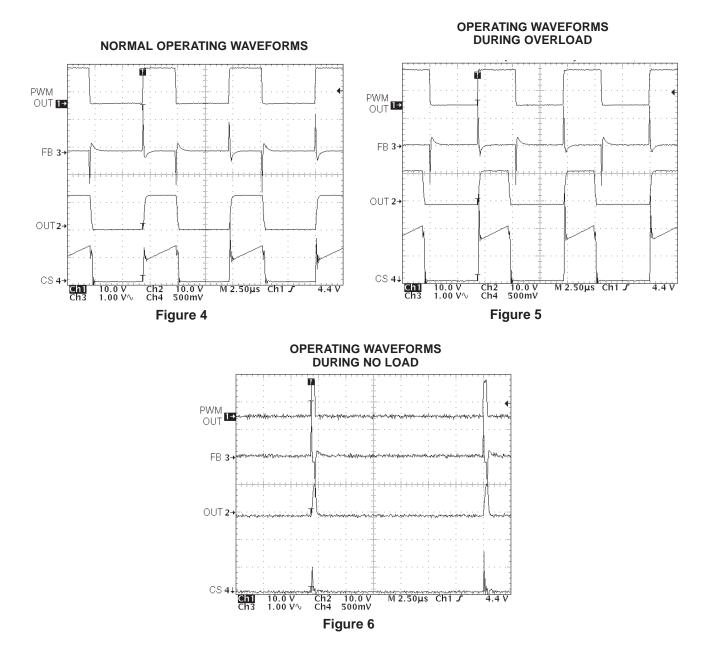

# PARAMETER MEASUREMENT INFORMATION

# ADDITIONAL REFERENCES

1. Dennis, Mark and Michael Madigan, *50-W Forward Converter with Synchronous Rectification and Secondary-Side Control*, SEM–1300, Topic 4, Texas Instruments Literature Number SLUP002.

# PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| UCC2961D         | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UCC2961DG4       | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UCC2961DTRG4     | ACTIVE                | SOIC            | D                  | 14   |                | TBD                       | Call TI          | Call TI                      |

| UCC3961D         | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UCC3961DG4       | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UCC3961DTR       | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UCC3961DTRG4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UCC3961N         | ACTIVE                | PDIP            | N                  | 14   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UCC3961NG4       | ACTIVE                | PDIP            | N                  | 14   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD**: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

TEXAS INSTRUMENTS www.ti.com

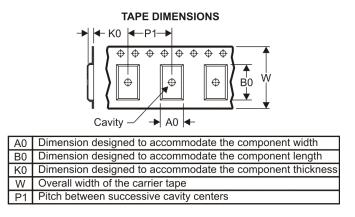

# TAPE AND REEL INFORMATION

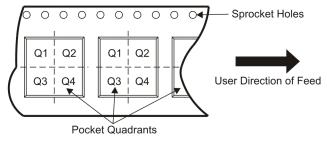

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All | dimensions | are | nominal |

|------|------------|-----|---------|

|------|------------|-----|---------|

| Device     |      | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UCC3961DTR | SOIC | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5     | 9.0     | 2.1     | 8.0        | 16.0      | Q1               |

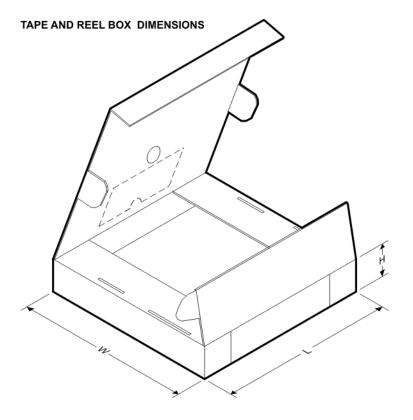

# PACKAGE MATERIALS INFORMATION

11-Mar-2008

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC3961DTR | SOIC         | D               | 14   | 2500 | 346.0       | 346.0      | 33.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated