# UM92870 Series

# Integrated DTMF Receiver

### Features

- Full DTMF receiver in single 18-pin package

- Single 5-volt power supply

- Internal gain setting amplifier

- Adjustable guard time

- Built-in dial-tone filter

- Uses inexpensive 3.5795 MHz crystal

- CMOS for low power consumption

- Tristate outputs

- Early steering output

### General Description

The UM92870 is a complete DTMF receiver designed It includes a standard DTMF signals. to detect decoder section, amplifier. filter input differential The differential logic circuits. section, and steering input amplifier allows adjustment of gain and choice of input configuration. The filter section provides a dial tone filter for dial-tone rejection and separates the dual-tone signal into low-group and high-group tones. The decoder decodes all 16 DTMF tone pairs into a four bit code. The steering logic circuits allow the designer to tailor system parameters such as talk-off and noise immunity. The UM92870 is packaged in 3 standard 18-pin DIP configurations and requires only a few external passive components.

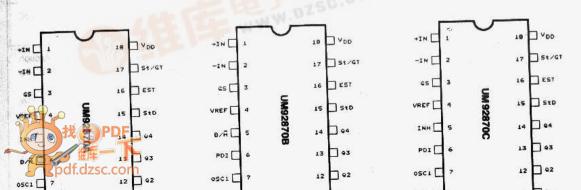

## Pin Configurations

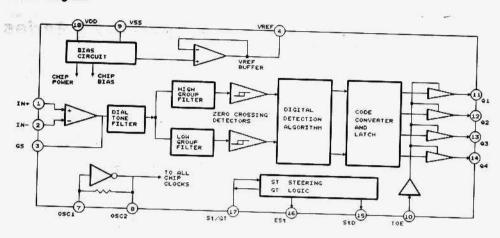

## **Block Diagram**

## Pin Description

| Pin No. | Symbol              | 1/0   | Y .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Description | <del>*</del> |  |  |  |  |

|---------|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--|--|--|--|

| 1       | IN+                 | 1     | Non-inverting input of op-amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |              |  |  |  |  |

| 2       | IN-                 | ī     | Inverting input of op-amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |              |  |  |  |  |

| 3       | GS                  | 1     | Gain select. Gives access to output of front end differ amplifier for connection of feedback resistor.                                                                                                                                                                                                                                                                                                                                                                                 |             |              |  |  |  |  |

| 4       | VREF                | 0     | Reference Voltage output. May be used to bias the inputs at midrail VDD / 2.                                                                                                                                                                                                                                                                                                                                                                                                           |             |              |  |  |  |  |

| 5,6     | INH , B/ H ,<br>PDI | 1,1,1 | INH: DTMF signal control, When this pin is pulled high, detection of tone pairs containing the 1633Hz component is inhibited. To detect all 16 standard digits this pin must be pulled low. B/ H̄: Digital output format control. When this pin is pulled low the UM92870 output is given in hexadecimal code. When input is high, output is in 2-of-8 binary code. Output codes are shown in Table 1.  PDI: power down input. To enter power down mode, this pin must be pulled high. |             |              |  |  |  |  |

| = = -   |                     |       | UM92870A                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin No. 5,6 | INH,B/H      |  |  |  |  |

|         |                     |       | UM92870B                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin No. 5,6 | B/H, PDI     |  |  |  |  |

|         | *                   |       | UM92870C                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin No. 5,6 | INH, PDI     |  |  |  |  |

## Pin Description (Continued)

| Pin No. | Symbol  | 1/0 | Description                                                                                                                                                                                                                                                                                                              |

|---------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | OSCI    | 3 1 | Clock input.                                                                                                                                                                                                                                                                                                             |

| 8       | OSC2    | 1   | Clock output. A 3.5795 MHz crystal connected between OSC1 and OSC2 completes the oscillator circuit.                                                                                                                                                                                                                     |

| 9       | Vss     | 1   | Negative power supply input.                                                                                                                                                                                                                                                                                             |

| 10      | TOE     | 1   | Three-state output enable. Logic high enables the output from Q1 through Q4.                                                                                                                                                                                                                                             |

| 11 - 14 | Q1 - Q4 | . 0 | Three-state output. When enabled by TOE, provides the code which corresponds to the last valid tone-pair received. See Table 1.                                                                                                                                                                                          |

| 15      | StD     | 0   | Delayed steering output. Presents a logic high when a received tone-<br>pair has been registered and the output latch updated; returns to<br>logic low when the voltage on St/Gt falls below VTST.                                                                                                                       |

| 16      | ESt     | . 0 | Early steering output. Presents a logic high once the digital algorithm has detected a valid tone pair. Any subsequent loss of signal condition will cause ESt to return to a logic low.                                                                                                                                 |

| 17      | St/GT   | 1/0 | Steering input/guard time output (bi-directional). A voltage greater than VTST detected at St causes the device to register the detected tone pair and update the output latch. A voltage less than VTST output acts to reset the external steering time constant; its state is a function of ESt and the voltage on St. |

Mode the

| Digit | TOE | Hexadecimal |    |    | Binary Coded 2 of 8 |    |    | of 8       | Low Group | High Group        |                   |

|-------|-----|-------------|----|----|---------------------|----|----|------------|-----------|-------------------|-------------------|

|       |     | Q4          | Q3 | Q2 | Q1                  | Q4 | Q3 | <b>Q</b> 2 | Q1        | Frequency<br>(Hz) | Frequency<br>(Hz) |

| 1     | Н   | 0           | 0  | 0  | 1                   | 0  | 0  | 0          | 0         | 697               | 1209              |

| 2     | Н   | 0           | 0  | 1  | 0                   | 0  | 0  | 0          | 1         | 697               | 1336              |

| 3     | н   | 0           | 0  | 1  | 1                   | 0  | 0  | 1          | 0         | 697               | 1477              |

| 4     | Н   | 0           | 1  | 0  | 0                   | 0  | 1  | 0          | 0         | 770               | 1209              |

| 5     | Н   | 0           | 1  | 0  | 1                   | 0  | 1  | 0          | 1         | 770               | 1336              |

| 6     | н   | 0           | 1  | 1  | 0                   | 0  | 1  | 1          | 0         | 770               | 1477              |

| 7     | н   | 0           | 1  | 1  | 1                   | 1  | 0  | 0          | 0         | 852               | 1209              |

| 8     | Н   | 1           | 0  | 0  | 0                   | 1  | 0  | 0          | 1         | 852               | 1336              |

| 9     | н   | 1           | 0  | 0  | 1                   | 1  | 0  | 1          | 0         | 852               | 1477              |

| 0     | Н   | 1           | 0  | 1  | 0                   | 1  | 1  | 0          | 1         | 941.              | 1336              |

| *     | н   | 1           | 0  | 1  | 1                   | 1  | 1  | 0          | 0         | 941               | 1209              |

| #     | н   | 1           | 1  | 0  | 0                   | 1  | 1  | 1          | 0         | 941               | 1477              |

| Α     | н   | -,1         | 1  | 0  | 1                   | 0  | 0  | 1          | 1         | 697               | 1633              |

| В     | Н   | , 1         | 1  | 1  | 0                   | 0  | 1  | 1          | 1         | 770               | 1633              |

| С     | н   | 1           | 1  | 1  | 1                   | 1  | 0  | 1          | 1         | 852               | 1633              |

| D     | Н   | 0           | 0  | 0  | 0                   | 1  | 1  | 1          | 1         | 941               | 1633              |

| ANY   | L   | Z           | z  | z  | z                   | Z  | Z  | Z          | z         |                   | 1000              |

#### **Function Description**

bet suct

The UM92870 monolithic DTMF receiver offers small size, low power consumption and high performance. Its general operation is described as follows:

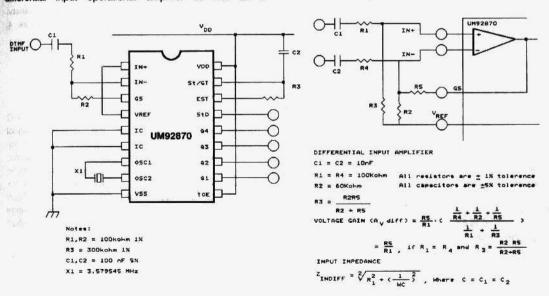

#### Differential Input Amplifier

To aid design flexibility, the UM92870 provides a differential input operational amplifier as well as a

bias source (VREF) which is used to bias the input at midrail. Adjustment of gain is achieved by connecting a feedback resistor to the op-amp output (GS). Figure 1 shows the differential configuration with the op-amp connected for unity gain and VREF biasing the input at Vob/z. Figure 2 shows the differential configuration, which permits the adjustment of gain with the feedback resistor, R5.

Figure 1. Single Ended Input Configuration

Figure 2. Differential Input Configuration

#### Filter Section

The differential input stage is followed by a low pass continuous RC active filter which performs an anti-

frequency components by two sixth order switched capacitor bandpass filters. Each component tone is then