6427525 0050012 550 ■NECE

# PRELIMINARY PRODUCT INFORMATION

# **BIPOLAR ANALOG INTEGRATED CIRCUIT μPC1861**

# HORIZONTAL LOCK CLOCK GENERATOR

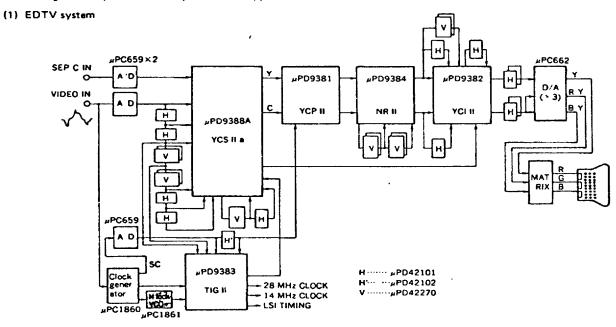

The µPC1861 is an LSI chip which incorporates a PLL circuit to generate clocks whose frequency is multipliable by f (Horizontal sync signal frequency) and is ideal for the processing of digital video signals.

so reported in the LSI chip, Thanks to the sync separator, phase comparator, and voltage controlled oscillator (VDQ) also a horizontal lock clock (synchronous with a horizontal sync signal) can be obtained by divine the frequency of the generated clock with an external frequency divider. In addition, the µPC1861 adopts a win small outline package (SOP) and thus saves WWW.DZSC.COM mounting space on a PC board.

#### **FEATURES**

- VCO is incorporated (may be used up to 1 820 fm

- Horizontal sync separator is incorporated.

- Low current consumption (approx. 55

ORDERING INFORMATION

PART NUMBER PACAKGE

QUALITY GRADE

μPC1861GR હિક્રા 6- માર્જિટ Dastic SOP (225 mil)

Standard

Please refer to Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

> The information contained in this document is being issued in advance of the production cycle for the The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

Document No IP-2889 (O.D.No. 1P-8369) ate Published June 1991 M

■ 6427525 0050013 497 **■**NECE

NEC

μPC1861

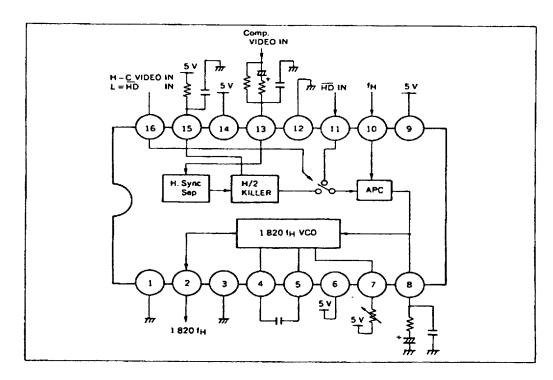

#### **BLOCK DIAGRAM**

Block Diagram of System to which µPC1861 Is Applied.

FROM 半導体応用技術本部 TO EC SBU MV4560

'92.10. 9 6:16 ^°-y¨ 03 dia nouri TOTAL : 8 nadia nouri

■ 6427525 0050014 323 ■NECE

NEC

μPC1861

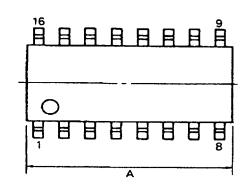

PIN ASSIGNMENTS (Top View)

GND (for VCO) 1 16 Input selector switch VCO output 2 15 H/2 killer pulse width time constant GND (for Sync separator) 3 14 VCC (for Sync separator) 13 H sync separation input (C VIDEO input) Osc capacitor 1 4 12 GND (for APC) Osc capacitor 2 5 VCC (for VCO) 6 11 HD pulse input Osc frequency adjust 7 10 External frequency divider input 9 VDD (for APC) Filter B

# ■ 6427525 0050015 26T ■NECE

# NEC

μPC1861

#### **ELECTRICAL CHARACTERISTICS**

## ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C)

| PARAMETER                            | SYMBOL | CONDITIONS                                    | RATING                       | TINU             |

|--------------------------------------|--------|-----------------------------------------------|------------------------------|------------------|

| Supply Voltage                       | VCC    | Applicable to Power Supply pins 6 & 14        | 7                            | V                |

| Supply Voltage                       | VDO    | Applicable to Power Supply pin 9              | 7                            | V                |

| Composite Video Input Signal Voltage | ei2    |                                               | 3                            | V <sub>P-P</sub> |

| Input Voltage                        | ei     | Applicable to Input pins 10 & 11 (CMOS input) | -0.5 to V <sub>DD</sub> +0.5 | V                |

| Input Select Voltage                 | V16    | Applicable to Input pin 16 (CMOS input)       | -0.5 to V <sub>DD</sub> +0.5 | V                |

| Power Dissipation of Package         | PD     | T <sub>a</sub> = 75 °C                        | 275                          | mW               |

| Operating Temperature                | Topt   |                                               | -10 to +75                   | *c               |

| Storage Temperature                  | Tata   |                                               | -40 to +125                  | *c               |

# RECOMMENDED OPERATING CONDITIONS (Topt = -10 to +75 °C)

| PARAMETER                    | SYMBOL          | MIN.                | TYP. | MAX.                | UNIT | CONDITIONS                              |  |

|------------------------------|-----------------|---------------------|------|---------------------|------|-----------------------------------------|--|

| Supply Voltage 1             | V <sub>CC</sub> | 4.5                 | 5.0  | 5.5                 | V    | Applicable to Power Supply pins 6 & 14  |  |

| Supply Voltage 2             | V <sub>DD</sub> | 4.5                 | 5.0  | 5.5                 | V    | Applicable to Power Supply pin 9        |  |

| Composite Video Input Signal | ei2             |                     | 1.0  |                     | Vpp  |                                         |  |

| Input Voltage, Low           | •iL             | 0                   |      | 0.3 V <sub>DD</sub> | V    | Applicable to Input pins 10 & 11        |  |

| Input Voltage, High          | eil )           | 6.7 V <sub>UU</sub> |      | VDD                 | v    | (CMOS input)                            |  |

| Input Select Voltage, Low    | V16L            | 0                   |      | 0.3 V <sub>DD</sub> | v    | Applicable to Input pin 11 (CMOS input) |  |

| Input Select Voltage, High   | V16H            | 0.7 V <sub>DD</sub> |      | VDD                 | V    | Applicable to Input pin 13 (CMOS input) |  |

'92.10. 9 6:16 ^\*-y" 05 nadia nouri TOTAL : 8 nadia nouri

■ 6427525 0050016 1T6 ■NECE

NEC

μPC1861

# AC/DC CHARACTERISTICS (T<sub>2</sub> = 25 ± 2 °C, RH ≤ 70 %, V<sub>CC</sub> = 5.0 V, V<sub>DD</sub> = 5.0 V)

| No. | PARAMETER                                                                  | SYMBOL         | MIN. | TYP.  | MAX. | UNIT                | CONDITIONS                                                                                                                                                                                                                                       |

|-----|----------------------------------------------------------------------------|----------------|------|-------|------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Current Consumption 1                                                      | lcc1           |      | 9.5   |      | mA                  | Circuit current when no signal is input (including I <sub>DO</sub> . Pins 11, 15 = "L"; Pin 13: Open; Pin 7 = 200 µA)                                                                                                                            |

| 2   | Current Consumption 2                                                      | ¹CC2           |      | 10.7  |      | mA                  | Circuit current when PLL is locked (including IDD, Pins 11, 16 = "L"; Pin 13: C. Video; Pin 7 = 200 µA)                                                                                                                                          |

| 3   | DC Level of H Sync<br>Separation Level                                     | Vssн           | 1.9  | 2.2   | 2.5  | V                   | Voltage of Pin No. 13 when connected to GND via 10 kΩ resistor                                                                                                                                                                                   |

| 4   | Minimum Sync<br>Separation Level                                           | VSEP           | 60   |       |      | mW                  | Critical sync level at which output to<br>Pin 15 is no langer produced when<br>sync level of C. VIDEO is lowered                                                                                                                                 |

| 5   | H Sync Lock-in Range                                                       | fHP            |      | ±1.75 |      | kHz                 | Frequency range that can be pulled in by APC when HD input frequency is varied (f <sub>H</sub> conversion)                                                                                                                                       |

| 6   | VCO Control Sensitivity<br>High level (1)                                  | B              |      | 0.7   |      | Hz/mV               | Rate of variation of frequency with no signal being input to Pin 13, with Pins 10, 11, & 16 set to "H" or "L", and with 0 to 5 V being applied to Pin 8 (f <sub>H</sub> conversion)                                                              |

| 7   | Free-run Frequency<br>(Without Adjustment)                                 | to             |      | 0     |      | Hz<br>-             | Frequency difference of VCO output from<br>1 820 fg with no signal being input to<br>Pin 13, with Pins 10, 11, & 16 set to "H"<br>or "L", and with Pin 8 left open                                                                               |

| 8   | Free-run Frequency<br>Adjustable Range                                     | foc            |      | ±1.5  |      | MHz                 | Adjustable free-run frequency range with no signal being input to Pin 13, with Pins 10, 11, & 16 set to "H" or "L", and with Pin 8 left open                                                                                                     |

| 9   | VCO Output Level                                                           | eVCO           |      | 1     |      | V <sub>p•p</sub>    | Output level of VCO with no signal being input to Pin 13, with Pins 10, 11 & 16 set to "H" or "L", and with Pin 8 left open                                                                                                                      |

| 10  | Oscillation Start (Stop) Voltage of VCO                                    | ∨s⊤            | 2.85 |       |      | <b>~</b>            | Voltage at which VCO starts (or stops) oscillation when V <sub>CC</sub> (Pin 6) is gradually increased from 0 V (or decreased from 5 V) with no signal being input to Pin 13, with Pins 10, 11, & 16 set to "H" or "L", and with Pin 8 left open |

| 11  | Fluctuation of Free-run<br>Frequency Due to Supply<br>Voltage Fluctuations | ØtO<br>(VCC)   |      | o     |      | Hz/V                | Fluctuation of free-run frequency at V <sub>CC</sub> (Pin 6) = 4.5 to 5.5 V (under the same pin conditions as fo)                                                                                                                                |

| 12  | Fluctuation of VCO Output<br>Level Due to Supply<br>Voltage Fluctuations   | Aevco<br>(Vcc) |      | 0.5   |      | ν <sub>p-p</sub> /ν | Fluctuation of VCO output level at VCC (Pin 6) = 4.5 to 5.5 V (under the same pin conditions as fo)                                                                                                                                              |

'92.10. 9 6:16 ^-y" 06 adia nouri TOTAL : 8 nadia nouri

■ 6427525 0050017 032 ■NECE

**NEC**

μPC1861

| No. | PARAMETER                                                               | SYMBOL          | MIN. | TYP. | MAX. | UNIT                 | CONDITIONS                                                                                                 |

|-----|-------------------------------------------------------------------------|-----------------|------|------|------|----------------------|------------------------------------------------------------------------------------------------------------|

| 13  | Fluctuation of Free-run<br>Frequency Due to<br>Temperature Fluctuations | ∆to(T)          |      | 6.5  |      | Hz/°C                | Fluctuation of free-run frequency at $T_a = -10$ °C to +60 °C (under the same pin conditions as fo)        |

| 14  | Fluctuation of VCO Output Level Due to Temperature Fluctuations         | ∆evco<br>(T)    |      |      |      | V <sub>P-P</sub> /*C | Fluctuation of VCO output level at T <sub>a</sub> = -10 °C to +60 °C (under the same pin conditions as fo) |

| 15  | Residual Jitter                                                         | TJ              |      |      | 5    | ns                   | Distortion width of output waveform when PLL is locked                                                     |

| 16  | Output Delay Time 1<br>(to C. VIDEO)                                    | T <sub>d1</sub> |      |      |      | ns                   | Amount of delay in VCO output from H. SYNC of C. VIDEO when PLL is locked at C. VIDEO input                |

| 17  | Output Delay Time 2 (to HD)                                             | T <sub>d2</sub> |      |      |      | ns                   | Amount of delay in VCO output from<br>HD when PLL is locked at HD input                                    |

'92.10. 9 nadia nouri

6:.16

■ 6427525 0050018 T79 ■NECE

# NEC

μPC1861

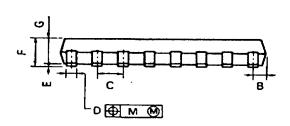

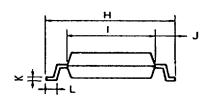

### 16PIN PLASTIC SOP (225 mil)

#### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS       | INCHES                  |  |  |

|------|-------------------|-------------------------|--|--|

| A    | 10 46 MAX.        | 0.412 MAX.              |  |  |

| В    | 0 78 MAX          | 0.031 MAX.              |  |  |

| С    | 1.27 (T P )       | 0.050 (T.P.)            |  |  |

| D    | 0.40 - 8 68       | 0.016 - 8 8 8 3         |  |  |

| ε    | 0.1*0 1           | 0.004 <sup>±0.004</sup> |  |  |

| F    | 1.8 MAX.          | 0.071 MAX.              |  |  |

| G    | 1.49              | 0 059                   |  |  |

| н    | 65 <sup>±03</sup> | 0.256 <sup>±0 012</sup> |  |  |

| ı    | 4.4               | 0 173                   |  |  |

| J    | 1 1               | 0 043                   |  |  |

| к    | 0.15-808          | 0 006±8 88\$            |  |  |

| L    | 0.6*02            | 0.024 -0 009            |  |  |

| M    | 0.12              | 0 005                   |  |  |

\$16GM-50-225B,C-1