# 9 GHz DIVIDE-BY-4 **DYNAMIC PRESCALER**

# **UPG503B**

### **FEATURES**

- WIDE OPERATING FREQUENCY RANGE:  $f_{IN} = 3.5 \text{ to } 9.0 \text{ GHz } (T_A = 25^{\circ}\text{C})$

- DIVISION RATIO OF 4

- GUARANTEED OPERATING TEMPERATURE RANGE: -25°C to +75°C

### **DESCRIPTION**

The UPG503B is a GaAs divide-by-4 prescaler that is capable of operating up to 9 GHz. It is designed to be used in the frequency synthesizers of microwave communication systems and measurement equipment. The UPG503B is a dynamic divider. It employs buffered FET logic (BFL). The UPG503B is available in a hermetic 8-lead ceramic flat package.

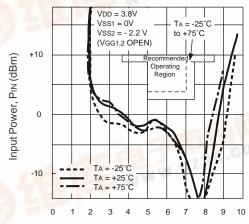

## INPUT POWER vs. INPUT FREQUENCY

Input Frequency, f (GHz)

| PART NUMBER PACKAGE OUTLINE |                                                                                                     |            | UPG503B<br>BF08 |      |              |

|-----------------------------|-----------------------------------------------------------------------------------------------------|------------|-----------------|------|--------------|

| SYMBOLS                     | PARAMETERS AND CONDITIONS                                                                           | UNITS      | MIN             | TYP  | MAX          |

| Idd                         | Supply Current Supply Current                                                                       | mA         | 40              | 80   | 130          |

| ISS1                        | Sink Current <sup>2</sup> Iss1 = IDD - ISS2                                                         | mA         |                 | 27   |              |

| ISS2                        | Sink Current <sup>2</sup>                                                                           | mA         | 21              | 53   | 93           |

| fIN(U)                      | Upper Limit of Input Frequency, PIN = +9 to +10 dBm                                                 | GHz        | 8.6             | 9.0  |              |

| fIN(L)                      | Lower Limit of Input Frequency, PIN = +9 to +10 dBm                                                 | GHz        | 47              | 3.5  | 3.7          |

| Pin                         | Input Power, fin = 3.7 to 8.6 GHz<br>fin = 5.0 to 7.4 GHz                                           | dBm<br>dBm | 9.0<br>3.0      | 0750 | 10.0<br>10.0 |

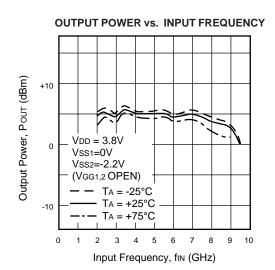

| Роит                        | Output Power, $fin = 8.6 \text{ GHz}$ , $Pin = +10 \text{ dBm}$<br>fin = 3.7  GHz, $Pin = +10  dBm$ | dBm<br>dBm | 0               | 3 3  |              |

| Rтн                         | Thermal Resistance, Channel to Case                                                                 | °C/W       |                 |      | 10           |

- 1. Device may exhibit low frequency spur typically below 150 Hz and -45 dBm.

- 2. Current is positive into the IDD pin and returns through the Iss1 and Iss2 pins.

### ELECTRICAL CHARACTERISTICS TA = 25°C to +75°C, VDD = 3.8 V, VSS1 = 0 V, VSS2 = -2.2 V)

| PART NUMBER PACKAGE OUTLINE |                                                                                                                  |            | UPG503B<br>BF08 |            |              |

|-----------------------------|------------------------------------------------------------------------------------------------------------------|------------|-----------------|------------|--------------|

| SYMBOLS                     | PARAMETERS AND CONDITIONS                                                                                        | UNITS      | MIN             | TYP        | MAX          |

| IDD                         | Supply Current                                                                                                   | mA         |                 | 80         |              |

| Iss1                        | Sink Current <sup>1</sup> Iss1 = IDD - Iss2                                                                      | mA         |                 | 27         |              |

| ISS2                        | Sink Current <sup>1</sup>                                                                                        | mA         |                 | 53         |              |

| fIN(U)                      | Upper Limit of Input Frequency, PIN = +9 to +10 dBm                                                              | GHz        | 8.0             |            |              |

| fIN(L)                      | Lower Limit of Input Frequency, PIN = +9 to +10 dBm                                                              | GHz        |                 |            | 4.0          |

| Pin                         | Input Power, fin = 4.0 to 8.0 GHz<br>fin = 5.0 to 7.0 GHz                                                        | dBm<br>dBm | 9.0<br>4.0      |            | 10.0<br>10.0 |

| Роит                        | Output Power fin = $8.0 \text{ GHz}$ , Pin = $+10 \text{ dBm}$ fin = $4.0 \text{ GHz}$ , Pin = $+10 \text{ dBm}$ | dBm<br>dBm | -1.0<br>-1.0    | 2.0<br>2.0 |              |

#### Note:

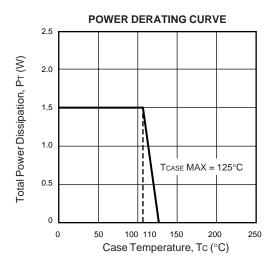

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup> (TA = 25°C)

| SYMBOLS   | PARAMETERS                           | UNITS | RATINGS     |

|-----------|--------------------------------------|-------|-------------|

| VDD-VSS1  | Supply Voltage                       | V     | 5.0         |

| Vss2-Vss1 | Supply Voltage                       | V     | -5.0        |

| PIN       | Input Power                          | dBm   | 13          |

| Рт        | Total Power Dissipation <sup>2</sup> | W     | 1.5         |

| Тѕтс      | Storage Temperature                  | °C    | -65 to +175 |

| Tc        | Case Temperature                     | °C    | -65 to +125 |

#### Notes:

- 1. Operation in excess of any one of these conditions may result in permanent damage.

- 2. Tc ≤ 125°C

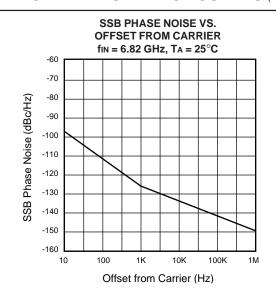

### TYPICAL PERFORMANCE CURVES (TA = 25°)

<sup>1.</sup> Current is positive into the IDD pin and returns through the ISS1 and ISS2 pins.

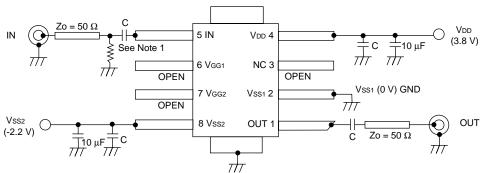

### POWER SUPPLY CONFIGURATIONS (VGG1 and VGG2 are normally open)

### CONFIGURATION 1 2 Bias Supply

VDD = 3.8 V VSS1 = 0 V (GND) VSS2 = -2.2 V

C: 1000 - 5000 pF Chip Capacitor

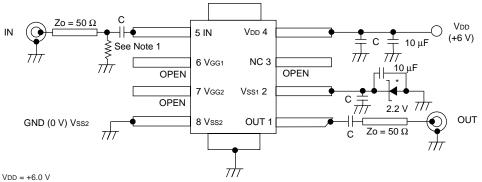

### CONFIGURATION 2 Single Positive Bias Supply

VSS2 = 0 V (GND) C: 1000 - 5000 pF Chip Capacitor

\* VSS1 should be connected to GND through a 2.2 V Zener Diode (RD2.2FB or IN3394).

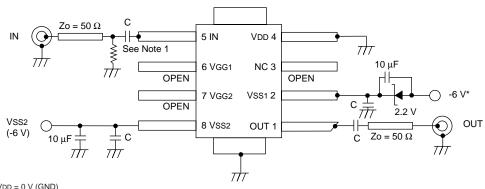

# CONFIGURATION 3 Single Negative Bias Supply

VDD = 0 V (GND) VSS2 = -6 V C: 1000 - 5000 pF Chip Capacitor

\* For VSS1, the bias voltage of -6.0 should be applied through a 2.2 V Zener Diode (RD2.2FB or IN3394).

#### Notes:

- 1. Because of the high internal gain and gain compression of the UPG503B, the device is prone to self-oscillation in the absence of an RF input signal. This self-oscillation can be suppressed by either of the following means:

- Add a shunt resistor to the RF input line. Typically a resistor value between 50 and 1000 ohms will suppress the self-oscillation (see the test circuit schematic).

- Apply a negative voltage through a 1000 ohm resistor to the normally open Vgg1 connection. Typically voltages between 0 and -9 volts will suppress the self-oscillation.

Both of these approaches will reduce the input sensitivity of the device (by as much as 3 dB for a 50 ohm shunt resistor), but otherwise have no effect on the reliability or electrical characteristics of the device.

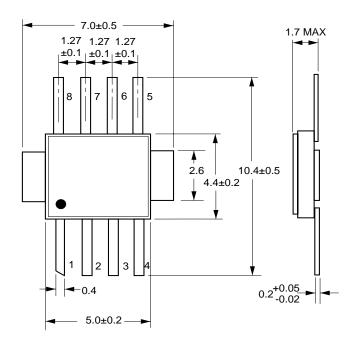

## OUTLINE DIMENSIONS (Units in mm)

### UPG503B **PACKAGE OUTLINE BF08**

### **LEAD CONNECTIONS:**

1. OUTPUT 5. INPUT 2. Vss1 6. Vgg1 3. NC\* 7. VGG2 4. VDD 8. Vss2

\* No Connection