April 2005 Revised May 2005

# USB1T1103 Universal Serial Bus Peripheral Transceiver with Voltage Regulator

## **General Description**

This chip provides a USB Transceiver functionality with a voltage regulator that is compliant to USB Specification Rev 2.0. this integrated 5V to 3.3V regulator allows interfacing of USB Application specific devices with supply voltages ranging from 1.65V to 3.6V with the physical layer of Universal Serial Bus. It is capable of operating at 12Mbits/s (full speed) data rates and hence is fully compliant to USB Specification Rev 2.0. The Vbusmon terminal allows for monitoring the Vbus line.

The USB1T1103 also provides exceptional ESD protection with 15kV contact HBM on D+, D- terminals.

#### **Features**

- Complies with Universal Serial Bus Specification 2.0

- Integrated 5V to 3.3V voltage regulator for powering VBus

- Utilizes digital inputs and outputs to transmit and receive USB cable data

- Supports full speed (12Mbits/s) data rates

- Ideal for portable electronic devices

- MLP technology package (16 terminal) with HBCC footprint

- 15kV contact HBM ESD protection on bus terminals

- Supports disable mode and is functionally equivalent to Philips ISP1102

## **Applications**

- PDA

- PC Peripherals

- Cellular Phones

- MP3 Players

- Digital Still Camera

- Information Appliance

## **Ordering Code:**

| Order Number | Number  |                                                                               |  |  |

|--------------|---------|-------------------------------------------------------------------------------|--|--|

| USB1T1103MPX | MLP14D  | Pb-Free 14-Terminal Molded Leadless Package (MLP), 2.5mm Square               |  |  |

| USB1T1103MHX | MLP16HB | Pb-Free 16-Terminal Molded Leadless Package (MHBCC), JEDEC MO-217, 3mm Square |  |  |

Pb-Free package per JEDEC J-STD-020B.

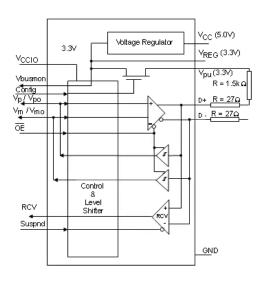

## **Logic Diagram**

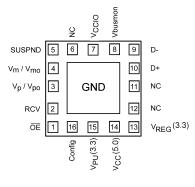

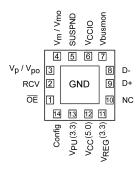

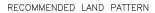

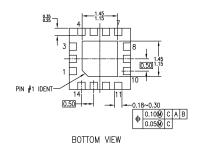

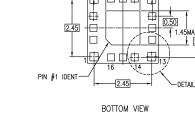

## **Connection Diagrams**

MLP16 GND Exposed Diepad

(Bottom View)

MLP14 GND Exposed Diepad

(Bottom View)

## **Terminal Descriptions**

| Termina           | Number            | Terminal                        | 1/0  | Tourning! Description                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------|-------------------|---------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MLP14             | MLP16             | Name                            | I/O  | Terminal Description                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 1                 | 1                 | ŌĒ                              | I    | Output Enable: Active LOW enables the transceiver to transmit data on the bus. When not active the transceiver is in the receive mode (CMOS level is relative to V <sub>CCIO</sub> )                                                                                                                                                                                                                              |  |  |

| 2                 | 2                 | RCV                             | 0    | Receive Data Output: Non-inverted CMOS level output for USB differential Input (CMOS output level is relative to $V_{\text{CCIO}}$ ). Driven LOW when SUSPN is HIGH; RCV output is stable and preserved during SE0 condition.                                                                                                                                                                                     |  |  |

| 3                 | 3                 | V <sub>p</sub> /V <sub>po</sub> | I/O  | Single-ended D+ receiver output $V_P$ (CMOS level relative to $V_{CCIO}$ ): Used for external detection of SE0, error conditions, speed of connected device; Terminal also acts as drive data input $V_{po}$ (see Table 1 and Table 2). Output drive is 4 mA buffer.                                                                                                                                              |  |  |

| 4                 | 4                 | V <sub>m</sub> /V <sub>mo</sub> | I/O  | Single-ended D– receiver output $V_m$ (CMOS level relative to $V_{CCIO}$ ): Used for external detection of SE0, error conditions, speed of connected device; Terminal also acts as drive data input $V_{mo}$ (see Table 1 and Table 2). Output drive is 4 mA buffer.                                                                                                                                              |  |  |

| 5                 | 5                 | SUSPND                          | ı    | Suspend: Enables a low power state (CMOS level is relative to V <sub>CCIO</sub> ). While the SUSPND terminal is active (HIGH) it will drive the RCV terminal to logic "0" state.                                                                                                                                                                                                                                  |  |  |

|                   | 6                 | NC                              |      | No Connect                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 6                 | 7                 | V <sub>CCIO</sub>               |      | Supply Voltage for digital I/O terminals (1.65V to 3.6V): When not connected the D+ and D- terminals are in 3-STATE. This supply bus is totally independent of $V_{\rm CC}$ (5V) and $V_{\rm REG}$ (3.3V), and must never exceed the $V_{\rm REG}$ (3.3) voltage. For $V_{\rm CCIO}$ disconnected the O+/O- terminals are HIGH Impedance and the $V_{\rm PU}$ (3.3V) is turned off.                               |  |  |

| 7                 | 8                 | Vbusmon                         | 0    | Vbus monitor output (CMOS level relative to V <sub>CCIO</sub> ): When Vbus > 4.1V then Vbusmon = HIGH and when Vbus < 3.6V then Vbusmon = LOW. If SUSPND = HIGH then Vbusmon is pulled HIGH.                                                                                                                                                                                                                      |  |  |

| 9, 8              | 10, 9             | D+, D-                          | AI/O | Data +, Data -: Differential data bus conforming to the USB standard. Terminals are HIGH Impedance for bus powered mode when Vbus < 3.6V. For ByPass Mode then HIGH Impedance when V <sub>REG</sub> / Vbus < V <sub>REG</sub> minimum.                                                                                                                                                                            |  |  |

| 10                | 11                | NC                              |      | No Connect                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                   | 12                | NC                              |      | No Connect                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 11                | 13                | V <sub>REG</sub> (3.3V)         |      | Internal Regulator Option: Regulated supply output voltage (3.0V to 3.6V) during 5V operation; decoupling capacitor of at least 0.1 µF is required. Regulator ByPass Option: Used as supply voltage input for 3.3V operation.                                                                                                                                                                                     |  |  |

| 12                | 14                | V <sub>CC</sub> (5.0V)          |      | Internal Regulator Option: Used as supply voltage input (4.0V to 5.5V); can be connected directly to USB line Vbus. Regulator ByPass Option: Connected to V <sub>REG</sub> (3.3V)                                                                                                                                                                                                                                 |  |  |

| 13                | 15                | V <sub>PU</sub> (3.3V)          |      | Pull-up Supply Voltage $(3.3V\pm10\%)$ : Connect an external $1.5k\Omega$ resistor on D+ (FS data rate); Terminal function is controlled by Config input terminal: Config = LOW – V <sub>PU</sub> $(3.3V)$ is floating (HIGH Impedance) for zero pull-up current. Config = HIGH – V <sub>PU</sub> $(3.3V)$ = $3.3V$ ; internally connected to V <sub>REG</sub> $(3.3V)$ . V <sub>PU</sub> is OFF in disable mode. |  |  |

| 14                | 16                | Config                          | I    | USB connect or disconnect software control input. Configures 3.3V to external 1.5k $\Omega$ resistor on D+ when HIGH.                                                                                                                                                                                                                                                                                             |  |  |

| Exposed<br>Diepad | Exposed<br>Diepad | GND                             | GND  | GND supply down bonded to exposed diepad to be connected to the PCB GND.                                                                                                                                                                                                                                                                                                                                          |  |  |

## **Functional Description**

The USB1T1103 transceiver is designed to convert CMOS data into USB differential bus signal levels and to convert USB differential bus signal to CMOS data.

To minimize EMI and noise the outputs are edge rate controlled with the rise and fall times controlled and defined for full speed data rates only (12Mbits/s). The rise, fall times are balanced between the differential terminals to minimize skew.

The USB1T1103 differs from earlier USB Transceiver in that the  $V_p/V_m$  and  $V_{po}/V_{mo}$  terminals are now I/O terminals

rather than discrete input and output terminals. Table 1 describes the specific terminal functionality selection. Table 2 and Table 3 describe the specific Truth Tables for Driver and Receiver operating functions.

The USB1T1103 also has the capability of various power supply configurations, including a disable mode for  $\rm V_{CCIO}$  disconnected, to support mixed voltage supply applications (see Table 4) and Section 2.1 for detailed descriptions.

#### **Functional Tables**

**TABLE 1. Function Select**

| SUSPND | OE | D+, D-                 | RCV                  | V <sub>p</sub> /V <sub>po</sub> | V <sub>m</sub> /V <sub>mo</sub> | Function                                                |

|--------|----|------------------------|----------------------|---------------------------------|---------------------------------|---------------------------------------------------------|

| L      | L  | Driving &<br>Receiving | Active               | V <sub>po</sub> Input           | V <sub>mo</sub> Input           | Normal Driving<br>(Differential Receiver Active)        |

| L      | Н  | Receiving (Note 1)     | Active               | V <sub>p</sub> Output           | V <sub>m</sub> Output           | Receiving                                               |

| Н      | L  | Driving                | Inactive<br>(Note 2) | V <sub>po</sub> Input           | V <sub>mo</sub> Input           | Driving during Suspend (Differential Receiver Inactive) |

| Н      | Н  | 3-STATE<br>(Note 1)    | Inactive<br>(Note 2) | V <sub>p</sub> Output           | V <sub>m</sub> Output           | Low Power State                                         |

Note 1: Signal levels is function of connection and/or pull-up/pull-down resistors.

Note 2: For SUSPND = HIGH mode the differential receiver is inactive and the output RCV is forced LOW. The out-of-suspend signaling (K) is detected via the single-ended receivers of the  $V_p/V_{po}$  and  $V_m/V_{mo}$  terminals.

TABLE 2. Driver Function (OE = L) using Differential Input Interface

|   | V <sub>m</sub> /V <sub>mo</sub> | V <sub>p</sub> /V <sub>po</sub> | Data (D+ / D−)       |

|---|---------------------------------|---------------------------------|----------------------|

| Ī | L                               | L                               | SE0 (Note 3)         |

| Ī | L                               | Н                               | Differential Logic 1 |

| Ī | Н                               | L                               | Differential Logic 0 |

| Ī | Н                               | Н                               | Illegal State        |

Note 3: SE0 = Single Ended Zero

TABLE 3. Receiver Function ( $\overline{OE} = H$ )

| D+, D-               | RCV | V <sub>p</sub> /V <sub>po</sub> | V <sub>m</sub> /V <sub>mo</sub> |

|----------------------|-----|---------------------------------|---------------------------------|

| Differential Logic 1 | Н   | Н                               | L                               |

| Differential Logic 0 | L   | L                               | Н                               |

| SE0                  | Х   | L                               | L                               |

X = Don't Care

RCV(0) denotes the signal level on output RCV just prior to the SE0 or SE1 event. This level is stable during the SE0 or SE1 event period.

## **Power Supply Configurations and Options**

The three modes of power supply operation are:

- · Normal Mode: Regulated Output and Regulator Bypass

- Regulated Output: V<sub>CCIO</sub> is connected and V<sub>CC</sub>(5.0) is connected to 5V (4.0V to 5.5V) and the internal voltage regulator then produces 3.3V for the USB connections.

- 2. Internal Regulator Bypass Mode:  $V_{CCIO}$  is connected and both  $V_{CC}(5.0)$  and  $V_{REG}(3.3)$  are connected to a 3.3V source (3.0V to 3.6V).

In both cases for normal mode the  $\rm V_{CCIO}$  is an independent voltage source (1.65V to 3.6V) that is a function of the external circuit configuration.

Sharing Mode: V<sub>CCIO</sub> is only supply connected. V<sub>CC</sub> and V<sub>REG</sub> are not connected. In this mode the D+ and D- terminals are 3-STATE and the USB1T1103 allows external signals up to 3.6V to share the D+ and D- bus lines. Internally the circuitry limits leakage from D+ and D- terminals (maximum 10  $\mu\text{A})$  and  $V_{CCIO}$  such that device is in low power (suspended) state. Terminals Vbusmon and RCV are forced LOW as an indication of this mode with Vbusmon being ignored during this state.

• Disable Mode:  $V_{CCIO}$  is not connected.  $V_{CC}$  is connected, or  $V_{CC}$  and  $V_{REG}$  are connected. 0V to 3.3V in this mode D+ and D- are 3-STATE and  $V_{PU}$  is HIGH Impedance (switch is turned off). The USB1T1103 allows external signals up to 3.6V to share the D+ and D- bus lines. Internally the circuitry limits leakage from D+ and D- pins (maximum  $10\mu A$ ).

A summary of the Supply Configurations is described in Table  $4. \,$

**TABLE 4. Power Supply Configuration Options**

| Power Supply Mode Configuration |                                 |                              |                                    |                                                                        |  |  |

|---------------------------------|---------------------------------|------------------------------|------------------------------------|------------------------------------------------------------------------|--|--|

| Terminals                       | Disable                         | Sharing                      | Normal (Regulated<br>Output)       | Normal (Regulator<br>Bypass)                                           |  |  |

| V <sub>CC</sub> (5V)            | Connected to 5V source          | Not Connected<br>or<br><3.6V | Connected to 5V<br>Source          | Connected to V <sub>REG</sub> (3.3V) [Max Drop of 0.3V] (2.7V to 3.6V) |  |  |

| V <sub>REG</sub> (3.3V)         | 3.3V, 300μA<br>Regulated Output | Not Connected                | 3.3V, 300 μA<br>Regulated Output   | Connected to 3.3V<br>Source                                            |  |  |

| V <sub>CCIO</sub>               | ≤0.5V                           | 1.65V to 3.6V Source         | 1.65V to 3.6V Source               | 1.65V to 3.6V Source                                                   |  |  |

| V <sub>PU</sub> (3.3V)          | 3-STATE (off)                   | 3-STATE (Off)                | 3.3V Available if<br>Config = HIGH | 3.3V Available if<br>Config = HIGH                                     |  |  |

| D+, D-                          | 3-STATE (off)                   | 3-STATE                      | Function of<br>Mode Set Up         | Function of<br>Mode Set Up                                             |  |  |

| $V_p/V_{po}, V_m/V_{mo}$        | Invalid [I]                     | L                            | Function of<br>Mode Set Up         | Function of<br>Mode Set Up                                             |  |  |

| RCV                             | Invalid [I]                     | L                            | Function of<br>Mode Set Up         | Function of<br>Mode Set Up                                             |  |  |

| Vbusmon                         | Invalid [I]                     | L                            | Function of<br>Mode Set Up         | Function of<br>Mode Set Up                                             |  |  |

| OE, SUSPND, Config              | Hi-Z                            | Hi-Z                         | Function of<br>Mode Set Up         | Function of<br>Mode Set Up                                             |  |  |

Invalid [I] I/O are to be 3-STATE, outputs to be LOW.

#### **ESD Protection**

#### ESD Performance of the USB1T1103

HBM D+/D-: 15.0kV

HBM, all other terminals (Mil-Std 883E): 6.5kV

#### ESD Protection: D+/D- Terminals

Since the differential terminals of a USB transceiver may be subjected to extreme ESD voltages, additional immunity has been included in the D+ and D- terminals without compromising performance. The USB1T1103 differential terminals have ESD protection to the following limits:

- 15kV using the contact Human Body Model

- 8kV using the Contact Discharge method as specified in IEC 61000-4-2

#### **Human Body Model**

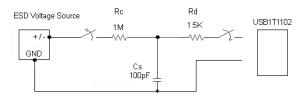

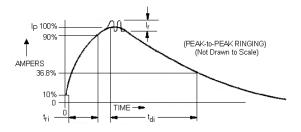

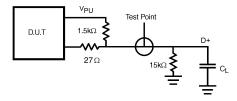

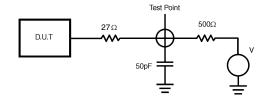

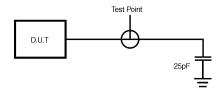

Figure 1 shows the schematic representation of the Human Body Model ESD event. Figure 2 is the ideal waveform representation of the Human Body Model.

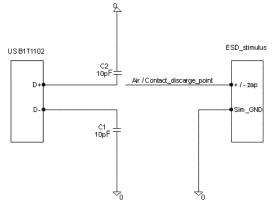

#### IEC 61000-4-2, IEC 60749-26 and IEC 60749-27

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment, and as such evaluates the equipment in its entirety for ESD immunity. Fairchild Semiconductor has evaluated this device using the IEC 6100-4-2 representative system model depicted in Figure 3. Under the additional standards set forth by the IEC, this device is also compliant with IEC 60749-26 (HBM) and IEC 60749-27 (MM).

#### **Additional ESD Test Conditions**

For additional information regarding our product test methodologies and performance levels, please contact Fairchild Semiconductor.

FIGURE 1. Human Body ESD Test Model

FIGURE 2. HBM Current Waveform

FIGURE 3. IEC 61000-4-2 ESD Test Model

#### **Absolute Maximum Ratings**(Note) **Conditions** -0.5V to +6.0V Supply Voltage (V<sub>CC</sub>)(5V)

-0.5V to +4.6V

I/O Supply Voltage (V<sub>CCIO</sub>)

Latch-up Current (ILU)

$V_1 = -1.8V \text{ to } +5.4V$ 150 mA

DC Input Current (IIK)

$V_1 < 0$ -18 mA

DC Input Voltage (V<sub>I</sub>)

(Note) -0.5V to  $V_{CCIO}$  +0.5V

DC Output Diode Current (IOK)

$V_O > V_{CC}$  or  $V_O < 0$ ±18 mA

DC Output Voltage (V<sub>O</sub>)

(Note) -0.5V to  $V_{CCIO} + 0.5V$

Output Source or Sink Current  $(I_O)$

$V_O = 0$  to  $V_{CC}$

Current for D+, D- Terminals ±12 mA Current for RCV, V<sub>m</sub>/V<sub>p</sub> ±12 mA

DC V<sub>CC</sub> or GND Current

±100 mA  $(I_{CC}, I_{GND})$

ESD Immunity Voltage (V<sub>ESD</sub>);

Contact HBM [3]

Terminals D+, D-,  $I_{LI} < 1\mu A$ ±15kV All Other Terminals [3]  $I_{1.1} < 1 \mu A$ ±6.5kV

Storage Temperature (T<sub>STO</sub>) -40°C to + 125°C

Power Dissipation (P<sub>TOT</sub>)

48 mW I<sub>CC</sub> (5V)

I<sub>CCIO</sub>

**Recommended Operating**

DC Supply Voltage V<sub>CC</sub> (5V) 4.0V to 5.5V

I/O DC Voltage V<sub>CCIO</sub> 1.65V to 3.6V

0V to  $V_{CCIO}$  +5.5V DC Input Voltage Range (V<sub>I</sub>) DC Input Range for AI/O (V<sub>AI/O</sub>) 0V to  $V_{CC}$

Terminals D+ and D-0V to 3.6V

Operating Ambient Temperature

-40°C to +85°C  $(T_{\mathsf{AMB}})$

Note 4: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristic tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 5: IO Absolute Maximum Rating must be observed.

Note 6: Per ESD Methodology described in page 5.

#### DC Electrical Characteristics (Supply Terminals)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC}$  (5V) = 4.0V to 5.5V or  $V_{REG}$  (3.3V) = 3.0V to 3.6V,  $V_{CCIO}$  = 1.65V to 3.6V

| Symbol                     | Parameter                                      | Conditions                                     | -4                   | Limits -40°C to +85°C |           |      |  |

|----------------------------|------------------------------------------------|------------------------------------------------|----------------------|-----------------------|-----------|------|--|

|                            |                                                |                                                | Min                  | Тур                   | Max       | Ì    |  |

| V <sub>REG</sub> (3.3V)    | Regulated Supply Output                        | Internal Regulator Option;                     | 3.0                  | 3.3                   | 3.6       |      |  |

|                            |                                                | $I_{LOAD} \le 300 \ \mu A$                     | (Note 7)<br>(Note 8) |                       |           | V    |  |

| I <sub>CC</sub>            | Operating Supply Current (V <sub>CC</sub> 5.0) | Transmitting and Receiving at                  |                      | 4.0                   | 8.0       | mA   |  |

|                            |                                                | 12 Mbits/s; C <sub>LOAD</sub> = 50 pF (D+, D-) |                      | (Note 9)              |           | IIIA |  |

| I <sub>CCIO</sub>          | I/O Operating Supply Current                   | Transmitting and Receiving at                  |                      | 1.0                   | 2.0       | mA   |  |

|                            |                                                | 12 Mbits/s                                     |                      | (Note 9)              |           | IIIA |  |

| I <sub>CC (IDLE)</sub>     | Supply Current during                          | IDLE: $V_{D+} \ge 2.7V$ , $V_{D-} \le 0.3V$ ;  |                      |                       | 300       | ۸    |  |

|                            | FS IDLE and SE0 (V <sub>CC</sub> 5.0)          | SE0: $V_{D+} \le 0.3V$ , $V_{D-} \le 0.3V$     |                      |                       | (Note 10) | μА   |  |

| I <sub>CCIO</sub> (STATIC) | I/O Static Supply Current                      | IDLE, SUSPND or SE0                            |                      |                       | 20.0      | μА   |  |

| I <sub>CC(DISABLE)</sub>   | Disable Supply Current                         | V <sub>CCIO</sub> = 0V                         |                      |                       | 25.0      | μА   |  |

|                            |                                                | V <sub>CC</sub> Connected                      | 25.                  |                       | 25.0      | μА   |  |

| I <sub>CC(SUSPND)</sub>    | Suspend Supply Current                         | SUSPND = HIGH                                  |                      |                       | 25.0      |      |  |

|                            | USB1T1103                                      | OE = HIGH                                      |                      |                       | (Note 10) | μА   |  |

|                            |                                                | $V_m = V_p = OPEN$                             |                      |                       |           |      |  |

| I <sub>CCIO(SHARING)</sub> | I/O Sharing Mode Supply Current                | V <sub>CC</sub> (5V) Not Connected             |                      |                       | 20.0      | μА   |  |

| I <sub>D+</sub> (SHARING)  | Sharing Mode Load Current on                   | V <sub>CC</sub> (5V) Not Connected             |                      |                       | 10.0      | ^    |  |

| I <sub>D+/-</sub>          | D+/D- Terminals                                | Config = LOW; $V_{D\pm} = 3.6V$                |                      |                       | 10.0      | μА   |  |

| I <sub>D+(DISABLE)</sub>   | Disable Mode Load Current on                   | V <sub>CCIO</sub> Not Connected or 0V          |                      |                       | 10.0      | ^    |  |

| I <sub>D+/-</sub>          | D+/D- Terminals                                | Config = $V_D \pm = 3.6V$ LOW or HIGH          |                      |                       | 10.0      | μА   |  |

9 mW

## DC Electrical Characteristics (Continued)

|                      |                                                             |                                                                                                      |                  | Limits -40°C to +85°C |     |    |

|----------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----|----|

| Symbol               | Parameter                                                   | Conditions                                                                                           | -4               |                       |     |    |

|                      |                                                             |                                                                                                      | Min              | Тур                   | Max |    |

| V <sub>CCTH</sub>    | V <sub>CC</sub> Threshold Detection Voltage                 | 1.65V ≤ V <sub>CCIO</sub> ≤ 3.6V                                                                     |                  |                       |     |    |

|                      |                                                             | Supply Lost                                                                                          |                  |                       | 3.6 | V  |

|                      |                                                             | Supply Present                                                                                       | 4.1              |                       |     |    |

| V <sub>CCHYS</sub>   | V <sub>CC</sub> Threshold Detection<br>Hysteresis Voltage   | V <sub>CCIO</sub> = 1.8V                                                                             |                  | 70.0                  |     | mV |

| V <sub>CCIOTH</sub>  | V <sub>CCIO</sub> Threshold Detection Voltage               | 2.7V ≤ V <sub>REG</sub> ≤ 3.6V                                                                       |                  |                       |     |    |

|                      |                                                             | Supply Lost                                                                                          |                  |                       | 0.5 | V  |

|                      |                                                             | Supply Present                                                                                       | 1.4              |                       |     |    |

| V <sub>CCIOHYS</sub> | V <sub>CCIO</sub> Threshold Detection<br>Hysteresis Voltage | V <sub>REG</sub> = 3.3V                                                                              |                  | 450                   |     | mV |

| V <sub>REGTH</sub>   | Regulated Supply Threshold Detection Voltage                | $\begin{aligned} 1.65 V &\leq V_{CCIO} \leq V_{REG} \\ 2.7 V &\leq V_{REG} \leq 3.6 V \end{aligned}$ |                  |                       |     |    |

|                      |                                                             | Supply Lost                                                                                          |                  |                       | 0.8 | V  |

|                      |                                                             | Supply Present                                                                                       | 2.4<br>(Note 12) |                       |     |    |

| V <sub>REGHYS</sub>  | Regulated Supply Threshold Detection Hysteresis Voltage     | V <sub>CCIO</sub> = 1.8V                                                                             |                  | 450                   |     | mV |

Note 7:  $I_{LOAD}$  includes the pull-up resistor current via terminal  $V_{PU}$

Note 8: The minimum voltage in Suspend mode is 2.7V.

Note 9: Not tested in production, value based on characterization.

Note 10: Excludes any current from load and  $V_{\mbox{\footnotesize{PU}}}$  current to the 1.5k $\!\Omega$  resistor.

Note 11: Includes current between  $\mathrm{V}_{\mathrm{pu}}$  and the 1.5k internal pull-up resistor.

Note 12: When  $V_{CCIO}$  < 2.7V, minimum value for  $V_{REGTH}$  = 2.0V for supply present condition.

## DC Electrical Characteristics (Digital Terminals – excludes D+, D- Terminals)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CCIO} = 1.65V$  to 3.6V

|                                    |                           |                                   | Lin                      | Limits -40°C to +85°C |    |  |

|------------------------------------|---------------------------|-----------------------------------|--------------------------|-----------------------|----|--|

| Symbol                             | Parameter                 | Test Conditions                   | -40°C t                  |                       |    |  |

|                                    |                           |                                   | Min                      | Max                   |    |  |

| Input Levels                       |                           |                                   |                          |                       |    |  |

| V <sub>IL</sub>                    | LOW Level Input Voltage   |                                   |                          | 0.3*V <sub>CCIO</sub> | V  |  |

| V <sub>IH</sub>                    | HIGH Level Input Voltage  |                                   | 0.6*V <sub>CCIO</sub>    |                       | V  |  |

|                                    | OUTPUT LEVELS:            |                                   |                          |                       |    |  |

| V <sub>OL</sub>                    | LOW Level Output Voltage  | I <sub>OL</sub> = 2 mA            |                          | 0.4                   | V  |  |

|                                    |                           | $I_{OL} = 100 \ \mu A$            |                          | 0.15                  | V  |  |

| V <sub>OH</sub>                    | HIGH Level Output Voltage | I <sub>OH</sub> = 2 mA            | V <sub>CCIO</sub> - 0.4  |                       | V  |  |

|                                    |                           | I <sub>OH</sub> = 100 μA          | V <sub>CCIO</sub> - 0.15 |                       | V  |  |

| Leakage Cu                         | rent                      | <u> </u>                          | •                        |                       |    |  |

| lu                                 | Input Leakage Current     | V <sub>CCIO</sub> = 1.65V to 3.6V |                          | ±1.0<br>(Note 13)     | μА |  |

| Capacitance                        |                           | <u>.</u>                          | •                        |                       |    |  |

| C <sub>IN</sub> , C <sub>I/O</sub> | Input Capacitance         | Terminal to GND                   |                          | 10.0                  | pF |  |

Note 13: If  $V_{CCIO} \ge V_{REG}$  then leakage current will be higher than specified.

## DC Electrical Characteristics (Analog I/O Terminals – D+, D- Terminals)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC} = 4.0 \text{V}$  to 5.5V or  $V_{REG} = 3.0 \text{V}$  to 3.6V

|                   |                                  |                                         |                               | Limits            |      |       |  |

|-------------------|----------------------------------|-----------------------------------------|-------------------------------|-------------------|------|-------|--|

| Symbol            | Parameter                        | Test Condition                          | -40°C to +85°C                |                   |      | Units |  |

|                   |                                  |                                         | Min                           | Тур               | Max  |       |  |

| Input Levels      | - Differential Receiver          |                                         | •                             |                   |      |       |  |

| V <sub>DI</sub>   | Differential Input Sensitivity   | V <sub>I(D+)</sub> - V <sub>I(D-)</sub> | 0.2                           |                   |      | V     |  |

| V <sub>CM</sub>   | Differential Common Mode Voltage |                                         | 0.8                           |                   | 2.5  | V     |  |

| INPUT LEVE        | LS - Single-ended Receiver       |                                         | •                             |                   |      |       |  |

| V <sub>IL</sub>   | LOW Level Input Voltage          |                                         |                               |                   | 0.8  | V     |  |

| V <sub>IH</sub>   | HIGH Level Input Voltage         |                                         | 2.0                           |                   |      | V     |  |

| V <sub>HYS</sub>  | Hysteresis Voltage               |                                         | 0.30                          |                   | 0.7  | V     |  |

| Output Leve       | ls                               |                                         | •                             |                   |      | •     |  |

| V <sub>OL</sub>   | LOW Level Output Voltage         | $R_L = 1.5k\Omega$ to 3.6V              |                               |                   | 0.3  | V     |  |

| V <sub>OH</sub>   | HIGH Level Output Voltage        | $R_L = 15k\Omega$ to GND                | 2.8<br>(Note 14)              |                   | 3.6  | V     |  |

| Leakage Cui       | rent                             | •                                       | •                             |                   |      |       |  |

| I <sub>OFF</sub>  | Input Leakage Current Off State  |                                         |                               |                   | ±1.0 | μΑ    |  |

|                   | CAPACITANCE                      |                                         | •                             |                   |      |       |  |

| C <sub>I/O</sub>  | I/O Capacitance                  | Terminal to GND                         |                               |                   | 20.0 | pF    |  |

| Resistance        | -                                | - 1                                     |                               |                   |      |       |  |

| Z <sub>DRV</sub>  | Driver Output Impedance          |                                         | 34.0                          | 41.0<br>(Note 15) | 44.0 | Ω     |  |

| Z <sub>IN</sub>   | Driver Input Impedance           |                                         | 10.0                          |                   |      | MΩ    |  |

| R <sub>SW</sub>   | Switch Resistance                |                                         |                               |                   | 10.0 | Ω     |  |

| V <sub>TERM</sub> | Termination Voltage              | R <sub>PU</sub> Upstream Port           | 3.0<br>(Note 16)<br>(Note 17) |                   | 3.6  | V     |  |

**Note 14:** If V<sub>OH</sub> min. = V<sub>REG</sub> - 0.2V.

Note 15: Includes external resistors of  $27\Omega$  on both D+ and D- terminals.

Note 16: This voltage is available at terminal  $\rm V_{PU}$  and  $\rm V_{REG}.$

Note 17: Minimum voltage is 2.7V in the suspend mode.

## AC Electrical Characteristics (A I/O Terminals Full Speed)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC} = 4.0 \text{V to } 5.5 \text{V or } V_{REG} = 3.0 \text{V to } 3.6 \text{V}, V_{CCIO} = 1.65 \text{V to } 3.6 \text{V}, C_L = 50 \text{ pF}; R_L = 1.5 \text{K on D+ to V}_{PU}$

|                  |                                              |                                                          |                | Limits |       |      |

|------------------|----------------------------------------------|----------------------------------------------------------|----------------|--------|-------|------|

| Symbol           | Parameter                                    | Test Conditions                                          | -40°C to +85°C |        |       | Unit |

|                  |                                              |                                                          | Min            | Тур    | Max   |      |

| Driver Cha       | racteristics                                 |                                                          |                |        |       |      |

| t <sub>R</sub>   | Output Rise Time                             | C <sub>L</sub> = 50 – 125 pF                             | 4.0            |        | 20.0  |      |

|                  |                                              | 10% to 90%                                               |                |        |       | ns   |

| $t_{F}$          | Output Fall Time                             | Figures 4, 8                                             | 4.0            |        | 20.0  |      |

| t <sub>RFM</sub> | Rise/Fall Time Match                         | t <sub>F</sub> /t <sub>R</sub> Excludes First Transition | 90.0           |        | 111.1 | %    |

|                  |                                              | from Idle State                                          | 90.0           |        | 111.1 | %    |

| V <sub>CRS</sub> | Output Signal Crossover Voltage              | Excludes First Transition from                           | 1.3            |        | 2.0   | V    |

| (Note 18)        |                                              | Idle State see Waveform                                  | 1.3            |        | 2.0   | V    |

| Driver Tim       | ing                                          |                                                          |                |        |       |      |

| t <sub>PLH</sub> | Propagation Delay                            | Figures 5, 8                                             |                |        | 18.0  | ns   |

| t <sub>PHL</sub> | $(V_p/V_{po}, V_m/V_{mo} \text{ to } D+/D-)$ | rigules 5, 6                                             |                |        | 16.0  | 115  |

| t <sub>PHZ</sub> | Driver Disable Delay                         | Figures 7, 8                                             |                |        | 15.0  | ns   |

| $t_{PLZ}$        | (OE to D+/D-)                                | rigules 7, 6                                             |                |        | 13.0  | 115  |

| t <sub>PZH</sub> | Driver Enable Delay                          | Figure 7.0                                               |                |        | 15.0  |      |

| $t_{PZL}$        | (OE to D+/D-)                                | Figures 7, 9                                             |                |        | 15.0  | ns   |

| Receiver T       | iming                                        |                                                          |                |        |       |      |

| t <sub>PLH</sub> | Propagation Delay (Diff)                     | Figures 6, 10                                            |                |        | 15.0  | ne   |

| $t_{PHL}$        | (D+/D- to Rev)                               | rigules 6, 10                                            |                |        | 13.0  | ns   |

| t <sub>PLH</sub> | Single Ended Receiver Propagation Delay      | Figures 6, 10                                            |                |        | 18.0  | ns   |

| t <sub>PHL</sub> | $(D+/D- to V_p/V_{po}, V_m/V_{mo})$          | i iguies 0, 10                                           |                |        | 10.0  | 115  |

Note 18: Not production tested, limits guaranteed by design.

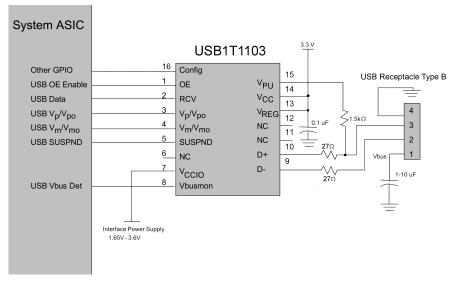

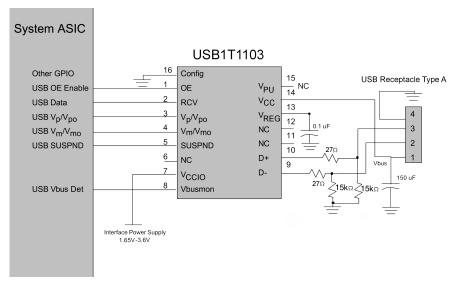

## **Typical Application Configurations**

Upstream Connection in Bypass Mode with Differential Outputs

**Downstream Connection in Normal Mode with Differential Outputs**

#### **AC Waveforms**

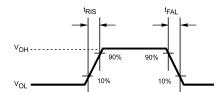

FIGURE 4. Rise and Fall Times

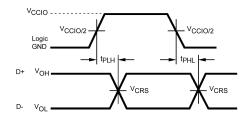

FIGURE 5.  $V_{po}$ ,  $V_{mo}$  to D+/D-

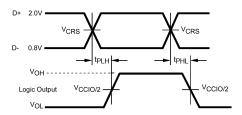

FIGURE 6. D+/D- to R<sub>CV</sub>,  $V_{po}/V_{p}$  and  $V_{mo}/V_{m}$

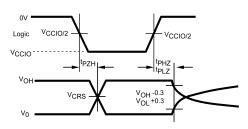

FIGURE 7. OE to D+/D-

## **Test Circuits and Waveforms**

- $C_L = 50 \ pF$  Full Speed Propagation Delays  $C_L = -125 \ pF$  Edge Rates only

FIGURE 8. Load for D+/D-

$V=0 \ for \ t_{PZH}, \ t_{PHZ}$  $V = V_{REG}$  for  $t_{PZL}$

FIGURE 9. Load for Enable and Disable Times

FIGURE 10. Load for  $\rm V_m/\rm V_{mo}, \rm V_{p/}\rm V_{po}$  and RCV

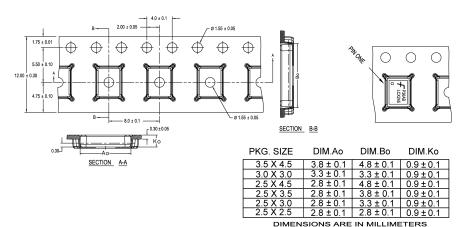

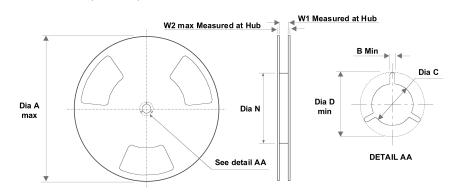

## **Tape and Reel Specification**

Tane Format for MHRCC and MI P

| Tape Format for Min | Tape Format for MinbCC and MLF |           |        |            |  |  |  |  |  |

|---------------------|--------------------------------|-----------|--------|------------|--|--|--|--|--|

| Package             | Tape                           | Number    | Cavity | Cover Tape |  |  |  |  |  |

| Designator          | Section                        | Cavities  | Status | Status     |  |  |  |  |  |

|                     | Leader (Start End)             | 125 (typ) | Empty  | Sealed     |  |  |  |  |  |

| MHX/MPX             | Carrier                        | 2500/3000 | Filled | Sealed     |  |  |  |  |  |

|                     | Trailer (Hub End)              | 75 (typ)  | Empty  | Sealed     |  |  |  |  |  |

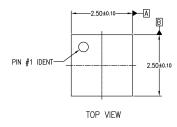

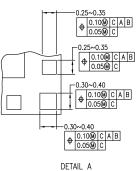

#### TAPE DIMENSIONS inches (millimeters)

#### NOTES: unless otherwise specified

- 1. Cummulative pitch for feeding holes and cavities (chip pockets) not to exceed 0.008[0.20] over 10 pitch span.

- Smallest allowable bending radius.

Thru hole inside cavity is centered within cavity.

- 3. Intu note inside carry is centered within cavity.

4. Tolerance is ±0.002[0.05] for these dimensions on all 12mm tapes.

5. Ao and Bo measured on a plane 0.120[0.30] above the bottom of the pocket.

6. Ko measured from a plane on the inside bottom of the pocket to the top surface of the carrier.

7. Pocket position relative to sprocket hole measured as true position of pocket. Not pocket hole.

8. Controlling dimension is millimeter. Diemension in inches rounded.

- **REEL DIMENSIONS** inches (millimeters)

| Tape Size | Α    | В      | С       | D       | N     | W1     | W2     |

|-----------|------|--------|---------|---------|-------|--------|--------|

| 12 mm     | 13.0 | 0.059  | 0.512   | 0.795   | 7.008 | 0.488  | 0.724  |

|           | 330  | (1.50) | (13.00) | (20.20) | (178) | (12.4) | (18.4) |

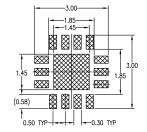

## Physical Dimensions inches (millimeters) unless otherwise noted

#### NOTES:

- A. NO JEDEC REGISTRATION

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

MLP14DrevA

Pb-Free 14-Terminal Molded Leadless Package (MLP), 2.5mm Square Package Number MLP14D

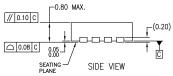

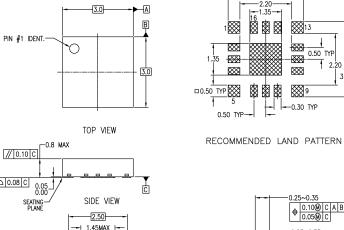

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

0.50

#### NOTES:

- A. SIMILAR TO JEDEC REGISTRATION MO-217, DATED 11/2001

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

MI P16HBrevA

# Pb-Free 16-Terminal Molded Leadless Package (MHBCC), JEDEC MO-217, 3mm Square Package Number MLP16HB

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com